Académique Documents

Professionnel Documents

Culture Documents

Tema VHDL

Transféré par

María MarmagoTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Tema VHDL

Transféré par

María MarmagoDroits d'auteur :

Formats disponibles

Captulo 3

Lenguaje VHDL de Descripcin

Hardware

ndice General

3.1. Introduccin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

59

3.2. Descripcin del lenguaje . . . . . . . . . . . . . . . . . . . . . . . . .

59

3.2.1. Objetos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

61

3.2.2. Tipos de datos . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

61

3.2.3. Entidad . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

62

3.2.4. Arquitectura . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

63

3.2.5. Sentencias secuenciales . . . . . . . . . . . . . . . . . . . . . . .

63

3.2.6. Sentencias concurrentes . . . . . . . . . . . . . . . . . . . . . . .

65

3.3. Descripcin de circuitos combinacionales . . . . . . . . . . . . . .

67

3.3.1. Multiplexor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

67

3.3.2. Descodificador . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

67

3.3.3. Sumador . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

69

3.4. Descripcin de circuitos secuenciales . . . . . . . . . . . . . . . . .

69

3.4.1. Biestable tipo D . . . . . . . . . . . . . . . . . . . . . . . . . . . .

69

3.4.2. Biestable tipo T . . . . . . . . . . . . . . . . . . . . . . . . . . . .

71

3.4.3. Registro de 8 bits con reset asncrono y seal de carga . . . . . .

72

3.4.4. Registro de desplazamiento de 8 bits con reset asncrono . . . .

74

3.4.5. Contador de 8 bits con reset asncrono, seal de carga y habilitacin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

75

3.5. Diseo de mquinas de estado

. . . . . . . . . . . . . . . . . . . . .

75

3.5.1. Ejemplo . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

76

3.6. Fichero de estmulos . . . . . . . . . . . . . . . . . . . . . . . . . . . .

78

58

Lenguaje VHDL de Descripcin Hardware

El empuje de la electrnica de los ltimos aos permite disponer de dispositivos con mayores escalas de integracin y consumos menores, proceso que se acenta

con el paso de los aos. Actualmente es posible disponer de dispositivos programables

que superan el milln de puertas equivalentes, por no hablar de los dispositivos programables a nivel de mscaras, que la superan ampliamente. Esta enorme capacidad

hace posible la implementacin de diseos digitales de gran complejidad, cuya realizacin a base de ecuaciones lgicas o captura esquemtica es prcticamente imposible,

consumiendo un tiempo de diseo prohibitivo. En este sentido, los lenguajes de descripcin hardware surgen como una herramienta fundamental para el ingeniero a la hora

de abordar estos diseos. Utilizando un smil histrico, los lenguajes de descripcin

hardware suponen algo as como la evolucin desde el trabajo artesanal a la produccin industrial.

La amplia popularidad de estos lenguajes ha posibilitado que su uso no se limite

nicamente a dispositivos de gran capacidad, sino que tambin se encuentra en entornos de desarrollo de dispositivos de pequea capacidad.

En este captulo se estudiar una versin muy reducida del lenguaje VHDL. Se

omitirn aquellos tipos, variables, estructuras de control y otros elementos que no sean

imprescindibles para realizar un diseo pequeo que pueda implementarse en un dispositivo lgico de baja capacidad.

3.1 Introduccin

59

3.1. Introduccin

Un lenguaje de descripcin hardware (HDL, Hardware Description Language) permite

el diseo y simulacin de circuitos electrnicos digitales complejos con un nivel de abstraccin

muy superior a las tcnicas tradicionales, como son los mapas de Karnaugh o las ecuaciones

Booleanas. Los lenguajes HDL han supuesto para la electrnica un avance similar al que

supuso la aparicin de lenguajes de alto nivel, como el C, frente a la programacin en ensamblador. En este tema se va a estudiar el lenguaje de descripcin hardware ms popular

llamado VHDL (VHSIC HDL; donde VHSIC: Very High Speed Integrated Circuits).

Las ventajas fundamentales que aporta un lenguaje como VHDL frente a las tcnicas

tradicionales son las siguientes:

Potencia y flexibilidad.

VHDL permite realizar descripciones esquemticas o de comportamiento de los circuitos. Es un lenguaje de simulacin y de sntesis. La sntesis consiste en la traduccin del

cdigo VHDL a puertas lgicas.

Independencia de la tecnologa.

VHDL permite la descripcin funcional previa de un circuito sin especificar un dispositivo concreto para su implementacin final.

Portabilidad.

VHDL es un estndar que permite que el cdigo sea portable y reutilizable entre entornos de trabajo de distintos fabricantes.

Reduccin del ciclo de diseo1 .

Como consecuencia de lo anterior, el diseo con VHDL permite un flujo de diseo rpido

puesto que el cdigo puede simularse y depurarse antes de realizar la sntesis. Es decir,

se puede verificar la lgica del circuito antes de su traduccin a puertas lgicas. De esta

forma se acelera el diseo, los plazos de entrega y la colocacin de un nuevo producto en

el mercado.

En el mercado existe gran variedad de herramientas para la simulacin y sntesis de

circuitos digitales con el lenguaje VHDL. La gran competencia entre ellas ha ocasionado que

las prestaciones que ofrecen sean muy similares.

3.2. Descripcin del lenguaje

Una descripcin VHDL de un circuito de baja complejidad requiere, al menos de estos 3

elementos:

Libreras (library). La potencialidad de un lenguaje depende en gran medida de sus

libreras. En la cabecera de cada diseo se deben incluir aquellas libreras que se necesiten.

Entidad (entity). Describe la entradas y salidas del diseo, como si se tratase de una

caja negra.

Arquitectura (architecture). Describe el contenido de ese diseo.

1

En ingls se conoce como Time to Market

60

Lenguaje VHDL de Descripcin Hardware

El primer ejemplo es muy simple y muestra como se disea una puerta AND de 2 entradas en VHDL. Se aprecia claramente las 3 partes o elementos necesarios para el diseo de un

circuito con este lenguaje: libreras, entidad y arquitectura.

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

ENTITY and2 IS

PORT (

a,b: IN std_logic;

s:

OUT std_logic

);

END and2;

Pines de entrada

Pin de salida

ARCHITECTURE and2_arq OF and2 IS

BEGIN

s<= a AND b;

END and2_arq;

Las dos primeras lneas son dos sentencias utilizadas habitualmente en el cdigo VHDL

para incluir el paquete estndar std_logic_1164. Esta librera define un tipo de dato llamado

std_logic, utilizado habitualmente en la sntesis y simulacin de circuitos digitales. A continuacin se declara la entidad, que incluye las entradas y salidas, y, finalmente, la arquitectura, que es la descripcin de una puerta AND, utilizando el operador AND de VHDL.

Las palabras reservadas del lenguaje VHDL se escribirn en maysculas en este documento para distiguirlas del resto. En los entornos de desarrollo de VHDL no es necesario

hacerlo ya que disponen de editores que las muestran con otro color por lo que no es necesario

utilizar las maysculas para destacarlas.

Los identificadores utilizados por el usuario no pueden ser iguales a estas palabras reservadas y pueden estar formados por letras, dgitos o el carcter "_". El primer carcter

siempre debe ser una letra, y un identificador no puede acabar con el carcter "_", as como

tampoco se pueden usar dos seguidos "__". Por ejemplo, son identificadores legales:

tx_clk, T hree_State_Enable, sel7D, HIT _1029

Por contra no son vlidos los identificadores:

_tx_clk, 8B10B, large#num, register, clk_, link__bar

Como es habitual en cualquier lenguaje de programacin, estn prohibidas las vocales acentuadas as como la letra "".

La estructura genrica de un cdigo VHDL es la indicada a continuacin. El doble carcter indica que el texto que viene a continuacin, hasta el final de la lnea, es un

comentario.

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

ENTITY eee IS

PORT (

declaracin de los puertos de entrada y salida

);

END eee;

ARCHITECTURE aaa OF eee IS

declaraciones de tipos de datos y objetos

BEGIN

lneas de cdigo

END aaa;

3.2 Descripcin del lenguaje

61

3.2.1. Objetos

Los objetos que se manejan en un cdigo VHDL son constantes, seales y variables.

Todos ellos deben ser declarados en su lugar correspondiente dentro de la arquitectura. La

declaracin genrica de un objeto es la siguiente:

OBJETO nombre : TIPO [ := expresin ]

Constantes (CONSTANT). Una constante define un valor que no vara dentro de la

descripcin VHDL. Se utilizan para mejorar la legibilidad del cdigo y facilitar su modificacin.

CONSTANT cierto

: BOOLEAN := true;

CONSTANT ciclo

: TIME

:= 20ns;

Seales (SIGNAL). Las seales pueden representar cables o elementos de memoria. Los

puertos de entrada o salida de la declaracin de la entidad son seales que se pueden

utilizar en el bloque de la arquitectura sin necesidad de volverlos a declarar. La siguiente declaracin podra ser un contador de 4 bits declarado dentro de la arquitectura:

SIGNAL contador : std_logic_vector(3 DOWNTO 0);

Variables (VARIABLE). Las variables se usan nicamente en procesos (que se vern

ms adelante). La sntesis de una variable depende de la herramienta utilizada por lo

que no se tiene un concepto fsico claro de lo que va a resultar. No se usarn en este

texto y se deja para cursos ms avanzados.

3.2.2. Tipos de datos

Los nicos tipos de datos que se van a utilizar en este texto son las dos siguientes:

Enumerado. La enumeracin define una lista que un objeto de ese tipo soporta. Se utiliza habitualmente para definir las mquinas de estado. Por ejemplo, se podra declarar

una seal (signal) tipo estado de la siguiente manera:

TYPE estado IS (inicio,estado1,estado2,estado3,estado4,final);

SIGNAL estado_actual, estado_siguiente: estado;

std_logic y std_logic_vector. Constituyen los tipos lgicos estndar para diseos digitales, y se dispone de ellos incluyendo el paquete std_logic_1164. Los valores definidos en

este estndar aparecen en la tabla 3.1.

Sintaxis

0

1

Z

L

H

Valor

fuerza un cero lgico.

fuerza un uno lgico.

alta impedancia.

cero lgico dbil (pull-up). No se usar.

uno lgico dbil (pull-down). No se usar.

no importa.

Cuadro 3.1: Valores lgicos definidos en el estndar std_logic_1164

La potencia del lenguaje VHDL se basa en las libreras. Sin el paquete std_logic_1164

no se podran trabajar con seales de salida en alta impedancia.

62

Lenguaje VHDL de Descripcin Hardware

Los operadores que se pueden aplicar a los datos de un diseo son los siguientes:

Lgicos

OR

AND

NOR

NAND

XOR

NOT

3.2.3.

Relacionales

= (igual que)

/= (distinto que)

> (mayor que)

< (menor que)

>= (mayor o igual que)

<= (menor o igual que)

Aritmticos

+,-,*,/

(valor absoluto)

Abs

(mdulo)

Mod

(Resto)

Rem

(potencia)

**

(concatena vectores/matrices)

&

Entidad

Una declaracin de una entidad describe el mdulo cuya descripcin VHDL se va a implementar (como si se tratase de un smbolo de una captura esquemtica). Cada entrada o

salida en la declaracin de una entidad se denomina puerto. El puerto se define indicando

su nombre, modo y tipo. El nombre es un identificador vlido, segn las reglas expuestas. El

modo define la direccin en la que se transfiere el dato a travs de ese puerto. La siguiente

tabla 3.2 muestra los diferentes tipos de puertos y sus modos de funcionamiento.

Tipo

IN

OUT

INOUT

BUFFER

Modo de operacin

el dato slo entra a la entidad a travs del puerto.

el dato slo sale de la entidad a travs del puerto.

el dato es bidireccional, es decir, entra o sale de la entidad a travs del puerto.

el dato sale de la entidad a travs del puerto, pero es realimentado internamente,

pudiendo actuar de entrada a elementos de la arquitectura. Una seal de salida es tipo buffer

cuando aparece en el lado derecho de una asignacin o cuando acta como condicin.

Es decir, cuando influye en el valor de otra seal interna o de otro puerto de salida.

Cuadro 3.2: Tipos de puertos definidos en VHDL

En la figura 3.1 se muestra un ejemplo de los modos de funcionamiento de los puertos

detallados anteriormente.

In

Out

Buffer

Inout

In

In

Out

Figura 3.1: Modos de un puerto

3.2 Descripcin del lenguaje

63

Por ejemplo, la declaracin de una entidad correspondiente a un sumador de 4 bits (figura 3.2) y su esquema seran de la forma:

ci

ENTITY add4 IS PORT(

a,b: IN std_logic_vector(3 DOWNTO 0);

IN std_logic;

ci:

sum: OUT std_logic_vector(3 DOWNTO 0);

co:

OUT std_logic);

END add4;

a[3:0]

sum[3:0]

co

b[3:0]

Figura 3.2: Sumador de 4 bits

3.2.4. Arquitectura

La arquitectura describe la funcionalidad de la caja negra declarada anteriormente.

Bsicamente, existen tres estilos fundamentales para describir esta funcionalidad dentro del

cuerpo de la arquitectura:

Descripcin de comportamiento (behavioral). Alto nivel de abstraccin.

Descripcin de flujo de datos (dataflow). Mediano/Bajo nivel de abstraccin.

Descripcin estructural (structural). Nulo nivel de abstraccin.

El tipo de descripcin de la arquitectura depende del tipo de elementos y estructuras que

se utilicen dentro de ella. Por ejemplo la descripcin de mayor nivel de abstraccin (behavioral) solo utiliza procesos. En este texto se utilizarn, dentro de la arquitectura, los diferentes

elementos de sintaxis que se proponen en los siguientes apartados sin prestar atencin al tipo

de descripcin que resulte para la arquitectura.

En general, descripciones diferentes pueden dan lugar a implementaciones electrnicas

distintas aunque funcionalmente equivalentes. Un herramienta de sntesis ser buena si es

capaz de llegar al resultado ptimo partiendo de descripciones diferentes.

3.2.5. Sentencias secuenciales

En este tema introductorio solo se estudiar la sintaxis bsica de VHDL. Se omitirn bastantes elementos de sta como es el caso de los bucles iterativos o las funciones.

Las sentencias secuenciales se ubican solo en el cuerpo de un proceso o de un subprograma (no se estudiarn). Permiten describir o modelar funcionalidad de un componente.

Aunque los circuitos digitales trabajan en paralelo, pueden ser modelados por una serie

de expresiones secuenciales, de forma similar a como se hara con un lenguaje de propsito

general. Las dos sentencias que se estudiarn en este apartado son la sentencia if y la sentencia case.

La sentencia if

La asignacin condicional secuencial debe utilizarse dentro de un proceso. Puede presentarse de diferentes formas:

IF

IF-ELSE

IF-ELSIF-ELSIF-...-ELSE

64

Lenguaje VHDL de Descripcin Hardware

Su sintaxis genrica es:

IF condicion1 THEN

sentencias secuenciales

ELSIF condicion2 THEN

sentencias secuenciales

ELSE

sentencias secuenciales

END IF;

A continuacin se muestra un ejemplo y el resultado de su sntesis en puertas. Se aprecia que el circuito, resultado de la sntesis, cumple con el orden secuencial de la sentencia if.

y

a

f

PROCESS (a,b,c,x,y)

BEGIN

IF x=1 THEN

f <= a;

ELSIF y=1 THEN

f <= b;

ELSE

f <= c;

END IF;

END PROCESS

La interpretacin secuencial del cdigo anterior supone que la salida tomar el valor de

la entrada a siempre que x valga 1. La salida tomar el valor de la entrada b no slo cuando

y valga 1, sino cuando adems se verifique que x valga cero. La secuencialidad del cdigo

supone que no se comprueba la condicin del ELSIF a menos que no se cumpla la condicin del

IF. Finalmente, la salida ser igual a c cuando no se cumpla ninguna de las dos condiciones

previas. La sntesis refleja la interpretacin indicada.

El ltimo ELSE es vital para garantizar que el circuito sea puramente combinacional.

Si no estuviera y se diera ese caso ([x,y]=00), el sistema intentara que la salida f mantuviera

su valor anterior, es decir, introducira un biestable para almacenar el valor de f por lo que el

circuito dejara de ser combinacional.

La sentencia case

La estructura condicional CASE-WHEN especifica una serie de asignaciones condicionales en funcin de una seal de seleccin. Su sintaxis, de forma genrica, es:

CASE valor_seleccion IS

WHEN valor_1 =>

sentencias_secuenciales;

WHEN valor_2 =>

sentencias_secuenciales;

WHEN valor_3 =>

sentencias_secuenciales;

...

WHEN valor_n =>

sentencias_secuenciales;

WHEN OTHERS =>

sentencias_secuenciales;

END CASE;

3.2 Descripcin del lenguaje

65

Con la ltima condicin, WHEN OTHERS, se cubren las condiciones no contempladas

en los valores anteriores. En los valores expresados a continuacin de la palabra reservada

WHEN deben de cubrirse todos los posibles valores de la seal de seleccin; por tanto, usar

WHEN OTHERS es opcional siempre y cuando se cubran los valores posibles de la seal de

seleccin.

La sentencia CASE se utiliza habitualmente en el diseo de mquinas de estado. Ms

adelante se ver algn ejemplo de uso de la misma.

3.2.6. Sentencias concurrentes

La caracterstica comn a todas ellas es que se ejecutan en paralelo. Principalmente las encontramos en las arquitecturas de los modelos y no estarn contenidas en ningn

proceso. Las tres sentencias concurrentes que se estudiarn en este apartado son:

La sentencia process (proceso).

Asignacin a seal concurrente.

Asignacin concurrente condicional (WHEN-ELSE).

La sentencia process

Los procesos son bloques que se van evaluar en paralelo con otras sentencias concurrentes: otros procesos o asignaciones. Sin embargo, el contenido de un proceso se evala secuencialmente. Este hecho obliga a que las sentencias que constituyen el cuerpo de un proceso

sean sentencias secuenciales. La sntesis de la descripcin VHDL generar un circuito digital que se comporte segn ese cdigo que se ejecuta de forma secuencial (ver ejemplo de la

sentencia if). Dentro de una arquitectura pueden existir varios procesos, que se ejecutan de

manera concurrente entre s.

La sintaxis genrica de un proceso se muestra a continuacin. La etiqueta y la declaracin de variables son opcionales.

[etiqueta:] PROCESS [(lista sensible)]

declaraciones de variables (no se utilizarn variables en este texto)

BEGIN

sentecias secuenciales

END PROCESS [etiqueta];

Normalmente, el proceso se encuentra en modo suspendido hasta que se produce un

cambio en una de las seales que figura en la lista de variables sensibles (sensitivity list).

Cuando se produce un evento en una de estas seales, se ejecutan las lneas de cdigo del

proceso, realizndose la asignacin de las seales al final de la ejecucin del proceso. Una vez

finalizado el proceso, entra de nuevo en modo suspendido hasta que vuelva a producirse un

nuevo evento en una de las seales de la lista sensible.

Si el proceso contiene la sentencia WAIT, utilizada para la simulacin, entonces no puede tener lista sensible. La explicacin se deja para textos ms avanzados sobre VHDL.

En los circuitos sncronos, todos los elementos secuenciales cambian su valor con el flanco de reloj. En consecuencia, la descripcin en VHDL de cualquier elemento de memoria sncrono deber utilizar un proceso con el reloj en su lista sensible. Todas las asignaciones que se

realizan dentro de un proceso se hacen efectivas al final del mismo a efectos de interpretacin

y simulacin.

66

Lenguaje VHDL de Descripcin Hardware

Asignacin a seal concurrente

Se encuentran fuera de un proceso y son evaluadas en paralelo con el resto de procesos

y asignaciones concurrentes que estn presentes en la arquitectura. La sintaxis genrica es

la siguiente:

[etiqueta:] nombre_seal <= expresin_o_dato;

En realidad este tipo de sentencia es equivalente a un proceso cuya lista sensible est

compuesta por las variables que aparecen en el trmino de la derecha de la asignacin. A

continuacin se muestra el proceso equivalente de la sentencia y <= a (a la izquierda), y el

proceso equivalente a la sentencia y <= (a AND (NOT b)) OR (a AND c) (a la derecha).

PROCESS (a)

BEGIN

y <= a

END PROCESS;

PROCESS (a,b,c)

BEGIN

y <= (a AND (NOT b)) OR (a AND c)

END PROCESS;

Asignacin concurrente condicional (WHEN-ELSE)

La asignacin condicional concurrente que estudiaremos es de la forma WHEN-ELSE.

Su sintaxis, de forma genrica, es:

nombre_seal <= valor_1 WHEN condicion1 ELSE

valor_2 WHEN condicion2 ELSE

...

valor_n WHEN condicionn ELSE

valor_x;

Segn las condiciones, a la seal se le asigna un valor. La prioridad va segn el orden

de aparicin. Es decir, una vez que una de las condiciones se cumple, es indiferente si alguna otra condicin ms abajo se verifica, se asigna el valor de la primera condicin que se

cumple. Es importante poner siempre un ELSE al final para evitar que la sntesis introduzca

latches en la implementacin en puertas, normalmente indeseados en una lgica puramente

combinacional.

En la tabla 3.3 se detallan las sentencias concurrentes, as como algunos ejemplos.

Sentencias concurrentes

Asignacin a seal

Asignacin condicional

Ejemplos

x <= (a AND (NOT sel1)) OR (b AND sel1);

g <= NOT (y AND sel2);

y <= d WHEN (sel=1) ELSE c;

h <= 0 WHEN (x=1 AND sel2=0) ELSE 1;

y <= a WHEN (sel="00") ELSE

b WHEN (sel="01") ELSE

d WHEN (sel="01") ELSE

d;

Cuadro 3.3: Ejemplos de sentencias que se interpretan concurrentemente en VHDL

3.3 Descripcin de circuitos combinacionales

67

3.3. Descripcin de circuitos combinacionales

3.3.1. Multiplexor

Como ejemplo, se realizar la descripcin VHDL de un multiplexor de 4 a 1, cuyas entradas y salidas son elementos de 4 bits. A continuacin se muestra el cdigo VHDL del circuito

y el esquema del circuito. La sentencia ms apropiada es la asignacin condicional.

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

ENTITY mux IS

PORT (

a,b,c,d : IN std_logic_vector(3 DOWNTO 0);

: IN std_logic_vector(1 DOWNTO 0);

sel

y

: OUT std_logic_vector(3 DOWNTO 0)

);

END mux;

a[3:0]

b[3:0]

y[3:0]

c[3:0]

d[3:0]

ARCHITECTURE mux_arq OF mux IS

BEGIN

y <= a WHEN (sel="00") ELSE

b WHEN (sel="01") ELSE

c WHEN (sel="10") ELSE

d ;

END mux_arq;

sel(0)

sel(1)

3.3.2. Descodificador

A continuacin se va a realizar la descripcin VHDL de un descodificador de direcciones

para el mapa de memoria de la siguiente figura.

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

FFFF

EEPROM

C000

SRAM

8000

Perifrico 2

Perifrico 1

4010

4008

4000

PROM/RAM

0000

ENTITY decod IS

PORT (

: IN std_logic_vector(15 DOWNTO 0);

bus_dir

arranque

: IN std_logic;

ram, prom, per1, per2, sram, eeprom : OUT std_logic

);

END decod;

ARCHITECTURE decod_arq OF decod IS

BEGIN

PROCESS (bus_dir, arranque, habilita)

BEGIN

sram <= 0;

ram <= 0;

prom <= 0;

per1 <= 0;

eeprom <= 0;

per2 <= 0;

IF ( bus_dir >=x"0000"AND bus_dir <=x"4000") THEN

IF (arranque=1) THEN

ram<=1;

ELSE

prom<=1;

END IF;

ELSIF ( bus_dir >=x"4000"AND bus_dir <x"4008") THEN

per1<=1;

ELSIF ( bus_dir >=x"4008"AND bus_dir <x"4010") THEN

per2<=1;

ELSIF ( bus_dir >=x"8000"AND bus_dir <x" C000") THEN

sram<=1;

ELSIF ( bus_dir >=x" C000") THEN

eeprom<=1;

END IF;

END PROCESS;

END decod_arq;

68

Lenguaje VHDL de Descripcin Hardware

La descripcin se ha realizado usando la estructura condicional IF-THEN-ELSE. Como

entradas del bloque decodificador se encuentran las 16 lneas de direcciones que cubren el

mapa de memoria de la figura 3.3, de 64 Kb. Las salidas son las seales de seleccin de los

distintos dispositivos, que arbitran que en un instante slo uno de los dispositivos vuelque

informacin al bus de datos.

bus_dir[15:0]

arranque

a15

a14

a15

a14

sram

prom

a15

a14

a15

a14

eepro

m

ram

a15

a14

a13

a12

a11

a10

a9

a8

a7

per1

a6

a5

a4

a3

a15

a14

a13

a12

a11

a10

a9

a8

a7

per2

a6

a5

a4

a3

Figura 3.3: Sntesis del cdigo del decodificador

En este caso, las condiciones expresadas en las sentencias IF son mutuamente excluyentes, y todas las salidas se asignan al principio, por lo que no es necesario incluir un ELSE

final. Como normal general, habr que asegurarse que ninguna combinacin de entradas da

lugar a que una salida quede sin asignar. El valor "x"que aparece al expresar las condiciones relativas al bus de direcciones indica que el valor que viene a continuacin se expresa en

formato hexadecimal, que la forma habitual de trabajar al definir un mapa de memoria.

Evidentemente, de todo el bus de direcciones, tan slo se utilizarn unas cuantas lneas para decodificar, como puede observarse en el resultado de la sntesis de la figura 3.3.

Usualmente, las herramientas de sntesis son lo bastante inteligentes como para eliminar el

cableado innecesario.

3.4 Descripcin de circuitos secuenciales

69

3.3.3. Sumador

Se va a disear un sumador de 4 bits -sin signo- con acarreo de entrada y de salida. En el diseo se va a emplear el operador + por lo que habr que incluir la librera

ieee.std_logic_unsigned.ALL que lo contiene.

Si no hubiera acarreos ni problemas de desbordamiento, el diseo sera tan simple como

escribir la sentencia suma <= a + b. Como resulta que hay que contemplarlos, la dificultad

mayor consistir en calcular el acarreo.

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

ENTITY suma IS

PORT (

a,b : IN

: IN

ci

co

: OUT

suma : OUT

);

END suma;

std_logic_vector(3 DOWNTO 0);

std_logic;

Acarreo de entrada

std_logic;

Acarreo de salida

std_logic_vector(3 DOWNTO 0);

ARCHITECTURE suma_arq OF suma IS

SIGNAL ax, bx, sumax : std_logic_vector(4 DOWNTO 0);

BEGIN

ax(4) <= 0;

ax(3 DOWNTO 0)<= a;

bx(4) <= 0;

bx(3 DOWNTO 0)<= b;

sumax <= (ax+bx+ci) ;

suma <= sumax(3 DOWNTO 0);

co

<= sumax(4);

END suma_arq;

El circuito sumador utilizar 3 seales

internas llamadas ax, bx y sumax de tamao un bit mayor que las originales.

El acarreo se almacenar el bit 4 (nuevo

bit ms significativo) de sumax. Supngase que a=13, b=9 y ci=1. El resultado de la suma desborda el tamao de 4

bits. Se genera acarreo y el valor almacenado en suma = 7. En binario se ve

mejor:

ci

a

b

suma

1

1101

1001

co=1, 0111

3.4. Descripcin de circuitos secuenciales

Todos los circuitos sncronos descritos en VHDL suelen utilizar un proceso con la seal

de reloj clk en su lista sensible, ms una estructura condicional tipo IF que se activa cuando

ocurre una transicin en la seal de reloj, para lo que se utiliza el atributo EVENT.

3.4.1. Biestable tipo D

A continuacin se detallan dos versiones equivalentes del diseo VHDL para el biestable tipo d activo por flanco de subida del reloj. Una versin con la sentencia IF y la otra con la

sentencia IF-ELSE.

D

clk

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

ENTITY dff IS

PORT (

d, clk : IN

q

: OUT

);

END dff;

ENTITY dff IS

PORT (

std_logic;

d, clk : IN

q

: BUFFER std_logic

);

END dff;

std_logic;

std_logic

ARCHITECTURE dff_arq OF dff IS

BEGIN

PROCESS (clk)

BEGIN

IF (clk EVENT AND clk=1) THEN

q<=d;

END IF;

END PROCESS;

END dff_arq;

ARCHITECTURE dff_arq OF dff IS

BEGIN

PROCESS (clk)

BEGIN

IF (clk EVENT AND clk=1) THEN

q<=d;

ELSE

q<=q;

END IF;

END PROCESS;

END dff_arq;

70

Lenguaje VHDL de Descripcin Hardware

Los dos diseos generan un biestable tipo D pero es interesante observar que en la primera opcin no se utiliza ELSE en la estructura condicional. Esto es posible porque estamos

definiendo un elemento de memoria que debe conservar su valor en el caso de que no se verifique la condicin del IF (falta el ELSE).

En la segunda opcin se ha utilizado el ELSE para fijar de forma explcita qu debe

hacer el biestable cuando no ocurre un flanco positivo de reloj (la salida se queda como est

q<=q). En este caso la salida q no debe declararse como OUT sino como BUFFER, ya que la

seal q aparece al lado derecho de una asignacin.

La expresin clkEVENT y el hecho de incluir la seal clk en la lista sensible son redundantes. Es decir, ambas sirven para detectar un evento sobre la seal clk. La explicacin

de esta redundancia en el cdigo es que algunas herramientas de sntesis ignoran la lista

sensible, por lo que es necesaria esta expresin clkEVENT.

Biestable tipo D activo por nivel: latch

Si en lugar de describir un biestable activo por nivel se desea describir uno activo por

nivel (latch), sera preciso eliminar la condicin clkEVENT e incluir la entrada d en la lista

sensible. Recurdese que en el caso de un latch la salida se modifica siempre que vare la

entrada y que el reloj se encuentre en su nivel activo.

D

clk

LE

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

ENTITY dff IS

PORT (

d, clk : IN

q

: OUT

);

END dff;

std_logic;

std_logic

ARCHITECTURE dff_arq OF dff IS

BEGIN

PROCESS (clk,d)

BEGIN

IF (clk=1) THEN

q<=d;

END IF;

END PROCESS;

END dff_arq;

Biestable tipo d con reset asncrono

El siguiente cdigo VHDL ilustra cmo describir un biestable con un reset (o preset)

asncrono, esto es, capaz de poner a cero (o a uno) el biestable, independientemente de la seal de reloj.

Es importante destacar que la PAL16R4 y la PAL16R8 (figuras 2.18 y 2.17, respectivamente) no tienen biestables con entrada de reset. Por tanto, la herramienta de sntesis dara

error ya que no podra implementarse en ese tipo de dispositivo. Sin embargo, si podra sintetizarse este biestable en la PAL22V10.

En el siguiente cdigo VHDL se ha diseado un biestable activo por flanco de subida de

reloj y con seal de reset activa a nivel alto. Ambas seales de entrada deben figurar en la

lista sensible.

3.4 Descripcin de circuitos secuenciales

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

ENTITY dff IS

PORT (

d, clk : IN

q

: OUT

);

END dff;

clk

Q

reset

71

std_logic;

std_logic

ARCHITECTURE dff_arq OF dff IS

BEGIN

PROCESS (clk,reset)

BEGIN

IF (reset=1) THEN

q<=0;

ELSIF (clk EVENT AND clk=1) THEN

q<=d;

END IF;

END PROCESS;

END dff_arq;

Biestable tipo d con reset sncrono

En este caso se trata de describir un biestable con reset (o preset) sncrono. Es decir, un

biestable que se pone a 0 o 1 si la seal de reset o preset se activa y ocurre un flanco activo

de reloj. Este dispositivo es apropiado para el hardwarde de la PAL16R4 y la PAL16R8. En el

siguiente ejemplo se muestra un biestable tipo d con reset sncrono activo a nivel alto.

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

d

D

reset

Q

clk

ENTITY dff IS

PORT (

d, clk : IN

q

: OUT

);

END dff;

std_logic;

std_logic

ARCHITECTURE dff_arq OF dff IS

BEGIN

PROCESS (clk)

BEGIN

IF (clk EVENT AND clk=1) THEN

IF (reset=1) THEN

q<=0;

ELSE

q<=d;

END IF;

END IF;

END PROCESS;

END dff_arq;

3.4.2. Biestable tipo T

El biestable tipo T se caracteriza porque su salida (estado) cambia de valor cada vez que

ocurre un flanco activo de reloj y la entrada t est a 1 lgico.

Los dispositivos PAL de registro solo disponen de biestables tipo d en sus etapas de

salida. En este caso la herramienta de sntesis crea el biestable tipo t a partir de un biestable

tipo d ms un multiplexor. A continuacin se muestra el cdigo VHDL y el resultado de la

sntesis.

72

Lenguaje VHDL de Descripcin Hardware

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

0

t

clk

ENTITY tff IS

PORT (

std_logic;

t, clk : IN

q

: BUFFER std_logic

);

END tff;

ARCHITECTURE tff_arq OF tff IS

BEGIN

PROCESS (clk)

BEGIN

IF (clk EVENT AND clk=1) THEN

IF (t=1) THEN

q<=NOT (q);

END IF;

END IF;

END PROCESS;

END tff_arq;

3.4.3.

Registro de 8 bits con reset asncrono y seal de carga

La descripcin de un registro es anloga a la de un flip-flop, pero definiendo seales como

vectores de la forma std_logic_vector(n-1 DOWNTO 0)). Con el reset asncrono introducimos

un valor inicial deseado, que no tiene por qu ser los 8 bits a 0 lgico. Este circuito captura la

seal de entrada de 8 bits cuando se produce el flanco activo del reloj y la seal de carga est

a 1 lgico.

registro[7:0]

data[7:0]

Registro

de 8 bits

carga

clk

reset

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

ENTITY registro8 IS

PORT (

carga, clk, reset : IN

: IN

data

: OUT

registro

);

END registro8;

std_logic;

std_logic_vector(7 DOWNTO 0);

std_logic_vector(7 DOWNTO 0)

ARCHITECTURE registro8_arq OF registro8 IS

BEGIN

PROCESS (clk,reset)

BEGIN

IF (reset=1) THEN

registro<="00000000";

registro<= (OTHERS=>0)

ELSIF (clk EVENT AND clk=1) THEN

IF (carga=1) THEN

registro<=data;

END IF;

END IF;

END PROCESS;

END registro8_arq;

En la sentencia de asignacin del reset se presenta -como comentario- otra forma de poner todos los bits del registro a un mismo valor. La palabra reservada OTHERS implica que

todos los bits del registro se pondrn al valor especificado independientemente del tamao del

registro. En realidad esta opcin es ms verstil y permite asignar a ciertos bits un valor y al

resto otro. El siguiente ejemplo fija los bits ms y menos significativos a 1, y el resto a 0:

registro <= (7=>1, 0=>1, OTHERS=>0);

registro <= "10000001"

3.4 Descripcin de circuitos secuenciales

73

Registro de 8 bits con reset asncrono, seal de carga y salida en alta impedancia

Sobre el registro definido anteriormente, introduciremos una nueva funcionalidad: salidas en alta impedancia. Para que la herramienta de sntesis traduzca a puertas el cdigo

VHDL deber contar con elementos de librera con salidas en alta impedancia, lo que es habitual en los dispositivos programables de baja capacidad. La nica precaucin a tener en

cuenta es que ciertas pales tiene un pin comn de habilitacin de salida en alta impedancia

que es activo a nivel bajo. Por ejemplo sera imposible sintentizar en una PAL16R4 o PAL16R8

salidas en alta impedancia gobernadas por una seal activa a nivel alto.

Para seleccionar entre el estado normal o de alta impedancia de una salida, el registro

debe poseer una entrada adicional, que es la entrada oen (output-enable activa a nivel bajo).

En el siguiente ejemplo, cuando dicha seal est a 0 habilita la salida normal del registro,

pero cuando est a 1 deja la salida en alta impedancia.

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

oen

data[7:0]

carga

clk

Registro

de 8 bits

reset

registro_aux[7:0]

registro[7:0]

ENTITY registro8 IS

PORT (

carga, clk, reset, oen : IN

: IN

data

: OUT

registro

);

END registro8;

std_logic;

std_logic_vector(7 DOWNTO 0);

std_logic_vector(7 DOWNTO 0)

ARCHITECTURE registro8_arq OF registro8 IS

SIGNAL registro_aux: std_logic_vector(7 DOWNTO 0);

BEGIN

registro<= registro_aux WHEN (oen=0) ELSE "ZZZZZZZZ";

PROCESS (clk,reset)

BEGIN

IF (reset=1) THEN

registro_aux<=(OTHERS=>0);

ELSIF (clk EVENT AND clk=1) THEN

IF (carga=1) THEN

registro_aux<=data;

END IF;

END IF;

END PROCESS;

END registro8_arq;

El cuerpo de la arquitectura es un ejemplo de dos procesos que se interpretan de manera

concurrente. Este segundo proceso es una asignacin concurrente condicional que sirve para

definir las salida normal o en alta impedancia. La seal oen es el control de la salida en alta

impedancia y registro_aux se ha definido como una seal interna de la arquitectura para

apoyarnos en ella. Cuando oen es 1 utilizamos la asignacin registro<="ZZZZZZZZ", donde

el valor Z se entiende como alta impedancia y se encuentra definido en el paquete estndar

std_logic_1164.

Respecto al ejemplo anterior, la seal registro contina en la lista de puertos. La herramienta de sntesis incluir bferes tri-estado a la salida.

74

Lenguaje VHDL de Descripcin Hardware

Registro de 8 bits con reset asncrono, seal de carga, salida en alta impedancia y carga desde la propia salida

Si se desea que la carga paralelo se efecte desde la propia seal de salida registro en

lugar de hacerlo desde la entrada data, habra que declarar la primera de ellas como INOUT

y omitir la segunda.

oen

Registro

de 8 bits

carga

clk

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

registro[7:0]

registro_aux[7:0]

reset

La seal registro[7:0] es bidireccional. A la hora de darle estmulos (valores) para la simulacin se

presentan dos casos:

Acta de salida, oen=0: En el fichero de estmulos hay que asignarle el valor de alta impedancia Z

para que el simulador entienda que funciona en esta

direccin. El valor que se mostrar en pantalla para la

seal registro no ser Z (el estmulo dado) sino el contenido de los 8 biestables que constituyen el registro.

Acta de entrada, oen=1: En el fichero de estmulos

hay que asignarle cualquier valor distinto de alta impedancia Z. En este diseo se presentan dos opciones:

(a) No importa, carga=0: El valor de la seal registro, actuando como entrada, no importa ya que no se

va a cargar en los biestables. Se le asigna el valor -;

y (b) Valor determinado, carga=1: El valor asignado a

la seal registro se cargar en los biestables cuando se

produzca un flanco activo (de subida) del reloj.

3.4.4.

ENTITY registro8 IS

PORT (

std_logic;

carga, clk, reset, oen : IN

: INOUT std_logic_vector(7 DOWNTO 0)

registro

);

END registro8;

ARCHITECTURE registro8_arq OF registro8 IS

SIGNAL registro_aux: std_logic_vector(7 DOWNTO 0);

BEGIN

registro<= registro_aux WHEN (oen=0) ELSE (OTHERS=>Z);

PROCESS (clk,reset)

BEGIN

IF (reset=1) THEN

registro_aux<=(OTHERS=>0);

ELSIF (clk EVENT AND clk=1) THEN

IF (carga=1) THEN

registro_aux<=registro;

END IF;

END IF;

END PROCESS;

END registro8_arq;

Registro de desplazamiento de 8 bits con reset asncrono

El listado presentado a continuacin describe un regitro de desplazamiento con carga

por el bit ms significativo y desplazamiento a la derecha.

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

dato

ENTITY desplaza8 IS

PORT (

std_logic;

dato, clk, reset : IN

: BUFFER std_logic_vector(7 DOWNTO 0)

salida

);

END desplaza8;

7

6

5

4

3

clk

reset

2

1

0

salida[7:0]

ARCHITECTURE desplaza8_arq OF desplaza8 IS

BEGIN

PROCESS (clk,reset)

BEGIN

IF (reset=1) THEN

salida<="00000000";

ELSIF (clk EVENT AND clk=1) THEN

salida(6 DOWNTO 0) <= salida(7 DOWNTO 1);

salida(7) <= dato;

END IF;

END PROCESS;

END desplaza8_arq;

3.5 Diseo de mquinas de estado

75

3.4.5. Contador de 8 bits con reset asncrono, seal de carga y

habilitacin

El contador de 8 bits que se presenta tendr una entrada de reset asncrono, una seal

de carga paralelo y una seal de habilitacin que permite la cuenta cuando est activa y se

recibe el flanco activo del reloj.

La descripcin requiere del operador suma por lo que es necesaria la librera std_logic_unsigned.

Algunos entornos de programacin requieren tambin la librera std_logic_arith. A continuacin se muestra un esquema del circuito y su cdigo en VHDL.

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

data[7:0]

habilita

carga

clk

reset

cuenta[7:0]

Contador

de 8 bits

ENTITY contador8 IS

PORT (

std_logic;

carga, clk, reset, habilita : IN

: IN

std_logic_vector(7 DOWNTO 0);

data

: BUFFER std_logic_vector(7 DOWNTO 0)

cuenta

);

END contador8;

ARCHITECTURE contador8_arq OF contador8 IS

BEGIN

PROCESS (clk,reset)

BEGIN

IF (reset=1) THEN

cuenta<= (OTHERS=>0);

ELSIF (clk EVENT AND clk=1) THEN

IF (carga=1) THEN

cuenta<=data;

ELSIF (habilita=1) THEN

cuenta<=cuenta+1;

END IF;

END IF;

END PROCESS;

END contador8_arq;

3.5. Diseo de mquinas de estado

El diseo de mquinas de estado se puede realizar de una forma muy simple en VHDL,

y constituye un claro ejemplo de la potencia de los lenguajes de descripcin hardware frente a

los mtodos tradicionales de diseo.

La metodologa tradicional comienza por construir un diagrama de estados o diagrama

de bolas, de la que se deriva una tabla de estados. Sobre esta tabla se pueden agrupar estados

equivalentes, si se da el caso. A continuacin se asignan los estados y se pasa a una tabla de

transicin de estados de la que se obtienen las ecuaciones lgicas de los estados siguientes y

de las salidas segn el tipo de biestable elegido para la implementacin de los estados.

Se trata de un mtodo algortmico y, por tanto, susceptible de ser realizado por una herramienta software que libere del mismo al diseador. Esto es precisamente lo que se consigue

en VHDL y otros lenguajes HDL. El cdigo VHDL describe la tabla de estados de partida o

el diagrama de bolas, y es la herramienta de sntesis quien lleva a cabo todo el proceso de

resolucin e implementacin de puertas lgicas y biestables.

En general, la mquinas de estado se clasifican como mquinas de Moore y mquinas de

Mealy. Las primeras se caracterizan porque las salidas dependen nicamente del estado, en

tanto que en las segundas dependen del estado y las entradas. En lo que sigue nos centraremos

en las mquinas de Moore. La descripcin de mquinas de Mealy nicamente se diferencia en

la forma de expresar las seales de salida.

76

Lenguaje VHDL de Descripcin Hardware

En VHDL no es necesario resolver ninguna tabla de estados. Las transiciones de estados

se pueden expresar con una estructura condicional del tipo IF-THEN-ELSE , lo que es ms

habitual, con una estructura CASE-WHEN. Ambas deben ser utilizadas en un proceso. El

diagrama de bloques resultante para los diseos que se realicen, basados en mquinas de

Moore, se muestra en la figura 3.4.

Entradas

Biestables

Lgica

combinacional

estado_siguiente

Case ... When

clk'EVENT

and clk='1'

Lgica

combinacional

Salidas

Case ... When

estado_actual

Figura 3.4: Estructura genrica de resolucin de mquinas de estado

Los estados se definen por una enumeracin que agrupa a todos los estados, y se declaran dos seales segn ese tipo: una que corresponde al estado actual y otra corresponde al

estado siguiente al que hay que transicionar.

TYPE estado IS (reposo,decide,escribe,lee);

SIGNAL estado_actual, estado_siguiente: estado;

Aunque existen diversos estilos para describir mquinas de estado, nos centraremos

nicamente en uno de ellos, basado en la utilizacin de dos procesos:

Proceso combinacional. Describe los dos bloques combinacionales de la mquina de estados. Suele utilizar la sentencia condicional CASE-WHEN.

Bloque combinacional de las entradas: Lgica combinacional que va desde las entradas del circuito -declaradas en la entidad- hasta las entradas de los biestables

que almacenan el estado.

Bloque combinacional de las salidas: Lgica combinacional que va desde las salidas

de los biestables hasta las salidas del circuito -declaradas en la entidad-.

Proceso secuencial. Describe las transiciones sncronas de estados con el flanco de reloj.

Este bloque es el nico que recibe las entradas de reset y reloj.

3.5.1.

Ejemplo

Como ejemplo, realizaremos una mquina de Moore consistente en el control de la barrera de un paso a nivel -una sola salida-. Se supondr que el tren va en un nico sentido y que

nunca da marcha atrs. Las entradas son el sensor que est antes de la barrera (sensor(0))

y el sensor ubicado despus de la barrera (sensor(1)). La salida del sistema estar a 0 en el

estado de reposo (barrera abierta) y a 1 en el resto de estados (barrera cerrada). El diagrama

de bolas de la mquina de Moore, correspondiente a este sistema, presenta una bifurcacin

debido a que puede darse el caso de que pase un tren largo que pise ambos sensores simultneamente y el caso de que pase un tren corto cuya longitud sea menor a la distancia entre

ambos sensores. En este caso habr un estado en el que las entradas valen 00 (como en reposo)

pero el tren est entre ambos sensores sin pisarlos.

3.5 Diseo de mquinas de estado

La descripcin de cada uno de los

estados es la siguiente:

reposo. No ha llegado ningn tren

todava. Barrera abierta (salida).

pisa_1. El tren est pisando el primer sensor. Barrera cerrada.

pisa_1_2. El tren es largo y est

pisando los dos sensores. Barrera

cerrada.

enmedio. El tren es corto. Ha dejado de pisar el primer sensor pero

no ha llegado al segundo. No est

activo ninguno de los dos sensores.

Barrera cerrada.

pisa_2. El tren est marchndose. Pisa el segundo sensor. Barrera

cerrada.

sensores = 00

reposo

Entradas

barrera=0

Salida

Estado

sensores = 01

sensores = 01

pisa_1

barrera=1

sensores = 00

sensores = 11

enmedio

pisa_1_2

barrera=1

barrera=1

sensores = 10

sensores = 00

sensores = 11

sensores = 10

Pisa_2

barrera=1

77

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

ENTITY tren IS

PORT (

clk, reset : IN std_logic;

sensores : IN std_logic_vector(2 DOWNTO 1);

barrera : OUT std_logic;

);

END tren;

ARCHITECTURE tren_arq OF tren IS

TYPE estado IS (reposo, pisa_1, pisa_1_2, enmedio, pisa_2);

SIGNAL estado_actual, estado_siguiente: estado;

BEGIN

secu: PROCESS (clk,reset)

BEGIN

IF (reset=1) THEN

estado_actual<=reposo;

ELSIF (clk EVENT AND clk=1) THEN

estado_actual <= estado_siguiente;

END IF;

END PROCESS secu;

comb: PROCESS (estado_actual, sensores)

BEGIN

CASE estado_actual IS

WHEN reposo =>

barrera <= 0;

Barrera abierta (salida)

IF (sensores="01") THEN

estado_siguiente<=pisa_1;

ELSE

estado_siguiente <= reposo;

END IF;

WHEN pisa_1 =>

barrera <= 1;

Barrera cerrada (salida)

IF (sensores="00") THEN

estado_siguiente<=enmedio;

ELSIF (sensores="10") THEN

estado_siguiente <= pisa_1_2;

ELSE

estado_siguiente <= pisa_1;

END IF;

sensores = 10

El proceso secuencial (secu) tiene

en su lista sensible la seal de reset y

el reloj. Si no acta el reset asncrono

y ocurre un flanco de reloj, se asigna

el estado actual. El posible cambio del

estado actual activa a su vez el proceso

combinacional (est en su lista sensible)

para determinar el estado siguiente y las

salidas. El reset asncrono debe utilizarse

cuando el dispositivo sobre el que se va

a implementar el circuito dispone de

biestables con reset asncrono.

En la lista sensible del proceso combinacional (comb) figuran las

entradas del sistema y el estado actual,

que permiten ir preparando el estado

siguiente. Tambin en este proceso se

asignan las salidas, que, en el caso

de una mquina de Moore, dependen

exclusivamente del estado.

WHEN pisa_1_2 =>

barrera <= 1;

Barrera cerrada (salida)

IF (sensores="10") THEN

estado_siguiente<=pisa_2;

tren saliendo

ELSE

estado_siguiente <= pisa_1_2;

END IF;

WHEN enmedio =>

barrera <= 1;

Barrera cerrada (salida)

IF (sensores="10") THEN

estado_siguiente<=pisa_2;

tren saliendo

ELSE

estado_siguiente <= enmedio;

END IF;

WHEN pisa_2 =>

barrera <= 1;

Barrera cerrada (salida)

IF (sensores="00") THEN

estado_siguiente<=reposo;

ELSE

estado_siguiente <= pisa_2;

END IF;

WHEN OTHERS =>

estado_siguiente<= reposo;

END PROCESS comb;

END tren_arq;

78

Lenguaje VHDL de Descripcin Hardware

El estado se encuentra codificado en los biestables, siendo necesaria una lgica combinacional para determinar el estado siguiente y para decodificar el estado y obtener las salidas.

La figura 3.5 muestra el resultado genrico de la implementacin de una mquina de Moore.

Lgica combinacional:

process comb

Lgica secuencial:

process secu

D

Lgica combinacional:

process comb

Entradas

salida1

estado_actual

estado_siguiente

salida2

estado_actual

clk

reset

Figura 3.5: Esquema genrico de implementacin en puertas de una mquinas de

Moore

Existen otros estilos de diseo de mquinas de estados y otras mtodos para codificar

los estados, para lo que se requiere de una codificacin diferente en VHDL. En obras ms

avanzadas sobre VHDL es posible profundizar en este y otros aspectos.

3.6.

Fichero de estmulos

Una vez realizado el diseo de un circuito en VHDL el siguiente paso consiste en la

simulacin del mismo. Se necesitar otro fichero VHDL que contenga los estmulos y que

se conoce con el nombre de banco de pruebas (test bench). Los estmulos describen como las

entradas del diseo cambian en el tiempo. El banco de pruebas permite comprobar si la salida

obtenida por el modelo diseado es la deseada o no; dando el correspondiente aviso de error.

La sintaxis del fichero de estmulos es idntica a la de cualquier fichero escrito en lenguaje

VHDL. Consta, por tanto, de tres partes diferenciadas:

Libreras.

Entidad. No tiene entradas ni salidas en su caso ms simple. Su nombre no puede coincidir con el nombre de la entidad que describe el circuito. Es habitual llamarla test o top.

El nombre de esta entidad es la informacin que hay que darle al entorno de trabajo

para realizar la simulacin.

Arquitectura. Contiene un nico componente correspondiente a la entidad a simular.

Tambin tiene seales internas correspondientes a las entradas y salidas del mismo.

Estas seales se pasan como parmetros al componente cuando se instancia (se crea).

De esta forma al darle valores a las seales internas de la arquitectura -accesibles por

3.6 Fichero de estmulos

79

sta- conectadas a las entradas del componente, se obtiene la respuesta de ste de forma

visible en las seales de la arquitectura conectadas a la salida del componente. Normalmente suelen llamarse igual las seales de la arquitectura y las del componente para

facilitar la legibilidad del diseo. Adems suele tener dos procesos: (a) uno para definir

el reloj -en el caso de que el circuito sea sncrono-, y (b) otro para indicar la evolucin

de resto de entradas. Los procesos presentes en la arquitectura utilizan la instruccin

WAIT y, por razones que se estudiarn en cursos superiores, no pueden tener lista sensible.

Para concretar estas ideas se presenta el fichero del diseo y de la simulacin de un

circuito muy simple: una puerta AND de 2 entradas. En la izquierda se muestra el contenido

del fichero and2.vhd que describe la lgica del circuito y en la derecha tenemos el contenido

del fichero de estmulos que lo hemos llamado and2_tb.vhd. El circuito es puramente combinacional por lo que no se requiere un proceso que genere seal de reloj.

Fichero: and2_tb.vhd

Fichero: and2.vhd

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

LIBRARY ieee;

ieee.std_logic_1164.ALL;

USE

ENTITY and2 IS

PORT (

a, b : IN

s

: OUT

);

END and2;

ENTITY test IS

END test;

std_logic

ARCHITECTURE and2_arq OF and2 IS

BEGIN

s <= a AND b;

END and2_arq;

no tiene entradas ni salidas

ARCHITECTURE estimulos OF test IS

COMPONENT and2

std_logic;

PORT( a, b : IN

s

: OUT std_logic);

END COMPONENT;

SIGNAL a, b, s : std_logic

Seales internas

BEGIN

Se instancia el componente llamado puerta del tipo and2

La descripcin del componente est en el fichero and2.vhd

puerta: and2 PORT MAP(a,b,s);

PROCESS

Sin lista sensible (por la sentencia WAIT)

BEGIN

a<=0;

b<=0;

WAIT FOR 100 ns;

b<=1;

WAIT FOR 50 ns;

a<=1;

WAIT FOR 200 ns;

ASSERT (s=1) REPORT "La salida no es 1";

b<=0;

WAIT FOR 50 ns;

a<=0;

WAIT;

Espera infinita

END PROCESS;

END estimulos;

El resultado de la simulacin de la AND2 con los estmulos del fichero and2_tb.vhd se

muestra a continuacin:

Seales

a

b

s

50ns

100ns

150ns

200ns

250ns

300ns

350ns

400ns

450ns

500ns

Figura 3.6: Resultado de la simulacin del diseo de la AND de 2 entradas.

Vous aimerez peut-être aussi

- Lista de Cotejo DigitacionDocument8 pagesLista de Cotejo DigitacionArainga Blas TomasPas encore d'évaluation

- Hoja de Vida para Mantenimiento de PCDocument2 pagesHoja de Vida para Mantenimiento de PCjorge81% (21)

- Lab OratoriosDocument260 pagesLab OratoriosRodrigo RamirezPas encore d'évaluation

- Matriz de CongruenciaDocument3 pagesMatriz de CongruenciaNelson Rubio100% (1)

- Historia Computacion Presentacion Power PointDocument21 pagesHistoria Computacion Presentacion Power PointPaola Melo67% (3)

- Manual de InformaticaDocument17 pagesManual de InformaticaDenis Rios RamosPas encore d'évaluation

- LCD LM016Document7 pagesLCD LM016María MarmagoPas encore d'évaluation

- 2007 SeptiembreDocument4 pages2007 SeptiembreMaría MarmagoPas encore d'évaluation

- FiltroDocument5 pagesFiltroMaría MarmagoPas encore d'évaluation

- Expended or ADocument7 pagesExpended or AMaría MarmagoPas encore d'évaluation

- Exámenes 2009-2010Document35 pagesExámenes 2009-2010María MarmagoPas encore d'évaluation

- Datos y CifrasDocument176 pagesDatos y CifrasMaría MarmagoPas encore d'évaluation

- Generalidades Pic ImprDocument14 pagesGeneralidades Pic ImprMaría MarmagoPas encore d'évaluation

- DisplaysDocument6 pagesDisplaysMaría MarmagoPas encore d'évaluation

- Conv AdDocument8 pagesConv AdMaría MarmagoPas encore d'évaluation

- CursocDocument18 pagesCursocMaría MarmagoPas encore d'évaluation

- Tema 1Document23 pagesTema 1María MarmagoPas encore d'évaluation

- Ejercicios C1-2Document5 pagesEjercicios C1-2María MarmagoPas encore d'évaluation

- Datos y CifrasDocument176 pagesDatos y CifrasMaría MarmagoPas encore d'évaluation

- T 02 SistemasDocument19 pagesT 02 SistemasMaría MarmagoPas encore d'évaluation

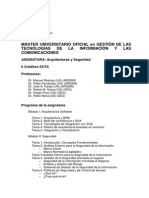

- Programa Asignatura GovTICDocument1 pagePrograma Asignatura GovTICMaría MarmagoPas encore d'évaluation

- 2006 SeptiembreDocument2 pages2006 SeptiembreMaría MarmagoPas encore d'évaluation

- BodeDocument3 pagesBodeMaría MarmagoPas encore d'évaluation

- Boletín Tema 10 Parte 2Document3 pagesBoletín Tema 10 Parte 2María MarmagoPas encore d'évaluation

- Tema TrazadoBodeDocument31 pagesTema TrazadoBodeCora LailopPas encore d'évaluation

- 2005 SeptiembreDocument4 pages2005 SeptiembreMaría MarmagoPas encore d'évaluation

- Ejercicios C1-2Document5 pagesEjercicios C1-2María MarmagoPas encore d'évaluation

- T6 3Document20 pagesT6 3Mauro JimenezPas encore d'évaluation

- DiagramadeflujoDocument2 pagesDiagramadeflujoMaría MarmagoPas encore d'évaluation

- Programa Asignatura GovTICDocument1 pagePrograma Asignatura GovTICMaría MarmagoPas encore d'évaluation

- Programa Asignatura IyPDocument2 pagesPrograma Asignatura IyPMaría MarmagoPas encore d'évaluation

- Programa de PODocument1 pagePrograma de POMaría MarmagoPas encore d'évaluation

- Programa Asignatura ARQSEGDocument2 pagesPrograma Asignatura ARQSEGMaría MarmagoPas encore d'évaluation

- Programa Asignatura HDPTICDocument2 pagesPrograma Asignatura HDPTICMaría MarmagoPas encore d'évaluation

- Ejemplo de Auditoria A Un LaboratorioDocument10 pagesEjemplo de Auditoria A Un LaboratorioGabrielita Lugo Mi CeroochoPas encore d'évaluation

- Cable 6 UtpDocument2 pagesCable 6 UtpEdwin OrtegaPas encore d'évaluation

- Evaluación de 10 preguntas sobre conceptos básicos de Tecnologías de la Información y ComunicaciónDocument12 pagesEvaluación de 10 preguntas sobre conceptos básicos de Tecnologías de la Información y Comunicacióncristian Garcia GámezPas encore d'évaluation

- Guia Instalación GNURadioDocument4 pagesGuia Instalación GNURadioMiguel Angel Sarmiento AcostaPas encore d'évaluation

- Manual de Restauración PDFDocument4 pagesManual de Restauración PDFoooPas encore d'évaluation

- Guia Configuraciones Basicas Router Observa Aw4062Document30 pagesGuia Configuraciones Basicas Router Observa Aw4062Cesar DiazPas encore d'évaluation

- Blog TRABAJO FINALDocument3 pagesBlog TRABAJO FINALjeferbri95Pas encore d'évaluation

- Ejercicios Resueltos Direccionamiento Ip - PDFDocument16 pagesEjercicios Resueltos Direccionamiento Ip - PDFLaurimarPas encore d'évaluation

- Politica de Uso de Medios de Almacenamiento DigitalDocument2 pagesPolitica de Uso de Medios de Almacenamiento DigitalLuis Alberto Murcia G.100% (2)

- Practica 2 - Circuitos CombinacionalesDocument14 pagesPractica 2 - Circuitos CombinacionalesMario Poveda NavaroPas encore d'évaluation

- Manual MultiCAS CCcam Rev1.2Document15 pagesManual MultiCAS CCcam Rev1.2Oscar Cardeñosa RomeroPas encore d'évaluation

- Monografia SlideshareDocument8 pagesMonografia SlideshareLuisamariaJimenezCamachoPas encore d'évaluation

- Unidad Educativa Particular 8voDocument2 pagesUnidad Educativa Particular 8voGiovanny UtrerasPas encore d'évaluation

- Foundation FieldbusDocument4 pagesFoundation FieldbusJonnathan Paul Valdez SolisPas encore d'évaluation

- El Equipo fotografico-SENA-Daniela Si.Document4 pagesEl Equipo fotografico-SENA-Daniela Si.Daniela LozanoPas encore d'évaluation

- Lab 02 Lenguajes de ProgramaciónDocument6 pagesLab 02 Lenguajes de ProgramaciónVeyhan HanccoPas encore d'évaluation

- Ept-Instructivo para Diseño GráficoDocument19 pagesEpt-Instructivo para Diseño GráficoLuis Ñavincopa CarhuamacaPas encore d'évaluation

- SRD UT7 AsteriskDocument5 pagesSRD UT7 AsteriskPepe CachimbaPas encore d'évaluation

- Ecosistema Digital 1Document26 pagesEcosistema Digital 1ArturoPas encore d'évaluation

- Características hardware ALU memoria entrada salidaDocument3 pagesCaracterísticas hardware ALU memoria entrada salidaEduardo Rodriguez100% (2)

- Leccion Evaluativa3Document4 pagesLeccion Evaluativa3Yuly Marcela Tapias SuarezPas encore d'évaluation

- Acceso a internet de banda ancha para escuelas rurales de Malawi a través de redes over-the-air que utilizan el espectro de TV no utilizadoDocument3 pagesAcceso a internet de banda ancha para escuelas rurales de Malawi a través de redes over-the-air que utilizan el espectro de TV no utilizadoElias MadridPas encore d'évaluation

- Sistemas de Información VerdesDocument3 pagesSistemas de Información VerdesefrenqrPas encore d'évaluation

- Electronica Digital - Página Web de Electronicadigital-ItcDocument18 pagesElectronica Digital - Página Web de Electronicadigital-ItcLeonardo MisaelPas encore d'évaluation