Académique Documents

Professionnel Documents

Culture Documents

ApostilaLabEletr2 PDF

Transféré par

Anonymous zzfx7mz3Description originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

ApostilaLabEletr2 PDF

Transféré par

Anonymous zzfx7mz3Droits d'auteur :

Formats disponibles

UNIVERSIDADE ESTADUAL PAULISTA JLIO DE MESQUITA FILHO

Campus Universitrio de Bauru

FACULDADE DE ENGENHARIA

www.feb.unesp.br

Prof. Dr. Alceu Ferreira Alves

2016

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

LABORATRIO DE ELETRNICA II

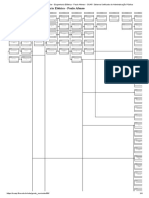

PROGRAMAO DE AULAS 1 SEMESTRE 2016

Horrios das Aulas

Turma 2318EE11

Turma 2318EE12

Turma 2318EE13

Turma 2318EE14

Teras-feiras

Teras-feiras

Teras-feiras

Segundas-feiras

14h s 16h

14h s 16h

16h s 18h

14h s 16h

Lab. 33

Lab. 33

Lab. 33

Lab. 33

Prof. Andreoli

Prof. Alceu

Prof. Alceu

Prof. Alfredo

sem

Turmas

11,12,13

Turma

14

01

15/03

14/03

Apresentao do Programa, Critrios de Avaliao, Informaes

Gerais (esta aula no ser computada para efeito de avaliao)

02

22/03

21/03

Laboratrio 01 Amplificador Classe A

03

29/03

28/03

Laboratrio 02 Amplificador Classe B Parte I

04

05/04

04/04

Laboratrio 03 Amplificador Classe B Parte II

05

12/04

11/04

Semana da Engenharia no haver aulas de Laboratrio

05

19/04

18/04

Laboratrio 04 Amplificador Classe C

06

26/04

25/04

Laboratrio 05 Efeitos de Frequncia

07

03/05

02/05

Laboratrio 06 Resposta em Frequncia de Amplificadores

08

10/05

09/05

1 Prova (PL1) frequncia e matria referentes s aulas

ministradas nas semanas de 02 a 07 (Labs. 01 a 06)

09

17/05

16/05

Laboratrio 07 Amplificador Diferencial

10

24/05

23/05

Laboratrio 08 Circ. Inversor e Circ. No-Inversor de Tenso

com Amp-Op

11

31/05

30/05

Laboratrio 09 Circuito Somador de Tenso

12

07/06

06/06

Laboratrio 10 Filtros Ativos

13

14/06

13/06

Laboratrio 11 Circuitos No Lineares usando Amp-Op

14

21/06

20/06

Laboratrio 12 Circuitos Comparadores

15

28/06

27/06

2 Prova (PL2) frequncia e matria referentes s aulas

ministradas nas semanas de 09 a 14 (Labs. 07 a 12)

16

05/07

04/07

Prtica Substitutiva (*)

17

12/07

11/07

3 Prova de Laboratrio (PL3) toda a matria

(*)

19/07

19/07

Atividades Programadas

Aula de Recuperao Lab. 33 data e horrio a combinar

Prova de Recuperao Lab. 33 horrio a combinar

(*) Aos alunos que perderam alguma prtica sem justificativa.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina i

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

Critrio de Avaliao:

1) No h relatrios semanais;

2) Haver 02 (duas) provas (PL1 e PL2), prticas, individuais, obrigatrias, constando tambm de

questes tericas, nas datas especificadas na programao.

3) As notas das provas PL1 e PL2 sero ponderadas pela frequncia do aluno nas aulas de laboratrio

que esto sendo avaliadas, dando origem s notas P1 e P2:

P1 = a * PL1 e P2 = b * PL2 , sendo a e b os pesos respectivos das notas de provas PL1 e PL2,

calculados pela expresso:

n de presenas

n de aulas dadas

Caso MP = (P1 + P2) / 2 seja >= 5,0, esta passa a ser a Mdia Final (MF) e o aluno est aprovado por

nota;

Caso MP < 5,0

a prova P3 obrigatria, englobando toda a matria lecionada no semestre, e a mdia

final (MF) recalculada como segue:

MF = (P1 + P2 + 2*P3) / 4

Neste caso, a mdia final dever ser igual ou superior a 5,0 para aprovao.

4) Controle de Frequncia: haver chamada todas as aulas. Para aprovao: frequncia >= 70%

Aos alunos reprovados, haver uma aula de recuperao e uma prova de recuperao, cuja nota mnima

para aprovao 5,0 (cinco inteiros).

INSTRUES GERAIS

Aulas prticas com 01 ou 02 alunos por bancada; os alunos podem e devem discutir os procedimentos

e resultados com os colegas e o professor, mas preciso entender os objetivos da experincia e tirar

suas concluses individualmente;

Horrio de incio das aulas ser rigorosamente cumprido;

imprescindvel o uso da apostila (edio 2016, sem resultados anotados) para realizao dos

experimentos, sem a qual o aluno poder ser impedido de fazer a prtica;

O atraso mximo permitido aos alunos ser 5 minutos; aps esta tolerncia, o aluno poder entrar na

sala e fazer a prtica, mas ficar com registro de falta na aula, podendo substituir at uma aula sem

justificativa;

Ao terminar de fazer a prtica e colher seus dados experimentais, o aluno poder ir embora, aps

organizar todo o material utilizado;

O descumprimento das Normas de Utilizao ser julgado pelo professor, que poder, a seu critrio,

aplicar um redutor no coeficiente de presena na aula de 0 a 100% (marcar falta), o que alterar a

ponderao do clculo da mdia de laboratrio.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina ii

unesp

DEPARTAMENTO DE ENGENHARIA ELTRICA

NORMAS DE UTILIZAO DO LABORATRIO DIDTICO PELOS ALUNOS DE ELETRNICA II

1) Cada aluno dever informar ao professor da disciplina qual ser a sua bancada de trabalho durante

todo o semestre e ficar responsvel pela conservao da mesma (mesa, equipamentos, bancos,

etc.);

2) Ao iniciar a aula, o aluno dever informar ao professor qualquer problema verificado com sua

bancada;

3) Ao terminar a aula, o aluno dever deixar sua bancada em perfeita ordem, observando:

a) Os bancos devero ser colocados sob as mesas;

b) As mesas devero estar limpas, sem resduos de borrachas, restos de papel, copos

descartveis, etc.;

c) Os equipamentos devero estar desligados e em ordem para o aluno que for utilizar a

bancada em seguida;

4) As placas, cabos, fios, alicates e componentes eletrnicos devero ser colocados onde foram

encontrados, e os fios usados em protoboard devem ser devolvidos em ordem;

5) Defeitos constatados em componentes, cabos ou equipamentos devero ser comunicados ao

professor para que sejam tomadas providncias no sentido de se efetuar a manuteno adequada;

6) A tenses utilizadas durante as aulas so geralmente baixas, mas lembre-se que tenses acima de

50V podem matar; portanto, preste bastante ateno no circuito que est montando e s ligue aps

ter absoluta certeza do que est fazendo.

PENSE PRIMEIRO, FAA DEPOIS !

7) No permitido aos alunos fumar, comer ou beber dentro do Laboratrio Didtico.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina iii

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

AMPLIFICADOR CLASSE A

1.0 OBJETIVOS

Aps completar estas atividades de laboratrio, voc dever ser capaz de:

1. Medir as tenses de polarizao em um amplificador emissor-comum e comparar os valores prticos

medidos com os valores tericos esperados.

2. Observar o funcionamento do amplificador e medir a mxima tenso de sada pico-a-pico no ceifada

para o ponto quiescente no meio da reta de carga CC.

3. Recalcular a polarizao de modo que a compliance de sada seja mxima.

4. Observar novamente o funcionamento do amplificador e verificar o aumento da compliance quando o

ponto quiescente desloca-se para o meio da reta de carga CA.

2.0 DISCUSSO

Os amplificadores de tenso a transistor podem ser analisados sob dois diferentes enfoques: a anlise CC

e a anlise CA; para cada um destes enfoques, possvel traar-se uma reta de carga, que representa o

funcionamento do transistor para aquele circuito especfico. Nas anlises realizadas at o momento,

utilizava-se apenas a reta de carga CC, pois os amplificadores analisados sempre funcionavam com

pequenos sinais, excursionando sobre uma pequena regio desta reta. Aps vrios estgios de ganho de

tenso, a oscilao do sinal utiliza toda a reta de carga e a anlise sob o enfoque CC j no mais

representa o comportamento real do amplificador, pois deixa de considerar as impedncias de fonte e

carga. Nesta situao, faz-se necessria a anlise CA, considerando-se a fonte e a carga, para

representar exatamente o comportamento do amplificador.

Com a reta de carga CA, torna-se possvel calcular a mxima tenso de sada pico-a-pico no-ceifada do

amplificador (compliance). E, considerando-se estes parmetros CA, possvel redefinir a melhor

localizao do ponto quiescente, recalculando a polarizao do transistor de modo a obter-se a mxima

compliance.

3.0 PROCEDIMENTO

OBS.: Recomenda-se aos senhores alunos que realizem os clculos necessrios para esta experincia

antecipamente e tragam os resultados j computados, para facilitar a implementao dos circuitos e

aproveitar melhor o tempo de aula.

POLARIZAO NO MEIO DA RETA DE CARGA CC

1. Considere o amplificador EC cujo esquema encontra-se na figura 1 e calcule as tenses e correntes CC

de polarizao constantes na tabela da figura 2. Anote os resultados obtidos.

2. Insira a placa EB-98 no sistema. No necessrio inicializar o sistema e nem ligar a fonte principal da

MB-U.

3. Monte o circuito do amplificador esquematizado na figura 1 observando os seguintes cuidados:

a) Seja organizado na sua montagem, para facilitar eventuais correes no circuito montado;

b) Evite entortar os terminais dos componentes, pois estes so frgeis podem se quebrar;

c) Ligue a alimentao do circuito somente quando tiver terminado a montagem e conferido todas

as ligaes.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 1

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

+12V

2K2

+ 270

4K7

4,7F

+

+

TIP31

4,7F

1K

270 - vermelho, violeta, marrom

220 - vermelho, vermelho, marrom

470 - amarelo, violeta, marrom

1 k - marrom, preto, vermelho

1,2 k - marrom, vermelho, vermelho

2,2 k - vermelho, vermelho, vermelho

4,7 k - amarelo, violeta, vermelho

4,7F

470

1K2

Fig. 1 Amplificador Emissor Comum (EC)

VB [V]

Grandeza

VE [V]

IE [mA]

VC [V]

VCE [V]

VCC [V]

Valor Calculado

Valor Medido

Fig. 2 Valores Calculados e Valores Medidos de Polarizao

4. Ligue a alimentao do circuito, e utilizando-se do aparelho de medio adequado, mea e anote os

resultados prticos na tabela da figura 2.

Compare os resultados medidos com os valores calculados e tente justificar eventuais diferenas.

5. Calcule os valores necessrios para traar a reta de carga CC e localizar o ponto quiescente para este

circuito e anote-os na tabela da figura 3. Trace, na figura 4, a reta de carga CC e localize o ponto

quiescente (utilize Vce medido).

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 2

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

Grandeza

VCE(corte) [V]

IC(sat) [mA]

Reta de Carga CC

Fig. 3 Pontos da Reta de Carga CC

IC (mA)

VCE (V)

Fig. 4 Reta de Carga CC e Reta de Carga CA

6. A partir da reta de carga CC, estime o valor da mxima tenso de sada pico-a-pico sem distoro por

ceifamento que o amplificador deveria produzir. Em seguida, aplique na entrada um sinal senoidal de 1kHz

usando o cabo BNC-jacar e observe a sada. Aumente a amplitude de entrada at obter

experimentalmente a compliance.

Compliance estimada: __________________________

Compliance medida: ___________________________

Compare os dois resultados e justifique a diferena observada.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 3

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

7. Calcule os valores necessrios para traar a reta de carga CA e anote-os na tabela da figura 5. Em

seguida, trace na figura 4, a reta de carga CA. A partir das curvas traadas, tente justificar o ocorrido com

a compliance medida.

VCE(corte) [V]

Grandeza

IC(sat) [mA]

Reta de Carga CA

Fig. 5 Pontos da Reta de Carga CA

8. Calcule os novos valores de polarizao, com os componentes escolhidos para colocar o ponto de

operao prximo ao meio da reta CA. (R1=RC=1k; R2=RE=220). Preencha a tabela da figura 6 com

os novos valores calculados.

VB [V]

Grandeza

VE [V]

IE [mA]

VC [V]

VCE [V]

VCC [V]

Valor Calculado

Valor Medido

Fig. 6 Novos Valores Calculados e Medidos de Polarizao

9. Utilize a figura 7 para traar novamente a reta de carga CC e localizar o novo ponto quiescente.

10. Desligue o gerador de sinais e a alimentao CC, altere o circuito, religue a alimentao e mea os

novos valores CC do circuito alterado. Anote estes novos valores na tabela da figura 6.

IC (mA)

VCE (V)

Fig. 7 Reta de Carga CC e Reta de Carga CA (circuito alterado)

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 4

unesp

DEPARTAMENTO DE ENGENHARIA ELTRICA

11. Calcule o corte e a saturao CA nesta nova situao e anote na tabela da figura 8.

12. Trace na figura 7 a reta de carga CA.

Grandeza

VCE(corte) [V]

IC(sat) [mA]

Reta de Carga CA

Fig. 8 Pontos da Reta de Carga CA

13. Aplique na entrada um sinal senoidal de 1kHz usando o cabo BNC-jacar e observe a sada. Aumente

a amplitude de entrada at obter experimentalmente a compliance.

Compliance medida: ___________________________

Observe as retas traadas na figura 7 e conclua se o resultado experimental obtido coerente.

Houve melhora no valor da compliance? Justifique.

ATENO: APS A EXPERINCIA, ORGANIZE SUA BANCADA CONFORME AS NORMAS DE

UTILIZAO DO LABORATRIO DIDTICO PELOS ALUNOS DE ELETRNICA II

(pgina iii desta apostila). BANCADA EM DESACORDO COM AS NORMAS ACARRETAR EM

DIMINUIO DA NOTA DE LABORATRIO, CONFORME PREVISTO.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 5

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

AMPLIFICADOR CLASSE B PARTE I

1.0 OBJETIVOS

Aps completar estas atividades de laboratrio, voc dever ser capaz de:

1. Medir as tenses de polarizao em um amplificador Push-Pull e comparar os valores prticos medidos

com os valores tericos esperados.

2. Observar o funcionamento do amplificador e medir a mxima tenso de sada pico-a-pico no ceifada.

3. Verificar a distoro por cross-over em um amplificador com polarizao mal-projetada.

2.0 DISCUSSO

Operao classe B de um transistor significa que a corrente do coletor flui durante somente 180 do ciclo

CA. Isto implica que o ponto Q se situe aproximadamente no corte para as duas retas de carga, CA e CC.

A vantagem da operao classe B a menor dissipao de potncia no transistor, que resulta em maior

eficincia e menor corrente drenada da fonte.

Quando um transistor opera em classe B, ele corta um semiciclo. Para evitar a distoro resultante

necessrio o uso de dois transistores num arranjo push-pull; isto quer dizer que um transistor conduz

durante um semiciclo e o outro transistor conduz durante o outro semiciclo, sendo que ambos esto

configurados como seguidores de emissor, com ganho de tenso igual a um e forte linearizao. Deste

modo, obtm-se amplificadores classe B com baixa distoro e alta eficincia.

Arranjos push-pull so normalmente utilizados nos estgios de sada dos amplificadores de potncia, por

oferecerem baixa impedncia de sada e alta impedncia de entrada.

3.0 PROCEDIMENTO

OBS.: Recomenda-se aos senhores alunos que realizem os clculos necessrios para esta experincia

antecipamente e tragam os resultados j computados, para facilitar a implementao dos circuitos e

aproveitar melhor o tempo de aula.

POLARIZAO DO AMPLIFICADOR PUSH-PULL

1. Considere o amplificador Push-Pull cujo esquema encontra-se na figura 1 e calcule as tenses e

correntes CC de polarizao constantes na tabela da figura 2. Anote os resultados obtidos.

2. Insira a placa EB-98 no sistema (ou coloque o protoboard sobre a bandeja). No necessrio inicializar

o sistema e nem ligar a fonte principal da MB-U.

3. Monte o circuito do amplificador esquematizado na figura 1 observando os seguintes cuidados:

a) Seja organizado na sua montagem, para facilitar eventuais correes no circuito montado;

b) Evite entortar os terminais dos componentes, pois estes so frgeis podem se quebrar;

c) Ligue a alimentao do circuito somente quando tiver terminado a montagem e conferido todas

as ligaes.

4. Ligue a alimentao do circuito, e utilizando-se do aparelho de medio adequado, mea e anote os

resultados prticos na tabela da figura 2.

Compare os resultados medidos com os valores calculados e justifique eventuais diferenas.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 6

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

PS-1 = 9V

3,9K

4,7

TI

TI P 31

P

32

Q1

TIP31

680

BASE

4,7

COLETOR

Vx

EMISSOR

680

+

Q2

TIP32

4,7

1K

680 - azul, cinza, marrom

1 k - marrom, preto, vermelho

3,9 k - laranja, branco, vermelho

3,9K

Fig. 1 Amplificador Push-Pull

VCC [V]

Grandeza

VE [V]

VB1 [V]

VB2 [V]

Vx [V]

Valor Calculado

Valor Medido

Fig. 2 Valores Calculados e Valores Medidos de Polarizao

5. A partir dos resultados prticos (valores medidos), calcule as tenses pedidas na tabela da figura 3.

VCE1 [V]

VCE2 [V]

VBE1 [V]

VBE2 [V]

Fig. 3 Clculo das tenses de polarizao

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 7

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

AMPLIFICAO DE SINAL CA

6. Utilizando o gerador de sinais, aplique na entrada do circuito um sinal senoidal de 1kHz com amplitude

de 1V. Observe simultaneamente os sinais de entrada e sada e anote-os na figura 4.

CANAL 1

AC

DC

Escala vertical: _______ V/div

CANAL 2

AC

DC

Escala vertical: _______ V/div

Escala horizontal: ______ s/div

Fig. 4 Tenses de entrada e sada no amplificador classe B Push-Pull

H alguma distoro perceptvel no sinal de sada? Quanto o ganho de tenso nesta situao?

Ganho (Av) = _______________

COMPLIANCE

7. Aumente a amplitude do sinal de entrada enquanto observa simultaneamente os sinais de entrada e

sada. Verifique e anote a o valor da compliance para esta situao.

PP = _______________

O resultado encontrado o esperado?

DISTORO POR CROSS-OVER

8. Desligue a alimentao do circuito e o gerador de sinais.

9. Altere o circuito, curto-circuitando os dois resistores de 680.

10. Religue a alimentao (PS-1 = 9V). Com o voltmetro mea os novos valores de polarizao e

complete a tabela da figura 5.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 8

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

VCC [V]

Grandeza

VE [V]

VB1 [V]

VB2 [V]

Valor Medido

Fig. 5 Novos valores medidos de polarizao

11. Aplique novamente um sinal senoidal de 1kHz, ajustando a amplitude de entrada para 2V.

12. Observe simultaneamente os sinais de entrada e sada e anote-os na figura 6.

CANAL 1

AC

DC

Escala vertical: _______ V/div

CANAL 2

AC

DC

Escala vertical: _______ V/div

Escala horizontal: ______ s/div

Fig. 6 Entrada e Sada no Amplif. Push-Pull Distoro por Cross-over

Foi observada distoro por cross-over? Explique porque a alterao implementada causou este

tipo de distoro.

ATENO: APS A EXPERINCIA, ORGANIZE SUA BANCADA CONFORME AS NORMAS DE

UTILIZAO DO LABORATRIO DIDTICO PELOS ALUNOS DE ELETRNICA II

(pgina iii desta apostila). BANCADA EM DESACORDO COM AS NORMAS ACARRETAR EM

DIMINUIO DA NOTA DE LABORATRIO, CONFORME PREVISTO.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 9

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

AMPLIFICADOR CLASSE B PARTE II

1.0 OBJETIVOS

Aps completar estas atividades de laboratrio, voc dever ser capaz de:

1. Observar a corrente de coletor no amplificador Push-Pull.

2. Verificar a polarizao de base com compensao de temperatura utilizando diodos.

3. Observar o funcionamento do espelho de corrente.

2.0 DISCUSSO

Em um amplificador classe B necessrio ajustar o ponto quiescente ligeiramente acima do corte para

evitar-se a distoro por cross-over, ajustando-se a polarizao para um valor de VBE entre 0,6V e 0,7V. O

grande problema reside no fato da corrente de coletor ser muito sensvel s variaes de VBE, a qual, por

sua vez, fortemente dependente das variaes de temperatura. Quando a temperatura aumenta, a

corrente no coletor aumenta. Como a corrente no coletor aumenta, a temperatura na juno aumenta

ainda mais, alm de reduzir o valor exato de VBE. Esta situao de realimentao positiva significa que a

corrente no coletor pode disparar , causando o efeito de deriva trmica at que uma potncia excessiva

danifique o transistor.

Uma forma de evitar a deriva trmica usar diodos de compensao para produzir a tenso de

polarizao para os diodos do emissor. Se as curvas de juno dos diodos de compensao e dos diodos

de emissor casarem, aumentos de temperatura causaro diminuio nas tenses de juno e o disparo

trmico deixa de ocorrer.

3.0 PROCEDIMENTO

OBS.: Recomenda-se aos senhores alunos que realizem os clculos necessrios para esta experincia

antecipamente e tragam os resultados j computados, para facilitar a implementao dos circuitos e

aproveitar melhor o tempo de aula.

POLARIZAO DO AMPLIFICADOR PUSH-PULL

1. Considere o amplificador Push-Pull cujo esquema encontra-se na figura 1 e calcule as tenses e

correntes CC de polarizao constantes na tabela da figura 2. Anote os resultados obtidos.

2. Insira a placa EB-98 no sistema (ou coloque o protoboard sobre a bandeja). No necessrio inicializar

o sistema e nem ligar a fonte principal da MB-U.

3. Monte o circuito do amplificador esquematizado na figura 1 observando os seguintes cuidados:

a) Seja organizado na sua montagem, para facilitar eventuais correes no circuito montado;

b) Evite entortar os terminais dos componentes, pois estes so frgeis podem se quebrar;

c) Ligue a alimentao do circuito somente quando tiver terminado a montagem e conferido todas

as ligaes.

4. Ligue a alimentao do circuito, mea e anote os resultados prticos na tabela da figura 2.

OBS.: Calcular ICQ a partir de VC1 e/ou VC2. Calcular IR a partir de VB1 e/ou VB2

Compare os resultados medidos com os valores calculados e justifique eventuais diferenas.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 10

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

PS-1 = 7V

RC1

10

3,9K

4,7

Q1

TIP31

680

4,7

+

Vx

680

+

1K

Q2

TIP32

4,7

10 - marrom, preto, preto

680 - azul, cinza, marrom

1 k - marrom, preto, vermelho

3,9 k - laranja, branco, vermelho

RC2

3,9K

10

Fig. 1 Amplificador Push-Pull

VCC

Grandeza

Valor Calculado [Volt]

VE

VB1

VB2

Vx

ICQ

VC1

VC2

IR=3,9k

Valor Medido [Volt]

Fig. 2 Valores Calculados e Valores Medidos de Polarizao

5. A partir dos resultados prticos (valores medidos), calcule as tenses pedidas na tabela da figura 3.

VCE1 [V]

VCE2 [V]

VBE1 [V]

VBE2 [V]

Fig. 3 Clculo das tenses de polarizao

Nesta situao, os espelhos de corrente esto funcionando corretamente? Justifique sua resposta.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 11

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

OBSERVAO DA CORRENTE CA NO COLETOR

6. Utilizando o gerador de sinais, aplique na entrada do circuito um sinal senoidal de 1kHz com amplitude

de 3V. Observe simultaneamente o sinal de tenso de sada e a tenso sobre o resistor RC2 e anote-os na

figura 4.

CANAL 1

AC

DC

Escala vertical: _______ V/div

CANAL 2

AC

DC

Escala vertical: _______ V/div

Escala horizontal: ______ s/div

Fig. 4 Tenso e corrente na sada do amplificador classe B Push-Pull

A partir das formas de onda observadas, calcule o valor da corrente de pico no coletor do

transistor PNP. A forma de onda de corrente observada a esperada?

POLARIZAO COM DIODOS COMPENSADORES

7. Desligue a alimentao e desconecte o gerador de sinais do circuito. Altere o circuito montado

substituindo os resistores de 680 por diodos, conforme indicado na figura 5.

Vx

Fig. 5 Polarizao utilizando diodos compensadores

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 12

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

8. Considere o amplificador Push-Pull com a nova polarizao e Vcc = 10V. Recalcule as tenses e

correntes CC de polarizao e anote-as na tabela da figura 6.

VCC

Grandeza

Valor Calculado

VE

VB1

VB2

Vx

ICQ

VC1

VC2

IR=3,9k

Valor Medido

Fig. 6 Valores Calculados e Valores Medidos de Polarizao

9. Ligue a alimentao do circuito, reajuste a fonte PS-1 para 10V, mea e anote os resultados prticos na

tabela da figura 6.

10. A partir dos resultados prticos (valores medidos), calcule as tenses pedidas na tabela da figura 7.

VCE1

VCE2

VBE1

VBE2

Fig. 7 Clculo das tenses de polarizao

Compare os resultados medidos com os valores calculados e justifique eventuais diferenas.

O espelho de corrente est funcionando corretamente?

Nesta situao h o risco de deriva trmica?

ATENO: APS A EXPERINCIA, ORGANIZE SUA BANCADA CONFORME AS NORMAS DE

UTILIZAO DO LABORATRIO DIDTICO PELOS ALUNOS DE ELETRNICA II

(pgina iii desta apostila). BANCADA EM DESACORDO COM AS NORMAS ACARRETAR EM

DIMINUIO DA NOTA DE LABORATRIO, CONFORME PREVISTO.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 13

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

AMPLIFICADOR CLASSE C

1.0 OBJETIVOS

Aps completar estas atividades de laboratrio, voc dever ser capaz de:

1. Observar o funcionamento de um amplificador classe C.

2. Verificar o funcionamento do grampeador CC negativo na base.

2.0 DISCUSSO

Em um amplificador classe C, o transistor opera na regio ativa menos de 180 do ciclo CA do sinal.

Tipicamente, o ngulo de conduo muito menor do que 180 e a corrente do coletor um trem de

pulsos estreitos. Esta corrente no senoidal contm a frequncia fundamental mais as harmnicas e

obtida atravs de um circuito grampeador negativo ligado base. Um amplificador classe C sintonizado

tem um circuito tanque ressonante na sada que est em sintonia com a frequncia fundamental. Isto

produz uma tenso de sada senoidal com frequncia fr. Em um circuito multiplicador de frequncia, o

circuito tanque ressonante sintonizado em alguma frequncia harmnica superior, mltipla inteira da

frequncia fundamental da entrada.

3.0 PROCEDIMENTO

1. Antes de iniciar a montagem, mea o valor da indutncia e do fator de qualidade do indutor, anotando

estes resultados na tabela da figura 1. Utilize a ponte RLC digital disponvel com o professor.

2. Calcule os demais parmetros referentes ao amplificador classe C e complete a tabela.

L (H)

QL

fR (kHz)

XL ()

RS ()

RP ()

B (kHz)

Fig. 1 Valores Medidos e Calculados para o Amplificador Sintonizado

Q=

rC

XL

X L = 2. . f . L

rC = R p R L

R P = QL . X L

PP = 2.Vcc

fr =

1

2

B=

L. C

fr

Q

3. Considere o amplificador classe C sintonizado cujo esquema encontra-se na figura 2.

4. Insira a placa EB-98 no sistema (ou coloque o protoboard sobre a bandeja).

5. Monte o circuito do amplificador, observando os seguintes cuidados:

a) Seja organizado na sua montagem, para facilitar eventuais correes no circuito montado;

b) Evite entortar os terminais dos componentes, pois estes so frgeis podem se quebrar;

c) No ligue ainda a alimentao do circuito.

d) Como indutor, use o Transformador de Pulsos (TP) fornecido.

6. Ajuste o gerador de sinais para uma entrada senoidal de 40kHz com 2Vpp.

7. Ajuste a alimentao para 10V, ligue o circuito e aplique o sinal de entrada.

8. Com o osciloscpio, observe os sinais na entrada (gerador) e na sada (carga).

9. Varie a frequncia do gerador at que a sada alcance seu valor mximo (ressonncia). Mea a

frequncia nessa situao (Obs.: o valor da fR por volta de 40kHz, mas varia de bancada para bancada).

Frequncia de Ressonncia calculada: ________________

(utlizando o valor de indutncia medido)

Frequncia de Ressonncia medida:

(mede-se com o osciloscpio)

________________

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 14

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

10. Anote as formas de onda de entrada e de sada na figura 3.

Fig. 2 Amplificador Classe C

CANAL 1

AC

DC

Escala vertical: _______ V/div

CANAL 2

AC

DC

Escala vertical: _______ V/div

Escala horizontal: ______ s/div

Fig. 3 Amplif. Classe C Formas de onda de tenso na entrada e na carga

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 15

unesp

DEPARTAMENTO DE ENGENHARIA ELTRICA

Os resultados obtidos at o momento so os esperados ? (frequncia e formas de onda)

Comente e justifique as diferenas observadas entre a teoria e a prtica. Anote suas concluses.

_____________________________________________________________________________________

_____________________________________________________________________________________

11. Observe, simultaneamente, o sinal de entrada e o sinal na base do transistor. Anote as formas de onda

na figura 4.

CANAL 1

AC

DC

(entrada)

Escala vertical: _______ V/div

CANAL 2

AC

DC

(base)

Escala vertical: _______ V/div

Escala horizontal: ______ s/div

Fig. 4 Amplif. Classe C Grampeamento Negativo

O resultado o esperado? Justifique o que foi observado.

_____________________________________________________________________________________

_____________________________________________________________________________________

12. Varie a amplitude da tenso de entrada e observe o que ocorre com a tenso de sada. Anote a PP.

PP calculada: ________________

(terica)

PP medida:

(prtica)

________________

13. Altere a forma de onda da tenso de entrada para triangular, e depois, para onda quadrada. Observe

as diferenas na onda de tenso na carga. Justifique as alteraes de comportamento observadas.

ATENO: AO TERMINAR, ORGANIZE A BANCADA SEGUINDO AS NORMAS

UTILIZAO DO LAB. DIDTICO PELOS ALUNOS DE ELETRNICA II (pgina iii).

DE

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 16

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

ANLISE DE EFEITOS DE FREQUNCIA

1.0 OBJETIVOS

Aps completar estas atividades de laboratrio, o aluno dever ser capaz de analisar e entender o

funcionamento de uma rede de avano e de uma rede atraso, funcionando isoladamente.

2.0 DISCUSSO

O funcionamento dos amplificadores dentro de uma banda mdia, onde os capacitores so aproximados

por uma impedncia de muito baixo valor, foi estudado em sees anteriores. Fora desta banda mdia, os

efeitos das capacitncias no podem ser desprezados porque influenciam significativamente no

funcionamento dos amplificadores. Abaixo da banda mdia, os capacitores apresentam alta impedncia,

levando os amplificadores a ganhos menores, e acima da banda mdia, capacitncias internas das

junes e outras parasitas tambm alteram o ganho e devem ser consideradas para um perfeito

entendimento do comportamento destes circuitos. A anlise deste comportamento varivel com a

frequncia pode ser introduzido com o estudo das redes de avano e atraso, circuitos RC que permitem

uma visualizao da variao das impedncias capacitivas com a variao da frequncia.

3.0 PROCEDIMENTO

REDE DE AVANO

1. Coloque a placa EB-98 nas guias do bastidor e encaixe o conector. No necessrio ligar o sistema.

2. Monte o circuito da Rede de Avano esquematizada na figura 1; para tanto, observe os seguintes

cuidados:

a) Encaixe cuidadosamente os componentes no protoboard, sem forar para no danific-los;

b) O sinal de entrada ser aplicado a partir do gerador de sinais usando-se o cabo BNC-jacar.

3. Utilize o gerador de sinais e aplique uma tenso senoidal com 2Vp-p, sem offset.

100nF

2Vpp

1k

osciloscpio

(canal 2)

osciloscpio

(canal 1)

Fig. 1 Rede de Avano

4. Varie a frequncia do sinal de entrada para diversos valores; com o auxlio do osciloscpio, mea

simultaneamente os sinais de entrada e sada do circuito e anote os resultados na tabela da figura 2.

Anote, ao menos, 10 resultados para que a curva tenha resoluo adequada.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 17

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

OBS: A amplitude da tenso de entrada varia com a variao da frequncia; corrija, se necessrio.

f [Hz]

Vin [Vp-p]

Vout [Vp-p]

Ganho

Ganho

em dB

f [Hz]

Vin [Vp-p]

Vout [Vp-p]

Ganho

Ganho

em dB

Fig. 2 Medidas na Rede de Avano

5. Mea o valor das resistncias e da capacitncia, e calcule a frequncia de corte do circuito. Apresente a

curva de resposta em frequncia da em um grfico monolog (figura 3).

10

10

10

10

10

10

Fig. 3 Resposta em Frequncia da Rede de Avano

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 18

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

6. Compare o valor calculado da frequncia de corte (fC) com o valor encontrado no grfico traado.

coerente?

REDE DE ATRASO

7. Monte o circuito da Rede de Atraso esquematizada na figura 4 tomando os mesmos cuidados do item 2.

8. Ajuste o gerador de sinais para uma tenso senoidal com 2Vp-p, sem offset.

1k

2Vpp

100nF

osciloscpio

(canal 1)

osciloscpio

(canal 2)

Fig. 4 Rede de Atraso

9. Com o auxlio do osciloscpio, mea simultaneamente os sinais de entrada e sada do circuito e anote

pelo menos 10 resultados na tabela da figura 5, para diferentes frequncias de sinal de entrada.

OBS: A amplitude da tenso de entrada varia com a variao da frequncia;

corrija, se necessrio.

f [Hz]

Vin [Vp-p]

Vout [Vp-p]

Ganho

Ganho

em dB

f [Hz]

Vin [Vp-p]

Vout [Vp-p]

Ganho

Ganho

em dB

Fig. 5 Medidas na Rede de Atraso

10. Apresente a curva de resposta em frequncia da Rede de Atraso no grfico monolog da figura 6.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 19

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

11. Compare o valor calculado da frequncia de corte (fC) com o valor encontrado no grfico traado.

coerente?

10

10

10

10

10

10

Fig. 6 Resposta em Frequncia da Rede de Atraso

Responda:

1) Qual deveria se a taxa de inclinao (terica) fora da banda de passagem para ambas as redes de

atraso estudadas?

2) Quais os valores destas inclinaes obtidas na prtica?

ATENO: APS A EXPERINCIA, ORGANIZE SUA BANCADA CONFORME AS NORMAS DE

UTILIZAO DO LABORATRIO DIDTICO PELOS ALUNOS DE ELETRNICA II

(pgina iii desta apostila). BANCADA EM DESACORDO COM AS NORMAS ACARRETAR EM

DIMINUIO DA NOTA DE LABORATRIO, CONFORME PREVISTO.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 20

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

RESPOSTA EM FREQUNCIA DE AMPLIFICADORES

1.0 OBJETIVOS

Aps completar estas atividades de laboratrio, o aluno dever ser capaz de analisar e entender o

comportamento de um amplificador emissor comum funcionando com um sinal de frequncia varivel na

entrada.

2.0 DISCUSSO

O funcionamento dos amplificadores dentro de uma banda mdia, onde os capacitores so aproximados

por uma impedncia de muito baixo valor, foi estudado em sees anteriores. Fora desta banda mdia, os

efeitos das capacitncias no podem ser desprezados porque influenciam significativamente no

funcionamento dos amplificadores. Abaixo da banda mdia, os capacitores apresentam alta impedncia,

levando os amplificadores a ganhos menores, e acima da banda mdia, capacitncias internas das

junes e outras parasitas tambm alteram o ganho e devem ser consideradas para um perfeito

entendimento do comportamento destes circuitos.

ATENO: Recomenda-se aos senhores alunos que realizem os clculos necessrios para esta

experincia antecipamente e tragam os resultados j computados, para facilitar a implementao

dos circuitos e aproveitar melhor o tempo de aula. Os clculos necessrios encontram-se ao final

deste roteiro de aula.

3.0 PROCEDIMENTO

RESPOSTA EM FREQUNCIA DE UM AMPLIFICADOR EC

1. Coloque a placa EB-98 nas guias do bastidor e encaixe o conector. No ligar o sistema.

2. Monte o circuito do Amplificador Emissor-Comum esquematizado na figura 1 observando os seguintes

cuidados:

a) Seja organizado na sua montagem, para facilitar eventuais correes no circuito montado;

b) Evite entortar os terminais dos componentes, pois estes so frgeis podem se quebrar;

c) Encaixe cuidadosamente os componentes no protoboard, sem forar para no danific-los;

d) Observe as polaridades dos capacitores e a pinagem do transistor;

e) O sinal de entrada ser aplicado a partir do gerador de sinais usando-se o cabo BNC-jacar.

3. Ligue o sistema e ajuste PS-1 para 10V. (No preciso inicializar o sistema).

4. Ajuste o gerador de sinais para uma tenso senoidal de 100Hz com amplitude de 10mV (Vpp=20mV).

5. Mea os valores de polarizao utilizando um voltmetro CC e anote os resultados na tabela 01, no final

deste roteiro de aula (a corrente de emissor deve ser calculada; no abrir o circuito).

6. Com o auxlio do osciloscpio, mea simultaneamente os sinais de entrada e sada do circuito e anote

os resultados na tabela da figura 2. Varie a frequncia, obtendo ao menos 20 resultados para posterior

traado do grfico.

OBS.: Para que os resultados sejam confiveis e tenham qualidade, utilize sempre o osciloscpio nas

escalas adequadas. Para medidas de frequncia, utilize o osciloscpio.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 21

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

PS-1

10k

3,3k

2,2F

VCE(mx) = 40V

4,7F

+

VCB(mx) = 75V

2N2222A

PD(mx) = 0,5W

1,5k

Vin

IC(mx) = 0,8A

hfe = 150

fT = 300MHz

CC = 8pF

+

2,2k

1k

Ce = 25pF

10F

rb = 50

Rg = 400

Fig. 1 Amplificador Emissor Comum

OBS: Se a amplitude da tenso de entrada variar com a frequncia; reajuste-a.

f [Hz]

Vin [mVp-p]

Vout [mVp-p]

Ganho

Ganho

em dB

f [Hz]

Vin [mVp-p]

Vout [mVp-p]

Ganho

Ganho

em dB

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 22

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

f [Hz]

Vin [mVp-p]

Vout [mVp-p]

Ganho

Ganho

em dB

Fig. 2 Medidas no Amplificador EC

7. Apresente a curva de resposta em frequncia do amplificador na figura 3.

10

10

10

10

10

10

Fig. 3 Resposta em Frequncia do Amplificador EC

8. A partir do grfico,estime o valor das frequncias de corte superior e inferior.

9. Compare os valores calculados para as frequncias de corte superior e inferior com os resultados

obtidos no grfico. Eles so coerentes?

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 23

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

TABELA 1

Grandeza

VCC [V]

Valor

Calculado

Valor

Medido

VB [V]

VE [V]

IE [mA]

re []

rC []

Av

TABELA 2

Grandeza

fentr [Hz]

fsada [Hz]

fE [Hz]

fB [MHz]

fC [MHz]

Valor

Calculado

TABELA3

f1 [Hz]

Grandeza

f2 [Hz]

Valor Calculado

Valor Medido

Amplificador Emissor-Comum

Rent = R1 R 2 .re,

Rsada RC

re, =

25mV

IE

Am =

rC

re,

rC = RC // RL

Amplificador Coletor-Comum

Rent = R1 R 2 .RE

Rsada = re, +

RS R1 R 2

Aspectos Frequenciais

f ent =

1

2 ( Rs + Rent )Cent

f sada =

fE =

1

2 ( Rsada + RL )Csada

r

CB = Ce, + CC, 1 + C,

re

Cent ( Miller ) = C (1 A)

fB =

2 (Zs EMISSOR // RE ) CE

fC =

1

2 rC CC

rB = ( rG + rb, ) re,

A-1

Csada ( Miller ) = C

C,e =

1

2 rB CB

1

2 fT re,

Av [dB ] = 20.log Av

CC =C,C +CPE

AP [dB] = 10.log AP

rG = RS R1 R 2

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 24

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

AMPLIFICADOR DIFERENCIAL

1.0 OBJETIVOS

Aps completar estas atividades de laboratrio, o aluno dever ser capaz de:

1. Analisar e entender o funcionamento de um amplificador diferencial, funcionando com entrada simples

ou diferencial e sada simples ou diferencial;

2. Medir os ganhos experimentalmente e comparar com os valores tericos calculados;

3. Entender o funcionamento de um espelho de corrente e verific-lo em um amplificador diferencial.

2.0 DISCUSSO

Dentre os diversos tipos de amplificadores que podem ser construdos com dispositivos discretos, o

amplificador diferencial constitui-se numa topologia com caractersticas particulares que o torna

interessante para ser utilizado como estgio de entrada de amplificadores integrados, como os

Amplificadores Operacionais. O amplificador diferencial possui 2 entradas e 2 sadas, podendo ter

alimentao simples ou dividida. Dependendo da maneira como o sinal de entrada aplicado (apenas em

uma das entradas, nas duas entradas com valores diferentes ou com valor igual nas duas entradas), o

ganho, e por consequncia, a tenso obtida na sada, podem ser alterados. Dependendo da maneira

como a carga ligada, apenas em uma sada ou entre as duas sadas, novamente podem ser obtidos

valores diferentes de ganhos para cada situao. A utilizao de espelhos de corrente para a polarizao

destes circuitos oferece a alta impedncia necessria nos coletores e nos emissores dos transistores do

par diferencial, contribuindo tambm para a necessria equalizao das correntes nos 2 ramos do par

diferencial.

ATENO: Recomenda-se aos senhores alunos que realizem os clculos necessrios para esta

experincia antecipamente e tragam os resultados j computados, para facilitar a implementao

dos circuitos e aproveitar melhor o tempo de aula.

3.0 PROCEDIMENTO

POLARIZAO DO PAR DIFERENCIAL

1. Coloque a placa EB-98 nas guias do bastidor e encaixe o conector.

2. Monte o circuito do Par Diferencial esquematizado na figura 1; para tanto, observe os seguintes

cuidados:

a) Encaixe cuidadosamente os componentes no protoboard, sem forar para no danific-lo;

b) Evite entortar demais os terminais dos componentes, para no danific-los, pois estes sero

utilizados em aulas de outras turmas, ou mesmo nesta turma em outras experincias;

c) Faa sua montagem de maneira organizada, de modo a poder identificar qual o transistor Q1

e qual o transistor Q2.

3. Ligue o sistema, e ajuste PS-1 e PS-2 para obter as tenses de alimentao +12V e 12V.

4. Aterre as entradas vi1 e vi2 e mea, com o voltmetro, as tenses de polarizao nos coletores e nos

emissores de Q1 e Q2. Anote os resultados na tabela da figura 2.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 25

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

PS-1

100k

100k

vo1

v o2

v i1

v i2

Q2

Q1

2N2222A

2N2222A

100k

Fig. 1 Circuito do Amplificador Diferencial

PS-2

PS-1

PS-2

Vc1

Vc2

Ve1=Ve2

Fig. 2 Tenses de Polarizao do Par Diferencial

AMPLIFICAO DE SINAIS ENTRADA SIMPLES / SADA SIMPLES

5. Desligue a entrada vi1 do terra e aplique nela um sinal senoidal de 10mV de pico, frequncia de 1kHz.

Mantenha a entrada vi2 aterrada e a sada vo1 em aberto. Esboce na figura 3 as formas de onda de tenso

de entrada, e a sada observada em vo2 .

OBS: Para poder verificar a defasagem entre os dois sinais, observe os dois canais do

osciloscpio ao mesmo tempo, embora em escalas diferentes devido ao ganho.

6. Mantenha o canal 1 em vi1 e passe o canal 2 do osciloscpio para a sada vo1. Esboce a forma de onda

de vo1 juntamente com a tenso vo2 . Observe a defasagem e os valores de pico-a-pico de ambas as

ondas.

7. Calcule o ganho terico e compare com o ganho experimental observado nesta situao.

Ganho Terico:

_______________

Ganho Experimental:

_______________

Os resultados esto coerentes? O ganho experimental est prximo do esperado?

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 26

unesp

DEPARTAMENTO DE ENGENHARIA ELTRICA

Canal 1 Vi1 (gerador) escala vertical: ____ mV/div

Canal 2 Vo2 (sada) escala vertical: _____ V/div

escala horizontal (ambos): _____ ms/div

Fig. 3 Ganho Diferencial Entrada e Sada Simples

AMPLIFICAO DE SINAIS ENTRADA SIMPLES / SADA DIFERENCIAL

8. Com o mesmo circuito em funcionamento, mea a tenso diferencial de sada. Para tanto, conecte o

canal 1 do osciloscpio na sada vo2 e o canal 2 do osciloscpio na sada vo1 e faa a leitura da sada

diferencial (o osciloscpio dever estar no modo diferencial de leitura, fornecendo: vo2 vo1 ). Esboce a

forma de onda observada na figura 4.

Canal 1 Canal 2

(tenso diferencial de sada)

escala vertical: _____ V/div

escala horizontal: _____ ms/div

Fig. 4 Ganho Diferencial Entrada Simples e Sada Diferencial

9. Calcule o ganho terico e compare com o ganho experimental observado nesta situao.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 27

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

Ganho Terico:

_______________

Ganho Experimental:

_______________

Os resultados esto coerentes? O ganho experimental est prximo do esperado?

ANLISE DE MODO COMUM SADA SIMPLES

10. Desligue o modo diferencial do osciloscpio.

11. Conecte as duas entradas do amplificador diferencial no gerador, ajustando as entradas de modo que

vi1 = vi2 com 100 mVp, frequncia 1kHz, senoidal.

12. Esboce na figura 5 as formas de onda de tenso de entrada, e a sada observada em vo2 .

Canal 1 entrada de modo-comum

Canal 2 Vo2 (sada) escala vertical: _____ V/div

escala vertical: _____ V/div

escala horizontal (ambos): _____ ms/div

Fig. 5 Ganho de Modo-Comum Sada Simples

13. Calcule o ganho terico e compare com o ganho experimental observado nesta situao.

Ganho Terico:

_______________

Ganho Experimental:

_______________

Os resultados esto coerentes? O ganho experimental est prximo do esperado?

ANLISE DE MODO COMUM SADA DUPLA

14. Com o mesmo circuito em funcionamento, mea a tenso diferencial de sada.

Qual foi o resultado obtido nesta situao? Este resultado era o esperado?

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 28

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

AMPLIFICADOR NO-INVERSOR E AMPLIFICADOR INVERSOR DE TENSO COM AMP-OP

1.0 OBJETIVOS

Aps completar estas atividades de laboratrio, o aluno dever ser capaz de:

1. Verificar a operao do amplificador operacional (AMP-OP) em malha fechada.

2. Verificar experimentalmente o ganho de um amplificador inversor e de um amplificador no-inversor de

tenso com AMP-OP, para sinais CC e CA, utilizando-se de multmetro digital e osciloscpio.

3. Medir as impedncias de entrada e sada para o amplificador no-inversor de tenso.

4. Verificar a reduo do off-set de sada causada pela realimentao negativa.

5. Determinar a resposta em frequncia destes amplificadores.

2.0 DISCUSSO

A realimentao negativa altera as caractersticas de malha aberta do AMP-OP, e no caso da

configurao de amplificador inversor, dever ser observado que a impedncia de entrada estabiliza-se, a

impedncia de sada diminui e o ganho diminui e estabiliza-se. J a configurao de amplificador noinversor tem sua impedncia de entrada aumentada, a impedncia de sada diminuda e o ganho tambm

diminui e estabiliza-se.

Um amplificador operacional integrado pode ser utilizado para amplificar tenses CC e CA, e o ganho

deste amplificador depende da configurao da realimentao negativa escolhida. Na presente

experincia, sero configurados o amplificador inversor de tenso, que tem como ganho:

Rrealim

Av

Rentr

e tambm o amplificador no inversor de tenso, que tem como ganho:

Av = 1 +

Rrealim

Rentr

Experimentalmente, o ganho pode ser obtido medindo-se as tenses de entrada e sada do circuito e

calculando-se a relao:

Av

Vsaida

Ventrada

Deve ser observado que no amplificador inversor o sinal de sada tem fase invertida em relao ao sinal

de entrada.

Alm de alterar as caractersticas bsicas de funcionamento do amplificador operacional em malha aberta,

a realimentao negativa tambm altera o offset de sada, reduzindo-o, e aumenta a faixa de resposta em

frequncia dos amplificadores assim realimentados.

3.0 PROCEDIMENTO

AMPLIFICADOR NO-INVERSOR DE TENSO

1. Insira a placa EB-98 no sistema (ou coloque o protoboard sobre a bandeja). No necessrio inicializar

o sistema e nem ligar a fonte principal da MB-U.

2. Monte o circuito do Amplificador No-inversor de tenso esquematizado na figura 1 utilizando-se do

Amp-Op 741; para tanto, observe os seguintes cuidados:

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 29

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

a) Encaixe cuidadosamente o CI no protoboard e se necessrio retir-lo, faa com ateno para

no entortar ou danificar seus terminais;

b) No se esquea de ligar a alimentao do CI, deixando para energizar a MB-U apenas quando

tiver terminado a montagem e conferido todas as ligaes;

c) Evite entortar demais os terminais do capacitor, pois este frgil e quebra-se com facilidade;

d) O sinal de entrada ser aplicado a partir do gerador de sinais usando-se o cabo BNC-jacar.

e) Seja organizado na sua montagem, para facilitar eventuais correes no circuito montado;

Fig. 1 Amplificador No-inversor de Tenso

MEDIDAS DE AMPLIFICAO CC

3. Energize o circuito.

4. A fonte CC varivel PS-1 ser utilizada como o sinal CC de entrada do amplificador. Varie a fonte PS-1

para os valores da tabela da figura 2. Faa o melhor ajuste possvel das tenses e anote o valor real que o

voltmetro indicar. Com o uso do mesmo voltmetro, mea tambm a tenso de sada para cada caso e

complete a tabela da figura 2.

Vent [V]

(desejada)

Vent [V]

(medida)

Vsada [V]

10

Ganho Real

(medido)

Fig. 2 Ganho CC do Amplificador No-inversor

Os valores medidos de ganho CC so coerentes com o valor terico calculado?

MEDIDAS DE AMPLIFICAO CA

5. Para o mesmo circuito j montado, substitua a entrada CC (PS-1) por uma entrada senoidal (gerador de

sinais) de 10kHz e 2Vp-p, sem nvel DC (offset). Retire o voltmetro do circuito.

6. Com o auxlio do osciloscpio, utilizando os 2 canais simultaneamente, esboce as formas de onda de

entrada e sada, registrando os eixos horizontal e vertical na figura 3.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 30

unesp

DEPARTAMENTO DE ENGENHARIA ELTRICA

7. Calcule o valor do ganho e conclua o que foi observado com relao aos resultados terico/prtico e

fase do sinal.

Foi observado nvel DC no sinal de sada? Por que?

AMPLIFICADOR NO INVERSOR

escala vertical (ch1) =

_________

escala vertical (ch2) =

_________

escala horizontal = _____________

ganho prtico = __________________

Fig. 3 Ganho CA do Amplificador No-inversor

MEDIDAS DE IMPEDNCIA DE ENTRADA E SADA

8. Para a medida de impedncia de entrada, retire o osciloscpio e o gerador de sinais do circuito.

9. Mantenha o circuito alimentado e mea, com o ohmmetro, a resistncia entre Vent e terra.

Zin = _____________

10. Ligue Vent ao terra (curto-circuito da entrada) e mea, com o ohmmetro, a resistncia entre Vsada e

terra. (mantenha o circuito normalmente com a sua alimentao)

Zout = _____________

VERIFICAO DO EFEITO DA REALIMENTAO NEGATIVA SOBRE O OFF-SET DE SADA.

11. Mantenha o curto-circuito da entrada e retire o ohmmetro da sada.

12. Abra a realimentao (retire o resistor) e mea a tenso de sada com o voltmetro.

vos( sa da )OL = _____________

13. Ligue novamente o resistor de realimentao e mantenha a entrada curto-circuitada; mea novamente

a tenso de sada com o voltmetro nesta condio.

vos( sada )CL = _____________

Comente o que foi observado com relao tenso de off-set de sada em ambos os casos.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 31

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

AMPLIFICADOR INVERSOR MEDIDAS DE AMPLIFICAO CC

14. Monte agora o circuito do Amplificador Inversor de tenso esquematizado na figura 4, utilizando-se do

Amp-Op 741.

Fig. 4 Amplificador Inversor com Amp-Op

15. Varie a fonte de tenso PS-1 para os valores da tabela da figura 5. Faa o melhor ajuste possvel das

tenses e anote o valor real que o voltmetro indicar. Com o uso do mesmo voltmetro, mea tambm a

tenso de sada para cada caso e complete a tabela da figura 5.

Vent [V]

(desejada)

Vent [V]

(medida)

Vsada [V]

1.0

2.0

4.0

7.0

8.0

10

Ganho Real

(medido)

Fig. 5 Ganho do Amplificador Inversor

Os valores medidos de ganho CC so coerentes com os valores tericos calculados?

MEDIDAS DE AMPLIFICAO CA

16. Para o mesmo circuito j montado, retire os voltmetros e a fonte PS-1.

17. Aplique na entrada um sinal triangular de 1kHz e 1Vp-p, sem nvel DC do gerador.

18. Com o auxlio do osciloscpio, utilizando os 2 canais simultaneamente, esboce as formas de onda de

entrada e sada, registrando os eixos horizontal e vertical na figura 6. Observe a inverso de fase.

19. Calcule o valor do ganho e conclua o que foi observado com relao aos resultados terico/prtico e

fase do sinal.

Foi observado nvel DC no sinal de sada? Por que?

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 32

unesp

DEPARTAMENTO DE ENGENHARIA ELTRICA

AMPLIFICADOR INVERSOR

escala vertical (ch1) =

_________

escala vertical (ch2) =

_________

escala horizontal = _____________

ganho prtico = __________________

Fig. 6 Ganho CA do Amplificador Inversor

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 33

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

AMPLIFICADOR SOMADOR COM AMP-OP E REFORADOR DE CORRENTE

1.0 OBJETIVOS

Aps completar estas atividades de laboratrio, o aluno dever ser capaz de:

1. Construir e verificar o funcionamento de um amplificador somador de tenso utilizando amplificador

operacional;

2. Verificar experimentalmente o funcionamento de um reforador de corrente push-pull ligado sada de

um amp-op.

2.0 DISCUSSO

Um amplificador inversor construdo com amplificador operacional pode ter uma ou diversas entradas;

cada uma das entradas contribui com uma parcela de corrente na entrada inversora do amp-op, fazendo

com que a tenso de sada seja proporcional soma destas correntes de entrada. Considerando-se que a

entrada inversora um terra virtual, a tenso de sada ser ento propocional soma das tenses

aplicadas nas entradas, ponderadas pelos respectivos resistores de entrada, conforme a expresso a

seguir:

Vsaida V1 V2 V3 V4

+

+

+

+ ...

Rsaida

R1 R2 R3 R4

Como trata-se de um amplificador inversor, para uma entrada positiva, a sada negativa e para uma

entrada negativa, tem-se uma sada positiva; por este motivo, faz-se necessria uma alimentao dividida

(ou simtrica), ou ento alteraes no circuito que permitam a inverso de fase para o sinal amplificado de

sada. Isto possvel polarizando-se a entrada no-inversora do amp-op com uma tenso positiva,

prxima metade da tenso de alimentao e uso de capacitores para acoplamento e derivao.

Em algumas aplicaes, a capacidade de corrente na sada do amplificador operacional insuficiente para

os requisitos da carga; nestas situaes, possvel amplificar-se a corrente de sada utilizando-se um

transistor (para correntes unidirecionais) ou dois transistores num arranjo push-pull para correntes

alternadas. A realimentao negativa encarrega-se de minimizar os efeitos de VBE, dispensar a

polarizao na base dos transistores e praticamente eliminar a distoro por cross-over.

3.0 PROCEDIMENTO

AMPLIFICADOR SOMADOR DE 3 ENTRADAS COM ALIMENTAO SIMTRICA

1. Coloque a placa EB-98 nas guias do bastidor e encaixe o conector;

2. Monte o circuito da figura 1, tomando os seguintes cuidados:

a) Encaixe cuidadosamente o CI LM741 no protoboard e se necessrio retir-lo, faa com

ateno para no entortar ou danificar seus terminais (pinagem do CI na figura 6);

b) No se esquea de ligar a alimentao do CI, deixando para energizar a MB-U apenas quando

tiver terminado a montagem e conferido todas as ligaes;

3. Aplique as tenses de entrada conforme o esquema, ajustando-as para os seguintes valores:

PS-1 = 1V

PS-2 = 4V

Gerador: senoidal, sem offset, 1kHz, 1Vpp

4. Esboce a forma de onda de sada na figura 2. O resultado o esperado?

5. Varie a tenso das fontes PS-1 e PS-2 e observe o comportamento da tenso de sada.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 34

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

10k

10k

osciloscpio

(canal 1)

10k

+12V

10k

741

Vs

V

PS-1

osciloscpio

(canal 2)

-12V

PS-2

Fig. 1 Amplificador Somador com Amp-Op

AMPLIFICADOR SOMADOR

escala vertical =

_____________

escala horizontal = _____________

Fig. 2 Tenso de Sada do Somador

REFORADOR DE CORRENTE PUSH-PULL

6. Desligue a alimentao.

7. Monte o circuito esquematizado na figura 3, do amplificador inversor sem reforador de corrente.

8. Ligue novamente a alimentao e aplique na entrada um sinal senoidal de 0,5Vpp, sem offset do

gerador, frequncia de 1 kHz.

9. Aumente o valor da tenso de entrada para 2Vpp e observe o que ocorre na sada. Anote na figura 4 as

formas de onda de tenso de entrada e sada.

Quais so os valores das tenses de saturao positiva e negativa?

Voc no acha que estes valores esto muito baixos? Explique o que est ocorrendo.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 35

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

47k

+12V

osciloscpio

(canal 1)

10k

2

741

3

osciloscpio

(canal 2)

100

-12V

Fig. 3 Amplificador Inversor sem Reforador de Corrente

Amplificador Inversor

SEM reforador de corrente

Amplificador Inversor

COM reforador de corrente

Canal 1 tenso do gerador

escala vertical: ___________V/div

Canal 1 tenso do gerador

escala vertical: ___________V/div

Canal 2 tenso na carga

escala vertical: ___________V/div

Canal 2 tenso na cargaescala vertical: ___________V/div

escala horizontal (ambos): _____ ms/div

Fig. 4 Formas de onda de tenso no Amplificador Inversor

10. Desligue novamente a alimentao e o sinal da entrada.

11. Acrescente o reforador de corrente push-pull, conforme esquematizado na figura 5.

OBSERVE A PINAGEM CORRETA DOS TRANSISTORES NA FIGURA 6.

CUIDADO AO LIGAR PARA NO INVERTER OS TERMINAIS!

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 36

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

12. Aps conferir as ligaes, ligue a alimentao e aplique na entrada um sinal senoidal de at 3Vpp,

sem offset do gerador, frequncia de 1 kHz e anote na figura 4 as formas de onda de tenso de entrada e

sada.

47k

+12V

osciloscpio

(canal 1)

TIP31

10k

2

741

3

osciloscpio

(canal 2)

TIP32

100

-12V

Fig. 5 Amplificador Inversor com Reforador de Corrente

13. Calcule a corrente de pico na carga.

Tire suas concluses sobre o funcionamento do reforador Push-Pull. Foi possvel observar crossover ?

TI

TIP P 31

32

BASE

COLETOR

EMISSOR

Fig. 6 Pinagem dos terminais dos transistores TIP 31 e TIP32 e do CI LM741

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 37

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

FILTROS ATIVOS COM AMP-OP

1.0 OBJETIVOS

Aps completar estas atividades de laboratrio, o aluno dever ser capaz de:

1. Entender como funcionam os filtros ativos que utilizam-se de amplificadores operacionais.

2. Verificar o funcionamento dos mesmos, levantando as curvas de resposta em frequncia dos filtros

ativos em papel monolog.

3. Determinar experimentalmente as frequncias de corte (a partir dos grficos) para filtros ativos e

comparar com os valores tericos.

2.0 DISCUSSO

Um amplificador operacional pode ser utilizado para a construo de filtros (ativos) passa-baixas, passaaltas, passa-faixa e rejeita-faixa. Nesta prtica sero verificados os funcionamentos de um filtro passabaixas (FPB) e de um filtro passa-altas (FPA), que na sua banda mdia apresentam ganho relativamente

estvel, e fora da banda de passagem apresentam uma inclinao dependente do nmero de plos,

sempre mltipla de 20 dB/dcada.

Para os filtros ativos a serem estudados (Butterworth, 1 Plo e 2 Plos, no-inversores), se os resistores e

capacitores de filtro de cada rede de atraso forem iguais, a frequncia de corte pode ser calculada por:

fc =

1

2RC

O ganho na banda mdia pode ser obtido medindo-se as tenses de entrada e sada do circuito e

calculando-se a relao:

Av =

Vsa da

R

= 1+ 1

Ventrada

R2

ATENO: Recomenda-se aos senhores alunos que realizem os clculos necessrios para esta

experincia antecipamente e tragam os resultados j computados, para facilitar a implementao

dos circuitos e aproveitar melhor o tempo de aula.

3.0 PROCEDIMENTO

FILTRO PASSA-BAIXAS DE 1 PLO

1. Insira a placa EB-98 no sistema (ou coloque o protoboard sobre a bandeja). No necessrio inicializar

o sistema e nem ligar a fonte principal da MB-U.

2. Monte o circuito do FPB de 1 Plo esquematizado na figura 1 utilizando-se do Amp-Op 741; para tanto,

observe os seguintes cuidados:

a) Encaixe cuidadosamente o CI no protoboard e se necessrio retir-lo, faa com ateno para

no entortar ou danificar seus terminais;

b) No se esquea de ligar a alimentao do CI, deixando para energizar a MB-U apenas quando

tiver terminado a montagem e conferido todas as ligaes;

c) Evite entortar demais os terminais do capacitor, pois este frgil e quebra-se com facilidade;

d) O sinal de entrada ser aplicado a partir do gerador de sinais usando-se o cabo BNC-jacar.

e) Seja organizado na sua montagem, para facilitar eventuais correes no circuito montado;

3. Energize o circuito e ajuste o gerador de sinais para uma forma de onda senoidal.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 38

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

+12V

entrada

270

33nF

3

2

+

-

7

6

4

sada

4.7k

-12V

8.2k

Fig. 1 Filtro Ativo Passa-Baixas de 1 Plo

4. Calcule a frequncia de corte do filtro e escolha as frequncias nas quais colher os pontos para

construir o grfico. Com o auxlio do osciloscpio, mea simultaneamente os sinais de entrada e sada e

anote os resultados na tabela da figura 2.

5. Calcule o ganho experimental e apresente a curva de resposta em frequncia do FPB de 1 Plo em um

grfico monolog (figura 3).

OBS: A amplitude da tenso de entrada varia ligeiramente com a variao da frequncia; corrija, se

necessrio. Caso observe deformao na onda de sada devido ao slew-rate do amp-op, diminua a

amplitude do sinal de entrada para aumentar a Banda de Potncia do amplificador.

f [Hz]

Vin [Vp-p]

Vout [Vp-p]

Ganho

[dB]

f [Hz]

Vin [Vp-p]

Vout [Vp-p]

Ganho

[dB]

Fig. 2 Medidas no FPB de 1 Plo

6. Determine a frequncia de corte (fc) no grfico e observe a taxa de inclinao acima de fc.

7. Compare o resultado experimental obtido com a frequncia terica calculada. Mea e anote o valor das

resistncias e do capacitor utilizado. Comente as diferenas eventualmente observadas.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 39

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

10

10

10

10

10

10

Fig. 3 - Resposta em Frequncia do FPB de 1 Plo

FILTRO PASSA-ALTAS DE 2 PLOS

8. Monte o circuito do FPA de 2 Plos esquematizado na figura 4 utilizando-se do Amp-Op 741 e

observando os mesmos cuidados do item 2.

9. Energize o circuito e ajuste o gerador de sinais para uma forma de onda senoidal.

270

33nF

+12V

33nF

3

entrada

2

270

+

-

7

6

sada

4

-12V

4.7k

8.2k

Fig. 4 Filtro Ativo Passa-Altas de 2 Plos

10. Calcule a frequncia de corte do filtro e escolha as frequncias nas quais colher os pontos para

construir o grfico. Com o auxlio do osciloscpio, mea simultaneamente os sinais de entrada e sada e

anote os resultados na tabela da figura 5.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 40

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

11. Calcule o ganho experimental e apresente a curva de resposta em frequncia do FPA de 2 Plos em

um grfico monolog (figura 6).

OBS: Se necessrio, corrija a amplitude da tenso de entrada. Caso observe deformao na onda

de sada devido ao slew-rate, diminua a amplitude de entrada.

f [Hz]

Vin [Vp-p]

Vout [Vp-p]

Ganho

[dB]

f [Hz]

Vin [Vp-p]

Vout [Vp-p]

Ganho

[dB]

Fig. 5 - Resposta em Frequncia do FPA de 2 Plos

12. Determine a frequncia de corte (fc) no grfico e observe a taxa de inclinao abaixo de fc .

13. Compare o resultado experimental com a frequncia calculada. Comente as diferenas observadas.

10

10

10

10

10

10

Fig. 6 Resposta em Frequncia do FPA de 2 Plos

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 41

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

CIRCUITOS NO LINEARES COM AMP-OP

1.0 OBJETIVOS

Aps completar estas atividades de laboratrio, o aluno dever ser capaz de:

1. Entender como funciona um retificador ativo com amp-op (retificador de instrumentao).

2. Construir um detector de pico ativo e observar o efeito da carga no valor de pico detectado.

3. Entender o funcionamento dos circuitos limitador e grampeador positivos ativos.

2.0 DISCUSSO

Os amp-op's podem melhorar o funcionamento de circuitos que usam diodos (retificadores, grampeadores,

ceifadores, etc.), reduzindo substancialmente o efeito da tenso de compensao dos diodos, alm de

praticamente eliminar os efeitos de carga e de fonte nestes mesmos circuitos

Para que um circuito retificador convencional (no-ativo) funcione adequadamente necessrio que a

tenso de entrada seja maior que 0,7V para diodos de silcio e 0,3V para diodos de germnio. Quando a

tenso de entrada menor que estes valores, no possvel vencer-se a barreira de potencial da juno e

o circuito no funciona. Os circuitos retificadores ativos superam esta limitao, utilizando-se das

propriedades de funcionamento dos amplificadores operacionais que, devido realimentao negativa,

geram tenso suficiente em sua sada para colocar o diodo em conduo, antes mesmo da tenso de

entrada ter atingido a tenso de barreira.

No caso dos detectores de pico, a baixa impedncia de sada do amp-op garante carga praticamente

instantnea do capacitor, ficando o mesmo carregado com o valor mximo do pico positivo da tenso de

entrada. Nos intervalos em que os picos de tenso de entrada forem menores que a tenso do capacitor, a

descarga do mesmo ocorrer em funo da carga ligada a ele.

Para os circuitos limitador e grampeador, a eliminao praticamente total da tenso de barreira do diodo

permite sua utilizao em tenses pequenas de entrada.

3.0 PROCEDIMENTO

RETIFICADOR ATIVO

1. Coloque a placa EB-98 nas guias do bastidor e encaixe o conector.

2. Monte o circuito do Retificador Ativo esquematizado na figura 1 utilizando-se do Amp-Op 741 e com

RL=100; para tanto, observe os seguintes cuidados:

a) Encaixe cuidadosamente o CI no protoboard e se necessrio retir-lo, faa com ateno para

no entortar ou danificar seus terminais;

b) No se esquea de ligar a alimentao do CI, deixando para energizar a MB-U apenas quando

tiver terminado a montagem e conferido todas as ligaes;

c) O sinal de entrada ser aplicado a partir do gerador de sinais usando-se o cabo BNC-jacar.

3. Energize o circuito e ajuste o gerador de sinais para uma forma de onda senoidal de 1KHz com

amplitude de 0,5Vp, off-set zero.

4. Com o auxlio do osciloscpio, mea simultaneamente os sinais de entrada e sada do circuito e esboce

a forma de onda dos dois sinais, destacando as escalas horizontal e vertical.

5. Diminua a amplitude do sinal de entrada para 50mVp e repita o item anterior.

_____________________________________________________________________________________________________

Laboratrio de Eletrnica II Prof. Alceu Ferreira Alves 2016

pgina 42

DEPARTAMENTO DE ENGENHARIA ELTRICA

unesp

+12V

entrada

270

7

+

LM741

2 _

4

sada

-12V

RL

A

anodo

catodo

Fig. 1 Retificador Ativo

RETIFICADOR ATIVO, entrada 1Vpp

escala horizontal =

______________

escala vertical = _________________