Académique Documents

Professionnel Documents

Culture Documents

A-E-2 037 David Jimenez Marco

Transféré par

davinci300Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

A-E-2 037 David Jimenez Marco

Transféré par

davinci300Droits d'auteur :

Formats disponibles

SEGUNDA ACTIVIDAD EVALUABLE

1: Asignatura:

FUNDAMENTOS de SISTEMAS DIGITALES

2: Ttulo de la Actividad:

Diseo, Implementacin y Simulacin de un Circuito en

Lgica Secuencial

3: Datos personales:

- Nombre y Apellidos:

David Jimnez Marco

- DNI: 47802484-c

- Centro asociado: Barcelona Nou Barris

4: Cdigo de la actividad que

2_037_David_Jimenez_Marco.doc

le

ha

correspondido

realizar:

A-E-

5: Enunciado.

Enunciado A-E-2_037_David_Jimenez_Marco.doc

Esta actividad consiste en el diseo e implementacin en el un circuito secuencial que

consta de tres bloque funcionales que realizan funciones claramente diferentes. El primer

bloque consiste en construir un reloj con el circuito de tiempo 555 funcionando como

astable. El segundo bloque consiste en obtener, a partir de este reloj, una onda cuadrada de

mayor periodo y, por ultimo, el tercer bloque consiste en construir un autmata finito

controlado por el tren de pulsos anterior y que acte de una forma u otra en funcin de si

este pulso est en alta o en baja. Por tanto, el esquema a nivel de diagrama de bloques del

circuito a disear y simular es el de la siguiente figura:

Reloj

555

Reloj

t1 t2

Generador

de la seal

de control,

x

Circuito

secuencial

de 2 bits

Q1

Q0

Reloj

X

tm = 4T

tm = 4T

Disee el sistema lgico secuencial de la figura para que el circuito secuencial de 2

bits realice las siguientes funciones:

- Si x=1 no cambia de estado. Es decir, permanece en el mismo estado con

independencia del estado en el que se encuentre.

- Si x=0 y est en el estado 01 en el estado 10 en el estado 11 pasa al estado 00 y si

est en el estado 00 pasa al estado 10.

Apellidos, nombre: Jimnez Marco, David

DNI:47802484-C

1/10

Fundamentos de Sistemas Digitales

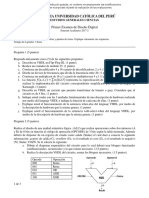

6: Realizacin del diseo y explicacin de los pasos seguidos para la realizacin del diseo

de los distintos bloques funcionales.

Empiezo por el primer bloque funcional, el reloj 555:

Conecto el integrado 555 tal y como se muestra en la figura 10.13 del texto base para

configurarlo como astable:

Teniendo en cuenta las frmulas para los intervalos en alta y baja (t1 y t2) en esta

configuracin(Rb en paralelo con un diodo):

t1 0,69*RA*C

t2 0,69*RB*C

T = t1+t2 = 0,69(RA+RB)*C

Segn estas frmula bastara con dar el mismo valor a Ra y Rb para tener los mismos

intervalos, he probado con Ra=Rb=10K y C=0,5nF, tericamente :

t1= t2=0,69*103*0,5*10-9 = 3,45us

pero al comprobar el cronograma he obtenido:

t14,5us (en alta)

t23,7us (en baja)

He ido cambiando los valores de Ra y Rb, tal y como explic el equipo docente en los foros

hasta que he obtenido t1t2 para los valores:

Ra=8k y Rb=10k

obteniendo t1t24,7us

Generador de la Seal de Control: Para realizar este generador utilizo el SN74393 como

recomiendan en la gua de estudio.

Apellidos, nombre: Jimnez Marco, David

DNI:47802484-C

2/10

Fundamentos de Sistemas Digitales

Mirando su hoja de caractersticas veo que la salida Qc cambia de alta a baja y viceversa cada 4

pulsos, con lo cual solo necesitamos conectar el reloj del anterior bloque funcional a la entrada

y coger la salida Qc .

*Ntese que hay que poner clear en baja para que funcione correctamente.

Circuito Secuencial de 2 bit: Empiezo por representar el diagrama de transicin con los datos

del enunciado:

Estado

QA

QB

S0

S1

S2

S3

Apellidos, nombre: Jimnez Marco, David

DNI:47802484-C

3/10

Fundamentos de Sistemas Digitales

Ahora represento los datos en forma de tabla porque para mi es la forma mas fcil de encontrar

las funciones de excitacin:

Entrada

X

0

0

0

0

1

1

1

1

Estado presente Estado

Qa

Qb

Qa'

0

0

1

0

1

0

1

0

0

1

1

0

0

0

0

0

1

0

1

0

1

1

1

1

futuro

Qb'

0

0

0

0

0

1

0

1

Ahora evalo las columnas Qa' y Qb' en funcin de X y su estado inicial(Qa y Qb):

Qa': Por un lado, siempre que x es 1 Qa' es igual a Qa por lo tanto es un producto lgico entre

x y Qa. >>xQa

Por otro lado, cuando x es 0 Qa' solo s verdad si Qa y Qb son mentira, por lo tanto es la suma

lgica de x,Qa y Qb negada: x+Qa+Qb o como productos lgicos xQaQb.

Ahora la suma lgica de estas dos funciones ser la funcin de excitacin que dar lugar al

circuito para controlar el primer biestable>> Qa'=(xQaQb)+xQa

Qb':Por un lado, cuando x es 0 Qb' siempre es 0 y no depende del estado inicial, por otro lado

cuando x es 1 Qb' es igual a Qb, por lo tanto no cave duda de que la funcin de excitacin es el

producto lgico entre x y Qb>> Qb'=xQb

Finalmente paso a desarrollar el esquema del bloque funcional, haciendo uso de dos biestables

D sn7474 como recomiendan en la guia de estudio:

Apellidos, nombre: Jimnez Marco, David

DNI:47802484-C

4/10

Fundamentos de Sistemas Digitales

*Ntese que he puesto las entradas preset y clear de los biestables fijas en alta, lo he hecho

porque segn la hoja de caractersticas, para cualquier otra configuracin de preset y clear la

salida deja de depender de D.

7: Esquemas capturados del simulador, primero presente los esquemas de cada uno de los

bloques funcionales por separado y despus presente el del circuito completo.

Los esquemas de los bloques funcionales por separado ya los he ido poniendo para el

apartado 6.

Esquema del circuito completo:

8: Descripcin de los parmetros de los componentes utilizados.

Reloj 555:

Ra=8k

Rb=10k

C=0,5nF

Fuente de continua= 5V

Seal de control(contador):

Clear en baja siempre.

Se coge la salida Qc.

Circuito secuencial de 2 bits:

Preset y clear en alta siempre.

Clk= un digClock con la misma frecuencia (aprox.) que el 555 que hemos

configurado(4,7us=t1=t2).

Apellidos, nombre: Jimnez Marco, David

DNI:47802484-C

5/10

Fundamentos de Sistemas Digitales

D1=(xQaQb)+xQa

D2=xQb

9: Cronograma de todas las seales (entrada, control y salida).

Reloj 555:

Generador de la seal de control:

Apellidos, nombre: Jimnez Marco, David

DNI:47802484-C

6/10

Fundamentos de Sistemas Digitales

Circuito secuencial de 2 bits:

Apellidos, nombre: Jimnez Marco, David

DNI:47802484-C

7/10

Fundamentos de Sistemas Digitales

Como se puede observar en el cronograma, nunca se llegan a dar los estados 01 y 11(S1yS3).

Con el fin de demostrar que las funciones de excitacin son correctas, voy a forzar los estados

S1 y S3 colocando un digclock con un pequeo intervalo en baja en la entrada preset de

los biestables, primero en el que genera Qb para tener 01 y despus en los dos para tener

11.

Cronograma forzando S1:

*He aadido la salida del digclock para modificar el preset para que se vea claro cuando

forzamos el estado.

Cronograma forzando S3:

Apellidos, nombre: Jimnez Marco, David

DNI:47802484-C

8/10

Fundamentos de Sistemas Digitales

Circuito completo:

Apellidos, nombre: Jimnez Marco, David

DNI:47802484-C

9/10

Fundamentos de Sistemas Digitales

10: Explicacin del funcionamiento y verificacin de que el circuito funciona de acuerdo con

las especificaciones del diseo.

Reloj 555:

Como se puede observar en su cronograma, este bloque funcional funciona correctamente

porque genera una onda cuadrada y tiene prcticamente el mismo intervalo en baja que en alta.

Generador de la seal de control:

Este bloque funcional genera una seal de 4T cambiando de estado cada cuatro pulsos de

entrada y funciona correctamente como se puede observar en su cronograma.

Secuencial de dos bits:

Consiste en generar un nuevo estado a partir del estado anterior, la seal de control y la

funcin de excitacin.

Se ha comprobado que el circuito funciona correctamente para todos los estados.

11: Explicacin de los problemas/dificultades encontrados y explicacin de la forma y el

medio por el que se han resuelto.

El primer problema con el que me he encontrado ha sido en la configuracin del reloj 555.

No entenda porqu no obtena el mismo en alta que en baja dndole los mismos valores a Ra y

Rb, lo solucion consultando en el foro dela asignatura.

Otro problema fue con el contador que siempre me daba 0 en la salida Qc, esto lo

solucion haciendo pruebas hasta que vi que dejando CLR en baja funcionando correctamente.

Por ltimo en el circuito secuencial no vea la manera de obtener los estados S1 y S3, lo

solucion consultando su hoja de caractersticas.

*********

Apellidos, nombre: Jimnez Marco, David

DNI:47802484-C

10/10

Vous aimerez peut-être aussi

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaD'EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaPas encore d'évaluation

- Diseño de circuito secuencial con contador reversible en PSpiceDocument9 pagesDiseño de circuito secuencial con contador reversible en PSpiceNemoPas encore d'évaluation

- 115 Ejercicios resueltos de programación C++D'Everand115 Ejercicios resueltos de programación C++Évaluation : 3.5 sur 5 étoiles3.5/5 (7)

- Pec2-Fsd Ion Catalin Mrejuica X8413146eDocument36 pagesPec2-Fsd Ion Catalin Mrejuica X8413146ejuanPas encore d'évaluation

- Prácticas de redes de datos e industrialesD'EverandPrácticas de redes de datos e industrialesÉvaluation : 4 sur 5 étoiles4/5 (5)

- SECUENCIALDocument2 pagesSECUENCIALMaddie ClarkPas encore d'évaluation

- Métodos Matriciales para ingenieros con MATLABD'EverandMétodos Matriciales para ingenieros con MATLABÉvaluation : 5 sur 5 étoiles5/5 (1)

- Pec2 091Document2 pagesPec2 091杨幂Pas encore d'évaluation

- 100 Circuitos de Shields para MotoresD'Everand100 Circuitos de Shields para MotoresÉvaluation : 4.5 sur 5 étoiles4.5/5 (4)

- Pec2 014Document2 pagesPec2 014Prueba PruebaPas encore d'évaluation

- Ped 2 FSDDocument13 pagesPed 2 FSDTere LuPas encore d'évaluation

- PEC2-Sistemas DigitalesDocument8 pagesPEC2-Sistemas DigitalesDavid HidalgoPas encore d'évaluation

- Guion p3Document5 pagesGuion p3estelaPas encore d'évaluation

- Sistemas Digitales Problemas 1Document25 pagesSistemas Digitales Problemas 1Ce ChavezPas encore d'évaluation

- Informe Final Lab6 Sc1Document10 pagesInforme Final Lab6 Sc1Victor yurivilca lazoPas encore d'évaluation

- Tarea 4 Circuitos Secuenciales - 243004 - 32. Yuly - Figueredo.Document22 pagesTarea 4 Circuitos Secuenciales - 243004 - 32. Yuly - Figueredo.MiGue DAzaPas encore d'évaluation

- Informe PED A-E-2 034Document10 pagesInforme PED A-E-2 034Jesús MelladoPas encore d'évaluation

- 10 Practicas de Electronica DigitalDocument42 pages10 Practicas de Electronica Digitalciudadano1729683% (12)

- Practica3 2019Document25 pagesPractica3 2019rc7pablorPas encore d'évaluation

- Laboratorio 1 Modelado y Simulacion 4278 y 4281Document7 pagesLaboratorio 1 Modelado y Simulacion 4278 y 4281Cesar BautistaPas encore d'évaluation

- Tarea 4 Circuitos Secuenciales - 243004 - 32. Yuly - Figueredo.Document22 pagesTarea 4 Circuitos Secuenciales - 243004 - 32. Yuly - Figueredo.MiGue DAza100% (1)

- Modelado de control analógico en SimulinkDocument16 pagesModelado de control analógico en SimulinkJose BaqueroPas encore d'évaluation

- Ejercicios de Simulink ModeladoDocument33 pagesEjercicios de Simulink ModeladoAna Karen Gonzalez100% (1)

- Lab1 - Circuito Temporizador - 2019-IDocument9 pagesLab1 - Circuito Temporizador - 2019-IMigvel Angel Soncco XDPas encore d'évaluation

- Aporte 1 - Momento III - Sistemas Digitales SecuencialesDocument14 pagesAporte 1 - Momento III - Sistemas Digitales SecuencialesCarl Agust SolanoPas encore d'évaluation

- Diseño de Un Controlador PID Difuso para Una Planta de Segundo Orden Sub-Amortiguada Usando LABVIEWDocument52 pagesDiseño de Un Controlador PID Difuso para Una Planta de Segundo Orden Sub-Amortiguada Usando LABVIEWcss_unac100% (2)

- Tarea 1 de Sist Digitales 2019-A (Unac)Document8 pagesTarea 1 de Sist Digitales 2019-A (Unac)C Geramias MoralesPas encore d'évaluation

- A e 1 - 091Document2 pagesA e 1 - 091MarcosPas encore d'évaluation

- EXAMEN PARCIAL DE SISTEMAS DIGITALES UNMSM 2017-1Document8 pagesEXAMEN PARCIAL DE SISTEMAS DIGITALES UNMSM 2017-1Camila Malu Miranda RomeroPas encore d'évaluation

- MultivibradoresDocument9 pagesMultivibradoresRyofenixPas encore d'évaluation

- Informe Control 2Document22 pagesInforme Control 2Sammy PerdomoPas encore d'évaluation

- Control Motor DC de Velocidad Mediante MRACDocument11 pagesControl Motor DC de Velocidad Mediante MRACAlberto Bardalez AricaPas encore d'évaluation

- Lab 1Document10 pagesLab 1Jonathan Campo JaimesPas encore d'évaluation

- Sistema lógico secuencial contador reversibleDocument9 pagesSistema lógico secuencial contador reversibleMCTLVPas encore d'évaluation

- Paper - IEEE Practica 3Document6 pagesPaper - IEEE Practica 3Aleja OrtegaPas encore d'évaluation

- Practica 2. Sistemas de ControlDocument12 pagesPractica 2. Sistemas de ControlVictor Hugo HernándezPas encore d'évaluation

- Act5 Ed1Document6 pagesAct5 Ed1KillSt4rtusPas encore d'évaluation

- Control Adaptativo Del Circuito Reductor RLC PDFDocument8 pagesControl Adaptativo Del Circuito Reductor RLC PDFArnold Rodriguez CarbajalPas encore d'évaluation

- GUÍA DE LABORATORIO 05 22040-Diego Fernando Quintanilla AyreDocument6 pagesGUÍA DE LABORATORIO 05 22040-Diego Fernando Quintanilla AyreDiego Fernando QuintanillaPas encore d'évaluation

- Practica Calificada 01-PreguntasDocument3 pagesPractica Calificada 01-PreguntasPedro Isaac Castillo TurpoPas encore d'évaluation

- Teoría Circuitos SecuencialesDocument17 pagesTeoría Circuitos SecuencialesLuisma_plasenciaPas encore d'évaluation

- Automata FinitoDocument8 pagesAutomata Finitoiceman2305Pas encore d'évaluation

- Control Adaptativo Del Circuito Reductor RLCDocument8 pagesControl Adaptativo Del Circuito Reductor RLCArnold Rodriguez CarbajalPas encore d'évaluation

- Reloj Contador DigitalDocument3 pagesReloj Contador DigitalIvan PerezPas encore d'évaluation

- Proceso de Obtención Del Controlador Por Posicionamiento de Polos Del Circuito Reductor RLCDocument9 pagesProceso de Obtención Del Controlador Por Posicionamiento de Polos Del Circuito Reductor RLCArnold Rodriguez CarbajalPas encore d'évaluation

- Tarea 4 Circuitos Secuenciales - 243004 - 32Document17 pagesTarea 4 Circuitos Secuenciales - 243004 - 32MiGue DAzaPas encore d'évaluation

- Lab3 CONTROL DIGTAL 2020ADocument3 pagesLab3 CONTROL DIGTAL 2020ACésar Jesús AlcaláPas encore d'évaluation

- Practica3 - Liliana Andrea LopezDocument3 pagesPractica3 - Liliana Andrea LopezJuan carlos Garacia mazueraPas encore d'évaluation

- Flip Flop ContadorDocument9 pagesFlip Flop ContadorAndrésCabreraSoriaPas encore d'évaluation

- CeduvirtSimulink PDFDocument33 pagesCeduvirtSimulink PDFArturo RawrPas encore d'évaluation

- Contador de 0 A 99Document11 pagesContador de 0 A 99arodi100% (1)

- Lab Informe 5.1 DigitalesDocument4 pagesLab Informe 5.1 DigitaleskarolPas encore d'évaluation

- Ej T4Document4 pagesEj T4Cris CruzPas encore d'évaluation

- Pre-Informe de Cont AdoresDocument16 pagesPre-Informe de Cont AdoresHector Yucra MattosPas encore d'évaluation

- Laboratorio - Informe - 5 Sumador y Restador CompletosDocument3 pagesLaboratorio - Informe - 5 Sumador y Restador CompletosBryan RodriguezPas encore d'évaluation

- 1IEE04 Diseño DigitalDocument12 pages1IEE04 Diseño DigitalLuis Sosa HernandezPas encore d'évaluation

- Unidad 8+9 - Problemas Electrónica DigitalDocument15 pagesUnidad 8+9 - Problemas Electrónica Digitalbemdas100% (1)

- ContadorDocument13 pagesContadorEdwin GavilanezPas encore d'évaluation

- Practica 7Document12 pagesPractica 7Sebastian MayorgaPas encore d'évaluation

- Lab10 Dispos Mendoza Rosales C15 4 CDocument11 pagesLab10 Dispos Mendoza Rosales C15 4 CJairo Hans Cardenas MauricioPas encore d'évaluation

- Capítulos 4, 5 y 6: Prueba de Evaluación A Distancia 2-1Document2 pagesCapítulos 4, 5 y 6: Prueba de Evaluación A Distancia 2-1davinci300Pas encore d'évaluation

- Concurso voluntario Resindencial Santa AguedaDocument1 pageConcurso voluntario Resindencial Santa Aguedadavinci300Pas encore d'évaluation

- Recurso de Reposicion Plusvalia Venta Con Perdida Completo No GananciaDocument5 pagesRecurso de Reposicion Plusvalia Venta Con Perdida Completo No Gananciadavinci300Pas encore d'évaluation

- Diseño ComparadorDocument1 pageDiseño Comparadordavinci300Pas encore d'évaluation

- Python para TodosDocument160 pagesPython para TodosJunior Sumosa100% (2)

- Taller TX-RX Examen Fin Carrera LLENO ESTUDIARDocument7 pagesTaller TX-RX Examen Fin Carrera LLENO ESTUDIARCristian CrsPas encore d'évaluation

- Evaluacion Informatica 1º BatanDocument2 pagesEvaluacion Informatica 1º BatanAlfredo TilleriaPas encore d'évaluation

- Informe TecnicoDocument12 pagesInforme TecnicoMayra Hidalgo0% (1)

- Conectando PIC a RS232Document42 pagesConectando PIC a RS232Epilogo LibertyPas encore d'évaluation

- PicsDocument358 pagesPicsJuan Carlos MartinPas encore d'évaluation

- Practica Modulación AMDocument8 pagesPractica Modulación AMAlfredo MorenoPas encore d'évaluation

- Modulacion en La Television y Coberura en BoliviaDocument21 pagesModulacion en La Television y Coberura en BoliviacristianPas encore d'évaluation

- Configuraciones del CI 555 como temporizador astable y monostableDocument5 pagesConfiguraciones del CI 555 como temporizador astable y monostableAdrian EsparzaPas encore d'évaluation

- Alarma Contra Ladrones Con Un SCRDocument3 pagesAlarma Contra Ladrones Con Un SCREdiPas encore d'évaluation

- Amoonsky Leddisplay Control Solution : en AliexpressDocument15 pagesAmoonsky Leddisplay Control Solution : en Aliexpressguuh2004Pas encore d'évaluation

- Engineering Electromagnetics 8th Edition-179-219.en - EsDocument41 pagesEngineering Electromagnetics 8th Edition-179-219.en - Esjulian LozanoPas encore d'évaluation

- Aplificadores de Potencia Tema (5)Document26 pagesAplificadores de Potencia Tema (5)Sumano AbrahamPas encore d'évaluation

- Ejercicio 15.19Document7 pagesEjercicio 15.19BRYAN ADRIAN CHALLCO CORONELPas encore d'évaluation

- Tema 9 Familias Logicas 2020Document92 pagesTema 9 Familias Logicas 2020Eduardo VelezPas encore d'évaluation

- HT S3500 EspanolDocument72 pagesHT S3500 EspanolOscar DanielPas encore d'évaluation

- AYF OPI 1 Introduccion Informatica Equipos Arquitectura ADocument13 pagesAYF OPI 1 Introduccion Informatica Equipos Arquitectura Aprueba123Pas encore d'évaluation

- LAB 7-2020-II - CIRCUITOS DIGITALES II - Análisis y Diseño de Circuitos Secuenciales - Modelo Tipo Moore y Modelo Tipo MealyDocument2 pagesLAB 7-2020-II - CIRCUITOS DIGITALES II - Análisis y Diseño de Circuitos Secuenciales - Modelo Tipo Moore y Modelo Tipo MealyLuis Misiyauri GutiérrezPas encore d'évaluation

- Caracterización diodos semiconductoresDocument1 pageCaracterización diodos semiconductoresJuan VargasPas encore d'évaluation

- Repaso de Electrónica I: Análisis y resolución de problemas de circuitos con transistoresDocument54 pagesRepaso de Electrónica I: Análisis y resolución de problemas de circuitos con transistoresKa RalaPas encore d'évaluation

- VSATDocument6 pagesVSATFelipe CapchaPas encore d'évaluation

- Transistor BJT como interruptor: análisis de su comportamiento en corte y saturaciónDocument5 pagesTransistor BJT como interruptor: análisis de su comportamiento en corte y saturaciónAdan Sierra LoaPas encore d'évaluation

- 1er. Laboratorio 5to Compu 2018Document13 pages1er. Laboratorio 5to Compu 2018ckdkgvfdkgPas encore d'évaluation

- Actividad Fundamental 1Document5 pagesActividad Fundamental 1René AlejandroPas encore d'évaluation

- U01 EjerciciosDocument3 pagesU01 EjerciciosAdrián SoutulloPas encore d'évaluation

- Microprocesadores y Programacion AssemblerDocument96 pagesMicroprocesadores y Programacion Assemblerjotape666100% (3)

- Introducción a las antenas y sus características fundamentalesDocument12 pagesIntroducción a las antenas y sus características fundamentalesSiranuchPas encore d'évaluation

- TDA8922CDocument40 pagesTDA8922Cgustavo de oliveiraPas encore d'évaluation

- Circuitos electrónicos protoboard y su funcionamientoDocument3 pagesCircuitos electrónicos protoboard y su funcionamientoAndré LlivicuraPas encore d'évaluation

- Examen ParcialDocument2 pagesExamen ParcialHenry FernandezPas encore d'évaluation

- Mapa Conceptual Electrónica Digital y Sus ComponentesDocument1 pageMapa Conceptual Electrónica Digital y Sus ComponentesBeatrizPas encore d'évaluation