Académique Documents

Professionnel Documents

Culture Documents

How Does Scan Work PDF

Transféré par

Are VijayDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

How Does Scan Work PDF

Transféré par

Are VijayDroits d'auteur :

Formats disponibles

HowdoesScanWork?

PreparedbyMahmutYilmaz

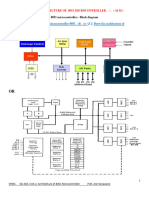

ScanChainOperationforStuckatTest

CombinationalLogic

CombinationalLogic

CombinationalLogic

CombinationalLogic

PrimaryInputs(PI)

PrimaryOutputs(PO)

ScanOut

DesignUnderTest(DUT)

ScanEnable

ScanIn

Hereisanexampledesignundertest(DUT).Ihaveshownasinglescanchain(inredcolor)inthecircuit,withScanInandScanOutports.

AssumethatallscanflipflopsarecontrolledbytheScanEnablesignal.

HowdoesScanWork?

PreparedbyMahmutYilmaz

ScanOut

DesignUnderTest(DUT)

PrimaryOutputs(PO)

CombinationalLogic

X

CombinationalLogic

X

CombinationalLogic

CombinationalLogic

PrimaryInputs(PI)

ScanEnable=1

ScanIn

100101011

Thefirstthingweshoulddoistoputthescanflipflopsintoscanmode.WedothisbyusingtheScanEnablesignal.Inthiscase,forcingScan

Enableto1enablesthescanmode.

Notethatinitiallyallthescanflopsatunknownstate(X).Forindustrialcircuits,therearearchitecturalwaystoinitializeallflipflopstoknown

statesifneeded.However,forthisparticularcase,assumethatallscanflopswereinitiallyatunknownstateX.

Wewanttoscaninthefollowingvector:100101011

HowdoesScanWork?

PreparedbyMahmutYilmaz

ScanOut

DesignUnderTest(DUT)

PrimaryOutputs(PO)

CombinationalLogic

X

CombinationalLogic

X

CombinationalLogic

CombinationalLogic

PrimaryInputs(PI)

ScanEnable=1

ScanIn

100101

Andwestartscanninginthetestvectorwewanttoapply.Inthefigureabove,youseethatthefirst3bitsarescannedin.Weshiftinasinglebit

ateachclockcycle.Usually,thescanshiftfrequencyisveryslow,muchlowerthanthefunctionalfrequencyofthecircuit.Thisfrequencyis

currentlyabout100MHzformostASICcircuits.AMDuses400MHzshiftfrequency,whichisaprettyhighvalueforthatpurpose.Ofcourse,the

higherthetestfrequency,theshorterthetesttime.

HowdoesScanWork?

PreparedbyMahmutYilmaz

DesignUnderTest(DUT)

ScanOut

PrimaryOutputs(PO)

CombinationalLogic

1

CombinationalLogic

1

CombinationalLogic

CombinationalLogic

PrimaryInputs(PI)

ScanEnable=0

ScanIn

Atthispoint,wehaveshiftedinthecompletetestvector'100101011'.Wearedonewithshiftingin.WewilldisablescanmodebyforcingScan

Enableto0.

Notethattheshiftedintestvectoriscurrentlyappliedtothecombinationallogicpiecesthataredrivenbyscanflipflops.Itmeansthat2nd,

3rd,and4thcombinationallogicblocksarealreadyforcedtestinputs.

HowdoesScanWork?

PreparedbyMahmutYilmaz

ScanOut

DesignUnderTest(DUT)

0

1

1

0

1

1

PrimaryOutputs(PO)

1

CombinationalLogic

1

CombinationalLogic

CombinationalLogic

PrimaryInputs(PI)

0

CombinationalLogic

0

ScanEnable=0

ScanIn

Thenextstepistoforceprimaryinput(PI)valuesandmeasuretheprimaryoutput(PO)values:force_PIandmeasure_PO.

Notethatfromthepreviousstep,theshiftedintestvectorwasalreadyappliedtothecombinationallogicpiecesthataredrivenbyscanflip

flops.Itmeansthat2nd,3rd,and4thcombinationallogicblockswerealreadyforcedtestinputs.Now,thesecombinationallogicblockshave

generatedtheiroutputs.

SinceweforcedvaluestoPI,the1stcombinationalblockalsohasitsoutputsready.Furthermore,theoutputsofthe4thcombinationalblockcan

nowbeobservedfromPOs.Wewillgettheoutputvaluesofcombinationalblock4bymeasuringPOs.

Fortherestofthecombinationalblocks(1,2,and3),weneedtopushtheoutputvaluesintoscanflipflopsandthenshiftthesevaluesout.

HowdoesScanWork?

PreparedbyMahmutYilmaz

DesignUnderTest(DUT)

ScanOut

1

1

0

1

1

PrimaryOutputs(PO)

1

CombinationalLogic

0

CombinationalLogic

CombinationalLogic

PrimaryInputs(PI)

0

CombinationalLogic

0

ScanEnable=0

ScanIn

Inordertopushtheoutputvaluesofcombinationalblocks1,2,and3intoscanflipflops,wehavetotogglethesystemclock.Oncewetogglethe

systemclock,allDflipflops(scanflipflops)willcapturethevaluesattheirDinput.

Inthefigureabove,thecaptureeventisshown.

HowdoesScanWork?

PreparedbyMahmutYilmaz

DesignUnderTest(DUT)

ScanOut

PrimaryOutputs(PO)

CombinationalLogic

1

CombinationalLogic

CombinationalLogic

CombinationalLogic

PrimaryInputs(PI)

ScanEnable=1

ScanIn

111100111

Now,wearereadytoshiftoutthecapturedcombinationallogicresponses.However,whiledoingthat,wewillalsoshiftinthenexttestvector.

Thenexttestvectoris'111100111'.

NotethatwehavesetScanEnablesignalbackto1toenableshifting.

HowdoesScanWork?

PreparedbyMahmutYilmaz

DesignUnderTest(DUT)

ScanOut

0111

PrimaryOutputs(PO)

CombinationalLogic

1

CombinationalLogic

1

CombinationalLogic

CombinationalLogic

PrimaryInputs(PI)

ScanEnable=1

ScanIn

11110

Hereisasnapshotoftheshiftoperation.Asyoucansee,wehaveshiftedout4bitsoftheprevioustestresponse,andatthesametimeshifted

in4bitsofthenewtestvectorinput.Thenewtestvectorbitsareshowninboldredinthefigureabove.

HowdoesScanWork?

PreparedbyMahmutYilmaz

DesignUnderTest(DUT)

ScanOut

011000111

PrimaryOutputs(PO)

CombinationalLogic

1

CombinationalLogic

1

CombinationalLogic

CombinationalLogic

PrimaryInputs(PI)

ScanEnable=1

ScanIn

Atthispoint,wehavecompletelyscannedout(shiftedout)thetestresponsefortheprevioustestvector,andalsoscannedin(shiftedin)the

newtestvectorinput.

Theprocesscontinuesinthiswayuntilallthetestvectorsareapplied.

Note:Onpage5,Imentionedforce_PIandmeasure_PO.Actually,forindustrialcircuits,force_PIandmeasure_POisnotdone.Thisisbecause

primaryinputsandoutputsareconnectedtoveryslowpads,andthesepadsarenottestedbystructuraltest.Youmayrealizethatinthiscase

the1stand4thcombinationalblockscannotbetested:1stblockcannotbetestedbecausewecannotapplyinputstoit(force_PI).4thblock

cannot be tested because we cannot check its output (measure_PO). This is usually not a problem because the circuits are surrounded by

wrapperscanflipflops.Thismeansthatthereisactuallynologicbeforethefirstlevelofscanflipflopsorafterthelastlevelofscanflipflops.

So,thecompleteDUTiscoveredbyscanflipflops.

HowdoesScanWork?

PreparedbyMahmutYilmaz

ScanChainOperationforDelayTest

Scanoperationfordelaytestisverysimilartostuckattest.Themaindifferenceisthatdelaytestneedstwoinputsinsteadofone.Thefirstinput

isalwaysthescannedinvector.Thesecondinputcanbegeneratedintwodifferentways.Eachwayhasitsownname:(1)LaunchonCapture

(LOC)orbroadsidedelaytest,(2)Launchonshift(LOS)orskewedloaddelaytest.NowIwillshowhoweachofthesemethodsworks...

(1)LaunchonCapture(Broadside)

ScanOut

DesignUnderTest(DUT)

0

PrimaryOutputs(PO)

1

CombinationalLogic

1

CombinationalLogic

CombinationalLogic

PrimaryInputs(PI)

0

CombinationalLogic

0

ScanEnable=0

ScanIn

Thisisthesamefigurethatisshownonpage5.Assumethatalltheprocessuntilthispointisthesameasstuckattest.Youscannedinthetest

vector, forced the PIs, and they created some output responses for combinational blocks. This is step 1. You have already applied your first

vectorforthedelaytest.Guesswhatisthesecondvector?Thesecondvectorwilltheoutputresponsesofthecombinationalblocks.Eachblock

willgeneratethe2ndtestvectorforthenextstage.Sincethereisnostagebeforethe1stone,youneedapplyforce_PIonemoretime.

10

HowdoesScanWork?

PreparedbyMahmutYilmaz

DesignUnderTest(DUT)

ScanOut

1 0

0 0

1

1

0

1

1

PrimaryOutputs(PO)

1 1

1

CombinationalLogic

1 0

1

CombinationalLogic

0 0

CombinationalLogic

PrimaryInputs(PI)

1 0

0

CombinationalLogic

1 1

1 0

ScanEnable=0

ScanIn

Ofcourse,inordertopushtheoutputresponsesofcombinationalblocksintoscanflipflops,weneedtotogglesystemclock.Oncewetoggle

thesystemclock(andapplythesecondPIforce),wewillgeneratethesecondtestvectorforthedelaytest,andeachcombinationalcircuitinput

will see an input state transition. The transition on scan flipflop outputs (which are inputs to the next stage combinational block) will be as

follows(startingfromtheclosesttoscaninflop):100101110>010010111

Thesecondinputvectorwillgenerateoutputresponsesjustlikethefirstone.And,youneedtocapturetheseresponsesjustlikewedidbefore,

by toggling the system clock. However, now there is a difference: You have to toggle the system clock at the real operating frequency: This

meansthattheperiodbetweenthefirstclocktoggleandsecondclocktoggleshouldbeequaltofunctionalclockperiod.Inthisway,youwill

capturethedelaytestresponsesatthefunctionalfrequency.

11

HowdoesScanWork?

PreparedbyMahmutYilmaz

HereisatimingdiagramoftheLOCprocess(source:MentorGraphicsScanandATPGProcessGuide,August2006):

Asyoucanseeabove,weshiftthetestvectorusingaslowclockfrequency.Then,wesetscanenableto0anddisablescanmode.Inthenext

step, we toggle the clock first time to launch a transition in combinational blocks. After that, we toggle the clock again (at the functional

frequency)tocapturethefinalresponsesofthecombinationalblocks.Thelaunch&captureeventshappenatfunctionalfrequency.Finally,we

shiftedoutthecapturedresponsesusingtheslowclockfrequency.

12

HowdoesScanWork?

PreparedbyMahmutYilmaz

(2)LaunchonShift(SkewedLoad)

ScanOut

DesignUnderTest(DUT)

0

PrimaryOutputs(PO)

1

CombinationalLogic

1

CombinationalLogic

CombinationalLogic

PrimaryInputs(PI)

0

CombinationalLogic

0

ScanEnable=1

ScanIn

Thisisthesamefigurethatisshownonpage5and10.So,westartasusual:Assumethatalltheprocessuntilthispointisthesameasstuckat

test.Youscannedinthetestvector,forcedthePIs,andtheycreatedsomeoutputresponsesforcombinationalblocks.ForLOS,wedon'tcare

abouttheseinitialoutputresponses.Thisisstep1.Youhavealreadyappliedyourfirstvectorforthedelaytest.Sincethereisnostagebefore

the1stone,youneedapplyforce_PIonemoretime.NotethatScanEnablesignalisstillatactivevalue1.Thisisbecausewehavenotyetdone

withshifting.Weneedtoshiftonemoretimetocreatethesecondtestvectorforthedelaytest.

13

HowdoesScanWork?

PreparedbyMahmutYilmaz

DesignUnderTest(DUT)

ScanOut

1 0

0 0

PrimaryOutputs(PO)

1 1

1

CombinationalLogic

1 0

1

CombinationalLogic

0 0

CombinationalLogic

PrimaryInputs(PI)

1 0

0

CombinationalLogic

1 1

1 0

ScanEnable=1

ScanIn 0

Notethatasmentionedinthepreviouspage,thefirstvectorofthedelaytestis(startingfromtheclosesttoscaninflop):100101110

Thesecondtestvectorisgeneratedbyshiftingonemoretime,andinsertingonemorebitfromScanIn,2ndvectoris:010010101

Justafteryoushiftthelastbit(andlaunchedatransitionbyapplyingthesecondvector),youhavetoforceScanEnableto0,andalsotogglethe

systemclockatthefunctionalfrequency.Thelasttoggleofthesystemclockwillcapturethedelaytestresponses.Finally,youwillscanoutthe

responsesasusual.

14

HowdoesScanWork?

PreparedbyMahmutYilmaz

HereisatimingdiagramoftheLOSprocess(source:MentorGraphicsScanandATPGProcessGuide,August2006):

Asyoucanseeabove,weshiftthetestvectorusingaslowclockfrequencyuntilthelastbit.ThelastshiftedbitcreatestheLaunchevent.Then,

before we toggle the system clock to capture responses, we set scan enable to 0 and disable scan mode. This has to happen very fast since

Launch & Capture event happen at high frequency. In the next step, we toggle the clock again to capture the final responses of the

combinationalblocks.Finally,weshiftedoutthecapturedresponsesusingtheslowclockfrequency.

YoucanseethatweneedtohaveaveryfastScanEnablesignalinordertouseLOS.ScanEnableshouldbeabletoswitchfrom1to0withina

veryshorttime.ThisisusuallyadifficultprocessbecauseScanEnableisnotdesignedtooperateathighfrequencies.Duetothisreason,many

industrialdesignsuseLOCinsteadofLOS.(TherearesomedesignsthatuseLOS.ThereareworkaroundstofastScanEnablesignalrequirement,

butIwillnotgointodetailsfornow.)

15

Vous aimerez peut-être aussi

- Engine Control SystemDocument21 pagesEngine Control SystemRaúl MartínezPas encore d'évaluation

- Design For Testablility Quick Reference GuideDocument22 pagesDesign For Testablility Quick Reference GuideRavichander BairiPas encore d'évaluation

- Test Point Insertion For Test Coverage Improvement in DFT - Design For Testability (DFT) .HTMLDocument75 pagesTest Point Insertion For Test Coverage Improvement in DFT - Design For Testability (DFT) .HTMLIlaiyaveni IyanduraiPas encore d'évaluation

- MCV 14 ADocument84 pagesMCV 14 AcandraPas encore d'évaluation

- Digital Circuit Testing: A Guide to DFT and Other TechniquesD'EverandDigital Circuit Testing: A Guide to DFT and Other TechniquesPas encore d'évaluation

- DFT VisionDocument18 pagesDFT VisionNaganithesh Ghattamaneni0% (1)

- Design For Testability and Design For Testability and Built Built - in Self in Self - Test TestDocument74 pagesDesign For Testability and Design For Testability and Built Built - in Self in Self - Test TestSyed Waqas Arif Shah100% (1)

- Scan Insertion Labs GuidelinesDocument12 pagesScan Insertion Labs GuidelinessenthilkumarPas encore d'évaluation

- QC Interview Qns DFTDocument15 pagesQC Interview Qns DFTdeepaPas encore d'évaluation

- On Chip Clock Controller For At-Speed TestingDocument4 pagesOn Chip Clock Controller For At-Speed TestingSachin*123Pas encore d'évaluation

- ATPG Srivatsa PPTDocument37 pagesATPG Srivatsa PPTMayur Mestry100% (1)

- Some DFT Related QuestionsDocument5 pagesSome DFT Related QuestionsAdhi SuruliPas encore d'évaluation

- Asic Design Flow:: Specification FloorplanDocument9 pagesAsic Design Flow:: Specification Floorplanp gangadhar KumarPas encore d'évaluation

- VLSI Test Principles and Architectures: Design for TestabilityD'EverandVLSI Test Principles and Architectures: Design for TestabilityÉvaluation : 4.5 sur 5 étoiles4.5/5 (4)

- DFT QuestionsDocument7 pagesDFT QuestionsTina_scribdPas encore d'évaluation

- What Is DFT in VLSIDocument22 pagesWhat Is DFT in VLSINaga Nithesh100% (4)

- SmartScan CompressionDocument5 pagesSmartScan CompressionAlexPas encore d'évaluation

- Mentorpaper 27753Document8 pagesMentorpaper 27753Sunil VermaPas encore d'évaluation

- DFT Interview QuestionsDocument5 pagesDFT Interview QuestionsHardik TrivediPas encore d'évaluation

- Morequestion On DFTDocument4 pagesMorequestion On DFTsenthilkumar100% (1)

- DFT Advantages Goals Types Cons Assignment 1Document12 pagesDFT Advantages Goals Types Cons Assignment 1senthilkumarPas encore d'évaluation

- 1 LOS and LOC in Vlsi Conference-ProceedingDocument9 pages1 LOS and LOC in Vlsi Conference-Proceedingbharghav saiPas encore d'évaluation

- Automating P1500 Wrapper CreationDocument24 pagesAutomating P1500 Wrapper CreationKrish GokulPas encore d'évaluation

- (Notes) DESIGN FOR TESTABILITYDocument34 pages(Notes) DESIGN FOR TESTABILITYsarathkumarPas encore d'évaluation

- GST200-2 1/2-Loop Addressable Fire Panel OverviewDocument82 pagesGST200-2 1/2-Loop Addressable Fire Panel OverviewgpuonlinePas encore d'évaluation

- Debugging Simulation MismatchesDocument4 pagesDebugging Simulation Mismatcheselectro123ePas encore d'évaluation

- DFT (Design For Testability)Document21 pagesDFT (Design For Testability)lavanyaPas encore d'évaluation

- Fastscan Tutorial v02Document55 pagesFastscan Tutorial v02Raghavendra MatturPas encore d'évaluation

- Digital Testing: Key Concepts of Scan-Path DesignDocument54 pagesDigital Testing: Key Concepts of Scan-Path DesignaguohaqdoPas encore d'évaluation

- Compression AssignmentDocument7 pagesCompression Assignmentpoojithas acharya100% (1)

- DFT Interview Questions - Welcome To World of VLSIDocument5 pagesDFT Interview Questions - Welcome To World of VLSINaganithesh GhattamaneniPas encore d'évaluation

- Mahitha Scan Insertion Observation PDFDocument30 pagesMahitha Scan Insertion Observation PDFPrafulani Gajbhiye100% (1)

- Tessent Samsung Han U2U18Document22 pagesTessent Samsung Han U2U18vasav1Pas encore d'évaluation

- ATPG IMP QuestionsDocument1 pageATPG IMP QuestionsMayur MestryPas encore d'évaluation

- Post-Silicon SOC: Keywords: DFT (Design For Testability), ATPG (Automatic Test Pattern Generation)Document10 pagesPost-Silicon SOC: Keywords: DFT (Design For Testability), ATPG (Automatic Test Pattern Generation)Amena FarhatPas encore d'évaluation

- Tracing CoverageDocument2 pagesTracing CoverageSrinath M SPas encore d'évaluation

- Logic BIST Case Studies and Real IssuesDocument10 pagesLogic BIST Case Studies and Real IssuesprakashthamankarPas encore d'évaluation

- An Introduction To Scan Test For Test Engineers: Part 1 of 2Document8 pagesAn Introduction To Scan Test For Test Engineers: Part 1 of 2Are VijayPas encore d'évaluation

- An Introduction To Scan Test For Test Engineers: Part 1 of 2Document8 pagesAn Introduction To Scan Test For Test Engineers: Part 1 of 2Are VijayPas encore d'évaluation

- Embedded Deterministic Test: by M. BalakrishnaDocument28 pagesEmbedded Deterministic Test: by M. Balakrishnasuryatejamula0% (1)

- DFT Interview QsDocument4 pagesDFT Interview QsHARISH DAMARLAPas encore d'évaluation

- Clock Setup and Hold Slack ExplainedDocument11 pagesClock Setup and Hold Slack Explainedmyforforum0% (1)

- DFT Interview QuestionsDocument3 pagesDFT Interview QuestionsJayesh PopatPas encore d'évaluation

- Synthesis Netlist - Library Model - Dofile CommandsDocument30 pagesSynthesis Netlist - Library Model - Dofile CommandsPrafulani GajbhiyePas encore d'évaluation

- EdtDocument10 pagesEdtjagruthimsPas encore d'évaluation

- Split Capture Cycle: During Scan Insertion - During SimulationDocument1 pageSplit Capture Cycle: During Scan Insertion - During SimulationsrikanthPas encore d'évaluation

- Frequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimeDocument15 pagesFrequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimedeepaPas encore d'évaluation

- Clock Issues in Deep Submircron DesignDocument50 pagesClock Issues in Deep Submircron Designshilpi lavaniaPas encore d'évaluation

- Design Clock Controllers For Hierarchical TestDocument2 pagesDesign Clock Controllers For Hierarchical Testneelalohith100% (1)

- MG580225 ATPG Clock Control Logic Appnote v2013 3 LPCT OCCDocument44 pagesMG580225 ATPG Clock Control Logic Appnote v2013 3 LPCT OCCchaitanyaPas encore d'évaluation

- Scan Insertion Lab ObservationsDocument3 pagesScan Insertion Lab ObservationssenthilkumarPas encore d'évaluation

- EDT Lab Observations AnalysisDocument42 pagesEDT Lab Observations Analysispoojithas acharyaPas encore d'évaluation

- Advanced Driver Assistance (ADAS) Solutions GuideDocument29 pagesAdvanced Driver Assistance (ADAS) Solutions GuideDharmody0% (1)

- Why Masking Is Needed: Scan Chain Masking in The AcompactorDocument6 pagesWhy Masking Is Needed: Scan Chain Masking in The AcompactorIlaiyaveni IyanduraiPas encore d'évaluation

- Lab5 Synopsys Tetramax DFTDocument20 pagesLab5 Synopsys Tetramax DFTJay PadaliyaPas encore d'évaluation

- VLSIGURU DFT TRAINING SCAN INSERTION LABDocument2 pagesVLSIGURU DFT TRAINING SCAN INSERTION LABsenthilkumarPas encore d'évaluation

- DFT Interview Questions and AnswersDocument3 pagesDFT Interview Questions and AnswersJayesh PopatPas encore d'évaluation

- 10 Tips For Successful Scan Design Part OneDocument6 pages10 Tips For Successful Scan Design Part Onebesha1987Pas encore d'évaluation

- Jtag PresentationDocument21 pagesJtag PresentationNivaz ChockkalingamPas encore d'évaluation

- Simulation Mismatches Can Foul Up Test-Pattern VerificationDocument6 pagesSimulation Mismatches Can Foul Up Test-Pattern VerificationAdhi SuruliPas encore d'évaluation

- An Introduction To Scan Test For Test Engineers: Part 2 of 2Document9 pagesAn Introduction To Scan Test For Test Engineers: Part 2 of 2Are VijayPas encore d'évaluation

- Stil PDFDocument9 pagesStil PDFSaurin ShahPas encore d'évaluation

- Test Power Case Study: Transition Fault Testing (LOC, LOS) Power Analysis and Reduction TechniquesDocument22 pagesTest Power Case Study: Transition Fault Testing (LOC, LOS) Power Analysis and Reduction TechniqueseashwarPas encore d'évaluation

- IJTAG Tutorial FINAL Circuitnet PDFDocument9 pagesIJTAG Tutorial FINAL Circuitnet PDFSairam Prasad MarataPas encore d'évaluation

- Segregated QuestionsDocument1 pageSegregated QuestionsdeepaPas encore d'évaluation

- Vlsiguru DFT Training Edt Insertion Lab ObservationsDocument12 pagesVlsiguru DFT Training Edt Insertion Lab ObservationssenthilkumarPas encore d'évaluation

- DFT FAQsDocument2 pagesDFT FAQsSanmati JainPas encore d'évaluation

- 15-Chapter 10 BSCAN 1500 PDFDocument81 pages15-Chapter 10 BSCAN 1500 PDFVeeranjaneyulu DhikondaPas encore d'évaluation

- Assignment 1Document3 pagesAssignment 1dheeraj.d JainPas encore d'évaluation

- DFTDocument106 pagesDFTBhatt JaydeepPas encore d'évaluation

- DFTDocument106 pagesDFTBhatt JaydeepPas encore d'évaluation

- Boundaryscan TutorialDocument58 pagesBoundaryscan TutorialAre VijayPas encore d'évaluation

- Lesson 41 PDFDocument23 pagesLesson 41 PDFAre VijayPas encore d'évaluation

- AC-JTAG Empowering JTAG Beyond Testing DC NetsDocument8 pagesAC-JTAG Empowering JTAG Beyond Testing DC NetsAre VijayPas encore d'évaluation

- EScholarship UC Item 1ww8c4b4Document129 pagesEScholarship UC Item 1ww8c4b4vaibhav.1991Pas encore d'évaluation

- Logic Synthesis 5 FSM and Retiming PDFDocument6 pagesLogic Synthesis 5 FSM and Retiming PDFAre VijayPas encore d'évaluation

- Pipeline PDFDocument2 pagesPipeline PDFAre VijayPas encore d'évaluation

- CummingsSNUG2008Boston CDCDocument56 pagesCummingsSNUG2008Boston CDCKiran RaoPas encore d'évaluation

- Lesson 41 PDFDocument23 pagesLesson 41 PDFAre VijayPas encore d'évaluation

- DFTDocument13 pagesDFTGeethanjali RajegowdaPas encore d'évaluation

- Edt GDDocument364 pagesEdt GDAre VijayPas encore d'évaluation

- DFTDocument13 pagesDFTGeethanjali RajegowdaPas encore d'évaluation

- Storage Devices 3Document29 pagesStorage Devices 3api-250921947Pas encore d'évaluation

- Combinational Logic Worksheet: Concept InventoryDocument11 pagesCombinational Logic Worksheet: Concept Inventorygiga moviesPas encore d'évaluation

- Hitachi Kokusai Electric IncDocument14 pagesHitachi Kokusai Electric IncGuruKPOPas encore d'évaluation

- HP Proliant Server - Hpasmcli (CmdrefDocument6 pagesHP Proliant Server - Hpasmcli (CmdrefVacesisoPas encore d'évaluation

- CX2020, CX2030, CX2040: ManualDocument52 pagesCX2020, CX2030, CX2040: Manualdarinel88Pas encore d'évaluation

- CT Iii 15ec301 - Set ADocument1 pageCT Iii 15ec301 - Set AskarthikpriyaPas encore d'évaluation

- Delay Calculation of Cell Based Designs For The Pre-Layout and Post-Layout Timing VerificationDocument6 pagesDelay Calculation of Cell Based Designs For The Pre-Layout and Post-Layout Timing VerificationKoush RastogiPas encore d'évaluation

- Design of Synchronous FifoDocument18 pagesDesign of Synchronous Fifoprasu440Pas encore d'évaluation

- Unit 2 Architecture of 8051 MicrocontrollerDocument25 pagesUnit 2 Architecture of 8051 Microcontrolleranil sonawanePas encore d'évaluation

- LogDocument12 pagesLogAgustín Rosero RamírezPas encore d'évaluation

- Implementing and Detecting An ACPI BIOS RootkitDocument36 pagesImplementing and Detecting An ACPI BIOS Rootkitphoebus almasyPas encore d'évaluation

- SH7020 HitachiDocument507 pagesSH7020 HitachiNoks stPas encore d'évaluation

- ENEL 111: NAND Gates and Duality Adders MultiplexersDocument6 pagesENEL 111: NAND Gates and Duality Adders MultiplexersPrafull BPas encore d'évaluation

- Appendix A: MOSFET and Logic Gate Parameters (PTM HP Models)Document26 pagesAppendix A: MOSFET and Logic Gate Parameters (PTM HP Models)Anuradha KhalkhoPas encore d'évaluation

- Question BankDocument26 pagesQuestion BankArun ChoudharyPas encore d'évaluation

- JK Flip FlopDocument7 pagesJK Flip FlopMohammad AbdulMajidPas encore d'évaluation

- Computer System Architecture Lab Report 5Document5 pagesComputer System Architecture Lab Report 5290 874Sheikh hasanPas encore d'évaluation

- 26 October - 20 November, 2009: Fpga Design & VHDL Fundamentals of FpgasDocument220 pages26 October - 20 November, 2009: Fpga Design & VHDL Fundamentals of FpgasJulio César Millán BarcoPas encore d'évaluation

- Lab 5 - Combinational Logic Modules - Adders and SubtractorsDocument13 pagesLab 5 - Combinational Logic Modules - Adders and SubtractorsSiegrique Ceasar A. JalwinPas encore d'évaluation

- CSE140L Homework5 V2 PDFDocument3 pagesCSE140L Homework5 V2 PDFramsampath78Pas encore d'évaluation

- Data Movement InstructionsDocument22 pagesData Movement InstructionsMarc Ryan SajaPas encore d'évaluation

- A Double Regulated Footer and Header Voltage Technique For Ultra-Low Power Iot SramDocument5 pagesA Double Regulated Footer and Header Voltage Technique For Ultra-Low Power Iot SramChaeyoung YooPas encore d'évaluation

- Full Adder For Low Power Applications: Mansi Jhamb, Manoj Kumar, VishalDocument6 pagesFull Adder For Low Power Applications: Mansi Jhamb, Manoj Kumar, VishalRiya JoshiPas encore d'évaluation

- Half AdderDocument16 pagesHalf AdderDemoPas encore d'évaluation