Académique Documents

Professionnel Documents

Culture Documents

Mentorpaper 84279

Transféré par

saiknaramTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Mentorpaper 84279

Transféré par

saiknaramDroits d'auteur :

Formats disponibles

WHY PCB DESIGN CONSTRAINTS

SHOULD DRIVE YOUR DESIGN FLOW

VASILY ERSHOV AND DANIT ATAR, MENTOR GRAPHICS

Why PCB Design Constraints Should Drive Your Design Flow

INTRODUCTION

Constraints derived from board fabrication and assembly requirements have always driven PCB design. These days

those constraints are overshadowed by the design requirements of differential pairs, BGAs, low voltage devices, and

high-speed parallel interfaces. These design components generate higher numbers and tighter tolerances of highspeed constraints.

Imagine a PCB designer finding missing or incorrect high-speed constraints during the late stages of layout design.

An attempt to fix the issue could start a costly redesign cycle, as routing changes for one signal could easily

introduce problems with neighboring signals. As the issue snowballs, a large amount of rework could be required,

causing delays and

additional costs.

Such scenarios show why

it is important to capture

signal integrity

requirements in the form

of high-speed constraints

as early as possible in the

PCB design cycle. These

constraints must be

rigorously maintained

throughout the design

cycle to ensure the

proper electrical

performance of the

completed board design.

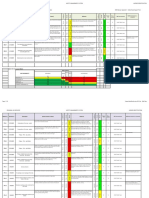

Figure 1: An independent study by the Aberdeen Group points to the importance of signal integrity

According to an

in PCB design.

independent study

performed by the

Aberdeen Group in 2010,

89% of PCB design developers and 77% of managers say that they design for technical performance, such as signal

integrity, in order to achieve manufacturability and costs goals (Figure 1).

HOW PADS CAN HELP

PADS puts constraints at the center of the design flow with a constraint management environment that is designed

to support a correct-by-design methodology.

PADS simplifies and speeds up the initial constraint-entry process with a spreadsheet-based interface and

convenient tools for reviewing constraints and performing constraint violation analysis.

All PCB design constraints are equally accessible from the schematic, layout, and routing environments. Two copies

of your constraint definitions (one for the schematic and another for layout) are kept and automatically

synchronized so that constraints entered or edited on the front end are available at the back end and vice versa.

w w w. m e nto r. co m /p a d s

Why PCB Design Constraints Should Drive Your Design Flow

EASY CONSTRAINT SETUP

One of the issues that often makes constraint setup tedious and time-consuming is a poorly designed user

interface. Having to open multiple windows without being able to see all your constraints at once, is confusing,

error prone, and forces you to manually update each constraint one at a time.

PADS provides significant benefits over traditional, dialog-based approaches by using a spreadsheet-based

approach to make it easier to capture and review constraints.

Figure 2: Constraint management can be complicated, especially with traditional dialog-based environments. A spreadsheetbased approach simplifies the entire process.

Powerful spreadsheet editing features, like multi-row/multi-column copy/paste and auto fill, allow large numbers of

constraint values to be captured or modified quickly. Opening two instances of the Constraint Manager allows

constraint values to be copied from one project to another, thus providing constraint reuse capabilities.

CONSTRAINT TYPES

There are a number of design-constraint types. Common design constraints include the following:

Length constraints impose restrictions on routing length for nets and net branches and include minimum length,

maximum length, and matched length. Minimum and maximum length constraints can be assigned to a constraint

class, individual net, or to an individual net branch (pin pair).

To define a matched-length constraint, a matched length group is required. A matched-length group includes the

group name and the group tolerance value. This approach establishes a restriction on relative lengths of group

members, i.e. the length difference between any two group members should not exceed the specified tolerance

value. A matched-length group can include either nets or net branches (pin pairs). Mixing nets and pin pairs in one

group is not allowed.

Routing constraints impose restrictions on routing layers, via usage, and trace width. Routing constraints are

defined at the net-class level and are applied to all nets in the net class. They impose restrictions on routing layer

usage, on via types allowed for routing, and on the allowed trace-width range.

w w w. m e nto r. co m /p a d s

Why PCB Design Constraints Should Drive Your Design Flow

Topology constraints restrict routing patterns for particular nets. They are used to control the routing structure

and to impose length restrictions on net branches (pin pairs).

PADS supports two topology constraints: topology type and max stub length. The topology type can be set to

three values:

MST (Minimum Spanning Tree) imposes no restrictions on the routing structure of the net

Chained restricts routing to a sequential pattern starting from the source pin and ending with the

terminator pin.

Custom indicates that the net branching is defined by a user and cant be violated during routing.

The max stub length constraint applies to nets with chained and custom topologies. It restricts the length of traces

shared by adjacent net branches. Both constraints can be specified at the constraint class level or be overwritten

for individual nets.

Figure 2: The spreadsheet view shows constraint types that can be specified for individual branches of nets with custom topology.

Shown here are matched-length restrictions and a stub-length violation.

Clearance constraints define a minimum allowed clearance between edges of two routing objects (such as traces,

pads, and copper areas) on a particular routing layer. Defining clearances is a two-stage process. First, create a set of

named clearance rules and specify the clearance values for each rule. Then, specify how to apply those rules to

particular nets referencing rules by their names. Figure 3 shows an example screen showing clearance constraints.

w w w. m e nto r. co m /p a d s

Why PCB Design Constraints Should Drive Your Design Flow

Figure 3: The clearances tab displays clearance rule values.

Differential pair constraints include trace width, differential spacing, and maximum separation distance. The

maximum separation distance, which specifies how long traces can run parallel while violating the differential

spacing value, is layer independent.

Figure 4: Differential pair constraints.

w w w. m e nto r. co m /p a d s

Why PCB Design Constraints Should Drive Your Design Flow

Power supply net constraints PADS auto

matically recognizes power supply nets based on

pre-defined standard names, such as GND, VCC,

+5V, -12V etc. In addition, you can specify power

supply nets automatically or manually. Figure 5

shows an example of automatic power supply net

creation.

CONSTRAINT GROUPINGS IMPROVE

RESULTS

Proper grouping and definition of net classes and

constraint classes in the early stages of the design

process simplify constraint definition and

management significantly. Grouped constraints

can increase layout efficiency, reducing design

time and, ultimately, saving PCB design costs.

Net classes are used to organize and speed the

definition of routing constraints for nets with

Figure 5: Automatic creation of power supply nets.

similar characteristics. For a net class you can

define the layers allowed for routing, the

corresponding trace-width range for these layers, and the via types allowed for nets in the net class. For differential

pairs, you can define a layer-dependent differential pair gap.

Constraint classes are used to organize and speed the definition of length, topology, and other constraints for nets

with similar electrical and timing properties. Although constraints assigned to a constraint class are applied

automatically to all nets in the class, particular constraint values can be customized for individual nets, pin pairs,

and differential pairs.

Figure 6: Constraint classes eliminate the need to create length and topology constraints for individual nets.

w w w. m e nto r. co m /p a d s

Why PCB Design Constraints Should Drive Your Design Flow

Differential pairs are groups of two physical nets

implementing a differential signal. As the number of differential

pairs increases, it becomes tedious to define the pairs one at a

time. PADS automates the process, making it easy to create

differential pairs quickly and easily. Net names typically follow

patterns. Use these patterns to find the net names you want to

assign as differential pairs. A list of proposed differential pairs is

displayed; uncheck the matches that you dont want to assign.

PADS instantly creates the differential pairs according to your

selections. See Figure 7 for an example.

REVIEWING CONSTRAINT VIOLATIONS

Traditionally, constraint violations are checked and reviewed

inside your layout tool. The obvious disadvantage of this

method is that electrical engineers are often not familiar with

layout tools. This is why PADS supports two ways to review

Figure 7: Create hundreds of differential pairs auto

violations: inside layout or inside the constraint management

matically by matching net name patterns.

environment. By viewing violations in the environment where

the constraints were defined, the process is accessible to

engineers and designers alike and more natural to your work flow.

The PADS constraint manager can load trace-length and via-count values from layout automatically or upon your

request. Color coding, yellow for warnings and red for violations, simplifies the detection of objects with violations.

A list of all violations can be created and analyzed (Figure 8) without scrolling through the long list of design nets.

Additionally, an ability to add comments simplifies the violation review process and improves communication

between an electrical engineer and a layout designer.

Figure 8: Condense constraint violations into a short list for easy review. Use cross-probing to locate violations on the board.

w w w. m e nto r. co m /p a d s

Why PCB Design Constraints Should Drive Your Design Flow

THE PADS SOLUTION

PADS constraint management is intuitive, quick and easy, and designed specifically to fit designers everyday work

processes. PADS unified approach ensures a correct-by-design methodology and eliminates errors caused when

separate constraint management tools are used in the schematic and layout environment. With PADS, all

constraints are synchronized and accessible throughout the flow.

Key features help you achieve first-time success:

Advanced tool tips display short videos, making PADS easy-to-learn and easy-to-use

Bi-directional cross-probing between the constraint management environment and the schematic and layout

environments display constraint data for selected objects.

Row and column filters make it easy to view specific objects and constraints for review and manipulation.

Intuitive color coding provides visual feedback of constraint violations.

Affected objects in the hierarchy are automatically updated whenever design rules are modified.

Built-in synchronization guarantees that constraints are never lost and helps to keep the electrical engineer

and layout designer in alignment.

For videos and data sheets on constraint management go to www.PADS.com

IMPORTANT NOTE: This paper describes how constraints are handled in PADS integrated projects (PADS VX and newer). For information about

constraint management in PADS netlist projects, download the white paper Overcome Challenges of Your Highly Constrained PCB

Design with PADS on www.pads.com.

For the latest product information, call us or visit: w w w . p a d s . c o m

2014 Mentor Graphics Corporation, all rights reserved. This document contains information that is proprietary to Mentor Graphics Corporation and may

be duplicated in whole or in part by the original recipient for internal business purposes only, provided that this entire notice appears in all copies.

In accepting this document, the recipient agrees to make every reasonable effort to prevent unauthorized use of this information. All trademarks

mentioned in this document are the trademarks of their respective owners.

MF 6-14

MISC-2040 w

Vous aimerez peut-être aussi

- ECE 414 Tutorial 1: Review: Random Process Fourier Transform OuetasoDocument16 pagesECE 414 Tutorial 1: Review: Random Process Fourier Transform OuetasosaiknaramPas encore d'évaluation

- Micro Programming ConceptsDocument2 pagesMicro Programming ConceptssaiknaramPas encore d'évaluation

- The Tree Data Structure: ECE 250 Algorithms and Data StructuresDocument37 pagesThe Tree Data Structure: ECE 250 Algorithms and Data StructuressaiknaramPas encore d'évaluation

- ECE 250 Algorithms and Data StructuresDocument15 pagesECE 250 Algorithms and Data StructuressaiknaramPas encore d'évaluation

- Relation-Based Operations On Containers: ECE 250 Algorithms and Data StructuresDocument23 pagesRelation-Based Operations On Containers: ECE 250 Algorithms and Data StructuressaiknaramPas encore d'évaluation

- Table 1: The Economy of Sea Island 2006 2007Document7 pagesTable 1: The Economy of Sea Island 2006 2007saiknaramPas encore d'évaluation

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Advance Concrete PDFDocument33 pagesAdvance Concrete PDFUdom RithPas encore d'évaluation

- BC 20s HandbuchDocument173 pagesBC 20s HandbuchmanoharPas encore d'évaluation

- ES - 1NZ-FXE Engine Control SystemDocument480 pagesES - 1NZ-FXE Engine Control SystemHari Prasad Ambaripeta84% (19)

- Section 1: Identification: TurpentineDocument10 pagesSection 1: Identification: TurpentineRobertPas encore d'évaluation

- Acidizing TreatmentsDocument93 pagesAcidizing TreatmentsPeña Lucia100% (2)

- FlowCon FAC6HP Instruction 04 2013Document4 pagesFlowCon FAC6HP Instruction 04 2013Jeff Anderson CollinsPas encore d'évaluation

- ARSTRUCTS Chapter1Document15 pagesARSTRUCTS Chapter1Aila MaePas encore d'évaluation

- Mercruiser Service Manual #14 Alpha I Gen II Outdrives 1991-NewerDocument715 pagesMercruiser Service Manual #14 Alpha I Gen II Outdrives 1991-NewerM5Melo100% (10)

- AY 2015-16cvbbnjDocument245 pagesAY 2015-16cvbbnjSyed Abdul AzizPas encore d'évaluation

- Tutorial Questions and Answers - 2011Document10 pagesTutorial Questions and Answers - 2011Jan ScarPas encore d'évaluation

- Light Object DSP Controller Setup GuideDocument20 pagesLight Object DSP Controller Setup Guideblondu0070% (1)

- 91 194 DCDocument57 pages91 194 DCGusdeluxePas encore d'évaluation

- Epi Gear 1 PDFDocument21 pagesEpi Gear 1 PDFTrevaughn ParkinsonPas encore d'évaluation

- Factors That Affect The Quality of CommunicationDocument9 pagesFactors That Affect The Quality of CommunicationWilliam Paras Inte100% (3)

- WinDNC - V05 - 02 English PDFDocument2 pagesWinDNC - V05 - 02 English PDFAnonymous XXKCjKnc0Pas encore d'évaluation

- Unit 5 GeosyntheticsDocument315 pagesUnit 5 Geosyntheticskowshik1737551Pas encore d'évaluation

- OML Section CDocument3 pagesOML Section Cمهند ستارPas encore d'évaluation

- Meinberg ManualDocument214 pagesMeinberg ManualLeonard NicolaePas encore d'évaluation

- Karcher K - 791 - MDocument12 pagesKarcher K - 791 - MJoão Paulo FernandesPas encore d'évaluation

- KYK CatalogueDocument94 pagesKYK Cataloguepriya kumariPas encore d'évaluation

- Procedure For Field Joint CoatingDocument10 pagesProcedure For Field Joint CoatingM Waqas HabibPas encore d'évaluation

- DPR Guidelines Oil and Gas 2019 PDFDocument114 pagesDPR Guidelines Oil and Gas 2019 PDFRubénPas encore d'évaluation

- Persuasive Speech Outline Spring 2016Document2 pagesPersuasive Speech Outline Spring 2016api-311467409Pas encore d'évaluation

- Forged - Pipe - Fittings - ANSI - B-16.11 PDFDocument1 pageForged - Pipe - Fittings - ANSI - B-16.11 PDFImran KamalPas encore d'évaluation

- (Communication) (English E-Book) Scientific Writing PDFDocument5 pages(Communication) (English E-Book) Scientific Writing PDFIrinaPas encore d'évaluation

- Head & Combo: Manual 1.0Document11 pagesHead & Combo: Manual 1.0NielsvdorstPas encore d'évaluation

- Azimuthal Instabilities in Annular Combustion ChambersDocument11 pagesAzimuthal Instabilities in Annular Combustion ChambersLarry SmithPas encore d'évaluation

- Chapter 3Document5 pagesChapter 3Ngozi OddiriPas encore d'évaluation

- Hazard-Identification Dec 2015Document22 pagesHazard-Identification Dec 2015Dumitru EninPas encore d'évaluation

- PSC Girder MethodologyDocument12 pagesPSC Girder MethodologySaurabh KumarPas encore d'évaluation