Académique Documents

Professionnel Documents

Culture Documents

Vlsi Design: Time: 3 Hours Total Marks: 100

Transféré par

Shivani Varshney0 évaluation0% ont trouvé ce document utile (0 vote)

25 vues4 pagesThis document appears to be an examination paper for a seventh semester B.Tech course in VLSI Design. It contains 5 questions with multiple parts each. Students are instructed to attempt any 2 parts from each question. The questions cover topics like the differences between discrete component and integrated circuits, MOS transistor working principles, CMOS inverter design, multiplexer design, memory cell designs, VLSI design styles, testing approaches, and CAD tools used in VLSI design.

Description originale:

Titre original

2006-07.pdf

Copyright

© © All Rights Reserved

Formats disponibles

PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentThis document appears to be an examination paper for a seventh semester B.Tech course in VLSI Design. It contains 5 questions with multiple parts each. Students are instructed to attempt any 2 parts from each question. The questions cover topics like the differences between discrete component and integrated circuits, MOS transistor working principles, CMOS inverter design, multiplexer design, memory cell designs, VLSI design styles, testing approaches, and CAD tools used in VLSI design.

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

25 vues4 pagesVlsi Design: Time: 3 Hours Total Marks: 100

Transféré par

Shivani VarshneyThis document appears to be an examination paper for a seventh semester B.Tech course in VLSI Design. It contains 5 questions with multiple parts each. Students are instructed to attempt any 2 parts from each question. The questions cover topics like the differences between discrete component and integrated circuits, MOS transistor working principles, CMOS inverter design, multiplexer design, memory cell designs, VLSI design styles, testing approaches, and CAD tools used in VLSI design.

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 4

Printed

EC-703

Pages - 4

(Following Paper ID and Roll No. to be filled in your Answer Book)

I

Roll No.

B.Tech.

SEVENTH

SEMESTER EXAMINATION,

2006-07

VLSI DESIGN

Total Marks : 100

Time : 3 Hours

Note:

1.

2.

(i)

Attempt

(ii)

All questions carry equal marks.

(iii)

In case of numerical problems assume data wherever

not provided.

(iv)

Be precise in your answer.

Attempt

ALL questions.

any two parts of the following:

(10x2=20)

(a)

Differentiate between a discrete component circuit

and an Integrated circuit. Classify the ICs on the

basis of scale of integration.

(b)

Write a comparison

technologies.

(c)

Explain the process of PHOTOLITHOGRAPHY

with the help of suitable diagram.

Attempt

(a)

EC - 703

among

TTL, ECL and IlL

any two parts of the following:

(10x2=20)

Calculate the threshold voltage VIa at VSB =0 for

a polysilicon gate n-channel MOS transistor, with

[Turn Over

..

the following ftarameters;

substrate doping

density NA = 10 61cm3. Polysilicon gate doping

density No = 2 X 10181cm3 gate oxide thickness

tax = 5000A and oxide interface charge density

Nox=4Xl01O/cm2.

3.

(b)

Explain working principle of NMOS transistor

with the help of its cross sectional view and VI

characteristics.

(c)

Explain constant field scaling model of MOS and

illustrate

its effect

on the following

electrical parametery : Threshold voltage, power

dissipation, Drain current and delay.

Attempt allY two parts of the following:

(a)

(b)

Design a CMOS inverter under following heads:

(i)

circuit diagram

(ii)

stick diagram

(iii)

layout based an LAMBDA based design

ruler

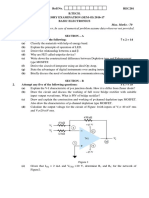

Calculate channel resistance of the following

CMOS inverter and calculate overall delay of the

circuit when two inverters based on 5 fJ.m

technology are cascaded (shown in fig.) typical

sheet resistances

of MOS layers for 5 fJ.m

technology is shown in the following table.

Layer

Sheet resistance in n/o

for 5 fJ.m technology

n mas channel

104

p mas channel

EC-703

(lOx2=20)

2.5 x 104

--.

';'

Typical area capacitance value for MOS layers is

as follows for (5 fLm technology)

Layers

Area capacitance

Gate to channel

4 (1.0)

Metal 1 to substrate

0.3 (0.075)

Metal 2 to substrate

0.2 (0.05)

in

PF x 10-4/mm2

VDD

r/r-~

CMOS inverter

(c)

'-../

4.

Draw and explain equivalent

circuit of SPICE

model of level 2 of MOS transistor used for circuit

simulation.

Attempt

(a)

EC - 703

any two parts of the following:

(10x2=20)

Design a 4 : 1 multiplexer

underfollowing

(i)

Block level design

verification.

and VHDL code for its

(ii)

Logic level design

verification

and VHDL code for its

heads:

[Turn Over

. (b)

(c)

5.

Draw and explain operation of S~AM cell and

EEROM cell.

Discuss about different VLSI design styles.

Attempt any two parts of the following:

(10x2=20)

(a)

What is VLSI testing? Explain different types of

fault models used in VLSI testing.

(b)

Explain programmable

VLSI design style.

(c)

Discuss about the use of CAD softwares used for

different steps of VLSI design.

-000-

EC - 703

gate array design style of

"-

Vous aimerez peut-être aussi

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyD'EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyPas encore d'évaluation

- r05410207 Vlsi DesignDocument7 pagesr05410207 Vlsi Design9010469071Pas encore d'évaluation

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysD'EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysPas encore d'évaluation

- J09BE7 ETRX BvlsiDocument1 pageJ09BE7 ETRX Bvlsianiket-mhatre-164Pas encore d'évaluation

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionD'EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionPas encore d'évaluation

- Jntu Vlsi Systems DesignDocument5 pagesJntu Vlsi Systems Design9010469071Pas encore d'évaluation

- Gujarat Technological University: InstructionsDocument2 pagesGujarat Technological University: InstructionsArchana TrivediPas encore d'évaluation

- Q Paper 09ec61 May June 2012Document2 pagesQ Paper 09ec61 May June 2012Bhaskar MishraPas encore d'évaluation

- Subject: Analog and Mixed Signal Ic DesignDocument3 pagesSubject: Analog and Mixed Signal Ic DesignchandravinitaPas encore d'évaluation

- B. Tech.: Time: Hours) (Total Marks: 100 Note: Attempt All Questions, All Questions Carry Equal MarksDocument4 pagesB. Tech.: Time: Hours) (Total Marks: 100 Note: Attempt All Questions, All Questions Carry Equal MarksRavindra KumarPas encore d'évaluation

- Set No. 1: M Ds GS TN 2 DSDocument6 pagesSet No. 1: M Ds GS TN 2 DSSRINIVASA RAO GANTAPas encore d'évaluation

- EVL562 ECL523 Digital IC Design Dec2020Document3 pagesEVL562 ECL523 Digital IC Design Dec2020akash rawatPas encore d'évaluation

- Roll No.: B. TechDocument3 pagesRoll No.: B. TechShivani VarshneyPas encore d'évaluation

- EC2354 - Nov 2011 - AU QP Anna University Exams - VLSIDocument3 pagesEC2354 - Nov 2011 - AU QP Anna University Exams - VLSISHARANYAPas encore d'évaluation

- Vlsi ModuleDocument2 pagesVlsi ModuleAshwini kumarPas encore d'évaluation

- Vlsi BestDocument4 pagesVlsi Bestkunjanb11Pas encore d'évaluation

- Ec 703 2019-20Document2 pagesEc 703 2019-202000520310061Pas encore d'évaluation

- Explain Small Signal AC Characteristics of MOSFET With Its Design EquationsDocument11 pagesExplain Small Signal AC Characteristics of MOSFET With Its Design EquationsradhikasontakayPas encore d'évaluation

- Kec 072 - CT2Document10 pagesKec 072 - CT22000520310061Pas encore d'évaluation

- Eec-703 Vlsi Design 2012-13Document4 pagesEec-703 Vlsi Design 2012-13kd17209Pas encore d'évaluation

- 6 Vlsi DesignDocument6 pages6 Vlsi Designapi-3704956Pas encore d'évaluation

- MJ12 PDFDocument6 pagesMJ12 PDFSarika VadivelanPas encore d'évaluation

- Question Bank For Mid-2 r13 (Vlsi) .Document6 pagesQuestion Bank For Mid-2 r13 (Vlsi) .rppvchPas encore d'évaluation

- 2023 Midterm PapersDocument5 pages2023 Midterm Papers40 XII-B Satyam SinhaPas encore d'évaluation

- A1429 VlsiDocument8 pagesA1429 VlsiratnamsPas encore d'évaluation

- ELX304 Ref ExamDocument13 pagesELX304 Ref ExamNadeesha Bandara0% (1)

- Analog - RF VLSI Design (ECE 503) (Makeup) PDFDocument2 pagesAnalog - RF VLSI Design (ECE 503) (Makeup) PDFRahul PinnamaneniPas encore d'évaluation

- Rr320405 Vlsi DesignDocument6 pagesRr320405 Vlsi DesignSrinivasa Rao GPas encore d'évaluation

- Jntuworld: Electrical and Electronics EngineeringDocument30 pagesJntuworld: Electrical and Electronics EngineeringRajeev BujjiPas encore d'évaluation

- Btech Ee 6 Sem Conventional and Cad of Electrical Machines Nee 023 2016 17Document2 pagesBtech Ee 6 Sem Conventional and Cad of Electrical Machines Nee 023 2016 17Tanisha ShahPas encore d'évaluation

- Ec 302Document1 pageEc 302gauravkumartech0Pas encore d'évaluation

- Ec 1401 Vlsi DesignDocument2 pagesEc 1401 Vlsi DesignsubhazPas encore d'évaluation

- Assignment Questions ECE VLSI NITTDocument6 pagesAssignment Questions ECE VLSI NITTAkhilGovindPas encore d'évaluation

- Basic Electronics Engineering I SemDocument3 pagesBasic Electronics Engineering I Semshubhambani45Pas encore d'évaluation

- EC Con-2Document8 pagesEC Con-2Prabhu SakinalaPas encore d'évaluation

- NR-221103 - Digital Circuits Design and ApplictionDocument5 pagesNR-221103 - Digital Circuits Design and ApplictionSrinivasa Rao G100% (1)

- Integrated Circuits Nec 501 PDFDocument2 pagesIntegrated Circuits Nec 501 PDFSaurabhPas encore d'évaluation

- EESB423 Sem1 1314 Assignment2Document3 pagesEESB423 Sem1 1314 Assignment2Shamraj KunnasagarPas encore d'évaluation

- 2 Ec2354 - Vlsi DesignDocument2 pages2 Ec2354 - Vlsi Designkrishna_ScrbidPas encore d'évaluation

- Gujarat Technological University: InstructionsDocument2 pagesGujarat Technological University: InstructionsPritesh SaxenaPas encore d'évaluation

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayPas encore d'évaluation

- M.E. (VLSI & Embedded System) : Asic Design and Modelling (2008 Course)Document9 pagesM.E. (VLSI & Embedded System) : Asic Design and Modelling (2008 Course)Manu SeaPas encore d'évaluation

- CS 801D PDFDocument4 pagesCS 801D PDFarnab paulPas encore d'évaluation

- DSP Integrated Circuits 3Document3 pagesDSP Integrated Circuits 3brindkowsiPas encore d'évaluation

- General Instructions To The CandidateDocument4 pagesGeneral Instructions To The Candidateapurv shuklaPas encore d'évaluation

- Cat1Document3 pagesCat1Manoharan KandasamyPas encore d'évaluation

- EEE312 EEE282 Lab4 Spring2015 PDFDocument5 pagesEEE312 EEE282 Lab4 Spring2015 PDFvognarPas encore d'évaluation

- 2008 Anna UniversityDocument1 page2008 Anna UniversitysasitsnPas encore d'évaluation

- Kec 072 2023Document2 pagesKec 072 20232000520310061Pas encore d'évaluation

- E - C Etj - .::B) : '/' '"Dem09-Dd - (A) Con. T? .14-09. 0As/C3 - O - /JL-S 'Document2 pagesE - C Etj - .::B) : '/' '"Dem09-Dd - (A) Con. T? .14-09. 0As/C3 - O - /JL-S 'aniket-mhatre-164Pas encore d'évaluation

- VLSI Design 2010 Sept CUSATDocument1 pageVLSI Design 2010 Sept CUSATvineethvrr5948Pas encore d'évaluation

- Previous PapersDocument12 pagesPrevious PapersKaran SanaPas encore d'évaluation

- Time: 3 Hours Full Marks: 70Document3 pagesTime: 3 Hours Full Marks: 70pikluPas encore d'évaluation

- Semester-1 - Chemistry Stream - Mid+end PaperDocument15 pagesSemester-1 - Chemistry Stream - Mid+end PaperGopiPas encore d'évaluation

- VLSIDesignDocument5 pagesVLSIDesignVenkatesh KolatiPas encore d'évaluation

- Question Bank PDFDocument2 pagesQuestion Bank PDFTina TaylorPas encore d'évaluation

- ES PaperDocument22 pagesES PaperRaghu Nath SinghPas encore d'évaluation

- PD ASSIGNMENT 01/12/2018: Two Major MOSFET Capacitance Are Cgs & Cgd. Both Have Overlap ComponentsDocument3 pagesPD ASSIGNMENT 01/12/2018: Two Major MOSFET Capacitance Are Cgs & Cgd. Both Have Overlap ComponentsRamakrishnaRao SoogooriPas encore d'évaluation

- PDC Sdec09Document8 pagesPDC Sdec09Lavanya_123Pas encore d'évaluation

- Time: 3 Hours Max. Marks: 70 Note: Be Precise in Your Answer. in Case of Numerical Problem Assume Data Wherever Not ProvidedDocument2 pagesTime: 3 Hours Max. Marks: 70 Note: Be Precise in Your Answer. in Case of Numerical Problem Assume Data Wherever Not Providedpcjoshi02Pas encore d'évaluation

- Geometry Questions Solutions PDFDocument3 pagesGeometry Questions Solutions PDFShivani VarshneyPas encore d'évaluation

- Geometry Questions PDFDocument2 pagesGeometry Questions PDFShivani VarshneyPas encore d'évaluation

- Geometry Questions Solutions PDFDocument1 pageGeometry Questions Solutions PDFShivani VarshneyPas encore d'évaluation

- Geometry Questions PDFDocument1 pageGeometry Questions PDFShivani VarshneyPas encore d'évaluation

- Elitmus Sample Model Question Paper With AnswersDocument21 pagesElitmus Sample Model Question Paper With AnswersTechnocrawlPas encore d'évaluation

- Cloud Computing Era PracticeDocument75 pagesCloud Computing Era PracticeSiddarth MadanPas encore d'évaluation

- CD Tut2Document2 pagesCD Tut2Shivani VarshneyPas encore d'évaluation

- Asp NetDocument40 pagesAsp NetsatishPas encore d'évaluation

- Elitmus Practice Sets - Fully SolvedDocument52 pagesElitmus Practice Sets - Fully SolvedSatya Murti100% (4)

- Benchmarking Unit-Iv (Nhu-601) PDFDocument12 pagesBenchmarking Unit-Iv (Nhu-601) PDFShivani VarshneyPas encore d'évaluation

- AUGMENTED REALITYVersion1Document33 pagesAUGMENTED REALITYVersion1Shivani VarshneyPas encore d'évaluation

- Roll No.: B. TechDocument3 pagesRoll No.: B. TechShivani VarshneyPas encore d'évaluation

- Types of DWDMDocument21 pagesTypes of DWDMKoshy GeojiPas encore d'évaluation

- PvMini Install Manual PDFDocument10 pagesPvMini Install Manual PDFCARLOS ANDRES SARMIENTO CUEVASPas encore d'évaluation

- Features: Intel Pentium M Uno W/4 X Pci, 1 X PC Card SlotDocument2 pagesFeatures: Intel Pentium M Uno W/4 X Pci, 1 X PC Card SlotSentaPas encore d'évaluation

- Sense Point XCD Technical ManualDocument80 pagesSense Point XCD Technical ManualKarina Jimenez VegaPas encore d'évaluation

- Rental RatesDocument1 pageRental RatesZigundPas encore d'évaluation

- Sedecal sm0510R4Document90 pagesSedecal sm0510R4PatriciaAraujo100% (3)

- Glider ASW28Document4 pagesGlider ASW28Marco OlivettoPas encore d'évaluation

- Linux Interview Questions 1-1Document9 pagesLinux Interview Questions 1-1kalaiarasan tkPas encore d'évaluation

- 4 Bit Multiplier Using StructuralDocument7 pages4 Bit Multiplier Using Structuralvinayaka11Pas encore d'évaluation

- Sample Configuration Nexus 5000 and Nexus 2000 With FEXDocument11 pagesSample Configuration Nexus 5000 and Nexus 2000 With FEXgochorneaPas encore d'évaluation

- Introduction To NI ELVISDocument136 pagesIntroduction To NI ELVISchrsolvegPas encore d'évaluation

- VX600 All in One Controller Specifications V1.3.1 PDFDocument11 pagesVX600 All in One Controller Specifications V1.3.1 PDFCV KHALIFPas encore d'évaluation

- 6 2 09Document4 pages6 2 09nirishkumarPas encore d'évaluation

- DDI0464F Cortex A7 Mpcore r0p5 TRMDocument269 pagesDDI0464F Cortex A7 Mpcore r0p5 TRMgem1144aaPas encore d'évaluation

- 01 Concepts PDFDocument30 pages01 Concepts PDFdarwinvargas2011Pas encore d'évaluation

- Abb MCBDocument96 pagesAbb MCBbrightstardustPas encore d'évaluation

- The 5 Generations of ComputersDocument23 pagesThe 5 Generations of ComputersRoshan ChaudharyPas encore d'évaluation

- List of Book - Computer ScienceDocument3 pagesList of Book - Computer Sciencelibranhitesh7889100% (1)

- Philips Mcm355Document31 pagesPhilips Mcm355nikola1660100% (1)

- 11gen 1Document106 pages11gen 1mypc88326Pas encore d'évaluation

- 1.5.4 Translator SoftwareDocument4 pages1.5.4 Translator SoftwareqamarmemonPas encore d'évaluation

- RAGU Z720: User's GuideDocument1 pageRAGU Z720: User's GuidecomphomePas encore d'évaluation

- Step by Step Installation Process of UG NX 7Document8 pagesStep by Step Installation Process of UG NX 7Ravi GavkarePas encore d'évaluation

- KM-2810-2820 Aviso MemoriasDocument17 pagesKM-2810-2820 Aviso Memoriasodd100% (1)

- 9495510-Honda Xr80r Xr100r Service Repair Manual 1985-1997 Xr80 Xr100Document168 pages9495510-Honda Xr80r Xr100r Service Repair Manual 1985-1997 Xr80 Xr100Douglas O'Neil33% (6)

- Parts CatalogDocument200 pagesParts CatalogAugusto RezendePas encore d'évaluation

- SHIMADZU Specification AA-7000 FlameDocument7 pagesSHIMADZU Specification AA-7000 FlameSaifuddinPas encore d'évaluation

- Fpga Class 2Document47 pagesFpga Class 2lowtecPas encore d'évaluation

- 140u sg004 - en eDocument44 pages140u sg004 - en eGomz RubPas encore d'évaluation

- ST Ceph Storage Intel Configuration Guide Technology Detail f11532 201804 enDocument23 pagesST Ceph Storage Intel Configuration Guide Technology Detail f11532 201804 enPaul R. MessinaPas encore d'évaluation