Académique Documents

Professionnel Documents

Culture Documents

Sistemas Microprocesados

Transféré par

Miguel Calle RomeroTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Sistemas Microprocesados

Transféré par

Miguel Calle RomeroDroits d'auteur :

Formats disponibles

SISTEMAS

REALIZADO POR:

MIGUEL CALLE ROMERO

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

Contenido

1.

2.

3.

4.

CAPITULO I...............................................................................................................................................2

1.1

Introduccin..........................................................................................................................................2

1.2

Que es un computador?..................................................................................................................3

1.3

Arquitectura del Sistema Microprocesador.................................................................................3

1.4

Descripcin de bloques funcionales, memorias, perifricos......................................................5

1.5

Sistemas de Memoria......................................................................................................................7

CAPITULO II..............................................................................................................................................8

2.1

Introduccin al micro controlador AVR ATMEGA164P............................................................8

2.2

Diagrama de bloques del Atmega164P..........................................................................................9

2.3

Distribucin de pines.....................................................................................................................10

2.4

Descripcin de Pines......................................................................................................................11

2.5

AVR CPU Core................................................................................................................................13

2.6

Registro de Estado.........................................................................................................................15

2.7

Modelo de programacin..............................................................................................................15

2.8

Operaciones en los 32 Registros..................................................................................................17

2.9

Modos de direccionamiento e instrucciones de movimientos de datos.................................17

2.10

Instrucciones lgicas-aritmticas................................................................................................17

2.11

Instrucciones de testeo de bits.....................................................................................................17

2.12

Instrucciones de salto....................................................................................................................17

2.13

Subrutinas.......................................................................................................................................17

Capitulo III...............................................................................................................................................17

3.1

Configuracin y manejo de prticos............................................................................................17

3.2

Interrupciones................................................................................................................................17

3.3

Conversin A/D..............................................................................................................................17

3.4

Timmers..........................................................................................................................................17

3.5

Comunicacin Serial......................................................................................................................17

BIBLIOGRAFIA.......................................................................................................................................18

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

1. CAPITULO I

1.1

Introduccin.

Variables:

o Discretas

o Continuas:

Analgica: Una variable continua que se

representa proporcionalmente por medio

de otra variable contina.

Digital: Necesito 2 cosas; Dgitos que no

son

necesariamente

nmeros

una

referencia.

Para realizar la representacin digital pasamos por un proceso de discretizacion.

En este proceso se comenten errores:

1. Error de cuantizacion o discretizacion, es aceptable por Ejm, cuando la

escala no da un valor exacto, es inevitable pero aceptable, y tiene que ver con

la seleccin de la referencia.

Hay que tener en cuenta la apreciacin que va a tener el instrumento.

2. Incertidumbre de la referencia: Como saber que la referencia que utilizo es

realmente la referencia exacta.

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

P ro c e s o

M ic r o p ro c e s a

dor

Representacin digital es ms robusta.

Se utiliza el sistema binario por su simplicidad y su inmunidad al ruido.

1.2

Que es un computador?

Un computador es una maquina cuya funcionalidad depende de una

secuencia de instrucciones guardadas en un almacn.

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

1.3

Arquitectura del Sistema Microprocesador.

1. Microprocesador.

Traer, decodificar, ejecutar instrucciones.

Controlar y temporizar todos los otros bloques.

Ciclo de Van Neumann.

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

Fetch

(Buscar

y traer)

Ejecutar

Decodific

ar

Fetch: Recuperar o extraer la informacin (Instrucciones) desde memoria y

llevarla al microcontrolador.

Decode: Decodificacin de las instrucciones.

Execute: Ejecucin de las instrucciones.

2. Memoria.

Funcin principal es almacenar o contener el programa

Contiene datos.

3. Dispositivos E/S

Relacionarse con el medio externo

4. Buses

Camino para el intercambio de informacin.

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

1.4

Descripcin de bloques funcionales, memorias, perifricos.

Bus de direcciones: Es un bus de un solo sentido (Lneas unidireccionales)

a travs del cual el microprocesador enva un cdigo de direccin a una memoria o

dispositivo externo.

La capacidad mxima de acceso a memoria del uP = nmero de lneas.

Ejemplo:

16 lneas = 216=65.536 posiciones= 64K

32 lneas = 232 = 4.294.467.296=4 Gigas (Pentium)

Zn = 2n; donde n: nmero de lneas.

Bus de datos: Es un bus de dos sentidos es decir lneas bidireccionales

(entrada/salida) empleadas para el envo y recepcin de datos entre el uP y los

dems elementos del sistema.

Tamao de palabra = # bits que procesa la CPU = # lneas que tiene el bus.

Potencia del uP A mayor tamao del bus mayor cantidad de informacin

puede ser enviada y recibida a la vez.

Bus de control: La funcionalidad de este bus es controlar y coordinar las

acciones de los elementos del sistema. Formado por lneas unidireccionales que

entran en la CPU y otras que salen de ella.

Seales de lectura/escritura

Ciclos de espera.

Interrupciones.

Sistemas de Entrada/Salida (I/O): Conjunto de circuitos electrnicos

que permiten el flujo de informacin entre las distintas unidades del sistema con el

medio externo por medio de perifricos.

6

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

Perifricos: Dispositivos encargados de la comunicacin entre el sistema y el

usuario y del almacenamiento de informacin.

Unidad de memoria: Dispositivo que almacenan las instrucciones de los

programas, los datos y resultados temporales que se van procesando.

Tipos de memoria:

a) Memorias de solo lectura.

ROM (Read Only Memory): Empleada principalmente en

microprogramacin de sistemas.

PROM (Programmable ROM): El proceso de escritura es

electrnico. Se puede grabar posteriormente a la fabricacin del

chip, a diferencia de las anteriores que se graba durante la

fabricacin. Permite una nica grabacin y es ms cara que la

ROM

b) Memorias de sobre todo lectura.

EPROM (Erasable PROM): Se puede escribir varias veces de

forma elctrica, sin embargo, el borrado de los contenidos es

completo y a traces de la exposicin a rayos ultravioletas (de

esto s que se suele tener una pequea ventanita en el chip).

EEPROM

(Electrically

EPROM):

Se

puede

borrar

selectivamente byte a byte con corriente elctrica. Es ms cara

que la EPROM.

Memoria Flash: Est basada en la memoria EEPROM pero

permite el borrado bloque a bloque y es ms barata y densa.

c) Memorias de Lectura/Escritura.

DRAM (Dynamic Random Access Memory): Los datos de

almacenan como en la carga de un condensador. Tiende a

7

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

descargarse y, por lo tanto, es necesario un proceso de refresco

peridico. Son ms simples y baratas que las SRAM.

SRAM (Static Random Access Memory): Los datos se

almacenan formando biestables, por lo que no requiere refresco.

Igual que DRAM es voltil. Son ms rpidas que las DRAM y

ms caras.

La memoria tambin puede ser clasificada como:

No voltil: Aquella memoria que al apagarla no pierde la informacin almacenada.

Ejm: ROM.

Voltil: Memoria que pierde la informacin al interrumpirse el flujo elctrico.

Ejm: RAM

1.5

Sistemas de Memoria.

Lneas de Direccin (Bus de direccin): Se encarga de direccionar la

informacin dentro de una memoria.

Direccin: Es la posicin de Identificacin de una palabra en memoria.

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

Longitud/Tamao de la Palabra: Cantidad de bits que puede almacenar cada

posicin.

Organizacin de la Memoria: Est determinado por el nmero de palabras

que es capaz de almacenar la memoria (m) y el tamao de cada palabra (n).

Formato = m x n.

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

2. CAPITULO II

2.1

Introduccin al micro-controlador AVR ATMEGA164P

Microcontrolador de 8 bits (Toda las estructuras internas son de 8 bits)

Arquitectura RISC.

Fully Static.

JTAG Port.

WatchDog Timer.

Brown Out Detection.

Arquitectura Harvard.

Es utilizado para aplicaciones embebidas.

Integrado incluye microprocesador, memoria y perifricos en un solo

chip.

10

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

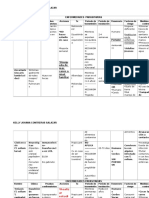

2.2

Diagrama de bloques del Atmega164P

Los 32 registros estn directamente relacionados con la ALU (admite 2

registros independientes al ejecutarse una instruccin en un ciclo de maquina)

Memoria:

16K de memoria Flash con capacidad de lectura y escritura (M. de

Programa)

1K memoria SRAM (Datos)

512 bytes de memoria EEPROM (Datos)

Perifricos:

32 pines de E/S para propsito general.

32 registros de propsito general.

Contador en tiempo real (RTC).

Sistema de interrupciones.

11

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

3 Temporizadores/Contadores (con modo comparacin y PWM).

Conversor Anlogo/Digital de 10 bits-8canales con opcin de entrada

diferencial.

Comunicaciones Serial: USART (Universal Synchronous/Asynchronous

Receiver/Transmitter), SPI (Serial Peripheral Interface), TWI.

WatchDog Timer programable con oscilador interno.

Interface de prueba JTAG

6 Modos Sleep: Detener reloj y se quede como congelado el uP, y puedo

volver a activarlo.

Voltaje al que trabaja: 1.8 a 5.5 V

El modo Power-down guarda el contenido de los registros pero paraliza al

oscilador, desactiva todas las otras funciones de chip hasta la prxima interrupcin

o mediante reseteo por hardware. En el modo Power-save, el reloj asincrnico

continua corriendo, permitiendo tener actualizado el reloj mientras el resto del

dispositivo est descansando. El modo Reduccin de ruido del ADC detiene al CPU

y a todos los mdulos de E/S excepto al Reloj asincrnico y al ADC, para minimizar

el ruido durante la conversin.

2.3

Distribucin de pines.

12

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

2.4

Descripcin de Pines.

2.4.1 VCC

Alimentacin de voltaje digital.

2.4.2 GND

Tierra

2.4.3 Port A (PA7-PA0)

El puerto A sirve como entradas analgicas para el ADC. El puerto A tambin

sirve como puerto bidireccional de 8 bits con resistencia interna de pull-up

(seleccionables para cada bit). Los pines del puerto A estn en tri-estado cuando las

condiciones de reset estn activadas o cuando el reloj no est corriendo.

13

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

2.4.4 Port B (PB7-PB0)

El puerto B es un puerto bidireccional de 8 bits de E/S con resistencias

internas de pull up (seleccionables para cada bit). Los pines del puerto B estn en

tri-estado cuando las condiciones de reset estn activadas o cuando el reloj no est

corriendo.

2.4.5 Port C (PC7:PC0)

El puerto C es un puerto bidireccional de 8 bits de E/S con resistencias

internas de pull up (seleccionables para cada bit). Los pines del puerto C estn en

tri-estado cuando las condiciones de reset estn activadas o cuando el reloj no est

corriendo.

El puerto C tambin sirve para las funcione de Interfaz del JTAG.

2.4.6 Port D (PD7-PD0)

El puerto D es un puerto bidireccional de 8 bits de E/S con resistencias

internas de pull up (seleccionables para cada bit). Los pines del puerto D estn en

tri-estado cuando las condiciones de reset estn activadas o cuando el reloj no est

corriendo.

2.4.7 RESET

Entrada del Reset. Un pulso de niel bajo en este pin por periodos de pulso

mnimo genera un reset, siempre y cuando el reloj no este corriendo.

2.4.8 XTAL1

Entrada para el amplificador del oscilador invertido y entrada para el circuito

de operacin del reloj interno.

2.4.9 XTAL2

Salida del Oscilador amplificador de salida.

2.4.10

AVCC

14

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

AVCC es la alimentacin de voltaje para el pin del puerto F y el ADC. Este

debe ser conectado externamente a VCC, siempre y cuando el ADC no sea usado. Si

el ADC es usado, este deber ser conectado VCC a travs de un filtro pasa bajo.

2.4.11AREF

Es la referencia para el pin de la Conversin Anloga Digital.

2.5

AVR CPU Core

La principal funcin del AVR es asegurar la correcta ejecucin del programa.

Tiene Arquitectura Harvard es decir una Arquitectura con separador de

memorias y buses para programa y datos. Las instrucciones en la memoria del

programa son ejecutadas con un simple nivel de colas. Mientras una instruccin es

ejecutada, la siguiente instruccin es ejecutada desde la memora del programa.

15

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

Este concepto permite que las instrucciones sean ejecutadas en cada ciclo de

mquina. La memoria del programa est en la memoria Flash re-programable.

El archivo de registro (Register File) de rpido acceso contiene 32 registros de

propsito general de 8 bits trabajando a un simple ciclo de reloj. En una operacin

tpica de la ALU, los operandos estn fuera del Archivo de Registro, la operacin es

ejecutada. Y el resultado es guardado en el Archivo de Registro en un ciclo de

mquina.

Seis de los 32 registros pueden ser usados con tres registros punteros de 16

bits de direccin, para direccionar los datos y permitir los clculos de direcciones

diferentes.

Uno de estos punteros puede ser usado como un puntero de direcciones para

tablas en la memoria de programa flash. Estos registros de funcin adicionales son

el X, Y, Z de 16 bits. La ALU soporta operaciones lgicas y aritmticas entre

registros o entre constantes y registros.

La mayora de instrucciones del AVR tienen un formato simple de una

palabra de 16 bits. Cada direccin de memoria contiene instrucciones de 16 o 32

bits. El espacio de memoria en la Flash est dividido en dos secciones, la seccin

baja del programa y la seccin de aplicacin del programa.

La instruccin SMP que se escribe en la Seccin de la memora Flash debe

residir en la seccin baja del programa.

Durante los llamados de interrupcin y subrutinas. La direccin de regreso

del Contador de Programa (CP) es almacenado en la pila (stack).

La pila (stack) est localizada efectivamente en la SRAM (RAM esttica) de

datos consecuentemente el tamao de la pila est limitado solo por el tamao total

de la SRAM y su uso.

Todos los programas a usarse deben inicializar en el SP (stack pointer) es

decir, antes de que sea ejecutada una interrupcin o una subrutina.

16

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

Un mdulo de interrupcin flexible tiene sus registros de control en los

espacio de E/S con una Habilitacin de Interrupcin Global en el Registro de

Estado.

Todas las interrupciones tienen separado un vector de interrupciones en la

tabla del vector de interrupciones. Las interrupciones tienen prioridad de

conformidad con su vector de interrupciones. La direccin ms baja del vector

interrupciones tiene alta prioridad.

El espacio de memoria E/S contiene 64 direcciones para las funciones

perifricas de la CPU, el Registro de Control SPI y otras funciones de entrada y

salida. La memoria E/S puede ser accedida directamente o como localidades de

espacio de datos siguiendo estos Archivos de Registro: 0x20 0x5F. El

atmega164p tiene espacios extendido de E/S desde la direccin 0x60 0xFF en la

SRAM donde solo las instrucciones ST/STS/STD y LD/LDS/LDD puede ser usada.

2.6

Registro de Estado

17

ESCUELA POLITECNICA NACIONAL

FACULTAD DE INDENIERIA ELECTRICA Y ELECTRONICA

DEPARTAMENTO DE ELECTRONICA, TELECOMUNICACIONES Y REDES DE LA INFORMACION

SISTEMAS MICROPROCESADOS

MATERIA

3. BIBLIOGRAFIA

Manual del AVR Atmega164P

18

Vous aimerez peut-être aussi

- Métodos Químicos de RecuperaciónDocument27 pagesMétodos Químicos de RecuperaciónJose Ignacio RC75% (4)

- Tarea para Hacer TareasDocument6 pagesTarea para Hacer TareasPilar Etxebarria80% (5)

- Clase 03 - Base de DatosDocument44 pagesClase 03 - Base de DatosRafael Edwin Gordillo FloresPas encore d'évaluation

- La Construcción de Un Telescopio de Aficionado Texerau FinalDocument58 pagesLa Construcción de Un Telescopio de Aficionado Texerau FinalMiguel Calle RomeroPas encore d'évaluation

- Preparatorio 7Document4 pagesPreparatorio 7Miguel Calle RomeroPas encore d'évaluation

- Prepa9 CalleDocument4 pagesPrepa9 CalleMiguel Calle RomeroPas encore d'évaluation

- Prepa 6Document4 pagesPrepa 6Miguel Calle RomeroPas encore d'évaluation

- Ejercicios de PresionDocument3 pagesEjercicios de PresionMiguel Calle RomeroPas encore d'évaluation

- Deber Nº2Document10 pagesDeber Nº2Miguel Calle RomeroPas encore d'évaluation

- Avance VtolDocument14 pagesAvance VtolMiguel Calle RomeroPas encore d'évaluation

- Tema 1 Diagnóstico Situacional de La Salud Mental Del Personal de La Salud en El Contexto Del COVID-19 PDFDocument12 pagesTema 1 Diagnóstico Situacional de La Salud Mental Del Personal de La Salud en El Contexto Del COVID-19 PDFJosé PlasenciaPas encore d'évaluation

- CAST (2011) - Universal Design For Learning Guidelines Version 2.0. Wakefield, MA: Author. Traducción Al Español Version 2.0. (2013)Document22 pagesCAST (2011) - Universal Design For Learning Guidelines Version 2.0. Wakefield, MA: Author. Traducción Al Español Version 2.0. (2013)Pauli DuránPas encore d'évaluation

- Tipos de Datos en Lenguaje CDocument9 pagesTipos de Datos en Lenguaje Csebastian cevallos100% (1)

- Control Quimico de La Placa BacterianaDocument7 pagesControl Quimico de La Placa BacterianaSasha Nicole SantanderPas encore d'évaluation

- Gaslac Tello Trabinv Bach 2019Document17 pagesGaslac Tello Trabinv Bach 2019jaime higuitaPas encore d'évaluation

- 2do Parcial Epidemio - KELLY NOTASDocument35 pages2do Parcial Epidemio - KELLY NOTASBetzi HannlyPas encore d'évaluation

- Las Revoluciones Como Cambios de La Visión Del MundoDocument20 pagesLas Revoluciones Como Cambios de La Visión Del MundoEugenia FloresPas encore d'évaluation

- Tesis Carrera Psicología Salario EmocionalDocument21 pagesTesis Carrera Psicología Salario EmocionalCONSET CONSULTORESPas encore d'évaluation

- Aclaración, Rectificación O EnmiendaDocument3 pagesAclaración, Rectificación O EnmiendaFernando Faret Saalfeld0% (1)

- Productos SerfiDocument19 pagesProductos SerfiDiego RoblesPas encore d'évaluation

- Adviento y NavidadDocument2 pagesAdviento y Navidadmonikaeva torrePas encore d'évaluation

- Tema 4 - HERRAMIENTAS DE INTELIGENCIA ARTIFICIALDocument25 pagesTema 4 - HERRAMIENTAS DE INTELIGENCIA ARTIFICIALDiego EscobarPas encore d'évaluation

- Mandos MediosDocument7 pagesMandos MediosGY HERNANDEZPas encore d'évaluation

- Informe ObservaciónDocument7 pagesInforme ObservaciónCarlos ChristianPas encore d'évaluation

- Hora Santa MisioneraDocument7 pagesHora Santa MisioneraGuadalupe100% (1)

- 5° Grado - Sesiones Del 10 de AbrilDocument24 pages5° Grado - Sesiones Del 10 de Abrilmicxyvcr1426Pas encore d'évaluation

- Sanacion Del Utero Con Hierbas PDF 20Document13 pagesSanacion Del Utero Con Hierbas PDF 20martin luceroPas encore d'évaluation

- Ventajas y DesventajasDocument2 pagesVentajas y DesventajasPerla Espino MarinPas encore d'évaluation

- 9 Herramientas para La Optimización y Mejora Continua de Los Sistemas de Gestión de Seguridad y Salud LaboralDocument4 pages9 Herramientas para La Optimización y Mejora Continua de Los Sistemas de Gestión de Seguridad y Salud LaboralLuis OrtizPas encore d'évaluation

- La Procuración Electrónica Necesita Inteligencia de NegociosDocument2 pagesLa Procuración Electrónica Necesita Inteligencia de NegociosTecnología 21Pas encore d'évaluation

- Trabajo Final Cambio ClimaticoDocument8 pagesTrabajo Final Cambio ClimaticoAndrea PedrazaPas encore d'évaluation

- Cómo Fotografiar Rayos de Tormentas (En 12 Pasos)Document20 pagesCómo Fotografiar Rayos de Tormentas (En 12 Pasos)ChronosZone0% (1)

- Vectores en R3-2Document1 pageVectores en R3-2yonatan flores cayllahuaPas encore d'évaluation

- Guia Operativa: Cliente: Z160 Atlantis Operadora de Servicios de SaludDocument15 pagesGuia Operativa: Cliente: Z160 Atlantis Operadora de Servicios de SaludCabrera SolutionsPas encore d'évaluation

- Diagnostico Total PolizaDocument17 pagesDiagnostico Total PolizaAlexander CejudoPas encore d'évaluation

- Nombres y Apellidos Código de Estudiante: Autor/esDocument8 pagesNombres y Apellidos Código de Estudiante: Autor/esArely Gallardo CoronadoPas encore d'évaluation

- Metodo de Mallas # 3Document5 pagesMetodo de Mallas # 3Cristian Aldo Sanchez BurgoaPas encore d'évaluation