Académique Documents

Professionnel Documents

Culture Documents

Aplicación de Diseño de Circuitos Combinacionales

Transféré par

José OñaDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Aplicación de Diseño de Circuitos Combinacionales

Transféré par

José OñaDroits d'auteur :

Formats disponibles

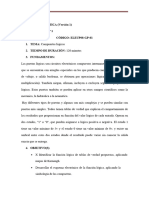

LABORATORIO ELECTRNICA DIGITAL

Practica N4

Aplicacin de diseo de circuitos Combinacionales

Estructura y esttica

Trabajo (clculos y

cuestionario)

Anlisis de resultados

2.

Conclusiones

MARCO

TEORICO

lgebra

de

RESUMEN:

Boole

El presente informe est destinado al anlisis

comprobacin e implementacin de un circuito

lgico que se ajuste a las necesidades del

ejercicio planteado.

Se dice que una variable tiene valor booleano

cuando, en general, la variable contiene un 0

lgico o un 1 lgico. [1]

Esto, en la mayora de los lenguajes de

programacin, se traduce en false (falso) o

true (verdadero), respectivamente. Una

variable puede no ser de tipo booleano, y

guardar valores que, en principio, no son

booleanos; ya que, globalmente, los

compiladores trabajan con esos otros valores,

numricos normalmente, aunque tambin

algunos permiten cambios desde, incluso,

caracteres, finalizando en valor booleano. [1]

El 0 lgico El valor booleano de negacin

suele ser representado como false, aunque

tambin permite y equivale al valor natural,

entero y decimal (exacto) 0, as como la

cadena "false", e incluso la cadena "0". [2]

El 1 lgico En cambio, el resto de valores

apuntan al valor booleano de afirmacin,

representado normalmente como true, ya que,

por definicin, el valor 1 se tiene cuando no

es 0. [2]

Cualquier nmero distinto de cero se

comporta como un 1 lgico, y lo mismo

sucede con casi cualquier cadena (menos la

"false", en caso de ser sta la correspondiente

al 0 lgico). [3]

ABSTRACT:

This report is intended for testing and

implementation of a logic circuit that meets the

needs of the proposed exercise analysis.

PALABRAS CLAVE: algebra de Boole,

compuertas lgicas, tablas de verdad, Mapas de

Karnaugh.

1.

OBJETIVOS

1.1. Objetivo general:

Disear, analizar e implementar un circuito

lgico que satisfaga las necesidades del

ejercicio planteado.

1.2. Objetivos especficos:

Obtener tablas de verdad que ayuden a

plantear la activacin del circuito.

Deducir mediante mapas de Karnaugh la

ecuacin lgica que solucione el problema.

Disear el circuito lgico para su

implementacin y comprobacin.

3.

MATERIALES Y EQUIPOS

-

Resistencias de 220.

Dip switch.

Protoboard.

Cables de conexin.

LABORATORIO ELECTRNICA DIGITAL

Practica N4

4.

Fuente de alimentacin en DC

Compuertas Lgicas NAND,

NOT, OR.

AND,

DESARROLLO Y PROCEDIMIENTO

Problema

Mediante dos bombas (m1 y m2) se controla el

nivel de un depsito. El depsito tiene 2 boyas (b1

y b2). Cuando el nivel est por debajo de la boya

el contacto correspondiente est abierto. Las

bombas sacan agua de dos pozos. Si no hay agua

en el pozo la bomba no funciona. Para controlar

esto, cada pozo lleva un sensor (n1 y n2).

El sistema funciona de la siguiente forma:

Si el nivel del depsito supera la boya b1,

las bombas estn paradas.

Si el nivel del depsito est entre la boya

b1 y b2, funciona la bomba m1, si hay

agua suficiente en el pozo 1. Si no hay

agua en el pozo 1 pero la hay en el 2,

funciona la bomba m2.

Si el nivel del depsito est por debajo de

la boya b2, se activa la bomba m2,

adems de la m1.

0

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

1

0

1

1

0

0

1

1

1

0

Tabla 1. Tabla de verdad

0

0

0

0

0

0

0

0

0

Parte 2. Mapas de Karnaugh

2.1 Salida m1

Mediante la tabla de verdad(Tabla1) se puede

plantear los mapas de Karnaugh para cada salida

m1 y m2.

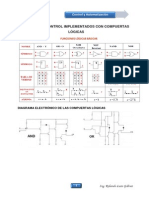

Tabla2. Mapa de Karnaugh para la salida m1

m1=b1n 1

Ecuacion1. Ecuacin Lgica para m1.

Fig1. Grafico del problema planteado.

2.2 Salida m2

Parte 1. Tabla de verdad

b1

0

0

0

0

0

0

0

b2

0

0

0

0

1

1

1

n1

0

0

1

1

0

0

1

n2

0

1

0

1

0

1

0

S1

0

0

1

1

0

0

1

S2

0

1

0

1

0

1

0

Tabla3. Mapa de Karnaugh para la salida m2

LABORATORIO ELECTRNICA DIGITAL

Practica N4

m2=( b2+ n1)(

b2)( n 2)

Ecuacion2. Ecuacin Lgica para m2.

Parte 3. Circuitos Lgicos

Anlisis: si b1 y b2 tienen un 0 y los depsitos

n1y n2 tienen 1 lgico se activarn m1 y m2

debido a que deben llenarse los tanques.

6.

CONCLUSIONES

Mediante la tabla de verdad se realiza las

comprobaciones debido a que al activar las

entradas con las distintas configuraciones

segn el enunciado la salida debe activar la

bomba o en este caso el led que demuestra el

funcionamiento del sistema.

Se observ que funcionaba correctamente al

accionar la entrada b1 debido a que segn las

condiciones del sistema al activarse el sensor

b1 existira un paro general de las bombas y

se observa en la tabla de vedad que todas las

combinaciones en las que b1 se encuentra con

un 1 lgico las salidas tienen un 0 lgico.

Si los tanques se encuentran vacos se

activarn las bombas llenndolos lo cual en la

tabla de verdad se comprueba con b2 con 0

lgico y n1 y n2 con1 lgico.

7.

REFERENCIAS BIBLIOGRFICAS

Fig2. Circuito a implementar para la salida m1

(Ecuacion1)

Fig3. Circuito a implementar para la salida m2

(Ecuacion2)

5.

Si el nivel del depsito est por debajo de

la boya b2, se activa la bomba m2,

adems de la m1.

ANLISIS Y RESULTADOS

Para su anlisis se debe tomar en cuenta las

condiciones del ejercicio.

Si el nivel del depsito supera la boya b1,

las bombas estn paradas.

Anlisis: al tener un 1 lgico en b1 el

sistema debe detenerse sin importar que valor

lgico tengan las otras entradas.

Si el nivel del depsito est entre la boya

b1 y b2, funciona la bomba m1, si hay

agua suficiente en el pozo 1. Si no hay

agua en el pozo 1 pero la hay en el 2,

funciona la bomba m2.

Anlisis: al tener un 1 lgico en las entradas b2,

n1 y 0 lgico en b1 funciona m2 lo que equivale

a un 1 lgico.

[1] T. L Floyd, "Dispositivos Electrnicos,"

Pearson Prentice Hall, octava edicin, Mxico

2008, pp. 182-183.

[2] R.L. Boylestad, L. Nashelsky, "Teora de

circuitos y Dispositivos Electrnicos," dcima

edicin, Mxico 2009, pp.206

[3] R. Araya.E.,(2006 mayo), Algebra de Boole,

Disponible

en:

http://users.dcc.uchile.cl/~clgutier/Capitulo_3.pdf

Vous aimerez peut-être aussi

- Problemas resueltos de Hidráulica de CanalesD'EverandProblemas resueltos de Hidráulica de CanalesÉvaluation : 4.5 sur 5 étoiles4.5/5 (7)

- Final Examen Electrónica 2020Document4 pagesFinal Examen Electrónica 2020Pascual MaféPas encore d'évaluation

- Aplicación de Circuitos Digitales para Manejo de Código BCDDocument3 pagesAplicación de Circuitos Digitales para Manejo de Código BCDLuisAlbertoPas encore d'évaluation

- LABORATORIO 1 Digitales.Document5 pagesLABORATORIO 1 Digitales.Daniela Paez BoteroPas encore d'évaluation

- Lab 3 DigitalDocument7 pagesLab 3 DigitalJorge GomezPas encore d'évaluation

- Universidad Tecnológica de Pereira Ingeniería Electrónica Laboratorio de Sistemas Digitales IiDocument2 pagesUniversidad Tecnológica de Pereira Ingeniería Electrónica Laboratorio de Sistemas Digitales IiAdiela patiñoPas encore d'évaluation

- Práctica 3. Diseño de Automatismos Digitales.Document5 pagesPráctica 3. Diseño de Automatismos Digitales.Mamosa MamosaPas encore d'évaluation

- InformelogicaDocument3 pagesInformelogicaCarlos PardoPas encore d'évaluation

- ED Practica 2Document3 pagesED Practica 2Alex De la TorrePas encore d'évaluation

- Informe 2 DigitalesDocument6 pagesInforme 2 DigitalesAlcocer AlejandraPas encore d'évaluation

- Estudio 2Document7 pagesEstudio 2Danilo FernandezPas encore d'évaluation

- AplicacioncircuitoscombDocument4 pagesAplicacioncircuitoscombakdkevinPas encore d'évaluation

- 4 - Simplificacion AlgebraicaDocument6 pages4 - Simplificacion AlgebraicaHc AlejandroPas encore d'évaluation

- Informe Ejercicio Cinco, Electronica DigitalDocument4 pagesInforme Ejercicio Cinco, Electronica DigitalmariadignoraPas encore d'évaluation

- Practica 4 Sitemas DigitalesDocument12 pagesPractica 4 Sitemas DigitalesAlessandra BernardoPas encore d'évaluation

- Practica 2Document4 pagesPractica 2Hatapro Abaran SaidPas encore d'évaluation

- Llenado de TanqueDocument6 pagesLlenado de TanqueStalin OmarPas encore d'évaluation

- Circuitos CombinacionalesDocument5 pagesCircuitos CombinacionalesJosé BatistaPas encore d'évaluation

- Práctica Nº1: Diseño de Circuitos CombinacionalesDocument3 pagesPráctica Nº1: Diseño de Circuitos CombinacionalesVíctor ArrietaPas encore d'évaluation

- EEE Automatizacion Clase N°15. 4 SE - 2019 OK SilabuDocument50 pagesEEE Automatizacion Clase N°15. 4 SE - 2019 OK SilabuCristian More TuanamaPas encore d'évaluation

- Trabajo GuerraDocument9 pagesTrabajo GuerraErik BonaventuraPas encore d'évaluation

- Practica 1Document12 pagesPractica 1Paul DamiánPas encore d'évaluation

- Proyecto Digitales1Document11 pagesProyecto Digitales1CrisPas encore d'évaluation

- Laboratorio 2. Lógica Combinacional y Mapas de KarnaughtDocument4 pagesLaboratorio 2. Lógica Combinacional y Mapas de KarnaughtAngie BarreraPas encore d'évaluation

- Electrónica AnalógicaDocument16 pagesElectrónica AnalógicaMax Palomino AltezPas encore d'évaluation

- DECODIFICADORDocument16 pagesDECODIFICADORDANIEL ANDRES RAMIREZ SEGURAPas encore d'évaluation

- Actividad 2.0 Circuito CombinacionalDocument2 pagesActividad 2.0 Circuito CombinacionalkuborusPas encore d'évaluation

- Electro Digital Pract 2Document5 pagesElectro Digital Pract 2Kevin Fer OrtegaPas encore d'évaluation

- Lab3 V1Document21 pagesLab3 V1Martial Arcos MedinaPas encore d'évaluation

- Analisis de Montaje Práctico de Compuertas LogicasDocument10 pagesAnalisis de Montaje Práctico de Compuertas LogicasAlexha MarthinezzPas encore d'évaluation

- INFORME Electrónica DigitalDocument4 pagesINFORME Electrónica DigitalAlvaro HaroPas encore d'évaluation

- Practicas de Electronic A DigitalDocument25 pagesPracticas de Electronic A DigitalFredy Alfonso Martinez TorresPas encore d'évaluation

- PRACTICA 1 - Comprobacion de Compuertas OR AND NOT NOR NANDDocument12 pagesPRACTICA 1 - Comprobacion de Compuertas OR AND NOT NOR NANDAndres DamianPas encore d'évaluation

- Guia PLC ActualizadaDocument168 pagesGuia PLC Actualizadajorge diazPas encore d'évaluation

- Practicas de Compuertas LogicasDocument10 pagesPracticas de Compuertas LogicasAngel Eduardo Hernandez SilvaPas encore d'évaluation

- GUIA 3 - PLCs - Listado de Instrucciones PDFDocument14 pagesGUIA 3 - PLCs - Listado de Instrucciones PDFNARVAEZ ORTIZ JUAN DIEGOPas encore d'évaluation

- U1 T1 BooleDocument48 pagesU1 T1 Boolebryan stalin arteaga montenegroPas encore d'évaluation

- Informe Control AutomaticoDocument21 pagesInforme Control AutomaticoJuan Francisco Vera AbarcaPas encore d'évaluation

- Practica1 Chico LedesmaDocument10 pagesPractica1 Chico LedesmaPatricia CandoPas encore d'évaluation

- Taller 2Document10 pagesTaller 2Raul Andres Mejia DiazPas encore d'évaluation

- Control Con Compuertas Logicas PDFDocument27 pagesControl Con Compuertas Logicas PDFAlison ReedPas encore d'évaluation

- Boletín de Práctica 1 FCO UPVDocument9 pagesBoletín de Práctica 1 FCO UPVRiwa DainPas encore d'évaluation

- Compuertas LogicasDocument4 pagesCompuertas LogicasAlexander PalmaPas encore d'évaluation

- Informe #1Document15 pagesInforme #1MARIA PAULA CABEZAS CHARRYPas encore d'évaluation

- Practica 2 Electrónica Equipo 14Document23 pagesPractica 2 Electrónica Equipo 14Ximena J LanderosPas encore d'évaluation

- Guía de Práctica de Laboratorio #8Document9 pagesGuía de Práctica de Laboratorio #8wcherovPas encore d'évaluation

- Tarea 3 - Ericka CutaDocument7 pagesTarea 3 - Ericka Cutaangelita morenoPas encore d'évaluation

- Practica No. 8 MultiplicadorDocument12 pagesPractica No. 8 MultiplicadorOscar Monroy100% (1)

- Tecnologico Nacional de Mexico. Instituto Tecnologico de La LagunaDocument11 pagesTecnologico Nacional de Mexico. Instituto Tecnologico de La LagunaFelipe ValdezPas encore d'évaluation

- ProblemaDocument1 pageProblemajsoberonPas encore d'évaluation

- LABORATORIO 3 DigitalesDocument5 pagesLABORATORIO 3 DigitalesVanessa Cárdenas BeltránPas encore d'évaluation

- Practica 2 Lab Electronica DigitalDocument7 pagesPractica 2 Lab Electronica DigitalSantiago Echeverri DuquePas encore d'évaluation

- Parcial1 PreparatorioDocument1 pageParcial1 PreparatorioCamilo BetancourtPas encore d'évaluation

- S12 Compuertas LógicasDocument22 pagesS12 Compuertas Lógicasluz maribelPas encore d'évaluation

- Aplicaciones de Circuitos MSIDocument7 pagesAplicaciones de Circuitos MSIkevinPas encore d'évaluation

- Informe Lab2Document3 pagesInforme Lab2Stalin MiguelPas encore d'évaluation

- Practica 2 SDDocument12 pagesPractica 2 SDAxel GonPas encore d'évaluation

- Tabla de VerdadDocument11 pagesTabla de VerdadAnderson IzaPas encore d'évaluation

- Electronica ExamenDocument1 pageElectronica ExamenAlfonso LockherupPas encore d'évaluation

- Memoria MagneticaDocument3 pagesMemoria MagneticaJosé OñaPas encore d'évaluation

- Informe Cronometro Cóndor MiguelDocument7 pagesInforme Cronometro Cóndor MiguelJosé OñaPas encore d'évaluation

- Informe Proyecto Digitales Seguidor de LineaDocument4 pagesInforme Proyecto Digitales Seguidor de LineaJosé OñaPas encore d'évaluation

- Informe Desplazamiento LCD CaracterDocument2 pagesInforme Desplazamiento LCD CaracterJosé Oña100% (1)

- Display 4 Digitos 7 Segmentos para Barrido PDFDocument7 pagesDisplay 4 Digitos 7 Segmentos para Barrido PDFJosé OñaPas encore d'évaluation

- Manejo de Varios Display de 7 SegmentosDocument2 pagesManejo de Varios Display de 7 SegmentosJosé OñaPas encore d'évaluation

- Aplicacion de Circuitos MsiDocument3 pagesAplicacion de Circuitos MsiJosé Oña0% (1)

- Efecto Joule en Los Conductores ElectricosDocument2 pagesEfecto Joule en Los Conductores ElectricosJosé OñaPas encore d'évaluation

- Cuadro GemmaDocument5 pagesCuadro GemmaAnonymous YivzQO9AuPas encore d'évaluation

- HV - Paquete RSS y VideosDocument2 pagesHV - Paquete RSS y VideosEsther RodriguezPas encore d'évaluation

- Historia Del InternetDocument13 pagesHistoria Del InternetValencia Caicedo IngridPas encore d'évaluation

- Ejercicio 1 DMLDocument3 pagesEjercicio 1 DMLEdison Franco SuarezPas encore d'évaluation

- Guía Del Usuario: Instrumentos ICP-OES Agilent 5800 y 5900Document72 pagesGuía Del Usuario: Instrumentos ICP-OES Agilent 5800 y 5900gabrielgerardo1505Pas encore d'évaluation

- SILABUS de WordDocument4 pagesSILABUS de WordCapacitaciones HardySoft100% (1)

- T.ti Penagos Jimenez Gina Tatiana 2014Document51 pagesT.ti Penagos Jimenez Gina Tatiana 2014axsel78997Pas encore d'évaluation

- Modelo Informe AVDocument3 pagesModelo Informe AVwcastro8182Pas encore d'évaluation

- Unidad I PDFDocument34 pagesUnidad I PDFMartín Arellano GómezPas encore d'évaluation

- Apuntes de Electronica III-extendidaDocument247 pagesApuntes de Electronica III-extendidaAlbertoPas encore d'évaluation

- Material de Reforzamiento U12 NetworkingDocument5 pagesMaterial de Reforzamiento U12 NetworkingSebastian MuñozPas encore d'évaluation

- Config Linked Server para FirebirdDocument10 pagesConfig Linked Server para FirebirdWalter Peraza MedranoPas encore d'évaluation

- Matematica Actividad Entregable - 001Document3 pagesMatematica Actividad Entregable - 001Ale LRPas encore d'évaluation

- Orden Servicio TecnicoDocument2 pagesOrden Servicio Tecnicoaudicon201150% (4)

- Almacenamiento en La Nube - Luis NavasDocument5 pagesAlmacenamiento en La Nube - Luis NavasLuis Alfonso Navas PiñangoPas encore d'évaluation

- Diseño Factorial de Dos FactoresDocument6 pagesDiseño Factorial de Dos Factoresjeyleen diaz100% (1)

- UntitledDocument41 pagesUntitledGigi SalveminiPas encore d'évaluation

- D9TDocument59 pagesD9TTony Ventura Vizcardo67% (3)

- Informe de Pasantias-DeiverDocument56 pagesInforme de Pasantias-Deiverdeiver_adsPas encore d'évaluation

- Couli 12 2021Document2 pagesCouli 12 2021gasparPas encore d'évaluation

- Correccion de Admi ControlDocument2 pagesCorreccion de Admi ControlAlarcon Torres Martin BraniPas encore d'évaluation

- Clase 6 Ejemplos Con Funcion CuadraticaDocument2 pagesClase 6 Ejemplos Con Funcion CuadraticaJose ReggePas encore d'évaluation

- Practica 01 - Clase ScannerDocument3 pagesPractica 01 - Clase ScannerDIANA TARQUIPas encore d'évaluation

- Normas Tecnicas Complementarias Del Diseño Arquitectonico Discapacidad PDFDocument135 pagesNormas Tecnicas Complementarias Del Diseño Arquitectonico Discapacidad PDFCristina BravoPas encore d'évaluation

- DistribuidosDocument6 pagesDistribuidosMANUEL ANDRES OLIVARES LOPEZPas encore d'évaluation

- Po3 y Po4 Cobit Ingenieria de SoftwareDocument19 pagesPo3 y Po4 Cobit Ingenieria de SoftwareJhan_PiedraPas encore d'évaluation

- Que Es DoggerDocument10 pagesQue Es DoggerJonathanPas encore d'évaluation

- Ejercicios Pag 30 Cordova ZamoraDocument8 pagesEjercicios Pag 30 Cordova ZamoraAracely Pulache100% (1)

- Quadstar II MANUAL TECNICODocument21 pagesQuadstar II MANUAL TECNICONarda Ticona50% (2)

- Pauta de Disertacion Segundo MedioDocument3 pagesPauta de Disertacion Segundo MedioValentina AguayoPas encore d'évaluation