Académique Documents

Professionnel Documents

Culture Documents

Bds Lab 4

Transféré par

Nagendra BoyellaTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Bds Lab 4

Transféré par

Nagendra BoyellaDroits d'auteur :

Formats disponibles

Basics of Digital Systems Lab

Dept. of ECE

1. Realization of gates using Universal gates

Aim: To realize all logic gates using NAND and NOR gates.

Apparatus:

S. No

1.

2.

3.

4.

Description of Item

IC 7400

IC 7402

Digital Trainer Kit

Bread Board

Quantity

01

01

01

01

Circuit Diagram:

I.

Implementation using NAND gate:

(a) NOT gate:

A

0

1

Y

1

0

A

0

0

1

1

B

0

1

0

1

Y

0

0

0

1

A

0

0

1

1

B

0

1

0

1

Y

0

1

1

1

A

0

0

1

1

B

0

1

0

1

Y

1

0

0

0

(b) AND gate:

(c) OR gate:

(d) NOR gate:

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

(e) Ex-OR gate:

A

0

0

1

1

II.

B

0

1

0

1

Y

0

1

1

0

Implementation using NOR gate:

(a) NOT gate:

A

0

1

Y

1

0

(b) AND gate:

A

0

0

1

1

B

0

1

0

1

Y

0

0

0

1

A

0

0

1

1

B

0

1

0

1

Y

0

1

1

1

A

0

0

1

1

B

0

1

0

1

Y

1

1

1

0

(c) OR gate:

(d) NAND gate:

(e) Ex-NOR gate:

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

0

0

1

1

0

1

0

1

1

0

0

1

Procedure:

a) Connections are made as per the circuit diagram I & II.

b) By applying the inputs, the outputs are observed and the operation is verified with the help

of truth table.

Precautions:

1. Connections must be tight on the bread board.

2. Identify the pins of the IC properly.

3. Take care while removing and inserting the IC on bread board.

Result:

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

2. Design of Combinational Logic Circuits

Aim: To design and implement combinational logic circuits like half-adder, full-adder and

half-subtractor using NAND gates.

Apparatus:

S. No

1.

2.

3.

Description of Item

IC 7400

Digital Trainer Kit

Bread Board

Quantity

03

01

01

Design procedure:

The design of combinational circuits starts from verbal outline of the problem and ends in a

logic circuit diagram, or a set of Boolean functions from which the logic diagram can be

easily obtained.

The different steps involved in the design of a combinational logic circuit are as follows:

1. Statement of the problem.

2. Identification of input and output variables.

3. Expressing the relationship between the input and output variables.

4. Construction of a truth table to meet inputoutput requirements.

5. Writing Boolean expressions for various output variables in terms of input variables.

6. Minimization of Boolean expressions.

7. Implementation of minimized Boolean expressions using gates.

Half-Adder:

A half adder is a combinational logic circuit that performs the arithmetic addition of two bits.

Such a circuit thus has two inputs that represent the two bits to be added and two outputs,

with one producing the SUM output and the other producing the CARRY.

Truth table:

A

0

0

1

1

B

0

1

0

1

S

0

1

1

0

C

0

0

0

1

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

For Sum S:

For Carry C:

The Boolean expressions for the SUM and CARRY outputs are given by the equations

Half-Adder using NAND gates

Full-Adder:

A full adder circuit is an arithmetic circuit block that can be used to add three bits to produce

a SUM and a CARRY output. Two of the input variables

significant bits to be added and the third input

and

represent the two

represents the carry from the previous lower

significant position.

X

0

0

0

0

1

1

1

1

Y

0

0

1

1

0

0

1

1

Z

0

1

0

1

0

1

0

1

S

0

1

1

0

1

0

0

1

C

0

0

0

1

0

1

1

1

For Sum S:

For Carry C:

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

To implement a full adder using two half adders, the following expressions are used:

Full-Adder using NAND gates

Half-Subtractor:

A Half-Subtractor is a combinational circuit that can be used to subtract one binary digit from

another to produce a DIFFERENCE output and a BORROW output. The BORROW output

here specifies whether a 1 has been borrowed to perform the subtraction.

X

0

0

1

1

Y

0

1

0

1

D

0

1

1

0

B

0

1

0

0

Truth table

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

Half-Subtractor using NAND gates

Procedure:

a) Connections are made as per the circuit diagrams shown.

b) By applying the inputs, the outputs are observed and the operation of logic circuits are

verified with the help of truth table.

Precautions:

1. Connections must be tight on the bread board.

2. Identify the pins of the IC properly.

3. Take care while removing and inserting the IC on bread board.

Result:

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

3. Design of Magnitude Comparator

Aim: To design and implement one bit magnitude comparator using gates and 4 bit

comparator using IC 7485.

Apparatus:

S. No

1.

2.

3.

Description of Item

IC 7402, 7404, 7408, 7485

Digital Trainer Kit

Bread Board

Quantity

01 Each

01

01

Design Procedure:

The comparison of two numbers is an operation that determines if one number is greater than,

less than, or equal to the other number. A magnitude comparator is a combinational circuit

that compares two numbers,

and , and determines their relative magnitudes. The outcome

of the comparison is specified by three binary variables that indicate whether

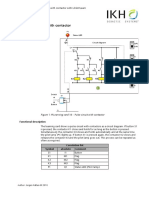

a) One Bit Magnitude Comparator:

The 1-bit comparator compares two 1 bit numbers and gives an output based on the

magnitude of two bits. The truth table for the circuit is as shown:

0

0

1

1

0

1

0

1

0

0

1

0

1

0

0

1

0

1

0

0

;

Fig. 1: One-bit Comparator

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

b) 4 Bit Magnitude Comparator using 7485:

The 7485 is a high speed, expandable 4-bit magnitude comparator which compares

two 4-bit words and generates three outputs: (A>B), (A=B) and (A<B). Three

cascading inputs allow serial expansion over any word length without external gates.

For 4-bit comparison, the cascading inputs

Fig. 2: 4-bit Comparator

Procedure:

One-bit Comparator:

1. Connections are made as per the Fig. 1.

2. By applying the inputs A & B, the output magnitude is determined and the truth table

is verified.

4-bit Comparator:

1. Connections are made as per the Fig. 2 using IC 7485.

2. Apply the comparing inputs and the output is observed for various cascading inputs

and the operation is verified with the help of truth table.

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

Function Table of 7485:

Precautions:

1. Connections must be tight on the bread board.

2. Identify the pins of the IC properly.

3. Take care while removing and inserting the IC on bread board.

Result:

4. Design of Multiplexer and Demultiplexer

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

Aim: To design and implement

Multiplexer and

using gates.

Apparatus:

S. No

1.

2.

3.

Description of Item

IC 7404, 7410, 7420

Digital Trainer Kit

Bread Board

Quantity

01 Each

01

01

Design Procedure:

A multiplexer is a combinational circuit that selects binary information from one of many

input lines and directs it to a single output line. The selection of a particular input line is

controlled by a set of selection lines. In general, there are 2n input lines and n selection lines

whose bit combinations determine which input is selected.

Multiplexer:

There are 4 input lines

and 2 select inputs

Demultiplexer:

A demultiplexer is a circuit that receives information on a single line and transmits this

information on one of 2n possible output lines. The selection of a specific output line is

controlled by the bit values of n selection lines.

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

Circuit Diagram:

Fig. 1: 4x1 Multiplexer

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

Fig. 2: 1x4 Demultiplexer

Procedure:

Multiplexer:

1. Connections are made as per the circuit diagram 1.

2. By varying the select inputs S1 & S0, any one of the 4 inputs can be selected on the

output and the truth table is verified.

:

1. Connections are made as per the Fig. 2.

2. By varying the select inputs S1 & S0, the information on the single input E is

transmitted to any one of 4 output lines and the truth table is verified.

Precautions:

1. Connections must be tight on the bread board.

2. Identify the pins of the IC properly.

3. Take care while removing and inserting the IC on bread board.

Result:

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

5. BCD to 7 Segment Decoder with Common anode display

Aim: To realize the operation of BCD to 7 segment decoder using IC 7447 and common

anode display.

Apparatus:

S. No

1.

2.

3.

Description of Item

IC 7447, 7490, FND 542

Digital Trainer Kit

Bread Board

Quantity

01 Each

01

01

Circuit Diagram:

IC 7490:

The 74LS90 is a 4-bit, ripple-type decade counter. The device consists of four master-slave

flip-flops internally connected to provide a divide-by-two section and a divide-by-five

section. The device can be operated in various counting modes like BCD counter, divide-byfive counter, divide-by-two counter and biquinary divide-by-ten counter.

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

In a BCD Counter, the input must be externally connected with the

output. The

input receives the incoming count producing a BCD count sequence. Set

.

IC 7447:

IC 7447 is a BCD to 7 segment decoder with active low outputs. It accepts the BCD code and

provides outputs to energize seven segment display devices in order to produce a decimal

read out.

stands for Lamp Test. When is low all the segments on the 7-segment display are lit

regardless of

stands for Blanking Input. When is low the display is blank so all the segments on the

7segment display are off regardless of

stands for Ripple Blanking Input. When is low and

the display

is blank otherwise the number is displayed on the display. This is used to remove leading

zeroes from a number (e.g. display 89 instead of 089). To use with more than one display

connect (Ripple Blanking Output) from most significant 7447 to the next 7447.

For normal operation,

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

Procedure:

1. Connections are made as per the circuit diagram shown.

2. BCD inputs are applied to 7 segment decoder using IC 7490, which is a ripple

counter.

3. Apply

to IC 7447.

4. For each clock pulse BCD number will be generated using 7490 and the ten

corresponding decimal digits can be displayed in common anode display.

Precautions:

1. Connections must be tight on the bread board.

2. Identify the pins of the IC properly.

3. Take care while removing and inserting the IC on bread board.

Result:

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

6. Realization of Flip-flops using Gates

Aim: To realize the flip-flops like SR, JK, D and T Flip-flops using gates.

Apparatus:

S. No

1.

2.

3.

Description of Item

IC 7400, 7404, 7410

Digital Trainer Kit

Bread Board

Quantity

01 Each

01

01

Circuit Diagram:

Clocked SR Flip-flop:

Truth table:

0

JK Flip-flop:

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

Truth table:

X

Procedure:

1. Connections are made as per the circuit diagram.

2. By applying inputs, the outputs are verified with the help of truth table.

Precautions:

1. Connections must be tight on the bread board.

2. Identify the pins of the IC properly.

3. Take care while removing and inserting the IC on bread board.

Result:

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

7. Design of Ripple Counters

Aim: To design and verify the operation BCD ripple counter using JK flip-flops.

Apparatus:

S. No

1.

2.

3.

4.

Description of Item

IC 7400

IC 7476

Digital Trainer Kit

Bread Board

Quantity

01

02

01

01

Design Procedure:

In ripple counter, the flip-flops within the counter are not made to change the states at exactly

the same time, i.e., they are not clocked simultaneously. In a ripple counter, also called an

asynchronous counter or a serial counter, the clock input is applied only to the first flip-flop,

also called the input flip-flop, in the cascaded arrangement. The clock input to any

subsequent flip-flop comes from the output of its immediately preceding flip-flop.

Modulus of the counter:

The number of states through which the counter passes before returning to the starting state is

called the modulus of the counter. The condition to determine the number of flip-flops is

BCD Ripple Counter: It is also known as MOD 10 ripple counter or Decade Ripple counter.

KL University, Guntur

Basics of Digital Systems Lab

Connect

Dept. of ECE

to a NAND gate and the output of the gate to clear input of the flip-flops.

Hence after state 1001, when the circuit enters into state 1010, the NAND output becomes 0

and hence the flip-flops will be in reset state, 0000 and the count continues.

Circuit Diagram:

Procedure:

1. Connections are made as per the circuit diagram.

2. Set preset = 1,

for all the flip-flops and apply clock signal manually to the

least significant flip-flop.

3. Connect

to a NAND gate and the output of the gate to clear input of the flip-

flops.

4. The flip-flops will change their state for each clock pulse and ten states are observed

before it returns to the initial state.

Precautions:

1. Connections must be tight on the bread board.

2. Identify the pins of the IC properly.

3. Take care while removing and inserting the IC on bread board.

Result:

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

8. Design of Synchronous Counters

Aim: To design a counter using JK flip-flops for the following binary sequence: 0, 4, 2, 1, 6

and repeat.

Apparatus:

S. No

1.

2.

3.

4.

Description of Item

IC 7408, 7432

IC 7476

Digital Trainer Kit

Bread Board

Quantity

01 Each

02

01

01

Design Procedure:

In a synchronous counter, also known as a parallel counter, all the flip-flops in the counter

change state at the same time in synchronism with the input clock signal. The clock signal in

this case is simultaneously applied to the clock inputs of all the flip-flops.

Present State (PS)

Next State (NS)

Circuit Excitation and output table:

Present State

(PS)

Next State (NS)

Flip-flop Input functions

0

1

1

KL University, Guntur

1

0

Basics of Digital Systems Lab

Dept. of ECE

By using K-maps, we get.

;

Procedure:

1. Connections are made as per the circuit diagram.

2. Set preset = clear = 1,

for all the flip-flops and apply clock signal

manually to all the flip-flops simultaneously.

3. The flip-flops will change their state for each clock pulse and the required states are

observed before the counter returns to the initial state.

Precautions:

1. Connections must be tight on the bread board.

2. Identify the pins of the IC properly.

3. Take care while removing and inserting the IC on bread board.

Result:

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

9. Shift Registers, Ring & Johnson Counter

Aim: To verify the operation of SISO shift register and Ring & Johnson counters using D

flip-flops.

Apparatus:

S. No

1.

2.

3.

4.

Description of Item

IC 7408, 7432

IC 7476

Digital Trainer Kit

Bread Board

Quantity

01 Each

02

01

01

Circuit Diagrams:

a) 4 bit SISO shift Register:

b) 4 bit Ring Counter:

Ring Counter States:

1

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

c) 4 bit Johnson Counter:

Johnson Counter States:

0

Procedure:

4 bit SISO shift register:

1. Connections are made as per the circuit diagram (a).

2. Set preset = clear = 1 for all the flip-flops and apply clock signal manually to all the

flip-flops simultaneously.

3. Apply the data to the left-most flip-flop and for every clock pulse, data input will shift

towards right side.

4 bit Ring Counter:

1. Connections are made as per the circuit diagram (b).

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

2. Set preset = clear = 1 for all the flip-flops and apply clock signal manually to all the

flip-flops simultaneously.

3. Apply logic 1 as input at the beginning and the ring counter will change its state for

every clock pulse and after 4 states, the cycle repeats.

4 bit Johnson Counter:

1. Connections are made as per the circuit diagram (c).

2. Set preset = clear = 1 for all the flip-flops and apply clock signal manually to all the

flip-flops simultaneously.

3. The Johnson counter will change its state for every clock pulse and after 8 states, the

cycle repeats and the truth table is verified.

Precautions:

1. Connections must be tight on the bread board.

2. Identify the pins of the IC properly.

3. Take care while removing and inserting the IC on bread board.

Result:

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

10. Design of Two digit display using IC 7490

Aim: To design and verify the operation of BCD to 7 segment decoder using IC 7447 and

common anode display.

Apparatus:

S. No

1.

2.

3.

Description of Item

IC 7447, 7490, FND 542

Digital Trainer Kit

Bread Board

Quantity

02 Each

01

01

Circuit Diagram:

Procedure:

1. Connections are made as per the circuit diagram shown.

2. Numbers from 00 to 99 can be observed using the above arrangement for every one

clock pulse.

Precautions:

KL University, Guntur

Basics of Digital Systems Lab

Dept. of ECE

1. Connections must be tight on the bread board.

2. Identify the pins of the IC properly.

3. Take care while removing and inserting the IC on bread board.

Result:

KL University, Guntur

Vous aimerez peut-être aussi

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Cap 5 IrwinDocument284 pagesCap 5 Irwinjoao0honorato100% (3)

- AnalogsDocument3 pagesAnalogsOscar GonzalezPas encore d'évaluation

- Full Flow RAK - RTL To Place & Route, Including ECO: Rapid Adoption Kit (RAK)Document38 pagesFull Flow RAK - RTL To Place & Route, Including ECO: Rapid Adoption Kit (RAK)dupipiPas encore d'évaluation

- Bus and Memory TransfersDocument11 pagesBus and Memory TransfersSam-eer Neo-paneyPas encore d'évaluation

- PIC16f877a TimerDocument9 pagesPIC16f877a Timerjohn moron100% (2)

- Stick Diagram and LayoutDocument9 pagesStick Diagram and LayoutNagendra Boyella100% (2)

- Batalov Amaro Us So V Viens WitDocument10 pagesBatalov Amaro Us So V Viens WitNagendra BoyellaPas encore d'évaluation

- VentilDocument2 pagesVentilNagendra BoyellaPas encore d'évaluation

- Sharma 2015Document4 pagesSharma 2015Nagendra BoyellaPas encore d'évaluation

- Adiabatic CMOS Circuit Design: Principles and Examples: X. Wu, G. Hang, and M. PedramDocument20 pagesAdiabatic CMOS Circuit Design: Principles and Examples: X. Wu, G. Hang, and M. PedramNagendra BoyellaPas encore d'évaluation

- CVBVNBGVVVVVVVVVVVVVVVVVVVVVVVVVVVVVVVVVVVCXVDocument2 pagesCVBVNBGVVVVVVVVVVVVVVVVVVVVVVVVVVVVVVVVVVVCXVNagendra BoyellaPas encore d'évaluation

- NMDocument2 pagesNMNagendra BoyellaPas encore d'évaluation

- 72 Adiabatic Midwest97 PDFDocument4 pages72 Adiabatic Midwest97 PDFNagendra BoyellaPas encore d'évaluation

- 9659799Document20 pages9659799Nagendra BoyellaPas encore d'évaluation

- SQP Maths XiiDocument15 pagesSQP Maths XiiAbhishek GoyalPas encore d'évaluation

- Semiconductor Basics: N Pérez SM Olaizola 2004Document33 pagesSemiconductor Basics: N Pérez SM Olaizola 2004swad1705Pas encore d'évaluation

- Admissions Flowchart PDFDocument1 pageAdmissions Flowchart PDFNagendra BoyellaPas encore d'évaluation

- MuxDocument5 pagesMuxNagendra BoyellaPas encore d'évaluation

- DFFDocument5 pagesDFFNagendra BoyellaPas encore d'évaluation

- Cpe358/Cs381 Switching Theory and Logical Design Class 2Document41 pagesCpe358/Cs381 Switching Theory and Logical Design Class 2Santhi SriPas encore d'évaluation

- 713 KouthaDocument32 pages713 KouthaNagendra BoyellaPas encore d'évaluation

- Nand 2 Nor 2Document19 pagesNand 2 Nor 2Nagendra BoyellaPas encore d'évaluation

- What Is LatchupDocument15 pagesWhat Is LatchupNagendra BoyellaPas encore d'évaluation

- Electronics - Basic CMOS Digital Circuits: Prof. M Arta Rencz, Gergely NagyDocument30 pagesElectronics - Basic CMOS Digital Circuits: Prof. M Arta Rencz, Gergely NagyMuhammad NasirPas encore d'évaluation

- Current MirrorsDocument17 pagesCurrent MirrorsNagendra BoyellaPas encore d'évaluation

- Design Doc MemDocument3 pagesDesign Doc MemNagendra BoyellaPas encore d'évaluation

- A - Sit Up B-Jack KnifeDocument2 pagesA - Sit Up B-Jack KnifeNagendra BoyellaPas encore d'évaluation

- Abdominal ExercisesDocument1 pageAbdominal ExercisesNagendra BoyellaPas encore d'évaluation

- A - Sit Up B-Jack KnifeDocument2 pagesA - Sit Up B-Jack KnifeNagendra BoyellaPas encore d'évaluation

- IC Fabrication NotesDocument134 pagesIC Fabrication NotesArooj RazaPas encore d'évaluation

- AssignmentDocument6 pagesAssignmentNagendra BoyellaPas encore d'évaluation

- Material TestingDocument1 pageMaterial TestingNafees AhmedPas encore d'évaluation

- Lesson Plan Microprocessor and Micro COntrollerDocument7 pagesLesson Plan Microprocessor and Micro COntrollerRaja Pirian0% (2)

- MAC Unit Using Carry Lookahead Adder and Wallace Tree MultiplierDocument11 pagesMAC Unit Using Carry Lookahead Adder and Wallace Tree MultiplierAnandPas encore d'évaluation

- MSP430™ Programming With The JTAG Interface: User's GuideDocument98 pagesMSP430™ Programming With The JTAG Interface: User's Guideagsan.algabh2718Pas encore d'évaluation

- Design With Operational Amplifiers and Analog Integrated Circuits 3E (Sergio Franco)Document334 pagesDesign With Operational Amplifiers and Analog Integrated Circuits 3E (Sergio Franco)kamran_450770450% (2)

- High Performance, Low Cost Microprocessor (US Patent 5530890)Document49 pagesHigh Performance, Low Cost Microprocessor (US Patent 5530890)PriorSmartPas encore d'évaluation

- Programmable Logic Overview - PLD, CPLD, FPGADocument8 pagesProgrammable Logic Overview - PLD, CPLD, FPGADaniel VoineaPas encore d'évaluation

- 16 Pulse Circuit With Contactor Solution ENGDocument3 pages16 Pulse Circuit With Contactor Solution ENGIndustrial ItPas encore d'évaluation

- Unit 1 PDFDocument14 pagesUnit 1 PDFMridupaban DuttaPas encore d'évaluation

- Defination of ROMDocument4 pagesDefination of ROMshubham shakyaPas encore d'évaluation

- Arm Based MicrocontrollerDocument44 pagesArm Based MicrocontrollerNavin KhatriPas encore d'évaluation

- Transmission GateDocument7 pagesTransmission GateVenkatesh VeluvoluPas encore d'évaluation

- VHDL Tutorial Using Aldec VHDL SoftwareDocument22 pagesVHDL Tutorial Using Aldec VHDL SoftwaresumaPas encore d'évaluation

- Mazda Panasonic Cn-Vm4360a Service ManualDocument43 pagesMazda Panasonic Cn-Vm4360a Service ManualElijah ChristensenPas encore d'évaluation

- Memory Chips and Finite State MachinesDocument18 pagesMemory Chips and Finite State MachinesAlexander TaylorPas encore d'évaluation

- DTMF Chip Flow PictureDocument1 pageDTMF Chip Flow Pictureswathikomati7870Pas encore d'évaluation

- Datasheet PiccoloDocument177 pagesDatasheet PiccoloEric DilgerPas encore d'évaluation

- Lab Session # 9 Finite State Machines (FSMS) : W), and Produces A Set of Outputs (Z)Document7 pagesLab Session # 9 Finite State Machines (FSMS) : W), and Produces A Set of Outputs (Z)Ahmad M. HammadPas encore d'évaluation

- 8086 Memory AddressingDocument9 pages8086 Memory AddressingPera Detlic0% (1)

- Prac 2 - Registers and Combinational Logic in VHDL: Design TaskDocument4 pagesPrac 2 - Registers and Combinational Logic in VHDL: Design TaskquintqasPas encore d'évaluation

- Lab No.9 Design of Synchronous Counter ObjectivesDocument5 pagesLab No.9 Design of Synchronous Counter Objectivesasadmehmoodsatti786Pas encore d'évaluation

- KEC-751B (VLSI Design Lab)Document44 pagesKEC-751B (VLSI Design Lab)ABHAY CHAUHANPas encore d'évaluation

- Logic FamiliesDocument29 pagesLogic FamiliesSid SinhaPas encore d'évaluation

- Introduction To Cplds and Fpgas: by N.ChandrasekharanDocument21 pagesIntroduction To Cplds and Fpgas: by N.ChandrasekharanWilliam Arief WengPas encore d'évaluation

- Tutorial On Cadence Virtuoso - IISCDocument8 pagesTutorial On Cadence Virtuoso - IISCK Sri KarthikPas encore d'évaluation

- Carry Save AdderDocument8 pagesCarry Save AdderSwati Malik33% (3)