Académique Documents

Professionnel Documents

Culture Documents

CS4355 Parallel Computing: Schedule, Utilization, Matrix Multiplication

Transféré par

Riyanny 'Wiwied' PratiwiDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

CS4355 Parallel Computing: Schedule, Utilization, Matrix Multiplication

Transféré par

Riyanny 'Wiwied' PratiwiDroits d'auteur :

Formats disponibles

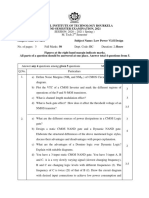

Introduction to Parallel Computing

CS4355/5325

Assignment 1

Due Date: September 17, 2009

1) Consider a processor with two pipelines with ability to simultaneously issue two instructions per

cycle.

a. Do the execution schedule for the code fragments in figure 2.1 (ii) and figure 2.1 (iii) in

the text book.

b. Do the utilization trace of the processor for both cases(figure 2.1 (ii) and figure 2.1 (iii))

2) Consider 1 GHz processor with 100 ns (nano second) latency DRAM. We have cache with size 32

KB with latency of 1 ns (1 cycle is 1 ns). Assume that we will multiply two 32x32 matrices

(A.B=C). Each matrix has integer values which are one word. A word size is 32 bits. Assume

memory to cache latency is 100 ns. According to the above given specifications, show explicit

solutions for the followings:

a. What is the total number of operations for this matrix multiplication?

b. What is total time for the computation?

c. What is the peak computation rate?

3) What is the route taken from node # 13 to node # 42 for hypercube topology with e-cube

routing algorithm with the least significant bit approach? Calculate each hop step by step.

13 (001101)->42(101010)

Vous aimerez peut-être aussi

- 2011 Advanced Computer Architecture: CS/B.TECH (CSE) /SEM-4/CS-403/2011Document7 pages2011 Advanced Computer Architecture: CS/B.TECH (CSE) /SEM-4/CS-403/2011Avik MitraPas encore d'évaluation

- 173 CSE313 FinalDocument2 pages173 CSE313 FinalSabbir HossainPas encore d'évaluation

- Gate Sample PaperDocument7 pagesGate Sample Papershettyashwin19Pas encore d'évaluation

- Btech Cs 3 Sem Computer Organization and Architecture rcs302 2022Document2 pagesBtech Cs 3 Sem Computer Organization and Architecture rcs302 2022GsgsgdhPas encore d'évaluation

- Please Check That This Question Paper Contains 9 Questions and 2 Printed Pages Within First Ten MinutesDocument2 pagesPlease Check That This Question Paper Contains 9 Questions and 2 Printed Pages Within First Ten Minutesdilpreet kaurPas encore d'évaluation

- Tute AnswersDocument11 pagesTute AnswerschulaPas encore d'évaluation

- NED University CS-531 Advanced Operating Systems Spring 2018 ExamDocument2 pagesNED University CS-531 Advanced Operating Systems Spring 2018 ExamTabish KhalidPas encore d'évaluation

- Thapar University, Patiala: Proc # RTN #A RTN #B RTN #C RTN #DDocument2 pagesThapar University, Patiala: Proc # RTN #A RTN #B RTN #C RTN #DAdamyaKaushikPas encore d'évaluation

- MST 2017 (O) PDFDocument2 pagesMST 2017 (O) PDFAdamyaKaushikPas encore d'évaluation

- KCS401 - OS - Final Question BankDocument6 pagesKCS401 - OS - Final Question Bankparidhiagarwal129Pas encore d'évaluation

- CSO Model PaperDocument2 pagesCSO Model PaperDeepak GourPas encore d'évaluation

- CAO Set 8Document8 pagesCAO Set 8Vilayat AliPas encore d'évaluation

- Computer Architecture Sample PaperDocument3 pagesComputer Architecture Sample Paperarnab_bhattacharj_26Pas encore d'évaluation

- CS6414 RTSD (21-22 End)Document2 pagesCS6414 RTSD (21-22 End)Pulakesh BagPas encore d'évaluation

- NIT Rourkela B.Tech Computer Organization Exam QuestionsDocument2 pagesNIT Rourkela B.Tech Computer Organization Exam QuestionsSatya DasPas encore d'évaluation

- 2008 FinalExam SoCN Final Master SolutionDocument10 pages2008 FinalExam SoCN Final Master SolutionBobby BeamanPas encore d'évaluation

- LDCA Previous Year PaperDocument4 pagesLDCA Previous Year Paperflipkart6392Pas encore d'évaluation

- Sheet 1Document2 pagesSheet 1nilay kharePas encore d'évaluation

- 2011 Basic Computation and Principles of Computer ProgrammingDocument7 pages2011 Basic Computation and Principles of Computer ProgrammingAman AgarwalPas encore d'évaluation

- HMK 4 ARCDocument3 pagesHMK 4 ARCskeletorfearsmePas encore d'évaluation

- Computer Organization Jan 2010Document2 pagesComputer Organization Jan 2010Prasad C MPas encore d'évaluation

- Technical Symposium MCQ Quiz on Telecom and Computer FundamentalsDocument4 pagesTechnical Symposium MCQ Quiz on Telecom and Computer Fundamentalskarthicktheboss1Pas encore d'évaluation

- Computer Organization Architecture RCS 302Document2 pagesComputer Organization Architecture RCS 302yugam sainiPas encore d'évaluation

- Electronic Structure Calculations on Graphics Processing Units: From Quantum Chemistry to Condensed Matter PhysicsD'EverandElectronic Structure Calculations on Graphics Processing Units: From Quantum Chemistry to Condensed Matter PhysicsRoss C. WalkerPas encore d'évaluation

- Btech Cs 3 Sem Computer Organization and Architecture kcs302 2022Document2 pagesBtech Cs 3 Sem Computer Organization and Architecture kcs302 2022Harshit dubeyPas encore d'évaluation

- MidtermsolutionsDocument3 pagesMidtermsolutionsRajini GuttiPas encore d'évaluation

- RT31055102020Document2 pagesRT31055102020elisha emilianPas encore d'évaluation

- NIT ROURKELA END SEM EXAMINATION EC-6210 LOW POWER VLSI DESIGNDocument3 pagesNIT ROURKELA END SEM EXAMINATION EC-6210 LOW POWER VLSI DESIGNajay vermaPas encore d'évaluation

- University of Ghana Computer Science Exam Designs 4-Bit CPU Logic CircuitsDocument3 pagesUniversity of Ghana Computer Science Exam Designs 4-Bit CPU Logic CircuitsPhilip Pearce-PearsonPas encore d'évaluation

- B) The Introduction of ParallelismDocument1 pageB) The Introduction of ParallelismBanan Al BarghouthiPas encore d'évaluation

- MCS 012Document4 pagesMCS 012rajatkumar.codingPas encore d'évaluation

- COA-Final Exam-2011Document2 pagesCOA-Final Exam-2011mulugetahiluf995Pas encore d'évaluation

- Computer Architecture exam questionsDocument2 pagesComputer Architecture exam questionssandeepaprPas encore d'évaluation

- MEL G642-Compre Solution - 2 2016-17Document9 pagesMEL G642-Compre Solution - 2 2016-17Gaurav PatilPas encore d'évaluation

- Paper - Iii Computer Science: Note: Attempt All The Questions. Each Question Carries Two (2) Marks. 1Document18 pagesPaper - Iii Computer Science: Note: Attempt All The Questions. Each Question Carries Two (2) Marks. 1Meenalochini GanesanPas encore d'évaluation

- Assignment 1Document2 pagesAssignment 1Samira YomiPas encore d'évaluation

- Computer Organization and ArchitectureDocument3 pagesComputer Organization and ArchitecturecoolshubupaunikarPas encore d'évaluation

- Computer Architecture: CS/B.TECH (CSE-NEW) /SEM-4/CS-403/2012Document8 pagesComputer Architecture: CS/B.TECH (CSE-NEW) /SEM-4/CS-403/2012Avik MitraPas encore d'évaluation

- Network Basics CollectionDocument11 pagesNetwork Basics Collectionrocks66aryanPas encore d'évaluation

- Os - 2Document1 pageOs - 2Kannan ThenmozhiPas encore d'évaluation

- Coa 21 22Document2 pagesCoa 21 22Dev RathorePas encore d'évaluation

- Solutions To Set 8Document18 pagesSolutions To Set 8kitana_sectPas encore d'évaluation

- COA KCS-302 Model Question Paper: Computer Organization & Architecture (Dr. A.P.J. Abdul Kalam Technical University)Document3 pagesCOA KCS-302 Model Question Paper: Computer Organization & Architecture (Dr. A.P.J. Abdul Kalam Technical University)Piyush GuptaPas encore d'évaluation

- Coa MCQDocument12 pagesCoa MCQAdithya R AnandPas encore d'évaluation

- Assignment 1 MCQDocument4 pagesAssignment 1 MCQamit dava0% (1)

- Technical Symposium Questions and AnswersDocument7 pagesTechnical Symposium Questions and AnswersprachiumangPas encore d'évaluation

- Btech Cs 3 Sem Computer Organization and Architecture rcs302 2020Document2 pagesBtech Cs 3 Sem Computer Organization and Architecture rcs302 2020Vishal Kumar SharmaPas encore d'évaluation

- Os + DsDocument12 pagesOs + DsAniket AggarwalPas encore d'évaluation

- 4TE05AMP1Document3 pages4TE05AMP1shah nisit nPas encore d'évaluation

- Online Exam for Operating Systems (Autumn 2021Document24 pagesOnline Exam for Operating Systems (Autumn 20219103SHIVAM JANAPas encore d'évaluation

- 3D Finite Difference Computation On Gpus Using Cuda: Paulius MicikeviciusDocument6 pages3D Finite Difference Computation On Gpus Using Cuda: Paulius MicikeviciusSiva GoPas encore d'évaluation

- Compre FinalDocument2 pagesCompre Finalf20201654Pas encore d'évaluation

- Introduction To Internet 2012 PDFDocument2 pagesIntroduction To Internet 2012 PDFPratap Kumar MahatoPas encore d'évaluation

- ACFr Og Ajp 3 Woh Li TFaj WBBM PLa YIK8 Obdn FZ WVV9 O2 Anjwaz 88 Jzy XHUWlz 9541Document2 pagesACFr Og Ajp 3 Woh Li TFaj WBBM PLa YIK8 Obdn FZ WVV9 O2 Anjwaz 88 Jzy XHUWlz 9541abhijitmandal27068Pas encore d'évaluation

- Subject Code: 322847 (22) : B.E.8 Semester Class Test - I (13/05/2021)Document5 pagesSubject Code: 322847 (22) : B.E.8 Semester Class Test - I (13/05/2021)Rajat JainPas encore d'évaluation

- Coa 2017Document4 pagesCoa 2017god level ytPas encore d'évaluation

- Q Sta CompDocument18 pagesQ Sta Compshravan2312Pas encore d'évaluation

- Akash Exam 2019 OSDocument1 pageAkash Exam 2019 OShaso khul ke hahaPas encore d'évaluation

- AxesDocument5 pagesAxesArchana RohitPas encore d'évaluation

- Mathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsD'EverandMathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsRoderick MelnikPas encore d'évaluation

- Fill in The Blanks !Document2 pagesFill in The Blanks !Riyanny 'Wiwied' PratiwiPas encore d'évaluation

- Annex-A - UK-final BDocument2 pagesAnnex-A - UK-final BRiyanny 'Wiwied' PratiwiPas encore d'évaluation

- Modul 8Document9 pagesModul 8Riyanny 'Wiwied' PratiwiPas encore d'évaluation

- Masalah Dualitas: N 1 J J JDocument9 pagesMasalah Dualitas: N 1 J J JRiyanny 'Wiwied' PratiwiPas encore d'évaluation

- Intro to Structural Design of BuildingsDocument1 pageIntro to Structural Design of BuildingsRiyanny 'Wiwied' PratiwiPas encore d'évaluation

- 1A Title Page - UK-finalDocument1 page1A Title Page - UK-finalRiyanny 'Wiwied' PratiwiPas encore d'évaluation

- 1 Contents Part A: Buildings, Structures and MechanicsDocument2 pages1 Contents Part A: Buildings, Structures and MechanicsRiyanny 'Wiwied' PratiwiPas encore d'évaluation

- Annex-C - UK-final FDocument1 pageAnnex-C - UK-final FRiyanny 'Wiwied' PratiwiPas encore d'évaluation

- Ways To Refuse To Do Something1Document1 pageWays To Refuse To Do Something1Riyanny 'Wiwied' PratiwiPas encore d'évaluation

- Intro to Structural Design of BuildingsDocument1 pageIntro to Structural Design of BuildingsRiyanny 'Wiwied' PratiwiPas encore d'évaluation

- Expressing AgreementDocument1 pageExpressing AgreementRiyanny 'Wiwied' PratiwiPas encore d'évaluation

- Assignment 3 CSCI 4355/5325introduction To Parallel Programming Hello MPI Due Date: October 15, 2009Document1 pageAssignment 3 CSCI 4355/5325introduction To Parallel Programming Hello MPI Due Date: October 15, 2009Riyanny 'Wiwied' PratiwiPas encore d'évaluation