Académique Documents

Professionnel Documents

Culture Documents

ECS Trans. 2014 Federspiel 127 34

Transféré par

Shruti MehrotraCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

ECS Trans. 2014 Federspiel 127 34

Transféré par

Shruti MehrotraDroits d'auteur :

Formats disponibles

ECS Transactions, 61 (3) 127-134 (2014)

10.1149/06103.0127ecst The Electrochemical Society

Effect of SOI substrate on CMOS devices reliability

X.Federspiel, W. Arfaoui, D.Angot, F. Monsieur, M.Rafik, P.Mora, F. Cacho, D. Roy,

V.Huard

STMicroelectronics 850 rue Jean Monnet 38926 Crolles, France

In this paper we will review the mains consequences of the

integration of buried oxide (Box) on CMOS device reliability,

since the presence of BOx under CMOS devices has already been

largely referred in the literature as being responsible for parasitic

self-polarization, or unwanted joule heating with negative impact

on device reliability. First the reliability of BOx itself will be

reviewed, BOx interface defect generation will be analyzed, then

the used of body bias polarization on transistor degradation

mechanisms (time dependent breakdown tddb, negative bias temp

instability NBTI, hot carrier injection HCI) will be presented with

a special focus on hci reliability and its dependence on body bias

polarization.

Performance of FDSOI technology

FDSOI (Fully Depleted SOI, Figure 1) technology process has been evidenced as very

attractive for low power application due to the very good control of short channel effects

and very good isolation of neighboring devices [1,2]. Besides, the use of undopped

channel improves mobility in the channel as well as device matching (Figure 2).

Ultimately the proposed architecture allows a wide range of back bias voltage operation

and the possibility to adapt the device performance or power consumption dynamically

with very limited reliability penalty regardless the performance gain. On Figure 3, we

reported the evolution of N and P fet transistor device threshold voltage Vth as function

of back-bias in forward and reverse condition. It is worth noting that Vth is a linear

function of Vb [3,4], unlike cmos devices on bulk Silicon substrate for which Vth is

function of the square root of body bias Vb. It was shown that linear dependence relates

to coupling between front gate FG and back gate BG (back plane to control

polarization under buried oxide). :

FG = Cbox / Cox.Csi / (Cbox+Csi)

(1)

BG = Cbox / Cox. (Cbox+Csi) / Csi

(2)

The wide modulation of FET Vth is used in FDSOI technology to boost circuit speed

(Forward Body Bias FBB, lowered Vth) or save power (Reverse Body Bias RBB,

Increased Vth) to adapt circuit to various mission profiles, i.e. boost portable device CPU

for gaming, or save power in standby mode.

Device Reliability Methodology

In advanced CMOS technology nodes, trade-off between performances and reliability

plays an importance role in fabrication process optimization. Process development relies

not only on usual figures of merit such as Ion/Ioff, Vth(L) etc but also on End-Of-Life

Ion drift, Vth drift or time to breakdown. In addition to electrical characterization of

127

Downloaded on 2016-02-01 to IP 115.248.114.51 address. Redistribution subject to ECS terms of use (see ecsdl.org/site/terms_use) unless CC License in place (see abstract).

ECS Transactions, 61 (3) 127-134 (2014)

MOS device, reliability tests [5], including gate dielectric tddb, as well as parameter drift

under HCI and NBTI stress are performed. In the following we will report the outcome of

reliability test performed on CMOS devices manufactured on SOI substrate but also

reliability tests performed on buried oxide layer itself.

Buried oxide reliability

Buried Oxide reliability was characterized by means of linear voltage ramp stress as well

as constant voltage stress. Constant voltage stress consists in applying a constant voltage

over buried oxide capacitor with front side transistor in inversion mode and to track

buried oxide breakdown (current leakage increase) of transistor parameter drift induced

by interface defects generation. From voltage ramped stress we found that breakdown

voltage is above 30V, corresponding to Efield of 12MV/cm which is comparable to thick

oxide transistor Efield, and smaller to that of gate of logic transistors. From this

perspective, reliability of Box is similar to that of thick oxide manufactured by furnace

process for which bulk oxide defects is the key parameter. However, time to breakdown,

projected to operating voltage show a huge margin consisting of several time decades

(Figure 5). Besides, transistor parameters drift under back bias stress occurs above 20V

and also exhibit large lifetime margins (Figure 6), while projected to operating conditions.

Additionally, MOS parameters drift (Ion, Vth), were also measured under various bulk

bias stress condition in the 19V to 23V range to build a parameter drift model used in

turn to extrapolate drift at operating voltage (1.8V maximum bulk bias), showing large

reliability margins. In depth analysis of Vth drift after back bias stress was measured for

various back-bias to track any change in coupling factor. Vth(Vb) still follows linear

trend as mentioned above, but with changes of coupling factor that is attributed to front

side traps, which charge status is function of back bias polarization ( data not shown here,

details given in [6]).

Gate dieletric reliability

A direct comparison of 28nm bulk vs 28nm SOI technology shows that gate dielectrics

related failure modes (time dependent breakdown and transistor parameter drift under

vertical electrical field and / or hot carrier injection) are un-affected by the presence of

buried oxide (Figure 7), since the vertical electrical field and gate stack composition are

the same. At the same time, we also evidenced that additional back bias does not

influence neither tddb (Figure 8) nor NBTI (Figure 9). This is consistent with screening

of applied back bias by the inversion layer. Additionally, we analyzed electrical defect

signature to track the defect generation on the channel back-side[6]. It was found that in

extreme back bias configuration only (>4-6V), defects can be generated at bottom

interface.

Hot carrier injection

Thin and thick oxide transistor device were submitted to HCI stress at mid Vg and

Vg=Vd condition. We found that hci voltage acceleration factor corresponding to MOS

transistors on FDSOI substrate is similar to that of devices on bulk (Figure 10) and that

HCI does not introduce defects on back-side interface [7].

We also reported a full characterization of Tsi (Figure 11) and back bias (Figure 12)

effect on HCI defect generation confirming the primary effect of carrier energy over

carrier density giving a comprehensive framework to the general behavior of 28FDSOI

performance-reliability trade-off. As a matter of fact, we found out that degradation with

stress current, increasing either drain voltage or body bias follows different trend (Figure

12). In particular, for same stress current, degradation is less in FBB than drain overdrive,

for which it is well understood that carrier energy is higher. It is worth noting that the

improvement of reliability trade-off obtained in FBB is confirmed by reliability tests

128

Downloaded on 2016-02-01 to IP 115.248.114.51 address. Redistribution subject to ECS terms of use (see ecsdl.org/site/terms_use) unless CC License in place (see abstract).

ECS Transactions, 61 (3) 127-134 (2014)

performed on ring oscillators for which better performance is obtained without drift

penalty (Figure 13). Similarly, decreasing silicon film thickness is expected to improve

carrier confinement, to reduce short channel effect and increase carrier energy. The

observed increase of hci degradation is similar to published results on fin FET device

[8,9] and is most likely to have the same origin, meanwhile authors claims primary

effect of enhanced self-heating.

As a matter of fact, transistor devices on SOI substrates as well as fin FET device are

often reported as being affected by excessive channel temperature increase due to thermal

resistance increase in presence of buried oxide layer [10, 11, 12]. Most of published

works report results obtained from partially depleted devices with very thick buried oxide

layer (up to ~1 um, [15]) for which self-heating can increase channel temperature of

about 100-200C with dramatic acceleration of wear out mechanisms such as hot carrier or

even leading to BTI degradation along channel [11, 13, 14]. We observed that for 28nm

FDSOI devices, even in presence of channel self-heating comparable to that of fin FETs

[16], degradation induced by hot carrier injection is not growing according to Ion / power

dissipation increase while thinning the gate oxide (I/O device Figure 14). We also noted

that HCI temperature activation is slightly negative, (Figure 15), which is consistent with

our previous observation that even in presence of significant power dissipation (i.e. selfheating), HCI degradation is not accelerated. In addition we found that Vth drift under

HCI in linear and saturated condition differs by a factor of 5, showing that, unlike PBTI

case, defect is localized on drain side and not distributed along the channel.

Conclusions

28nm FDSOI devices were submitted to electrical reliability tests. Buried oxide reliability

was found to have large margin and not being a limiting factor for circuit design. We

demonstrated that gate dielectric reliability is unaffected by the underlying oxide layer,

whereas hot carrier injection is moderately affected by silicon film thickness. Intrinsic

wear-out mechanisms as well as effect of Tsi and Vb on transistors failure mode were

quantified to be implemented in circuit simulators.

Figure 1: TEM cross section of FDSOI transistor device, channel length is 24nm, silicium

film thickness is 7nm, buried oxide thickness 25nm.

129

Downloaded on 2016-02-01 to IP 115.248.114.51 address. Redistribution subject to ECS terms of use (see ecsdl.org/site/terms_use) unless CC License in place (see abstract).

ECS Transactions, 61 (3) 127-134 (2014)

0.055

0.050

Bulk28nm

FDSOI28nm

0.045

sigma Vth [V]

0.040

0.035

0.030

0.025

0.020

0.015

0.010

0.005

0.000

0

10

15

20

25

1/sqrt(WxL) [1/um]

Threshold Voltage [mV]

Figure 2 : Vth mismatch as function of square root of device surface with Pelgrom model

for 28nm on bulk silicon compared to FDSOI

1200

1000

800

600

400

200

0

-200

-400

-600

-800

-1000

-1200

-1400

-12 -10

Nfet

Pfet

-8

-6

-4

-2

Body Bias [V]

22

20

18

16

14

12

10

8

6

4

2

0

EbdMVcm

Tickness

250

200

150

100

50

OXide Thickness [nm]

Ebd [MV/cm]

Figure 3 : Evolution of Nfet and Pfet threshold voltage Vth as function of body bias Vb

0

Gate

I/O

Low-k Furnace oxide Box

Dielectric

Figure 4 : Efield to breakdown of selected dielectrics of CMOS components

130

Downloaded on 2016-02-01 to IP 115.248.114.51 address. Redistribution subject to ECS terms of use (see ecsdl.org/site/terms_use) unless CC License in place (see abstract).

ECS Transactions, 61 (3) 127-134 (2014)

Time to Breakdown [a.u.]

1000

100

10

28.0

28.5

29.0

29.5

30.0

Back Bias [V]

Figure 5: Evolution of time to breakdown of 250nm thick Buried Oxide as function of

back bias

100

Vth Drift [%]

10

Vb19V

Vb21V

Vb22V

Vb24V

Vb23V

0.1

10

-1

10

10

10

10

10

10

10

10

10

Stress Time [a.u.]

Figure 6: Vth drift over stress time for various Vb stress condition.

TimeToBreakdown [a.u.]

NfetFD

NfetLP

PfetFD

PfetLP

1000

100

10

2.2

2.3

2.4

2.5

2.6

2.7

2.8

Gate Voltage [V]

Figure 7: Comparison of time to breakdown of Nfet and PFet thin oxide device on bulk

(LP)and FDSOI substrates.

131

Downloaded on 2016-02-01 to IP 115.248.114.51 address. Redistribution subject to ECS terms of use (see ecsdl.org/site/terms_use) unless CC License in place (see abstract).

ECS Transactions, 61 (3) 127-134 (2014)

2

SGPfet

SGPfetFBB

SGNfet

SGNfetFBB

Wbit

0

-1

-2

-3

-4

0.1

10

TimeToBReakdown [a.u.]

Figure 8 : Comparison cumulated distribution of time to breakdown of thin oxide Nfet

and Pfet with and without bulk bias, on Weibull scale.

0.09

Vg18Vb0

Vg22Vb0

Vg18Vb2

Vg22Vb2

0.08

Vth Drift [V]

0.07

0.06

0.05

0.04

0.03

0.02

0.01

Time [a.u.]

Figure 9: Comparison of NBTI induced Vth degradation over stress time of SG Pfets at

Vg=1.8V and 2.2V with or without back bias.

Ion Drift 28LP [a.u.]

Ion Drift 28FD [a.u.]

FDSOI

Bulk

1.20

1.25

1.30

1.35

1.40

1.45

1.50

1.55

1.60

1.65

1.70

Stress Voltage [V]

Figure 10: Comparison of hci voltage acceleration of bulk and FDSOI thin oxide Nfet

devices.

132

Downloaded on 2016-02-01 to IP 115.248.114.51 address. Redistribution subject to ECS terms of use (see ecsdl.org/site/terms_use) unless CC License in place (see abstract).

ECS Transactions, 61 (3) 127-134 (2014)

1.2

1.0

Ion drift [a.u.]

0.8

0.6

0.4

0.2

0.0

Tsi

Figure 11: Relative Ion drift under hci stress as function of Silicon film thickness.

18

16

Ion drift [%]

14

12

10

8

VgVdnoFBB

FBB1

FBB2

6

4

2

0.900.951.001.051.101.151.201.251.301.351.401.45

Stress Current [mA]

Figure 12: Evolution of HCI drift as function of stress current without or without back

bias, showing for same stress current less degradation in FBB.

4.5%

4.0%

Frequency Drift

3.5%

3.0%

2.5%

2.0%

Vb0

FBB

1.5%

1.0%

0.5%

0.0%

1.2

1.3

1.4

1.5

1.6

1.7

Ring Oscillator Frequency [a.u.]

Figure 13: Drift of Ring Oscillator Frequency as function of frequency at stress condition

with or with forward back bias.

133

Downloaded on 2016-02-01 to IP 115.248.114.51 address. Redistribution subject to ECS terms of use (see ecsdl.org/site/terms_use) unless CC License in place (see abstract).

ECS Transactions, 61 (3) 127-134 (2014)

30

HCI drift [a.u.]

25

20

15

10

5

0

500

600

700

800

900

IdsatF [uA/um], Gate thickness splits from 45 to 34A

Figure 14: HCI induced Idsatf drift as function of fresh Ion over various Tinv thickness

splits, showing no excess of degradation with increasing Ion and dissipated power.

T125C

T90C

T50C

0.25

Vth Drift [a.u.]

0.20

0.15

0.10

0.05

0.00

10

100

1000

Stress Time [s]

Figure 15:Evolution of hci induced drift as function of temperature, showing negative

activation energy around 0.17eV

References

1. Planes N., VLSI 2012.

2. Arnaud F., IEDM 2012.

3. Noel J.P., Trans. On Electron. Devices 2011.

4. Poiroux T, IEEE SOI conf. 2004.

5. Strong A., et al., reliability wearout mechanisms in advanced CMOS

Technologies, IEE Press series, Wiley 2009.

6. Angot D., IEEE IIRW2012.

7. Brunet L., IEE IRPS 2012.

8. Ramey S., Tutorial IEEE IRPS 2013.

9. Chabukswar S., Microelectronic Engineering 87 (2010) 19631967

10. Fiegna C., IEE trans. On Electron. Device, vol. 55, No. 1, 2008.

11. Roux J-M, IEE IRPS 2007.

12. Mittl S., IEEE IRPS 2012.

13. Rauch S., Trans on Device Material and Reliablity 2010.

14. Wang, IEEE IRPS 2007.

15. Dieudonne F., 25th Int Conf on Microelectronics 2006.

16. Prasad S., IEEE IRPS 2013.

134

Downloaded on 2016-02-01 to IP 115.248.114.51 address. Redistribution subject to ECS terms of use (see ecsdl.org/site/terms_use) unless CC License in place (see abstract).

Vous aimerez peut-être aussi

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5795)

- Eurosoi-Ulis 2018 FinalDocument4 pagesEurosoi-Ulis 2018 FinalShruti MehrotraPas encore d'évaluation

- 0 - 2015 ITRS 2.0 Executive Report PDFDocument79 pages0 - 2015 ITRS 2.0 Executive Report PDFShruti MehrotraPas encore d'évaluation

- Mess Menu W.E.F. April 2016 Breakfast Lunch Dinner: Daily Monday Tuesday Wednesday Thursday Friday Saturday SundayDocument1 pageMess Menu W.E.F. April 2016 Breakfast Lunch Dinner: Daily Monday Tuesday Wednesday Thursday Friday Saturday SundayShruti MehrotraPas encore d'évaluation

- ADBMS AssignmentDocument9 pagesADBMS AssignmentShruti Mehrotra100% (1)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- DGC 6D PDFDocument10 pagesDGC 6D PDFsurender kumarPas encore d'évaluation

- Short Answer Type Questions: Unit Ii Voltage Source ConvertersDocument7 pagesShort Answer Type Questions: Unit Ii Voltage Source ConvertersBhanu Ganesh LukkaPas encore d'évaluation

- Current BrochureDocument6 pagesCurrent BrochureKym GilhamPas encore d'évaluation

- D880 2SD880 Silicon NPN Power Transistors DatasheetDocument3 pagesD880 2SD880 Silicon NPN Power Transistors Datasheetlagarra50Pas encore d'évaluation

- Centre TapDocument3 pagesCentre TapEric GithinjiPas encore d'évaluation

- 8BK20 Operation enDocument24 pages8BK20 Operation enMufasa 7762Pas encore d'évaluation

- Sbec Plus FanDocument2 pagesSbec Plus FanSonny Adi WicaksonoPas encore d'évaluation

- SolaX Power Troubleshooting X3 MIC PDFDocument10 pagesSolaX Power Troubleshooting X3 MIC PDFmarketingsunfix sunfixPas encore d'évaluation

- MN04008005E HMAX Installation ManualDocument76 pagesMN04008005E HMAX Installation ManualSriniPas encore d'évaluation

- LM338K Regulador de VoltageDocument12 pagesLM338K Regulador de Voltagealexjcc10Pas encore d'évaluation

- Transducers: Light Dependent ResistorDocument3 pagesTransducers: Light Dependent ResistorIssa GrantPas encore d'évaluation

- Atlas Copco GA 15 To GA 30 Part List 24 25Document2 pagesAtlas Copco GA 15 To GA 30 Part List 24 25RICHARDPas encore d'évaluation

- Harmonics & There Filters 1Document41 pagesHarmonics & There Filters 1Talha MehmoodPas encore d'évaluation

- Capacitor Charging and DischargingDocument4 pagesCapacitor Charging and DischargingAnanya GoyalPas encore d'évaluation

- Pareto APU FaultDocument44 pagesPareto APU FaultimannurPas encore d'évaluation

- Amplificator Chitara 60WDocument5 pagesAmplificator Chitara 60WMărian IoanPas encore d'évaluation

- AMW Services SDN BHD Presentation - 9. January 2012-NewDocument26 pagesAMW Services SDN BHD Presentation - 9. January 2012-Newhizbi7Pas encore d'évaluation

- Step by Step Guide Book On Home WiringDocument50 pagesStep by Step Guide Book On Home WiringGerardo Mendoza100% (4)

- DatasheetDocument7 pagesDatasheetDarica Andojar TaparPas encore d'évaluation

- Transfer Switches: Technical Data TD01602016EDocument68 pagesTransfer Switches: Technical Data TD01602016EJohn SuarezPas encore d'évaluation

- 500KVA Technical Data Sheet INSO 1608 R1Document4 pages500KVA Technical Data Sheet INSO 1608 R1saravananPas encore d'évaluation

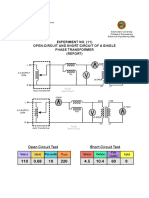

- Experiment No.11 - Machines LabDocument3 pagesExperiment No.11 - Machines LabSBPas encore d'évaluation

- Warning Lamps: "OIL W/L" When Ignition Switch Is in ON Position (Engine Stopped.) : On When Engine Running: OffDocument2 pagesWarning Lamps: "OIL W/L" When Ignition Switch Is in ON Position (Engine Stopped.) : On When Engine Running: OffSULIMAN HASSOUNAPas encore d'évaluation

- Siemens Internship ReportDocument17 pagesSiemens Internship ReportmirfanbilalPas encore d'évaluation

- Leslie Construction Project PDFDocument14 pagesLeslie Construction Project PDFMichael LeydarPas encore d'évaluation

- EMC Issue On HV SWGDocument9 pagesEMC Issue On HV SWGsusanto_andri_2005Pas encore d'évaluation

- Linkswitch-Cv Family: Energy-Efficient, Off-Line Switcher With Accurate Primary-Side Constant-Voltage (CV) ControlDocument21 pagesLinkswitch-Cv Family: Energy-Efficient, Off-Line Switcher With Accurate Primary-Side Constant-Voltage (CV) ControlAriel DajaoPas encore d'évaluation

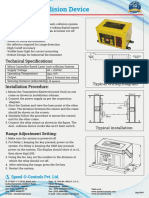

- Laser Anti Collision Device PDFDocument1 pageLaser Anti Collision Device PDFmanoj chougulePas encore d'évaluation

- 300VF WD DescriptionDocument59 pages300VF WD DescriptionSamuel Acevedo50% (2)

- EE213 Applied Electrical Engineering: Fall 2020 Mazhar JavedDocument18 pagesEE213 Applied Electrical Engineering: Fall 2020 Mazhar JavedElbert VonVerimPas encore d'évaluation