Académique Documents

Professionnel Documents

Culture Documents

Implementation of AMBA AHB Protocol Using Verilog HDL

Transféré par

Editor IJRITCCTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Implementation of AMBA AHB Protocol Using Verilog HDL

Transféré par

Editor IJRITCCDroits d'auteur :

Formats disponibles

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 4 Issue: 4

ISSN: 2321-8169

573 - 576

______________________________________________________________________________________

Implementation of AMBA AHB protocol using verilog HDL

Abhinandan Aggarwal

Prof. (Dr.) Neelam Sharma

Dept. of Electronics and communication Engineering

Maharaja Agrasen Institute of Technology, IPU

New Delhi, India

abhi2094@gmail.com

Dept. of Electronics and communication Engineering

Maharaja Agrasen Institute of Technology, IPU

New Delhi, India

neelam_sr@yahoo.co.in

Abstract Advanced Microcontroller Bus Architecture (AMBA) is a series of bus protocols provided by ARM. These include AHB, APB and

ASB. AMBA provides an on-chip communication standard for these buses to be used in high performance microcontrollers. In this paper we

have implemented the AMBA AHB (Advanced High-Performance Bus) which is used for high performance transfers among different modules

of the microcontroller. AHB supports efficient connection of processor, on chip memory, DMA and off chip external memories. AMBA AHB

system bus supports multiple bus masters and slaves. The design is implemented using Verilog HDL and simulated using ModelSim 6.4a.

Synthesis for the design is done using Xilinx ISE 14.4.

Keywords-AMBA;AHB;Arbitration;Burst; HDL ; Simulation;Synthsis;SOC; Verilog;

__________________________________________________*****_________________________________________________

I.

INTRODUCTION

In an SOC multiple blocks of IPs have to communicate and

this is achieved by well-defined communication protocols.

They are of great importance as they can have a great impact

on the systems performance. Some of the popular protocols

used in the industry include PCI, I2C, SPI, AMBA etc.

In this paper we have implemented a widely used industrial

protocol AMBA AHB. ARMs AMBA specification defines an

on chip communication standard for high performance systems.

AMBA is today the de facto standard for processors as it is

well documented and can be used without any royalties. It is

widely used in RAM controllers, DMA controllers and SOCs.

II.

BUS INTERCONNECTIONS

An AHB system consists of multiple masters from which

address and data signals are selected. The AMBA AHB bus

protocol is designed to be used with a central multiplexer

interconnection scheme. In this all bus masters drive out the

address and control signals indicating the transfer they wish to

perform and the arbiter determines which master has its

address and control signals routed to all of the slaves. A

central decoder is also required to control the read data and

response signal multiplexor, which selects the appropriate

signals from the slave that is involved in the transfer.

Figure 2 shows the interconnections between 3 masters and 4

slaves.

AHB sits above APB and implements the features required for

high performance which are:

Burst Transactions

Split Transactions

Single clock edge operation

Non tristate bus implementation.

Pipelined operation

AHB consists of multiple masters from which one is selected at

a time using the arbiter. Decoder is used to select one among

the multiple slaves that can be addressed.

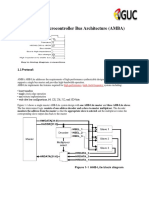

Figure 1. Shows how a typical AMBA based system looks like.

Figure 1 AMBA based system

Figure 2 Interconnections

.

573

IJRITCC | April 2016, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 4 Issue: 4

ISSN: 2321-8169

573 - 576

______________________________________________________________________________________

III.

AHB OPERATION

As seen in figure 2 AHB consists of multiple masters and

slaves, which are selected using arbiter and decoder

respectively. An AHB transfer starts when a master sends a

request to the arbiter for the bus. The arbiter uses a predefined

priority algorithm to arbitrate among the requests from

different masters. After selecting a particular master it then

grants the bus to that master.

The master which is granted the bus can now initiate

the transfer. It starts the transfer by driving the address and

control signals. These provide various information about the

address and the kind of operation (these will be discussed in a

following section). The master can also perform burst

transfers. There are two kinds of burst transfers that it can

perform incremental or wrapping burst transfers.

Each transfer consists of the following two cycles:

One address and control cycle

One or more data cycles

Slaves can insert wait states for sampling data but address

should be sampled at the same cycle. This can be done using

the HREADY signal by the slave. When low this signal

indicates the insertion of wait states by the slave. Slave can

also reflect the status of the transfer using the HRESP[1:0]

signal. Using this slave can provide OKAY, ERROR, RETRY

AND SPLIT responses.

IV.

AHB COMPONENTS

AMBA AHB consists of the following two global signals

which are same for all the components:

HCLK: this is the clock signal. All operations are

performed at the positive edge of this clock.

HRESETn: this is an active low reset. It is asserted

asynchronously and de-asserted synchronously.

The components of an AHB system are:

A. AHB Master

Master is the component that initiates the transfer. It sends

the request to the arbiter using the HBUSREQx singal and then

starts the transfer after receiving the grant from the arbiter this

is done by using the HGRANTx signal.

The transfer is performed in two phases the address phase

and the data phase. The address phase is a one cycle long phase

in which the address and the control signals are sent this is

performed at the start of the transaction after this the data phase

is started. In each cycle of the data phase the address of the

next data to be transferred is sent, this provides the pipelined

operation in AHB which makes it a high performance protocol.

The control information sent with the address includes:

HTRANS[1:0]: Provides the transfer type which can

be IDLE , BUSY , SEQ , NON-SEQ . The first

transfer in all burst transfers is NON-SEQ and the

remaining are SEQ.

HWRITE: High for write transfer and low for read

transfer.

HSIZE[2:0]: Indicates the size of transfer.

HBURST[2:0]: Indicates the kind of burst transfer.

HPROT[2:0] : It is a protection control signal. In this

paper it is considered to have a constant value.

In burst transfers the subsequent addresses are calculated by

the master according to the size of transfer, also the addresses

are required to be size aligned. Bursts should be such that they

do not cross 1kB address boundaries.

Apart from these signals a few auxiliary signals required by

the master to get information about address, control and data to

be sent are given to it.

B. AHB Arbiter

Arbiter is used to select a particular master among the

different masters that are currently requesting for the bus. A

fixed priority algorithm is used here to arbitrate among the

different requesting masters. In this algorithm the master are

given a fixed priority and the master having the highest

priority among the currently requesting masters is given the

grant to the bus. It also asserts the corresponding HMASTER

signal for the granted master in the next cycle, which is used

by the multiplexer to select the signals of the selected master

as shown in figure 2. HSPLITx signal is used by the arbiter

give back grant to a master which had been previously

removed due to a split response by a split capable slave.

During a burst transfer the master need not hold the

HBUSREQx signal as the arbiter will arbitrate again only after

the current burst transfer has completed or if the slave has

issued a split response.

A master can also assert the HLOCKx signal along with

the HBUSREQx signal which would indicate the arbiter to

perform a locked transfer and prevent it from granting the bus

to any other master. The arbiter indicates this by asserting the

HMASTLOCK signal.

C. AHB Slave

Slave responds to the transfers that are initiated by the

master. As multiple slaves are possible they are selected by

using the HSELx signal from the decoder. They are selected

on the basis of HADDR by the decoder. A slave has to be

allocated for a minimum of 1kB addresses so that address

boundaries are not crossed during a burst transfer.

Slave also provides the response for a transfer, it uses

HREADY signal to indicate wait states. A transfer can also be

aborted by slave but a master can never cancel a transfer once

it has started.

HRESP [1:0] signal is used by the slave to provide OKAY,

ERROR, RETRY or SPLIT responses. OKAY can be

provided in a single cycle but the others are two cycle

responses where in the first cycle HREADY is kept low with

the corresponding response on HRESP and in the second cycle

HREADY is made high keeping the HRESP same. This helps

the master to flush the pipeline.

D. AHB Decoder

Decoder is used to select the slave which is to be used in

the transfer. It uses HADDR to select the slave using HSELx

signal. This is also used to control the read data mux.

574

IJRITCC | April 2016, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 4 Issue: 4

ISSN: 2321-8169

573 - 576

______________________________________________________________________________________

E. AHB Multiplexers

In AHB address and control, write data and read data

multiplexers are used. Address and control mux and write data

mux are controlled by HMASTER signal from the arbiter and

read data mux is controlled by HSELx from the decoder.

V.

incremented by 4, for a halfword incremented by 2 and by 1 for

a byte transfer.

Figure 5 shows the operation for a burst 4 operation for a

word transfer followed by a burst 8 operation for a halfword

transfer.

SIMULATIONS

A. Single master operation

Figure 3 shows the operation of AHB for a single master

and slave. The first transaction is an incremental burst 4 write

followed by an incremental burst 8 write operation, which is

then followed by an incremental burst 8 read operation. The

response to this is given as an error response at the 7th cycle.

Figure 5 Incremental burst 4 and 8

Figure 3 Single master operation

B. Multi master simple write operation

Figure 4 shows the simulation for a single master simple

write operation. As shown in the figure master 1 being at the

highest priority gets the grant through the arbiter. An

undefined length incremental burst is used as the operation in

this simulation.

Wrapping bursts are special kinds of burst in which the

address is wrapped around the address boundaries. These are

used in cache line fills where the cache line is filled by the

master. The address boundary in a wrapping burst can be

calculated as:

(No. of Beats) * (size of transfer)

Where beats is the wrapping length (i.e. 4, 8 or 16) and size

is given by the no. of bytes in the transfer.

So, for a wrap 8 of word sized transfer the address

boundary would be at 8 * 4 = 32 byte boundary.

The expected waveform for such a transfer is shown in figure

6. As seen in the figure the address is wrapped after 0x3C i.e. at

the 32 byte boundary to 0x20.

Figure 6 Wrap 8 operation

The waveform for such a transfer is shown in the figure 7

which shows the same result.

Figure 4 Multi master incremental write operation

C. Burst operations

AHB has the capability of performing different kinds of

burst operations. The burst operations available are:

Single burst

Undefined length incremental burst (as shown in

figure 4)

Incremental burst of lengths 4, 8, and 16.

Wrapping burst of lengths 4, 8 and 16.

These are selected using the HBURST[2:0] signals. In any

burst transfer the subsequent addresses are calculated using the

HSIZE by the master. For a word transfer address is

Figure 7 Wrap 8 waveform

575

IJRITCC | April 2016, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 4 Issue: 4

ISSN: 2321-8169

573 - 576

______________________________________________________________________________________

VI.

SYNTHESIS

The complete design with 3 masters, 4 slaves, arbiter,

decoder, address mux, write and read data mux was

synthesized using Xilinx ISE 14.4.

Synthesis was done on xc3s500e-4fg320. The synthesis

report is shown in figure 8.

ARM processor and among the different components

connected to it.

REFERENCES

[1]

[2]

[3]

[4]

[5]

Figure 8 Synthesis result

[6]

VII. CONCLUSION

AMBA defines on chip communication standard for

communication among different IPs. AMBA AHB is a popular

industry protocol which is used in several applications.

Implementation of AMBA AHB with multi master, slaves,

arbiter and decoder was done in this paper using the Verilog

HDL. Waveforms were obtained as expected and synthesis was

also done using Xilinx ISE.

Further this design can be extended to be used in a

complete system where it can be modified to be used with an

[7]

[8]

YashdeepGodhal, Krishnendu Chatterjee, Thomas A. Henzinger

Synthesis of AMBA AHB from formal specification,

Springer-Verlag, 10 July 2011, Int J Softw Tools Technol

Transfer (2013),DOI 10.1007/s10009-011-0207-9.

ARM Ltd. AMBA specification ( Rev 2.0)

www.arm.com

Soo Yun Hwang, Dong Soo Kang, Hyeong Jun Park, and

Kyoung Son Jhang, Member, IEEE Implementation of self

motivated arbitration scheme for the multilayer AHB busmatrix

VOL. 18, NO. 5, MAY 2010 IEEE

D. Flynns AMBA: Enabling reusable on-chip designs, IEEE

Micro, Vol. 17, no. 4, pages 2027, July-August 1997.

M. Dubois, Y. Savaria, A generic AHB bus for implementing

high- speed locally synchronous islands, Bois, G. Southeast

Conference, Proceedings. IEEE, Page(s). 11 16, 2005.Y.

Yorozu, M. Hirano, K. Oka, and Y. Tagawa, Electron

spectroscopy studies on magneto-optical media and plastic

substrate interface, IEEE Transl. J. Magn. Japan, vol. 2, pp.

740741, August 1987.

www.asic-world.com

Verilog HDL: A Guide to Digital Design and Synthesis, By

Samir Palnitkar.

576

IJRITCC | April 2016, Available @ http://www.ijritcc.org

_______________________________________________________________________________________

Vous aimerez peut-être aussi

- Pitch AnythingDocument8 pagesPitch AnythingDoland drumb100% (1)

- Indian Pharmaceutical IndustryDocument25 pagesIndian Pharmaceutical IndustryVijaya enterprisesPas encore d'évaluation

- Real Options BV Lec 14Document49 pagesReal Options BV Lec 14Anuranjan TirkeyPas encore d'évaluation

- RTL Design of AHB ProtocolDocument10 pagesRTL Design of AHB ProtocolAnji medidiPas encore d'évaluation

- AMBA AnsDocument8 pagesAMBA AnsYeshoda MallikarjunaPas encore d'évaluation

- Amba AhbDocument67 pagesAmba Ahbeapenabrm100% (5)

- Investigation of the Usefulness of the PowerWorld Simulator Program: Developed by "Glover, Overbye & Sarma" in the Solution of Power System ProblemsD'EverandInvestigation of the Usefulness of the PowerWorld Simulator Program: Developed by "Glover, Overbye & Sarma" in the Solution of Power System ProblemsPas encore d'évaluation

- APB ProtocolDocument9 pagesAPB ProtocolMohit TopiwalaPas encore d'évaluation

- Digital Modulations using MatlabD'EverandDigital Modulations using MatlabÉvaluation : 4 sur 5 étoiles4/5 (6)

- CYPE 2021 + CYPE ArchitectureDocument15 pagesCYPE 2021 + CYPE ArchitectureHajar CypeMarocPas encore d'évaluation

- Ahb Faqs FAQsnewDocument10 pagesAhb Faqs FAQsnewKrunal ModiPas encore d'évaluation

- 2g ParameterDocument176 pages2g ParameterNitin PandeyPas encore d'évaluation

- Revised PARA Element2 Radio LawsDocument81 pagesRevised PARA Element2 Radio LawsAurora Pelagio Vallejos100% (4)

- Vlsi Design of Amba Based Ahb2apb BridgeDocument12 pagesVlsi Design of Amba Based Ahb2apb BridgeAnonymous e4UpOQEPPas encore d'évaluation

- AHU CatalogueDocument16 pagesAHU CatalogueWai Ee YapPas encore d'évaluation

- 2G Parameter DescriptionDocument310 pages2G Parameter DescriptionHirak Jyoti Mazumdar100% (3)

- AMBA AHB Protocol PresentationDocument45 pagesAMBA AHB Protocol Presentationachanta1291% (11)

- L11B-E-02 Ericsson LTE Field Guide Notification Alert - LTE RACH Preamble ChangeDocument5 pagesL11B-E-02 Ericsson LTE Field Guide Notification Alert - LTE RACH Preamble Changesarfraz Ahmed75% (4)

- Digital Spectral Analysis MATLAB® Software User GuideD'EverandDigital Spectral Analysis MATLAB® Software User GuidePas encore d'évaluation

- Arte PoveraDocument13 pagesArte PoveraSohini MaitiPas encore d'évaluation

- AmbaDocument13 pagesAmbaAtish BardePas encore d'évaluation

- Ahb 5Document8 pagesAhb 5ShaikAzharPas encore d'évaluation

- AHB SignalsDocument2 pagesAHB Signalsavdhesh7Pas encore d'évaluation

- AHB FeaturesDocument12 pagesAHB Featuresrahulnivak2333Pas encore d'évaluation

- Design of An Efficient FSM For An Implementation of AMBA AHB MasterDocument5 pagesDesign of An Efficient FSM For An Implementation of AMBA AHB Masterrahul shiv shankarPas encore d'évaluation

- Design and Verification of AMBA AHB-Lite Protocol Using Verilog HDLDocument8 pagesDesign and Verification of AMBA AHB-Lite Protocol Using Verilog HDLHeekwan SonPas encore d'évaluation

- Amba AhbDocument4 pagesAmba AhbArun BaskaranPas encore d'évaluation

- Design and Verification of AMBA AHBDocument6 pagesDesign and Verification of AMBA AHBrishi tejuPas encore d'évaluation

- NewAMBA PDFDocument14 pagesNewAMBA PDFPralhadrao sPas encore d'évaluation

- AMBA PDFDocument14 pagesAMBA PDFSHUKLA NISHANTPas encore d'évaluation

- Arm Ahb For McusDocument7 pagesArm Ahb For McusBharathwajan ParthasarathyPas encore d'évaluation

- On-Chip Bus Protocols: National Chiao Tung University Chun-Jen Tsai 05/3/2011Document63 pagesOn-Chip Bus Protocols: National Chiao Tung University Chun-Jen Tsai 05/3/2011madhukirPas encore d'évaluation

- Seminar ReportDocument17 pagesSeminar ReportG-1076-Sudhansu AwasthiPas encore d'évaluation

- Implementation of A Special Arbitration Scheme For AHB of AMBADocument4 pagesImplementation of A Special Arbitration Scheme For AHB of AMBAJmkPas encore d'évaluation

- USARTDocument17 pagesUSARTtharunvenkataPas encore d'évaluation

- Design of An AMBA AHB Reconfigurable Arbiter For On-Chip Bus ArchitectureDocument8 pagesDesign of An AMBA AHB Reconfigurable Arbiter For On-Chip Bus ArchitectureInternational Journal of Application or Innovation in Engineering & ManagementPas encore d'évaluation

- MBSD NOTES (PDF 2)Document25 pagesMBSD NOTES (PDF 2)Syed Ali Raza NaqviPas encore d'évaluation

- AMBA ProtocolDocument11 pagesAMBA Protocolsachin palPas encore d'évaluation

- Arm Amba AhbDocument18 pagesArm Amba AhbgeethaPas encore d'évaluation

- Amba 454Document27 pagesAmba 454HemanthPas encore d'évaluation

- Presented by B. Koteswar Rao 08G71D7005 Under The Guidence of Mr.B. Naresh Reddy M.TechDocument14 pagesPresented by B. Koteswar Rao 08G71D7005 Under The Guidence of Mr.B. Naresh Reddy M.TechSrinivas KumarPas encore d'évaluation

- Implementation Methodology of High Performance Multi Byte Data Access Control of AMBA BusDocument5 pagesImplementation Methodology of High Performance Multi Byte Data Access Control of AMBA BusKumar Goud.KPas encore d'évaluation

- Design Amba Based Ahb To Apb Bridge Using Verilog HDL: Prarthi Bhatt, Prof..Devang ShahDocument5 pagesDesign Amba Based Ahb To Apb Bridge Using Verilog HDL: Prarthi Bhatt, Prof..Devang ShahPotnuru KarishmaPas encore d'évaluation

- Development and Verification of Ahb2apb Bridge Protocol Using Uvm TechniqueDocument7 pagesDevelopment and Verification of Ahb2apb Bridge Protocol Using Uvm TechniqueUGCJOURNAL PUBLICATION100% (1)

- Implementation of AMBA Based AHB2APB Bridge: Bhagvati Panchal, Yogesh Parmar, Haresh SutharDocument1 pageImplementation of AMBA Based AHB2APB Bridge: Bhagvati Panchal, Yogesh Parmar, Haresh SutharDevendra BairagiPas encore d'évaluation

- WiMAX Channel Simulation Uni ReportDocument5 pagesWiMAX Channel Simulation Uni Reportandygray119Pas encore d'évaluation

- Ahb To Apb NotesDocument13 pagesAhb To Apb NotesAbhimanyuPas encore d'évaluation

- AMBA AHB Protocol OverviewDocument31 pagesAMBA AHB Protocol Overviewmuhammedayman350Pas encore d'évaluation

- Apb Interview QuestionsDocument1 pageApb Interview QuestionsbalajiPas encore d'évaluation

- GSM Cellplanning and OptimizationDocument24 pagesGSM Cellplanning and OptimizationRiyad Ismail SaeedPas encore d'évaluation

- Technical Seminar ReportDocument22 pagesTechnical Seminar Reportsai sandeep kumarPas encore d'évaluation

- Technical Seminar ReportDocument22 pagesTechnical Seminar Reportsai sandeep kumarPas encore d'évaluation

- Technical Seminar ReportDocument22 pagesTechnical Seminar Reportsai sandeep kumarPas encore d'évaluation

- Tems Parameters (Speech) : Cellw RKS, AhmedabadDocument29 pagesTems Parameters (Speech) : Cellw RKS, Ahmedabadsamadhan1187Pas encore d'évaluation

- Ahb QuestionsDocument20 pagesAhb QuestionsMohammed Nawaz ShaikPas encore d'évaluation

- AmbaDocument4 pagesAmbaBethuna Sayed100% (1)

- Distributed Bandwidth Allocation For Resilient Packet Ring NetworksDocument11 pagesDistributed Bandwidth Allocation For Resilient Packet Ring NetworksSupriya Nagane-GaikwadPas encore d'évaluation

- High Speed DL FachDocument23 pagesHigh Speed DL FachSumon Kumar BiswasPas encore d'évaluation

- Session 10 - AMBA-busDocument35 pagesSession 10 - AMBA-busSai Mohnish MuralidharanPas encore d'évaluation

- AMBA Interface Design RNSITDocument5 pagesAMBA Interface Design RNSITShailendra RajputPas encore d'évaluation

- Multicore Enabled Verification of AMBA AHB Protocol Using UVMDocument7 pagesMulticore Enabled Verification of AMBA AHB Protocol Using UVMSamPas encore d'évaluation

- On-Chip Bus: Speaker: Tian-Sheuan Chang July, 2004Document40 pagesOn-Chip Bus: Speaker: Tian-Sheuan Chang July, 2004Tarun GhoshPas encore d'évaluation

- Analysis of The 802.11s Mesh TechnologyDocument40 pagesAnalysis of The 802.11s Mesh Technologyabhisheksingh2Pas encore d'évaluation

- Basics Radio ParameterDocument4 pagesBasics Radio ParametersrimantaPas encore d'évaluation

- ROUTING INFORMATION PROTOCOL: RIP DYNAMIC ROUTING LAB CONFIGURATIOND'EverandROUTING INFORMATION PROTOCOL: RIP DYNAMIC ROUTING LAB CONFIGURATIONPas encore d'évaluation

- Channel Estimation Techniques Over MIMO-OFDM SystemDocument4 pagesChannel Estimation Techniques Over MIMO-OFDM SystemEditor IJRITCCPas encore d'évaluation

- A Review of 2D &3D Image Steganography TechniquesDocument5 pagesA Review of 2D &3D Image Steganography TechniquesEditor IJRITCCPas encore d'évaluation

- Importance of Similarity Measures in Effective Web Information RetrievalDocument5 pagesImportance of Similarity Measures in Effective Web Information RetrievalEditor IJRITCCPas encore d'évaluation

- Diagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmDocument5 pagesDiagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmEditor IJRITCCPas encore d'évaluation

- A Study of Focused Web Crawling TechniquesDocument4 pagesA Study of Focused Web Crawling TechniquesEditor IJRITCCPas encore d'évaluation

- Predictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth KotianDocument3 pagesPredictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth Kotianrahul sharmaPas encore d'évaluation

- Prediction of Crop Yield Using LS-SVMDocument3 pagesPrediction of Crop Yield Using LS-SVMEditor IJRITCCPas encore d'évaluation

- Safeguarding Data Privacy by Placing Multi-Level Access RestrictionsDocument3 pagesSafeguarding Data Privacy by Placing Multi-Level Access Restrictionsrahul sharmaPas encore d'évaluation

- 45 1530697786 - 04-07-2018 PDFDocument5 pages45 1530697786 - 04-07-2018 PDFrahul sharmaPas encore d'évaluation

- Itimer: Count On Your TimeDocument4 pagesItimer: Count On Your Timerahul sharmaPas encore d'évaluation

- Hybrid Algorithm For Enhanced Watermark Security With Robust DetectionDocument5 pagesHybrid Algorithm For Enhanced Watermark Security With Robust Detectionrahul sharmaPas encore d'évaluation

- 44 1530697679 - 04-07-2018 PDFDocument3 pages44 1530697679 - 04-07-2018 PDFrahul sharmaPas encore d'évaluation

- 41 1530347319 - 30-06-2018 PDFDocument9 pages41 1530347319 - 30-06-2018 PDFrahul sharmaPas encore d'évaluation

- 49 1530872658 - 06-07-2018 PDFDocument6 pages49 1530872658 - 06-07-2018 PDFrahul sharmaPas encore d'évaluation

- Paper On Design and Analysis of Wheel Set Assembly & Disassembly Hydraulic Press MachineDocument4 pagesPaper On Design and Analysis of Wheel Set Assembly & Disassembly Hydraulic Press MachineEditor IJRITCCPas encore d'évaluation

- Slem Descriptive EssayDocument2 pagesSlem Descriptive EssayMary Jane DingalPas encore d'évaluation

- A Project Diary-Wps OfficeDocument4 pagesA Project Diary-Wps OfficeSameer ShaikhPas encore d'évaluation

- End Points SubrogadosDocument3 pagesEnd Points SubrogadosAgustina AndradePas encore d'évaluation

- Project Synopsis On LAN ConnectionDocument15 pagesProject Synopsis On LAN ConnectionডৰাজবংশীPas encore d'évaluation

- 103-Article Text-514-1-10-20190329Document11 pages103-Article Text-514-1-10-20190329Elok KurniaPas encore d'évaluation

- Assessment PN1096617Document14 pagesAssessment PN1096617Amr TarekPas encore d'évaluation

- A History of The Ecological Sciences, Part 1 - Early Greek OriginsDocument6 pagesA History of The Ecological Sciences, Part 1 - Early Greek OriginskatzbandPas encore d'évaluation

- Chapter 3 PayrollDocument5 pagesChapter 3 PayrollPheng Tiosen100% (2)

- Unit 1: Power and Responsibility: 1. Important Leadership QualitiesDocument6 pagesUnit 1: Power and Responsibility: 1. Important Leadership QualitiesTrần Thanh MinhPas encore d'évaluation

- Comsol - Guidelines For Modeling Rotating Machines in 3DDocument30 pagesComsol - Guidelines For Modeling Rotating Machines in 3DtiberiupazaraPas encore d'évaluation

- d10 Sandra Darby FinalDocument3 pagesd10 Sandra Darby FinalFirstCitizen1773Pas encore d'évaluation

- L Rexx PDFDocument9 pagesL Rexx PDFborisg3Pas encore d'évaluation

- Sample TRM All Series 2020v1 - ShortseDocument40 pagesSample TRM All Series 2020v1 - ShortseSuhail AhmadPas encore d'évaluation

- 5 Teacher Induction Program - Module 5Document27 pages5 Teacher Induction Program - Module 5LAZABELLE BAGALLON0% (1)

- Integra Facade BrochureDocument2 pagesIntegra Facade BrochureHarshit PatadiyaPas encore d'évaluation

- General Mathematics SS3 2ND Term SchemeDocument2 pagesGeneral Mathematics SS3 2ND Term Schemesam kaluPas encore d'évaluation

- Car Section 2 Series (H) Part-IiDocument6 pagesCar Section 2 Series (H) Part-Iipandurang nalawadePas encore d'évaluation

- 3 - Risk Opportunity RegisterDocument4 pages3 - Risk Opportunity RegisterArmando CorboPas encore d'évaluation

- (2016) A Review of The Evaluation, Control and Application Technologies For Drillstring S&V in O&G WellDocument35 pages(2016) A Review of The Evaluation, Control and Application Technologies For Drillstring S&V in O&G WellRoger GuevaraPas encore d'évaluation

- EdM 101 - Joan Marie PeliasDocument9 pagesEdM 101 - Joan Marie Peliasjoan marie Pelias100% (1)

- Stellite 6 FinalDocument2 pagesStellite 6 FinalGumersindo MelambesPas encore d'évaluation

- ESA Mars Research Abstracts Part 2Document85 pagesESA Mars Research Abstracts Part 2daver2tarletonPas encore d'évaluation

- IOM - Rampa Hidráulica - Blue GiantDocument32 pagesIOM - Rampa Hidráulica - Blue GiantPATRICIA HERNANDEZPas encore d'évaluation