Académique Documents

Professionnel Documents

Culture Documents

Blackfin Processor

Transféré par

KameshSonti0 évaluation0% ont trouvé ce document utile (0 vote)

115 vues2 pagesDSP Blackfin Processor

Copyright

© © All Rights Reserved

Formats disponibles

PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDSP Blackfin Processor

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

115 vues2 pagesBlackfin Processor

Transféré par

KameshSontiDSP Blackfin Processor

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 2

Blackfin Processor Architecture Overview

Blackfin Processors are a new breed of embedded media processor designed

specifically to meet the computational demands and power constraints of today's

embedded audio, video and communications applications. Blackfin Processors

combine a 32-bit RISC-like instruction set and dual 16-bit multiply accumulate

(MAC) signal processing.

This combination of processing attributes enables Blackfin Processors to perform

equally well in both signal processing and control processing applications-in many

cases deleting the requirement for separate heterogeneous processors. This capability

greatly simplifies both the hardware and software design implementation tasks.

The Blackfin Processor offer a combination of high performance and low power. This

behaviour is essential in meeting the needs of today's and future signal processing

applications including broadband wireless, audio/video capable Internet appliances,

and mobile communications.

Blackfin Processor Core Basics

The Blackfin Processor core is a load-store architecture consisting of a Data

Arithmetic Unit, an Address Arithmetic Unit, and a sequencer unit:

Data Arithmetic Unit

The Data Arithmetic Unit contains roughly twice the system resources as previous

Analog Devices 16-bit architectures. It contains:

Two 16-bit MACs,

Two 40-bit ALUs,

Four 8-bit Video ALUs, and a

Single Barrel Shifter.

All computational resources can process 8, 16, or 32-bit operands from the data

register file. Each register can be accessed as a 32-bit register or a 16-bit register high

or low half.

Address Arithmetic Unit

Two data address generators (DAGs) provide addresses for simultaneous dual

operand fetches from memory. The DAGs share a register file that contains four sets

of 32-bit index (I), length(L), base(B), and modify(M) registers. There are also eight

additional 32-bit address registers that can be used as pointers for general indexing of

variables and stack locations. The four sets of I, L, B, and M registers are useful for

implementing circular buffering. Used together, each set of Index, Length, and Base

registers can implement a unique circular buffer in internal or external memory. The

Blackfin architecture also supports a variety of addressing modes including indirect,

auto-increment and decrement, indexed, and bit reversed.

Program Sequencer Unit

The program sequencer controls the flow of instruction execution and supports

conditional jumps and subroutine calls, as well as nested zero-overhead looping. A

multi-stage fully interlocked pipeline guarantees code is executed as expected and

that all data hazards are hidden from the programmer.

The Blackfin architecture supports 16 & 32-bit instruction lengths in addition

to limited multi-issue 64-bit instruction packets. This ensures maximum code

density by encoding the most frequently used control instructions as compact

16-bit words and the more challenging math operations as 32-bit double

words.

The family of the blackfin processors is much immense but the product we are going

to use in our project is the Analog Blackfin BF535.

Vous aimerez peut-être aussi

- Two Ray Path Loss ModelDocument35 pagesTwo Ray Path Loss ModelAyushi AggarwalPas encore d'évaluation

- Part III 8051 General PgmsDocument7 pagesPart III 8051 General PgmsHEMAPas encore d'évaluation

- ASAP7 TutorialDocument52 pagesASAP7 TutorialAtmadeep DeyPas encore d'évaluation

- Difference Between RISC and CISC ArchitectureDocument2 pagesDifference Between RISC and CISC ArchitectureakssahaPas encore d'évaluation

- Baseband Pulse Transmission: Presented by Asst. Professor ECE DepartmentDocument47 pagesBaseband Pulse Transmission: Presented by Asst. Professor ECE DepartmentImran BashaPas encore d'évaluation

- ASK FSK PSK Simulation Using MultisimDocument6 pagesASK FSK PSK Simulation Using MultisimSabari Muthu RamanPas encore d'évaluation

- DCOM Lab ManualDocument38 pagesDCOM Lab ManualGaurav Kalra0% (1)

- 8255 Ppi ExamplesDocument10 pages8255 Ppi Examplesvenky258100% (1)

- To Design An Adaptive Channel Equalizer Using MATLABDocument43 pagesTo Design An Adaptive Channel Equalizer Using MATLABAngel Pushpa100% (1)

- Wireless and Mobile Communications: Abhijit Bhowmick Sense VIT, Vellore, TN, IndiaDocument28 pagesWireless and Mobile Communications: Abhijit Bhowmick Sense VIT, Vellore, TN, IndiaAANCHALPas encore d'évaluation

- Chapter6 7thDocument14 pagesChapter6 7thMuhammad RidwanPas encore d'évaluation

- GSM Operations, Administration, and MaintenanceDocument17 pagesGSM Operations, Administration, and MaintenanceLenin. S.BPas encore d'évaluation

- PSD of Pulse Coding Techniques With MatlabDocument7 pagesPSD of Pulse Coding Techniques With MatlabNithin MukeshPas encore d'évaluation

- CCN Lab Manual VII Semester Telecommunication EngineeringDocument28 pagesCCN Lab Manual VII Semester Telecommunication Engineeringswapna_charanPas encore d'évaluation

- 8085 DataDocument3 pages8085 Datashylaja9Pas encore d'évaluation

- Experiment No-8: Write A MATLAB Program To Plot The Following FunctionDocument2 pagesExperiment No-8: Write A MATLAB Program To Plot The Following FunctionUnknown424Pas encore d'évaluation

- LINEAR DATA STRUCTURES - LISTDocument37 pagesLINEAR DATA STRUCTURES - LISTnandhuldkPas encore d'évaluation

- Time Domain AnalysisDocument94 pagesTime Domain AnalysisAbhayPas encore d'évaluation

- Chapter 3 - Serial Interfacing With Microprocessor Based SystemDocument28 pagesChapter 3 - Serial Interfacing With Microprocessor Based SystemAarav PoudelPas encore d'évaluation

- UG - EC303 DSP Part-6 On-Chip Peripherals-Print PDFDocument20 pagesUG - EC303 DSP Part-6 On-Chip Peripherals-Print PDFapuurvaPas encore d'évaluation

- Ec 2252 Communication Theory Lecture NotesDocument120 pagesEc 2252 Communication Theory Lecture NotesChoco BoxPas encore d'évaluation

- Ecad Lab ManualDocument55 pagesEcad Lab Manualjeravi84100% (3)

- 18EC33 2019-20 Mod1 Bonding Forces in Solids PDFDocument18 pages18EC33 2019-20 Mod1 Bonding Forces in Solids PDFPradnya VeeragoudarPas encore d'évaluation

- Shubham Rathod FOC LabDocument42 pagesShubham Rathod FOC LabShubham RathodPas encore d'évaluation

- Radar Systems - Delay Line CancellersDocument7 pagesRadar Systems - Delay Line Cancellersgajjala rakeshPas encore d'évaluation

- University of Pune S.E. I.T. Subject code: 214447 Processor Architecture and Interfacing Part 13: The 8255 PPIDocument24 pagesUniversity of Pune S.E. I.T. Subject code: 214447 Processor Architecture and Interfacing Part 13: The 8255 PPIPalash ParmarPas encore d'évaluation

- Microprocessor 80386Document40 pagesMicroprocessor 80386eshwar_worldPas encore d'évaluation

- N.I COLLEGE OF ENGINEERING KUMARACOIL TWO MARKS QUESTIONS AND ANSWERS ON ELECTRICAL MACHINESDocument15 pagesN.I COLLEGE OF ENGINEERING KUMARACOIL TWO MARKS QUESTIONS AND ANSWERS ON ELECTRICAL MACHINESAtchutharam EcePas encore d'évaluation

- Chapter 3 - String ProcessingDocument28 pagesChapter 3 - String ProcessingTanveer Ahmed HakroPas encore d'évaluation

- UAP Mobile Communication Course Repeat ExamDocument4 pagesUAP Mobile Communication Course Repeat ExamALI-EMAM- AL-BADIPas encore d'évaluation

- Digital Logic Design CourseDocument1 pageDigital Logic Design CourseVinay PasiPas encore d'évaluation

- Data Processing InstructionDocument35 pagesData Processing InstructionDado Fabrička GreškaPas encore d'évaluation

- Digital Circuits For GATE ExamDocument15 pagesDigital Circuits For GATE ExamSAMIT KARMAKAR100% (1)

- ES PaperDocument22 pagesES PaperRaghu Nath SinghPas encore d'évaluation

- 8051 Microcontroller Lab Manual Lab 07Document5 pages8051 Microcontroller Lab Manual Lab 07sidiqbal100% (1)

- 8051 Program To Find Number of Ones and Zeroes in A Given NumberDocument5 pages8051 Program To Find Number of Ones and Zeroes in A Given NumberHrithik SahuPas encore d'évaluation

- 17BEC0901 TASK 2 MicrocontrollersDocument13 pages17BEC0901 TASK 2 Microcontrollersrohan joshuaPas encore d'évaluation

- ARM Organization and Implementation: Aleksandar MilenkovicDocument37 pagesARM Organization and Implementation: Aleksandar Milenkovicarthicse100% (1)

- MP Viva Questions With AnswersDocument13 pagesMP Viva Questions With AnswersDeepti ChandrasekharanPas encore d'évaluation

- CS3362 C Programming and Data Structures LaboratoryDocument1 pageCS3362 C Programming and Data Structures LaboratoryanantPas encore d'évaluation

- DECO Lab FileDocument101 pagesDECO Lab Fileshivam100% (1)

- Lecture2 ThirdmicroprocessorcDocument22 pagesLecture2 Thirdmicroprocessorcxkurt358792100% (2)

- Experiment No. 01 Experiment Name-ASK ModulationDocument47 pagesExperiment No. 01 Experiment Name-ASK ModulationmuskanPas encore d'évaluation

- Microprocessor and Microcontroller ProgrammingDocument39 pagesMicroprocessor and Microcontroller ProgrammingGunasekaranPas encore d'évaluation

- Experiment No. 5: Binary Phase Shift KeyingDocument7 pagesExperiment No. 5: Binary Phase Shift KeyingGovind YadavPas encore d'évaluation

- Advanced Communication Lab Manual: Visvesvaraya Technological UniversityDocument46 pagesAdvanced Communication Lab Manual: Visvesvaraya Technological UniversityPunith Gowda M B100% (2)

- I2C Interfacing To XC3S400 FPGADocument14 pagesI2C Interfacing To XC3S400 FPGAMahesh BhatkalPas encore d'évaluation

- Lecture1 06 - 07 - 10 David Pozar Microwave EngDocument29 pagesLecture1 06 - 07 - 10 David Pozar Microwave EngBagus Van Houten IXPas encore d'évaluation

- Pipelining VerilogDocument26 pagesPipelining VerilogThineshPas encore d'évaluation

- Emtl CFDocument85 pagesEmtl CFSivaPas encore d'évaluation

- Internal Architecture of ADSP 21xx FamilyDocument14 pagesInternal Architecture of ADSP 21xx FamilyTanisha Shashikumar0% (1)

- 18EC44 I IA - New PDFDocument1 page18EC44 I IA - New PDFGovind M RoddannavarPas encore d'évaluation

- Ec - 501 - Microprocessor and Its ApplicationDocument41 pagesEc - 501 - Microprocessor and Its ApplicationDr Nikita ShivharePas encore d'évaluation

- Study of Architecture of DSP TMS320C6748Document9 pagesStudy of Architecture of DSP TMS320C6748Varssha BPas encore d'évaluation

- UNIT2 NotesDocument25 pagesUNIT2 Notes4PS19EC071 Lakshmi.MPas encore d'évaluation

- Programmable DSP Lecture1Document19 pagesProgrammable DSP Lecture1Paresh Sawant50% (2)

- Process Multiple Signals with ADSP-21csp01 DSPDocument6 pagesProcess Multiple Signals with ADSP-21csp01 DSPIgnite ThrissurPas encore d'évaluation

- Unit 3 Programmable Digital Signal ProcessorsDocument25 pagesUnit 3 Programmable Digital Signal ProcessorsPreetham SaigalPas encore d'évaluation

- ADSP-21060 SHARC DSP Memory, Registers & Instruction PipeliningDocument20 pagesADSP-21060 SHARC DSP Memory, Registers & Instruction PipeliningSirisha KurakulaPas encore d'évaluation

- Computer Orgn 230428 235533Document10 pagesComputer Orgn 230428 235533Arathi SuryaramananPas encore d'évaluation

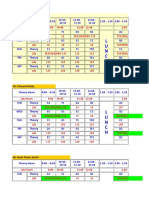

- Workload WIN 2018-19 SEMDocument10 pagesWorkload WIN 2018-19 SEMKameshSontiPas encore d'évaluation

- FLEX10 KdsDocument128 pagesFLEX10 KdsIbrahimFaroukSolarPas encore d'évaluation

- QuizDocument2 pagesQuizKameshSontiPas encore d'évaluation

- L U N C H: Mr. Kamesh SontDocument4 pagesL U N C H: Mr. Kamesh SontKameshSontiPas encore d'évaluation

- Edc Lab (180) Ii-IDocument92 pagesEdc Lab (180) Ii-ImikuloPas encore d'évaluation

- Course Outcomes Mapping To Program OutcomesDocument4 pagesCourse Outcomes Mapping To Program OutcomesKameshSontiPas encore d'évaluation

- Cs Co-Po MappingDocument7 pagesCs Co-Po MappingKameshSontiPas encore d'évaluation

- Author GuidelinesDocument3 pagesAuthor GuidelinesKameshSontiPas encore d'évaluation

- Course Outcomes Mapping To Program OutcomesDocument4 pagesCourse Outcomes Mapping To Program OutcomesKameshSontiPas encore d'évaluation

- ISE Design Suite 10.1 Release Notes and ISE Design Suite 10.1 Release Notes and Installation GuideDocument76 pagesISE Design Suite 10.1 Release Notes and ISE Design Suite 10.1 Release Notes and Installation GuideMigue SolinasPas encore d'évaluation

- Control SystemsDocument15 pagesControl SystemsKameshSontiPas encore d'évaluation

- DOS ProgramsDocument5 pagesDOS ProgramsKameshSontiPas encore d'évaluation

- r16 M.tech Vlsi SyllabusDocument427 pagesr16 M.tech Vlsi SyllabusratnamsPas encore d'évaluation

- Abstract AlgebraDocument438 pagesAbstract AlgebraThomas HPas encore d'évaluation

- MahiDocument19 pagesMahiKameshSontiPas encore d'évaluation

- Mr. S.Kamesh Faculty TimetableDocument2 pagesMr. S.Kamesh Faculty TimetableKameshSontiPas encore d'évaluation

- Image Transforms Explained in DetailDocument35 pagesImage Transforms Explained in DetailJacob HowardPas encore d'évaluation

- A Two Days Workshop On "PCB DESIGN": Academic Year 2014-2015Document5 pagesA Two Days Workshop On "PCB DESIGN": Academic Year 2014-2015KameshSontiPas encore d'évaluation

- PHD FT Stipend July2014Document3 pagesPHD FT Stipend July2014KameshSontiPas encore d'évaluation

- SSP Dip Ce SP IpDocument64 pagesSSP Dip Ce SP IpanjugaduPas encore d'évaluation

- AICTE - Laboratory DetailsDocument32 pagesAICTE - Laboratory DetailsKameshSontiPas encore d'évaluation

- BTech ECE VLSI Design Course InfoDocument3 pagesBTech ECE VLSI Design Course InfoKameshSontiPas encore d'évaluation

- Toshiba L515-SP4031Document3 pagesToshiba L515-SP4031Alejandro BorraPas encore d'évaluation

- HP Notebook LatestDocument1 pageHP Notebook LatestIftekhar Ahmed ShafiPas encore d'évaluation

- Multi Controlled WheelchairDocument7 pagesMulti Controlled WheelchairmafiaishotPas encore d'évaluation

- IC695 PBM300 Profibus Master ModuleDocument5 pagesIC695 PBM300 Profibus Master ModuleftomaziniiPas encore d'évaluation

- CS501 - HandoutsDocument359 pagesCS501 - HandoutsAlone GirlPas encore d'évaluation

- MP Div A 10045 Atharva BorikarDocument22 pagesMP Div A 10045 Atharva BorikarAtharva BorikarPas encore d'évaluation

- ARM7 LPC2129 Processor RegistersDocument34 pagesARM7 LPC2129 Processor RegistersAnchal ChaturvedyPas encore d'évaluation

- Computer Operations and Fundamentals: Learning ObjectivesDocument17 pagesComputer Operations and Fundamentals: Learning ObjectivesReem RezkPas encore d'évaluation

- DR - Chao Tan, Carnegie Mellon University: Computer Organization Computer ArchitectureDocument221 pagesDR - Chao Tan, Carnegie Mellon University: Computer Organization Computer ArchitectureGreat GuyPas encore d'évaluation

- LTBT Vlca 1688Document2 pagesLTBT Vlca 1688Chong Cong0% (1)

- Quantum Using Ecostruxure™ Control Expert: Hardware Reference ManualDocument496 pagesQuantum Using Ecostruxure™ Control Expert: Hardware Reference ManualMuhammad RidhoPas encore d'évaluation

- Mindray Datascope Passport V - Service ManualDocument132 pagesMindray Datascope Passport V - Service ManualSergio PérezPas encore d'évaluation

- L1 - Instructions - Intro - Operations - Operands of The ComputerDocument19 pagesL1 - Instructions - Intro - Operations - Operands of The ComputerJaisaiarun P SrinivasanPas encore d'évaluation

- ITSU 1001 Introduction To Computer Systems and Networking: Tutorial 4 For Lesson 4Document5 pagesITSU 1001 Introduction To Computer Systems and Networking: Tutorial 4 For Lesson 4Rakesh ydavPas encore d'évaluation

- Us 7607357Document19 pagesUs 7607357imru2Pas encore d'évaluation

- ABInitio FAQDocument21 pagesABInitio FAQGanga VenkatPas encore d'évaluation

- Lower Case To Upper Case MICDocument12 pagesLower Case To Upper Case MICAvadhut DeshmukhPas encore d'évaluation

- Intel® Workstation Board S5520SC Quick Start User's Guide 1 2Document1 pageIntel® Workstation Board S5520SC Quick Start User's Guide 1 2BleyaPas encore d'évaluation

- Emerson Fb2200 Flow Computer Instruction Manual en 586724Document124 pagesEmerson Fb2200 Flow Computer Instruction Manual en 586724Raymundo Maldonado AlvarezPas encore d'évaluation

- A Comprehensive New Player Guide To Tanking in Eve-OnlineDocument12 pagesA Comprehensive New Player Guide To Tanking in Eve-OnlineScudd100% (1)

- Computer Architecture I: Digital Design: CPU Registers Register Transfer and MicrooperationsDocument46 pagesComputer Architecture I: Digital Design: CPU Registers Register Transfer and MicrooperationsSaumenRoyPas encore d'évaluation

- Q. P. Code: 08235Document8 pagesQ. P. Code: 08235Mr AnonymousPas encore d'évaluation

- ch01 - Understanding Operating System Lecture Slides From USMDocument50 pagesch01 - Understanding Operating System Lecture Slides From USMJoshuaTanCYgPas encore d'évaluation

- Clock Cycles Lecture Performance OptimizationDocument8 pagesClock Cycles Lecture Performance OptimizationMohammad Abdul RafehPas encore d'évaluation

- Classes ParallelismDocument4 pagesClasses ParallelismMuthukumar ManickamPas encore d'évaluation

- LSF User GuideDocument88 pagesLSF User GuideNilson Santamaria GPas encore d'évaluation

- Systemsoftwarenotes 100929171256 Phpapp02Document201 pagesSystemsoftwarenotes 100929171256 Phpapp02Shruthi PatilPas encore d'évaluation

- Lec 8Document62 pagesLec 8JobQuirozPas encore d'évaluation

- General Purpose Registers in 8086 MicroprocessorDocument3 pagesGeneral Purpose Registers in 8086 MicroprocessorRona Yoro ObonPas encore d'évaluation