Académique Documents

Professionnel Documents

Culture Documents

Interfaces EyS

Transféré par

JOSEJOSECopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Interfaces EyS

Transféré par

JOSEJOSEDroits d'auteur :

Formats disponibles

1

Estructura y tecnologa de Computadores

Mdulo E. El subsistema de E/S

Tema 10. Interfaces de E/S programables

Jos Manuel Mendas Cuadros

Dpto.

Dpto. Arquitectura de Computadores y Automtica

Universidad Complutense de Madrid

contenidos

1. Estructura y funcin del interfaz de E/S

Repaso de conceptos. Estructura general de un interfaz de E/S. Mtodos de transmisin de

informacin entre interfaz y perifrico: E/S paralela y E/S serie. Tipos de interfaces de E/S:

genricos y especficos.

2. Interfaces de E/S paralela: MC6821 PIA

Organizacin de la PIA. Programacin de la PIA. Ejemplo: conexin del MC68000 a una

impresora paralelo a travs de la PIA

3. Fundamentos de E/S serie

Transmisin serie asncrona. Transmisin serie sncrona. Estructura de un interfaz serie

asncrono. Estructura de un interfaz serie sncrono. Ejemplos de interfaces de E/S serie

4. Interfaces de E/S serie: MC6850 ACIA

Organizacin de la ACIA. Programacin de la ACIA. Ejemplo: conexin del MC68000 a una

impresora serie a travs de la ACIA

estructura y tecnologa de computadores

3

1. estructura y funcin del interfaz de E/S

Repaso de conceptos

Los dispositivos perifricos se conectan al computador a travs de un INTERFAZ de E/S

Interfaz = Controlador = Adaptador = Tarjeta de E/S

Funciones del interfaz de E/S

Interpretar las rdenes que recibe de la CPU y transmitirlas al perifrico

Controlar la transferencia de datos entre la CPU y el perifrico

Conversin de formatos y/o niveles elctricos

Adaptar la diferencia de velocidades entre CPU y perifrico (mediante buffers de almacenamiento)

Informar a la CPU del estado del perifrico

Ejemplo conversin de formatos Esquema de conexin CPU-interfaz-perifrico

5

8

8

0

8

5

0

8

Tipo de conversin CPU

Datos en el perifrico

E: conversin A/D

ANALGICOS S: conversin A/D

E: conversin S/P

SERIE S: conversin P/S CPU INTERFAZ PERIFRICO

DIGITALES BUS Conexin

E: -- Sistema con

PARALELO perifricos

S: -- o de E/S

estructura y tecnologa de computadores

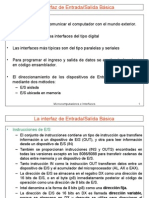

1. estructura y funcin del interfaz de E/S

Estructura general de un interfaz de E/S

Interfaz

Bus del sistema ENT Control

o de E/S P

IRQ* REGISTRO e

ESTA DO

REGISTRO

DATOS

ENT. Datos r

BUS ENTRA DA i

DATOS

f

CPU REGISTRO SAL. Datos

DATOS

BUS SALIDA r

DIR

DECODIF. CS* i

DIR

RS

LOGICA c

CONT ROL REGISTRO SAL Control

CONTROL o

R/W*

Un interfaz de E/S se est constituido de 3 elementos bsicos

Lneas de comunicacin con la CPU

Permiten a la CPU comunicarse con el interfaz

Lneas de comunicacin con el perifrico

Permiten al interfaz comunicarse con el perifrico

Registros del interfaz

Permiten a la CPU programar el interfaz, consultar el estado y enviar o recibir datos hacia/desde el perifrico

estructura y tecnologa de computadores

5

1. estructura y funcin del interfaz de E/S

Estructura general de un interfaz de E/S (cont.)

Registros del interfaz

Registro de datos de salida

Cuando la CPU quiere enviar datos al perifrico los escribe sobre el registro(s) de datos de salida

Registro de datos de entrada

Cuando la CPU quiere recibir datos del perifrico los lee desde el registro(s) de datos de entrada

Registro de estado

Cuando la CPU quiere conocer el estado del perifrico, lo hace leyendo el registro de estado:

Registro de control

Cuando la CPU quiere transmitir una orden al perifrico lo hace escribiendo en el registro de control

Lneas de comunicacin con la CPU

Lneas de datos

Para transferencia de datos entre la CPU y el interfaz

Programacin del registro de control y lectura del registro de estado

Lnea R/W*

Para especificar el tipo de operacin (lectura o escritura)

Lnea CS* (Chip Select) y RS (Register Select)

Para seleccionar el interfaz y acceder a un registro particular del mismo

Normalmente se conectan al bus de direcciones (mediante un descodificador en el caso de CS*)

Lnea IRQ*

Para peticin de interrupcin cuando el perifrico est listo para transmitir/recibir

Lneas de comunicacin con el interfaz

Lneas de datos de entrada y salida

Para transferencia de datos entre el interfaz y el perifrico

Lneas de control de entrada y salida

Para transferencia de rdenes al perifrico (salida control) y consultar su estado (entrada control)

estructura y tecnologa de computadores

1. estructura y funcin del interfaz de E/S

Mtodos de transmisin de informacin entre interfaz y perifrico

E/S paralela

Utiliza varias lneas de comunicacin a travs de las cual se se enva varios bits de informacin de

forma simultnea

Es adecuada para conexin de dispositivos a distancias cortas, que requieran altas velocidades de

transmisin

Conexin de elementos dentro de un computador mediante buses

Conexin de dispositivos externos a cortas distancias a travs de un interfaz paralelo

Problema de la E/S paralela

Para conectar dispositivos a distancias medias o largas resulta muy costosa

Redes de computadores

Los dispositivos de baja velocidad no aprovechan el potencial de la transmisin paralela

Teclados, ratones, modems, etc.

E/S serie

Utiliza una nica lnea de comunicacin a travs de las cual se se envan varios bits de informacin

de forma secuencial

Es menos costosa que la E/S paralela

Adecuada para conexin de dispositivos a largas distancias

Es til para conexin de dispositivos de velocidad media o baja

Modos de transmisin serie

Transmisin asncrona

Transmisin sncrona

estructura y tecnologa de computadores

7

1. estructura y funcin del interfaz de E/S

Tipos de interfaces de E/S

De propsito general: Permiten conectar distintos tipos de dispositivos al computador

Interfaces de E/S paralela

Para conectar dispositivos que realizan E/S paralela (reciben o transmiten varios bits de forma simultnea)

Ejemplos: MC6821 PIA, R6522 VIA, MC68320 PI/T, i8255 PPI

Interfaces de E/S serie

Para conectar dispositivos que realizan E/S serie

Ejemplos: MC6850 ACIA, R6552 DACIA, MC6854 ADLC, UART i8250, USART i8251

De propsito especfico: Diseados para conectar un tipo particular de perifrico

Controladores de teclado/display

Ejemplos: i8279

Controladores de disco y disquete

Ejemplos: MC6824, i8271, i82062

Controladores de red de rea local

Ejemplos: i82501 (controlador Ethernet)

Conversores A/D-D/A

Ejemplos: AD7824

etc.

estructura y tecnologa de computadores

2. interfaces de E/S paralela: MC6821 PIA

Interfaz MC6821 PIA (Peripheral Interface Adaptor)

Interfaz paralelo diseado para sistemas basados en el MC6800 (bus sncrono)

Compatible con el MC68000

Organizacin de la PIA Registros de datos (ORA y ORB)

Dispone de dos puertos paralelos de 8 bits Se utilizan como registro de entrada o de salida de datos,

cada uno (Puerto A y Puerto B) segn como estn programadas las lneas de

Las lneas de comunicacin con el perifrico comunicacin con el perifrico (PA7-PA0 y PB7-PB0)

(PA7-PA0, PB7-PB0), pueden programarse Registros de sentido de datos (DDRA y DDRB)

como entradas o como salidas

Se utilizan para programar las lneas de comunicacin con

IRQA* el perifrico (PA7-PA0 y PB7-PB0)

Si DDRA[i] = 0 PAi acta como lnea de entrada

CA 1

D7-D0 Puerto A Si DDRA[i] = 1 PAi acta como lnea de salida

CA2

E (reloj) DDRA (El mismo funcionamiento para el puerto B)

PA7-PA0

R/W* ORA Lneas de control (CA1-CA2, CB1-CB2)

Se utilizan como lneas de control de entrada y salida

CS0 CRA

Para examinar el estado de los perifricos

CS1

Para generar seales de control sobre los mismos

CS2*

DDRB

PB7-PB0 Registros de control (CRA, CRB)

ORB Se utilizan para programar el funcionamiento de las lneas

RS0 CB1

de control (CA1-CA2, CB1-CB2)

CRB

RS1 CB2 Permiten capacitar/decapacitar localmente las

Puerto B interrupciones del interfaz

IRQB* Tambin contienen informacin de estado

estructura y tecnologa de computadores

9

2. interfaces de E/S paralela: MC6821 PIA

Seleccin de registros en la PIA

Para acceder a cualquier registro de la PIA deben estar activadas las lneas de Chip Select

CS0-CS1 se activan a alta

CS2* se activa a baja

Para seleccionar un registro particular se usan las lneas de Register Select

RS1 selecciona entre el puerto A o el puerto B

Si RS1 = 0 acceso a puerto A

Si RS1 = 1 acceso a puerto B

RS0 selecciona entre los registros de datos del puerto (ORx, DDRx) y registro de control (CRx)

Si RS0 = 0 acceso a registros de datos (ORx o DDRx)

(Para discriminar entre el registro ORx y DDRx se utiliza el bit 2 del registro de control CRx)

Si RS0 = 1 acceso a registros de control (CRx)

RS1 RS0 CRA2 CRB2 Registro

seleccionado

0 0 0 x DDRA

Acceso a puerto A 0 0 1 x ORA

0 1 x x CRA

1 0 x 0 DDRB

Acceso a puerto B 1 0 x 1 ORB

1 1 x x CRB

estructura y tecnologa de computadores

10

2. interfaces de E/S paralela: MC6821 PIA

Programacin de la PIA

La programacin de la PIA se realiza a travs de los registros de control CRA y CRB

Tipo de transicin a detectar por las lneas Cx1 y Cx2 (positiva o negativa)

Capacitacin/descapacitacin de interrupciones cuando se detecta la transicin programada

Programacin de Cx2 como salida para generar pulsos o seales de control especficas

7 6 5 4 3 2 1 0

C Rx Trans. Trans. Program. Cx2 DDRx Program. Cx1 Programacin de Cx1 (slo entrada)

Cx1 Cx2 /ORx

CRx[1]: tipo de transicin a detectar

Se activa cuando se detecta la CRx[1] = 1 transicin positiva

transicin programada por Cx1 CRx[1] = 0 transicin negativa

(activa IRQx* si est capacitada) CRx[0]: Capacitacin de IRQx*

CRx[0] = 0 IRQx* descapacit.

Se activa cuando se detecta la CRx[0] = 1 IRQx* capacitada

transicin programada por Cx2

(activa IRQx* si est capacitada)

Seleccin del acceso

Programacin de Cx2 (lnea de entrada/salida) a DDRx o ORx

CRx[5]: programa Cx2 como entrada o salida Si Cx2 programada como salida

CRx[5] = 1 Cx2 acta como entrada CRx Modo Descripcin

CRx[5] = 0 Cx2 acta como salida bit 5 bit 4 bit 3

"Handshake" Cx2 a alta cuando se produce una

Si Cx2 programada como entrada 1 0 0 en lectura (A) transicin programada por Cx1

o en escritura (B) Vuelve a baja cuando se hace una lectura

CRx[4]: tipo de transicin a detectar

(A) o una escritura (B) del puerto

CRx[4] = 0 transicin positiva Cx2 a baja durante un ciclo despus de

CRx[4] = 1 transicin negativa 1 0 1 Salida pulso una lectura (A) o una escritura (B) del

CRx[3]: Capacitacin de IRQx* puerto. Puede usarse para indicar al

CRx[3] = 0 IRQx* descapacitada perifrico que se ha ledo el dato

1 1 0 Salida manual Cx2 a baja (sigue a bit 3)

CRx[3] = 1 IRQx* capacitada

1 1 1 Salida manual Cx2 a alta (sigue a bit 3)

estructura y tecnologa de computadores

11

2. interfaces de E/S paralela: MC6821 PIA

Ejemplo: conexin de una impresora paralela al MC68000 a travs de la PIA

MC68000 PIA MC6821

D7-D0 D7-D0 Puerto A

A1 RS0 PA7-PA0 D7-D0

IMPRESORA

A2 RS1 CA2 STB PARALELA

8 BITS

DECODIF.

A23-A3 DIR CS1 CA1 ACK

EN*

AS*

Puerto B

VPA*

PB7-PB0

LDS* CS0 CB2

VMA* CS2*

E E CB1 Conexin de la PIA (puerto A) a la impresora

Lneas de datos de la impresora (D0-D7)

Protocolo de comunicacin con la impresora Se conectan a las lneas PA0-PA7 (programadas

como salidas)

(Handshake simple)

Lnea de orden de impresin (STB = Strobe)

Se conecta a la lnea CA2 (progr. como salida)

D7-D0 carcter 1 carcter 2 Un flanco positivo por STB indica a la

carcter n

impresora que hay un nuevo carcter en

STB el registro ORA que debe imprimir

Lnea de respuesta de dato impreso (ACK)

ACK Se conecta a la lnea CA1 (entrada)

La impresora genera un flanco positivo

por ACK cuando ha terminado de imprimir

un carcter y est lista para el siguiente

estructura y tecnologa de computadores

12

2. interfaces de E/S paralela: MC6821 PIA

Conexin de la PIA al bus del MC68000

Utilizamos el bus sncrono del MC68000 (ya que la PIA es un interfaz sncrono)

E (seal de reloj) conectada al reloj de la PIA

VMA* (Valid Memory Address) conectada a CS2*

Conectamos la parte baja del bus de datos (D0-D7) a las lneas de datos de la PIA

Elegimos direcciones impares para los registros de la PIA

LDS* conectada a CS2*

A23-A3 conectadas a CS1 a travs de un descodificador (elegimos direcciones no usadas por la memoria)

A1-A2 conectadas a RS0-RS1

Conectamos VPA* a la salida del descodificador para que el MC68000 utilice interrupciones autovectorizadas

Programa de impresin a travs de la PIA con E/S programada con espera de respuesta

Inicializacin de la PIA

1. Programamos las lneas PA0-PA7 como salida: DDRA 11111111 = $FF (CRA[2] debe tener el valor 0)

2. Programacin del registro de control CRA: CRA XX11X110 = $36

a) Programamos CA2 como salida manual (haciendo que siga al valor de CRA3) para generar la seal STB

CRA[4] 1; CRA[3] 1

b) Programamos para que CA1 detecte un pulso positivo (seal ACK) y descapacitamos interrupciones

CRA[1] 1; CRA[0] 0

c) CRA[2] 1 para que quede seleccionado el registro de datos ORA

Transmisin de un carcter a la impresora

1. Enviar carcter a ORA (datos vlidos en PA0-PA7)

2. Generar manualmente pulso de Strobe

Poner CA2 a 0 (poniendo un 0 en CRA[3] CRA XX110110 = $36)

Poner CA2 a 1 (poniendo un 1 en CRA[3] CRA XX111110 = $3E)

3. Comprobar valor de CRA[7]

4. Si CRA[7]=0 (impresora no ha generado el pulso positivo ACK) volver a 3

estructura y tecnologa de computadores

13

2. interfaces de E/S paralela: MC6821 PIA

Programa ensamblador

Programar PIA

ORA EQU $ee0001 Etiqueta de ORA

Inicializar puntero del texto DDRA EQU $ee0001 Etiqueta de DDRA (=ORA)

A0 #TEXTO CRA EQU $ee0003 Etiqueta del registro CRA

MAXCAR EQU 100 Mx. n de caracteres del texto

EOT EQU 20 Carcter ASCII de fin de texto

Leer siguiente carcter *

D0 (A0)+ TEXTO DS.B MAXCAR Reservamos MAXCAR bytes

* para el texto

*

Final de texto? S INICIO MOVE.B #0,CRA Seleccionar DDRA (CRA[2] 0)

FIN MOVE.B #$FF,DDRA Programar PA0-PA7 como salidas

D0 = #EOT?

MOVE.B #$36,CRA Programar el registro CRA

NO MOVEA.L #TEXTO,A0 Llevar dir. de comienzo del texto a A0

Enviar carcter a impres. BUCLE MOVE.B (A0)+,D0 Leer carcter e incrementar A0

ORA D0 * para apuntar al siguiente carcter

CMP #EOT,D0 Comprobar si es el final de texto

BEQ FIN Si es final de texto vamos a FIN

Generar pulso STB MOVE.B D0,ORA Enviar carcter a impresora

CRA #$36 MOVE.B #$36,CRA Generar seal STB CA2 = 0

CRA #$3E MOVE.B #$3E,CRA Generar seal STB CA2 = 1

LEE_CRA BTST.B #7,CRA Chequer CRA[7]

BEQ LEE_CRA Si CRA[7] = 0 carcter no impreso

S ACK activada? BRA BUCLE Si CRA[7] = 1 siguiente carcter

CRA[7]=1? FIN TRAP #15 FIN: Regresar al programa monitor

DC.W $10

NO

estructura y tecnologa de computadores

14

3. fundamentos de la E/S serie

Modo de transmisin serie asncrona Errores por desincronizacin de los relojes

El emisor y el receptor utilizan seales de reloj

0 1 0 0 1 0 1 1 1 0 1 datos

distintas transmitidos

Problema muestreo

sincronizado

0 1 0 0 1 0 1 1 1 0 1

Aunque utilicen la misma frecuencia, los relojes

muestreo

del emisor y el receptor pueden estar desfasados desincronizado

0 1 0 0 1 0 1 1 1 1 0

Aunque ambos relojes estn perfectamente

sincronizados, transcurrido un cierto tiempo Errores

tendern a desincronizarse Sincronizacin mediante bits de start y stop

Solucin car1 car2 car3 car4

El receptor y el emisor resincronizan sus relojes al

inicio de cada carcter t

Con cada carcter se incluyen un bit de start y Caracter transmitido: $8B (10001011)

uno (o varios) bits de stop

Polaridad opuesta provoca una transicin LSB MSB

al inicio de cada carcter 1 1 0 1 0 0 0 1

Esta transicin es utilizada por el receptor

para sincronizarse con el emisor PARI

START DATOS (par) STOP

Es til nicamente a bajas velocidades de

transmisin

Desde unos pocos bps hasta varios Kbps

Punto medio Periodo muestreos en

bit deSTART 1 bit recepcin

estructura y tecnologa de computadores

15

3. fundamentos de la E/S serie

Modo de transmisin serie sncrona

El emisor y el receptor utilizan la misma seal de reloj

Puede utilizarse una lnea independiente para transmitir la seal de reloj en paralelo con los datos

Mayor coste de la lnea

Puede codificarse la seal de reloj junto con los datos

Codificacin bipolar

Codificacin Manchester

Codificacin Manchester diferencial

Etc. 1 0 0 1 1 1 0 1

Codificacin

Cdigo por Nivel

Manchester:

0= Codificacin

Manchester

1=

Reloj

extrado

Es necesaria para transmisin serie a velocidades medias y altas

Del orden de Mbps o Gbps

estructura y tecnologa de computadores

16

3. fundamentos de la E/S serie

Esquema de un interfaz serie asncrono

Lneas TxD y RxD

Hin

Para transmisin y recepcin de datos

Lneas Hin y Hout IRQ

Reg Estado Reg Trans.

Lneas de control o handshake para realizar los Reg Desp. T TxD

protocolos de comunicacin

Reg Control

Reloj Trans.

Registro de desplazamiento de transmisin Bus

Generador

Datos

Reloj

Realiza la conversin serie/paralelo Reloj Recep.

Registro de desplazamiento de recepcin R/W* RxD

Reg Desp. R

Realiza la conversin paralelo/ serie CS* Lgica

...

Control Reg Recep.

RS

Generador de reloj

Hout

Genera la seal de reloj de la transmisin y la recepcin

Registro de estado

Permite detectar el estado de las lneas de handshake de entrada

Permite conocer el estado de los registros de recepcin y transmisin (llenos o vacos)

Registro de control

Permite programar los parmetros de la transmisin

Velocidad de transmisin

N de bits de stop (1, 1.5 2)

N de bits por carcter (5, 6, 7 u 8)

Tipo de paridad (par, impar, no paridad)

Permite programar el funcionamiento de las lneas de handshake de salida

Permite capacitar/descapacitar localmente las interrupciones

estructura y tecnologa de computadores

17

3. fundamentos de la E/S serie

Esquema de un interfaz serie sncrono

Lneas TxD y RxD Hin

Para transmisin y recepcin de datos

IRQ Generador

Lneas Hin y Hout Reg Estado Reloj

FIFO Reloj Trans.

Lneas de control o handshake para realizar Trans.

TxD

los protocolos de comunicacin Reg Desp. T

Reg Control

Bus

Registro de desplazamiento de transmisin Datos RxD

Reg Desp. R

Realiza la conversin serie/paralelo FIFO

Recep. Reloj Recep.

Mezcla la seal de reloj junto con los datos R/W* Extractor

CS* Lgica Reloj

Registro de desplazamiento de recepcin Control

...

RS

Realiza la conversin paralelo/serie

Hout

Extrae la seal de datos a partir de la seal recibida

Extractor de reloj

Extrae la seal de reloj a partir de la seal recibida

Colas (FIFO) de transmisin y recepcin

Para adaptar la velocidad de los dispositivos

Registro de estado

Permite detectar el estado de las lneas de handshake de entrada

Permite conocer el estado de los registros y las colas de recepcin y transmisin

Registro de control

Permite programar los parmetros de la transmisin

Permite programar el funcionamiento de las lneas de handshake de salida

Permite capacitar/descapacitar localmente las interrupciones

estructura y tecnologa de computadores

18

4. interfaces de E/S serie

Ejemplos de interfaces de E/S serie

Interfaces para comunicacin serie asncrona

i8250 UART (Universal Asynchronous Receiver-Transmitter)

MC6850 ACIA (Asynchronous Communications Interface Adapter)

R6552 DACIA (Dual Asynchronous Communications Interface Adapter), compatible con Motorola 6800/68000

Interfaces para comunicacin serie sncrona

i8273 (Programmable HDLC/SDLC Protocolo Controller)

MC6852 ADLC (Advanced Data-Link Controller)

MC6854 SSDA (Synchronous Serial Data Adapter)

Interfaces para comunicacin serie sncrona y asncrona

i8251 USART (Universal Synchronous-Asynchronous Receiver-Transmitter)

MC68661 EPCI (Enhaced Programmable Communications Interface)

estructura y tecnologa de computadores

19

4. interfaces de E/S serie: MC6850 ACIA

Interfaz MC6850 ACIA (Asynchronous Communications Interface Adapter)

Interfaz de comunicacin serie asncrona diseado para sistemas basados en el MC6800 (bus sncrono)

Compatible con el MC68000

Organizacin de la ACIA

D7-D0 TxData

TDR Lnea de transmisin de datos

RDR RxData Lnea de recepcin de datos

CS0

CS1 TxCLK Seal de reloj de la transmisin Suelen conectarse

Lneas de CS2* RxCLK al mismo oscilador

Seal de reloj de la recepcin

comunicacin

E

con la CPU CTS*

RTS*

Seales de control de la transmisin

R/W * CR

para protocolos de comunicacin (handshake)

RS SR DCD*

Son un subconjunto de las lneas del RS-232

IRQ* Registro de estado (SR)

Informacin del estado de los registros RDR y TDR

Registro de transmisin de datos (TDR) Informacin del estado de las lneas de control

Para enviar datos a travs de TxD Informacin sobre situaciones de error

Realiza la conversin paralelo/serie Registro de control (CR)

Registro de recepcin de datos (TDR) Programacin de los parmetros de la transferencia

Para leer los datos recibidos a travs de RxD Programacin de las lneas de control

Realiza la conversin serie/paralelo Capacitacin/descapacitacin local de interrupciones

estructura y tecnologa de computadores

20

4. interfaces de E/S serie: MC6850 ACIA

Seleccin de registros de la ACIA

La ACIA dispone de 4 registros de 8 bits cada uno

Dos registros de escritura: TDR y CR

Dos registros de lectura: RDR y SR

Para acceder a cualquier registro de la ACIA deben estar activadas las lneas de Chip Select (CS)

CS0-CS1 se activan a alta

CS2* se activa a baja SR R/W* Reg. Selecc.

Para seleccionar un registro particular se usan las lnea 0 0 CR (escritura)

de Register Select (RS) y R/W* 0 1 SR (lectura)

Si RS = 0 acceso a registros de control y estado 1 0 TDR (escritura)

1 1 RDR (lectura)

Si RS = 1 acceso a registros de transmisin y recepcin

Seales de control de la transmisin

Son un subconjunto de las lneas RS-232 para la conexin y control de un mdem

RTS* (Request to Send) Solicitud de envo

Lnea de salida que activa la CPU cuando quiere solicitar permiso para enviar un dato al mdem

CTS* (Clear to Send) Preparado para el envo

Lnea de entrada que activa el mdem cuando est listo para recibir datos de la CPU (en respuesta a RTS)

y enviarlos a travs de la lnea telefnica

DCD* (Data Carrier Detect) Deteccin de portadora

Lnea de entrada que activa el mdem cuando detecta datos de llegada por la lnea telefnica

estructura y tecnologa de computadores

21

4. interfaces de E/S serie: MC6850 ACIA

Programacin de la ACIA

La programacin de la ACIA se realiza a travs del registro de control CR

Seleccin de la frecuencia Seleccin del formato

Puede modificarse la frecuencia de Permite seleccionar los siguientes parmetros:

0

Selecc. transmisin o recepcin dividiendo la N de bits de datos (7 u 8)

Frecuen- frecuencia del oscilador por 1, 16 64 Tipo de paridad (par, impar, no paridad)

cia CR[1] CR[0] Funcin N de bits de stop (1 2)

1

0 0 D iv i s i n p o r 1 CR[4] CR[3] CR[2] Funcin

0 1 D iv i s i n p o r 1 6 0 0 0 7 bits datos + paridad par + 2 bits stop

1 0 D iv i s i n p o r 6 4 0 0 1 7 bits datos + paridad impar + 2 bits stop

1 1 Reset ACIA 0 1 0 7 bits datos + paridad par + 1 bit stop

2

0 1 1 7 bits datos + paridad impar + 1 bit stop

1 0 0 8 bits datos + no paridad + 2 bits stop

1 0 1 8 bits datos + no paridad + 1 bit stop

Selecc. 1 1 0 8 bits datos + paridad par + 1 bit stop

3

1 1 1 8 bits datos + paridad impar + 1 bit stop

Formato

CR

Control de la Transmisin

4 CR[6] CR[5] Funcin

0 0 Descapacita interrupciones por TDR vaco

Pone RTS* a baja

0 1 Capacita interrupciones por TDR vaco

5 Pone RTS* a baja

Control 1 0 Descapacita interrupciones por TDR vaco

Pone RTS* a alta

Transmis.

1 1 Descapacita interrupciones por TDR vaco

6 Pone RTS* a baja y TxD a baja ("break")

Control de la Recepcin

CR[7] Funcin

7 Control

Recepc. 0 Descapacita interrupciones por RDR lleno

1 Capacita interrupciones por RDR lleno

estructura y tecnologa de computadores

22

4. interfaces de E/S serie: MC6850 ACIA

Registro de estado de la ACIA (SR)

La programacin de la ACIA se realiza a travs del registro de control SR

Bit

RDR Se activa cuando se ha recibido un carcter completo (el carcter recibido est almacenado en RDR)

0

Lleno Se desactiva al leer RDR

1 TDR Se activa cuando se ha transmitido completamente el contenido de TDR

Vaco Se desactiva al escribir sobre TDR

2 CDC*

Activado Indica si la lnea CDC* est activada

3 CTS* Indica si la lnea CTS* est activada

Activado

SR

Error Error de formato

4

Formato Se activa cuando se recibe un carcter con un formato errneo (n de bits de datos o de stop errneo)

Error Error de solapamiento de la recepcin

5 Solapam.

Recepc. Se activa cuando se recibe un nuevo carcter por RxD antes de que el anterior haya sido ledo

6 Error Error de paridad

Paridad Se activa cuando la paridad calculada no coincide con el valor del bit de paridad del carcter recibido

7 IRQ Flag de interrupcin

Refleja el estado de la lnea de peticin de interrupcin IRQ*

estructura y tecnologa de computadores

23

4. interfaces de E/S serie: MC6850 ACIA

Ejemplo: conexin de una impresora serie al MC68000 a travs de la ACIA

MC68000 ACIA MC68250

D7-D0 D7-D0

A1 RS TxD RxD

IMPRESORA

RTS* DSR* SERIE

DECODIF. CTS* DTR*

A23-A2 DIR CS1

EN*

AS*

VPA*

Conexin de la ACIA a la impresora

LDS* CS0

VMA* CS2* Lnea de transmisin(TxD)

E E

Se conecta a la lnea de recepcin (RxD)

Programacin de la ACIA para realizar de la impresora

E/S programada con espera de respuesta Lnea RTS* (Request to Send)

Se conecta a la lnea DSR* (Data Set

1. Control de recepcin Ready) de la impresora

No permitir interrupciones por recepcin CR[7]=0

2. Control de transmisin Estar activada durante toda la transmisin

Transmisin sin interrupciones y activacin de RTS* (desde el primer carcter hasta el ltimo)

CR[6]=0; CR[5]=0 Lnea de CTS* (Clear to Send)

3. Seleccin del formato Se conecta a la lnea DTR* (Data Terminal

8 bits de datos, no paridad, 1 bit de stop Ready) de la impresora

CR[4]=1; CR[3]=0; CR[2]=1

La impresora activa esta lnea cuando ha

4. Seleccin de la frecuencia

Dividir frecuencia por 16 CR[1]=0; CR[0]=1 impreso un carcter y est preparada para

Valor de CR: %00010101 = $15 recibir el siguiente

estructura y tecnologa de computadores

24

4. interfaces de E/S serie: MC6850 ACIA

Programar ACIA

CR #$15

Programa ensamblador

TDR EQU $ee0001 Etiqueta de TDR

Inicializar puntero del texto

CR EQU $ee0003 Etiqueta de CR

A0 #TEXTO

SR EQU $ee0003 Etiqueta de SR (=CR)

MAXCAR EQU 100 Mx. n de caracteres del texto

EOT EQU 20 Carcter ASCII de fin de texto

Leer siguiente carcter *

D0 (A0)+ TEXTO DS.B MAXCAR Reservamos MAXCAR bytes

* para el texto

*

Final de texto? S INICIO MOVE.B #$15,CR Programar ACIA

FIN

D0 = #EOT? MOVEA.L #TEXTO,A0 Llevar dir. de comienzo del texto a A0

NO BUCLE MOVE.B (A0)+,D0 Leer carcter e incrementar A0

* para apuntar al siguiente carcter

Enviar carcter a impres. CMP #EOT,D0 Comprobar si es el final de texto

TRD D0 BEQ FIN Si es final de texto vamos a FIN

MOVE.B D0,TDR Enviar carcter a impresora

TEST_TDR BTST.B #1,SR Chequear SR[1] (TDR vaco)

TDR vaco? NO BEQ TEST_TDR Si SR[1] = 0 TDR no vaco

SR[1]=1? TEST_CTS BTST.B #3,SR Chequear SR[3] (CTS* activado)

BEQ TEST_CTS Si SR[3] = 0 CTS* desactivado

S BRA BUCLE Pasar a imprimir siguiente carcter

FIN TRAP #15 FIN: Regresar al programa monitor

CTS* activado? NO

DC.W $10

SR[3]=1?

S

estructura y tecnologa de computadores

Vous aimerez peut-être aussi

- Tema 3 - Entrada - Salida Programada e InterrupcionesDocument43 pagesTema 3 - Entrada - Salida Programada e InterrupcionesJesús NamigtlePas encore d'évaluation

- Prácticas de redes de datos e industrialesD'EverandPrácticas de redes de datos e industrialesÉvaluation : 4 sur 5 étoiles4/5 (5)

- 22 23 M1T1 Arquitectura E SDocument48 pages22 23 M1T1 Arquitectura E SpepitaPas encore d'évaluation

- Reparación de instalaciones automatizadas. ELEE0109D'EverandReparación de instalaciones automatizadas. ELEE0109Pas encore d'évaluation

- Deber 2 - PLC - Kevin AlavaDocument4 pagesDeber 2 - PLC - Kevin AlavaKevin AlavaPas encore d'évaluation

- Operaciones auxiliares de montaje de componentes informáticos. 2ª edición (MF1207_1): HARDWARE (O SOPORTE FÍSICO DEL ORDENADOR)D'EverandOperaciones auxiliares de montaje de componentes informáticos. 2ª edición (MF1207_1): HARDWARE (O SOPORTE FÍSICO DEL ORDENADOR)Pas encore d'évaluation

- Resultado de Aprendizaje 6Document12 pagesResultado de Aprendizaje 6Cesar Omar Fierro AguilarPas encore d'évaluation

- Automatas Programables Industriales API - PLCDocument29 pagesAutomatas Programables Industriales API - PLCmaicolmzPas encore d'évaluation

- Interfaz E-S - Automation Studio 3.0.5Document47 pagesInterfaz E-S - Automation Studio 3.0.5ADOLFO ALEJANDRO CORDOVA PEÑAPas encore d'évaluation

- TIPOS de SEÑALESDocument14 pagesTIPOS de SEÑALESHuntolKiletfg100% (1)

- Entradas Salida MicroprocesadoresDocument10 pagesEntradas Salida MicroprocesadoresOscar SanchezPas encore d'évaluation

- Iasimp Qr009a Es P Planos Compact LogixDocument6 pagesIasimp Qr009a Es P Planos Compact Logixmarianela belloPas encore d'évaluation

- Unidad de Entrada-SalidaDocument41 pagesUnidad de Entrada-SalidaRaúl BacetePas encore d'évaluation

- Capitulo III - Interfaz ParalelaDocument72 pagesCapitulo III - Interfaz ParalelaJorge Gianotti HidalgoPas encore d'évaluation

- Practica 2Document6 pagesPractica 2Kevin Muyón RiveraPas encore d'évaluation

- SCANET应用基础篇 TRADUCIDODocument46 pagesSCANET应用基础篇 TRADUCIDOAlvaro Jesus Ledo PelaezPas encore d'évaluation

- Arquitectura, Configuración y Características Eléctricas de Los Puertos de ES Del MicrocontroladorDocument3 pagesArquitectura, Configuración y Características Eléctricas de Los Puertos de ES Del MicrocontroladorFelixAlvarez100% (2)

- Trabajando Con ARDUINO PDFDocument30 pagesTrabajando Con ARDUINO PDFOsito de AguaPas encore d'évaluation

- S04s1 - Arq - PDS - Manejo de Puertos in - Out - Matlab X-XC16Document41 pagesS04s1 - Arq - PDS - Manejo de Puertos in - Out - Matlab X-XC16renatto2089Pas encore d'évaluation

- Actividad ProcesadoresDocument5 pagesActividad ProcesadoresFelipe MontoyaPas encore d'évaluation

- Practica 2Document9 pagesPractica 2George Contreras HernandezPas encore d'évaluation

- Informe Practica 1 IoDocument7 pagesInforme Practica 1 IoFabricio ÑacatoPas encore d'évaluation

- Curso-PlcDocument30 pagesCurso-PlcR E P A R A N D O E N C A S APas encore d'évaluation

- Practica Bravo LeonDocument12 pagesPractica Bravo LeonLaura IO HernándezPas encore d'évaluation

- Interfaz Ieee 488 para PCDocument102 pagesInterfaz Ieee 488 para PCBen AvrahamPas encore d'évaluation

- Microprocesadores Luis-Urdaneta Capítulo 9Document84 pagesMicroprocesadores Luis-Urdaneta Capítulo 9Saint-Amy SuburbiaPas encore d'évaluation

- Lab 01 - Dispositivos y Software de ProgramaciónDocument7 pagesLab 01 - Dispositivos y Software de Programaciónfranshesco.mendizabaPas encore d'évaluation

- Prácticas y Tareas CLA - 16Document16 pagesPrácticas y Tareas CLA - 16H Tavera0% (1)

- UNSAM SPD 08 ES Interrupciones DMA PDFDocument58 pagesUNSAM SPD 08 ES Interrupciones DMA PDFKenton OrtizPas encore d'évaluation

- Laboratorio PLCDocument17 pagesLaboratorio PLCKenny Jiménez RuizPas encore d'évaluation

- Lab 03 Puertos de Entrada y SalidaDocument15 pagesLab 03 Puertos de Entrada y SalidaJames Jerry YTPas encore d'évaluation

- 6 - 6.7 ArqDocument22 pages6 - 6.7 Arqbyron guerreroPas encore d'évaluation

- Microprocesador 8085Document7 pagesMicroprocesador 8085Percy VillegasPas encore d'évaluation

- Tarea 5Document3 pagesTarea 5after909Pas encore d'évaluation

- Conexion PC - PLCDocument9 pagesConexion PC - PLCJesus Ortiz LopezPas encore d'évaluation

- Estructura y Funcionamiento Relés Digitales de ProteccionDocument12 pagesEstructura y Funcionamiento Relés Digitales de Proteccionrochopaez50% (2)

- Lab Sistemas MIcroprocesados Practica6 2018ADocument4 pagesLab Sistemas MIcroprocesados Practica6 2018AAngelogc2014Pas encore d'évaluation

- Inf Alu 8085Document14 pagesInf Alu 8085Paul ChiliquingaPas encore d'évaluation

- Informe Diseño ElectronicoDocument15 pagesInforme Diseño ElectronicoFernando Pinto MonteroPas encore d'évaluation

- Automatización IndustrialDocument17 pagesAutomatización IndustrialMarco Antonio Guevara Martinez100% (1)

- Micro 8051Document35 pagesMicro 8051slash571Pas encore d'évaluation

- Tema 2Document11 pagesTema 2Angel MartinezPas encore d'évaluation

- Manual Etap Power Station 5Document144 pagesManual Etap Power Station 5Carlos Andrés Ruiz HernandezPas encore d'évaluation

- Programación Básica Unidad 8: PuertosDocument38 pagesProgramación Básica Unidad 8: PuertosEdgar Hernández GarcíaPas encore d'évaluation

- Introduccion A Los MicroDocument9 pagesIntroduccion A Los MicroPabloPas encore d'évaluation

- Herramientas ElectrónicasDocument75 pagesHerramientas Electrónicasesteban muñozPas encore d'évaluation

- Practicas DigitalesDocument23 pagesPracticas DigitalesdavidPas encore d'évaluation

- SIST OPE Semana1Document39 pagesSIST OPE Semana1YULY SUAREZ TAPIAPas encore d'évaluation

- Portafolio Microcontroladores 5Document15 pagesPortafolio Microcontroladores 5Daniel100% (1)

- Diapositivas REDES SIEMENSDocument92 pagesDiapositivas REDES SIEMENSRUBEN DARIO TAMAYO BALLIVIANPas encore d'évaluation

- Material PLC - Instrucciones de Programación V 2.0Document70 pagesMaterial PLC - Instrucciones de Programación V 2.0Gilberto MottoPas encore d'évaluation

- Practica de Unidad UartDocument53 pagesPractica de Unidad UartLizzy GómezPas encore d'évaluation

- Funcionamiento Del 8255Document21 pagesFuncionamiento Del 8255José Luis PalloPas encore d'évaluation

- Comunicacion SerialDocument10 pagesComunicacion SerialSantiagoJimenezJavierJimenezPas encore d'évaluation

- Practica 5 Sistemas DigitalesDocument8 pagesPractica 5 Sistemas DigitalesWellington BasilioPas encore d'évaluation

- Bus Ieee-488 PDFDocument102 pagesBus Ieee-488 PDFGABRIELPEREZBRINDISPas encore d'évaluation

- Informe - ELIZABETH ESTEFANIA ALVARADO RUBIODocument5 pagesInforme - ELIZABETH ESTEFANIA ALVARADO RUBIOwilson sanchez ocanaPas encore d'évaluation

- Juan Pineros 201710340 Lab1 MicroCDocument22 pagesJuan Pineros 201710340 Lab1 MicroCJUAN CARLOS PI?æEROS PEREZPas encore d'évaluation

- Informe 01Document13 pagesInforme 01Jozeph NeirPas encore d'évaluation

- Mult Í MetroDocument15 pagesMult Í MetroJOSEJOSEPas encore d'évaluation

- Solucion General Examen 1 2014Document3 pagesSolucion General Examen 1 2014JOSEJOSEPas encore d'évaluation

- Examen 3 2013Document3 pagesExamen 3 2013JOSEJOSEPas encore d'évaluation

- Coleccion Problemas Examen 1 Elc-215Document5 pagesColeccion Problemas Examen 1 Elc-215Pedro Boanerges Paz RomeroPas encore d'évaluation

- Secciones 6.9 A 6.12.4Document36 pagesSecciones 6.9 A 6.12.4JOSEJOSEPas encore d'évaluation

- Examen 1 Elc-215 2013Document4 pagesExamen 1 Elc-215 2013JOSEJOSEPas encore d'évaluation

- Guia de Instalacion de Software Requerido para La AsignaturaDocument14 pagesGuia de Instalacion de Software Requerido para La AsignaturaAbiel RosaPas encore d'évaluation

- Examen Reprisse 1 2014Document1 pageExamen Reprisse 1 2014JOSEJOSEPas encore d'évaluation

- Examen 4 Elc-215 2011Document3 pagesExamen 4 Elc-215 2011JOSEJOSEPas encore d'évaluation

- Lenguaje Ensamblador Del MicroprocesadorDocument54 pagesLenguaje Ensamblador Del Microprocesadorfrancis huamanñahui zavalaPas encore d'évaluation

- Criterios de Evaluación de Los ReportesDocument1 pageCriterios de Evaluación de Los ReportesJOSEJOSEPas encore d'évaluation

- Guia 1 PDFDocument10 pagesGuia 1 PDFPablo Fernando Guzman QuispePas encore d'évaluation

- Señales en El Bus 8086 (8088)Document1 pageSeñales en El Bus 8086 (8088)JOSEJOSEPas encore d'évaluation

- Manual Ensamblador 8086Document17 pagesManual Ensamblador 8086Mario R. Cianone100% (1)

- Guia 1 SDG115-2016 PDFDocument5 pagesGuia 1 SDG115-2016 PDFJavi HnrqzPas encore d'évaluation

- Tutorial Del Emu8086 - ItescamDocument20 pagesTutorial Del Emu8086 - ItescamErick Alex DíazPas encore d'évaluation

- Primer Parcial RedesDocument10 pagesPrimer Parcial RedesCristhian CarrizalesPas encore d'évaluation

- Epson XP 401Document2 pagesEpson XP 401Fernando LopezPas encore d'évaluation

- EZ 1000plus SeriesDocument2 pagesEZ 1000plus SeriesRibbonPas encore d'évaluation

- SpoolingDocument6 pagesSpoolingDaniel MTPas encore d'évaluation

- La Computadora y Sus PartesDocument4 pagesLa Computadora y Sus PartesMango MoritaPas encore d'évaluation

- Tipos de Discos DurosDocument3 pagesTipos de Discos DurosChristopher StevensPas encore d'évaluation

- Brother DCP - T710W FTDocument6 pagesBrother DCP - T710W FTAlejo ByTech VillavoPas encore d'évaluation

- Componentes Internos Del ComputadorDocument9 pagesComponentes Internos Del Computadorcarla riveroPas encore d'évaluation

- Costas Lago NataliDocument16 pagesCostas Lago NatalialfredoesperanzaPas encore d'évaluation

- Que Es AsteriskDocument21 pagesQue Es Asteriskusuario99**Pas encore d'évaluation

- Presupuesto EquipamientoDocument1 pagePresupuesto EquipamientoMiguel Angel Huayhuani CardenasPas encore d'évaluation

- Redes InterconexiionDocument5 pagesRedes InterconexiionJulieth Andrea Lopez DoradoPas encore d'évaluation

- Codificacion y ModulacionDocument18 pagesCodificacion y Modulacionkerveroz0% (2)

- ExamDocument4 pagesExamadoPas encore d'évaluation

- Manual Configuration S7-300 - R1703Document55 pagesManual Configuration S7-300 - R1703AngelPas encore d'évaluation

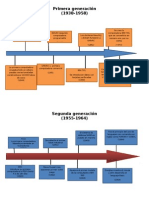

- Lineas Del Tiempo de Las GeneracionesDocument5 pagesLineas Del Tiempo de Las Generacionesrodrigomendozacruz123Pas encore d'évaluation

- EstandaresDocument22 pagesEstandaresSugey VegaPas encore d'évaluation

- Crucigrama para AlumnoDocument3 pagesCrucigrama para Alumnofguope27100% (1)

- Modulacion PCMDocument12 pagesModulacion PCMDiego ZMPas encore d'évaluation

- Ficha Técnica de Mantenimientos Programados de Equipos de Cómputo e ImpresorasDocument1 pageFicha Técnica de Mantenimientos Programados de Equipos de Cómputo e ImpresorasFranco AbrahanPas encore d'évaluation

- Lista Sistemas de Sonido Inteligente - 18-10-18Document7 pagesLista Sistemas de Sonido Inteligente - 18-10-18Julio Cesar PilcoPas encore d'évaluation

- Manual Del Proyector PDFDocument84 pagesManual Del Proyector PDFfranciscoPas encore d'évaluation

- Manual Impresora BrotherDocument171 pagesManual Impresora BrotherXiñor KobiñasPas encore d'évaluation

- Tecnologia 3GDocument23 pagesTecnologia 3GRonald GonzaloPas encore d'évaluation

- Guia TV 4KDocument36 pagesGuia TV 4KJoshPas encore d'évaluation

- Planificacion de Clase de RedesDocument22 pagesPlanificacion de Clase de RedesAribert GarciaPas encore d'évaluation

- Sistema de Comunicación Fase 1Document1 pageSistema de Comunicación Fase 1picoto0% (1)

- Sincronización de Gestores de Base de DatosDocument4 pagesSincronización de Gestores de Base de DatosglamaizvePas encore d'évaluation

- Aplicación de La Normatividad InformáticaDocument4 pagesAplicación de La Normatividad InformáticaJuan Niño TorresPas encore d'évaluation

- SolucionarioDocument3 pagesSolucionarioJhostin David Rojas Porras50% (2)