Académique Documents

Professionnel Documents

Culture Documents

Comparator Slides v1 - 0 PDF

Transféré par

Paramesh WaranTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Comparator Slides v1 - 0 PDF

Transféré par

Paramesh WaranDroits d'auteur :

Formats disponibles

Department of Electrical and Computer Engineering

CMOS Comparator Design

Extra Slides

Vishal Saxena, Boise State University

(vishalsaxena@boisestate.edu)

Vishal Saxena -1-

Comparator Design Considerations

Comparator =

Preamp (optional)

+ Reference Subtraction (optional for single-bit case)

+ Regenerative Latch

+Static Latch to hold outputs (optional)

Design Considerations

Accuracy (dynamic and static offset, noise, resolution)

Settling time (tracking BW, regeneration speed)

Sensitivity/resolution (gain)

Metastability (ability to make correct decisions)

Overdrive recovery (memory)

Power consumption

Vishal Saxena -2-

An Example CMOS Comparator

Vos orginiates from:

VDD

Preamp input pair

M3 M4 M5 M6 mismatch (Vth,W/L)

PMOS loads and

Vos + current mirror

Vo V o-

M1 M2

Latch offset

Vi M9

Charge-Injection

M7 M8

clock-feedthru imbalance

of the reset switch (M9)

VSS

Clock routing

Preamp Latch

Parasitics

Vishal Saxena -3-

Latch Regeneration

VDD

PA tracking Latch

Latch reseting regenrating

M5 M6

VDD

+ -

Vo Vo

Vo+

CL M9 CL

Vo

M7 M8

Vo-

VSS VSS

Exponential regeneration due to positive feedback of M7 and M8

Vishal Saxena -4-

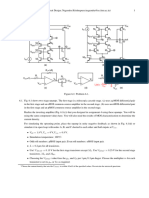

Regeneration Speed Linear Model

Vo+ Vo- Vo+

-1

CL CL

CL gmVo-

M7 M8 Vo-

Vo Vo

1 1 Vo

0

o

V gm Vo /sCL 1 gm /sCL Vo

s gm /sCL 1 0 sp gm /CL , singleRHP pole

Vo t 0 Vo t 0 expt gm /CL

Vishal Saxena -5-

Reg. Speed Linear Model

Vo+ Vo-

CL CL

Vo(t=0)

t Vo = 1V

M7 M8

Vo Vo(t=0) t/(CL/gm)

1V 100mV 2.3

CL Vo t

1V 10mV 4.6 t ln

gm Vo t 0

1V 1mV 6.9

1V 100V 9.2

Vishal Saxena -6-

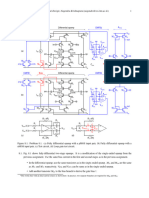

Reg. Speed Linear Model

Reg. Speed Linear Model

M3 M4 Vm+ M5 M6 Vm- gm5Vm+ gm5Vm-

Vm+ V m- =1 R9 R9

M1 M2 x Vo +

Vo-

Vo+ 2 2 Vo-

Vi M9 X

-1 -1

M7 M8

gm7 gm7

gm1 gm5R9 R9 1

A V1 A V2 , to be amplifier.

gm3 2 gm7R9 2 gm7

Vo 0 Vi 0 A V Vi 0 A V1A V2

Vo t Vi 0 A V1A V2 expt gm /CL

Vishal Saxena -7-

Comparator Metastability

T/2 Linear Model

Reg. Speed

Vo t Vi 0 A V1A V2 expt gm /CL

Curve AV1AV2 Vi(t=0)

10 10 mV

1 2 3 4

Vo+ 10 1 mV

-

10 100 V

Vo

10 10 V

Comparator fails to produce valid logic outputs within T/2 when input falls

into a region that is sufficiently close to the comparator threshold

Vishal Saxena -8-

Comparator Metastability

Reg. Speed Linear Model

Do

Assuming that the input is uniformly

j+1

distributed over VFS, then

Vi BER

1LSB

j

Vo t Vi 0 A V1A V2 expt gm /CL

Vos

Cascade preamp stages (typical flash comparator has 2-3 pre-amp stages)

Use pipelined multi-stage latches; pre-amp can be pipelined too

Vishal Saxena -9-

Charge-Injection and Clock-Feedthrough in Latch

Reg. Speed Linear Model

M5 M6

Vo+ Vo-

Cgs Cgd

CM

M9 jump

CL CL Vo+

M7 M8

Vo-

Charge injection (CI) and clock-feedthrough (CF) introduce CM jump

in Vo+ and Vo-

Dynamic latches are more susceptible to CI and CF errors

Vishal Saxena -10-

Dynamic Offset of a Latch

Reg. Speed Linear Model

Dynamic offset derives from:

Imbalanced CI and CF

Imbalanced load capacitance

Mismatch b/t M7 and M8

Mismatch b/t M5 and M6

+

Vo Clock routing

Vo- 0.5V CM jump

50mV offset

10% imbalance

Dynamic offset is usually the dominant offset error in latches

Vishal Saxena -11-

Typical CMOS Comparator

Reg. Speed Linear Model

VDD

Input-referred latch

M3 M4 M5 M6 offset gets divided by

the gain of PA

Vos

Vo +

V o- Preamp introduces

M1 M2

Vi its own offset (mostly

M9

static due to Vth, W,

M7 M8 and L mismatches)

PA also reduces

VSS

kickback noise

Preamp Latch

Kickback noise disturbs reference voltages, must settle before next sample

Vishal Saxena -12-

Comparator Offset

Reg. Speed Linear Model

VDD

M3 M4 M5 M6

Differential pair mismatch:

2

W

Vos 1

Vos Vth Vov L

Vo+ V o- 2 2 2

W

M1 M2

Vi M9

4

L

M7 M8

g gm5R9

A V1 m1 A V2

VSS gm3 2 gm7R9

Preamp Latch

Vos,34 Vos,56

2 2 2 2

Total input-referred Vos,78 Vos,dyn

Vos Vos,12

2 2

comparator offset: A

2

A

2

A V2

2 2

A V1 A V2

2

V1 V1

Vishal Saxena -13-

Recall: Matching Properties

Reg. Speed Linear Model

Suppose parameter P of two rectangular devices has a mismatch error of P. The

variance of parameter P b/t the two devices is

2

A

P P SP D2 ,

2 2 1st term dominates

WL for small devices

where, W and L are the effective width and length, D is the distance

A Vth2

Threshold : Vth =

2

+ S Vth2D2

WL

2 A 2

Current factor : S 2D2

2

WL

Ref: M. J. M. Pelgrom, et al., Matching properties of MOS transistors, IEEE Journal

of Solid-State Circuits, vol. 24, pp. 1433-1439, issue 5, 1989.

Vishal Saxena -14-

Recall: Device Sizing for Mismatch

Reg. Speed

R

Linear Model

R

1 2

W X X X X X X X X

L

10 identical resistors

L L

R1 RS with std R1 R2 RS 10 10R1 with std R2 ,

W W

10

R2 R j 2 10R12 R2 10R1

2

j1

R2 10R1 1 R1 R 1 1 Spatial

averaging

R2 10R1 10 R1 R A WL

Vishal Saxena -15-

Pre-amp Design

A fully-differential gain-stage

Avoid or use simple CMFB

Pre-amp gain reduces input referred offset due to the latch

Autozeroing techniques for offset storage and reduction

Pre-amp open-loop gain vs tracking bandwidth trade-off

Multiple stages of pre-amp limit bandwidth

Optimum value of stages 2-4

N stages:

N

N

A0 A0

AN

1 j / 0 1 / 2

0

1

A 0N

A N 3dB , 3dB 0 2 1

N

Vishal Saxena -16-

Pre-amp (PA) Autozeroing

2'

M3 M4

1 C Vos Vo+ Vo-

Vi 2'

Vo

M5 M6

2 A

Vi+ M1 M2 Vi-

Finite preamp gain :

VOS , preamp

VOS ,in

A

For the overall comparator :

2V 2V

2V 2

OS , pre

2

OS ,latch

OS ,in

A pre A pre

Vishal Saxena -17-

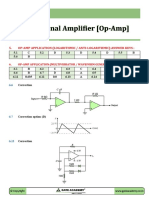

Pre-amp Design: Pull-up load

NMOS diode pull up :

gm1 W L 1

Pull-up AV

gmL W L L

Vo+ Vo-

PMOS diode pull up :

Vi+ M1 M2 Vi- gm1 W L 1

AV n

gmL p W L L

Resistorpull up :

A V gm1 RL

NMOS pull-up suffers from body effect, affecting gain accuracy

PMOS pull-up is free from body effect, but subject to P/N mismatch

Gain accuracy is the worst for resistive pull-up as resistors (poly, diffusion, well,

etc.) dont track transistors; but it is fast!

Vishal Saxena -18-

Pre-amp Design: More Gain

M3 Ip Ip M4

Vo + Vo-

gm1 I 2 W L 1

AV n

gm3 p I 2 Ip W L 3

Vi+ M1 M2 Vi-

Ip diverts current away from PMOS diodes (M3 & M4), reducing (W/L)3

Higher gain without CMFB

Needs biasing for Ip

M3 & M4 may cut off for large Vin, resulting in a slow recovery

Vishal Saxena -19-

Faster Settling Pre-amp

M3 M5 M6 M4 1

ro3

-1

ro5

gm3 gm5

Vo + Vo-

Vid gm1Vid ro1 Vod

Vi+ M1 M2 Vi-

1 1 g r

gm1 // //ro1//ro3 //ro5 m1 o1

dm

DM gain : A V

M7 gm3 gm5 3

NMOS diff-pair loaded with PMOS diodes and a PMOS cross-coupled latch

High DM gain, low CM gain, good CMRR

Simple, no CMFB required

(W/L)34 > (W/L)56 needs to be ensured for stability

Ref: K. Bult and A. Buchwald, An embedded 240-mW 10-b 50-MS/s CMOS ADC in 1-mm2,

JSSC, vol. 32, pp. 1887-1895, issue 12, 1997.

Vishal Saxena -20-

Pre-amp Example

M3 M4

RL RL

+

Vo Vo-

X

Vi+ M1 M2 Vi-

M5

NMOS diff. pair loaded with PMOS diodes and resistors

High DM gain, low CM gain, good CMRR

Simple, no CMFB required

Gain not well-defined

Ref: B.-S. Song et al., A 1 V 6 b 50 MHz current-interpolating CMOS ADC, in Symp. VLSI

Circuits, 1999, pp. 79-80.

Vishal Saxena -21-

Pre-amp Example

NMOS diff. pair loaded with PMOS Current mirror

Simple CMFB circuit

Gain is well-defined

Ref: V. Srinivas, S. Pavan, A. Lachhwani, and N. Sasidhar, A Distortion Compensating Flash

Analog-to-Digital Conversion Technique," IEEE JSSC, vol. 41, no. 9, pp. 1959-1969, Sep.

2006.

Vishal Saxena -22-

Latch Design

Regenerative latches for faster settling

See lecture notes

At least one cross-coupled regenerative core

Local positive feedback

Numerous methods for applying the input initial signal to

regenerate upon

Latches can have large static and dynamic offsets

Large Regenerative gain for resolving small inputs

Metastability (wrong or incomplete decisions) when latch cant

make decision

Pre-amp can be used for amplifying the inputs (slower tracking

BW)

One size doesnt fit all applications

Speed vs power consumption trade-off

Vishal Saxena -23-

Static Latch

Active pull-up and pull-down full

CMOS logic levels

M3 M4

Vi+ Vi- Very fast!

M1 M2

Q+ and Q- are not well defined in reset

mode ( = 1)

Q+ Q- Large short-circuit current in reset mode

M7

Zero DC current after full regeneration

M5 M6 Supply is very noisy

Vishal Saxena -24-

Semi-Dynamic Latch

Diode divider disabled in reset mode

less short-circuit current

M8 Pull-up not as fast

Q+ and Q- are still not well defined in

M3 M4 reset mode ( = 1)

Vi+ Vi-

M1 M2

Zero DC current after full

regeneration

Q+ Q- Supply still very noisy

M7

M5 M6

Vishal Saxena -25-

Dynamic Latch

Zero DC current in reset mode

Q+ and Q- are both reset to 0

M7 M5 M6 M8

Full logic level after

regeneration

Q+ Q-

Slow

M9 M10

Vi+ M1 M3 M4 M2 Vi-

Vishal Saxena -26-

Dynamic Latch 2

M7 M5 M6 M8 Zero DC current in reset

mode

+ -

Q+ and Q- are both reset to

Q Q

0

M9 M10 Full logic level after

regeneration

M3 M4 Slow

Vi+ M1 M2 Vi-

Ref: T. B. Cho and P. R. Gray, A 10 b, 20 Msample/s, 35 mW pipeline A/D converter,

JSSC, vol. 30, pp. 166-172, issue 3, 1995.

Vishal Saxena -27-

Current-Steering/CML Latch

RL RL

Q+ Q-

M7

Current mode logic (CML) latch

Vi+ M1 M2 Vi- M3 M4 Constant current supply very quite

Higher gain in tracking mode

M5 M6

Cannot produce full logic levels

M8

Fast

Popular for high-speed designs

Trip point of the inverters

Vishal Saxena -28-

PA Autozeroing Example

I. Mehr and L. Singer, A 55-mW, 10-bit, 40-Msample/s Nyquist-Rate CMOS ADC, IEEE

JSSC March 2000, pp. 318-25.

Vishal Saxena -29-

Reference Subtraction

S. Pavan, N. Krishnapura, R. Pandarinathan, P. Sankar, "A Power Optimized Continuous-time

Delta-Sigma Modulator for Audio Applications," IEEE JSSC, vol. 43, no. 2, pp. 351-360, Feb.

2008.

Vishal Saxena -30-

Autozeroing and Reference Subtraction

Pre-amp

V. Srinivas, S. Pavan, A. Lachhwani, and N. Sasidhar, A Distortion Compensating Flash

Analog-to-Digital Conversion Technique," IEEE JSSC, vol. 41, no. 9, pp. 1959-1969, Sep.

2006.

Vishal Saxena -31-

CML based Comparator

CML-Latch

V. Singh, N. Krishnapura, S. Pavan, B. Vigraham, D. Behera, and N. Nigania, A 16MHz BW 75

dB DR CT ADC Compensated for More Than One Cycle Excess Loop Delay," IEEE JSSC,

vol. 47, no. 8, Aug. 2012.

Vishal Saxena -32-

Comparators for Pipelined ADCs

Pipelined ADCs employ at least 0.5 bit/stage redundancy

Can tolerate large offsets and large noise with appropriate redundancy

Should consume negligible power in a good design

50-100 mW or less per comparator

Lots of implementation options

Resistive/capacitive reference generation

Different pre-amp/latch topologies

Vishal Saxena -33-

Comparators for Pipelined ADCs

Vishal Saxena -34-

Comparator Example

A 6-b 1.3-Gsample/s A/D Converter in 0.35-m CMOS

IEEE JSSC, vol. 36, no. 12, Dec 2001.

Vishal Saxena -35-

Latch Example

A 0.9-V 60-W 1-Bit Fourth-Order Delta-Sigma Modulator With 83-dB Dynamic Range

IEEE JSSC, vol. 43, no. 2, Feb. 2008

Vishal Saxena -36-

Comparator Example

A 77-dB Dynamic Range, 7.5-MHz Hybrid Continuous-Time/Discrete-Time

Cascaded Modulator, IEEE JSSC, vol. 43, no. 4, Apr 2008

Vishal Saxena -37-

Comparator Example

I. Galdi, 40 MHz IF 1 MHz Bandwidth Two-Path Bandpass Modulator With 72 dB

DR Consuming 16 mW, IEEE JSSC, vol. 39, no. 8, pp. 13411346, Aug. 2004.

Vishal Saxena -38-

Comparator Example

Y. Chiu, P. R. Gray, and B. Nikolic, "A 14-b 12-MS/s CMOS pipeline ADC with over

100-dB SFDR," IEEE JSSC, vol. 39, pp. 2139 - 2151, December 2004.

Vishal Saxena -39-

Comparator Example

B. Min, P. Kim, F. W. Bowman, D. M. Boisvert, and A. J. Aude, "A 69-mW 10-bit

80-MSample/s pipelined CMOS ADC," IEEE JSSC, vol. 38, pp. 2031 - 2039,

Dec. 2003.

Vishal Saxena -40-

Comparator Example

J. Lin and B. Haroun, "An embedded 0.8 V/480 W 6B/22 MHz flash ADC in 0.13

m digital CMOS Process using a nonlinear double interpolation technique," IEEE

JSSC, vol. 37, pp. 1610 - 1617, Dec. 2002.

Vishal Saxena -41-

Comparator Example

S . Limotyrakis, S. D. Kulchycki, D. Su, and B. A. Wooley, "A 150MS/s 8b 71mW

time-interleaved ADC in 0.18m CMOS," proc. IEEE ISSCC, pp. 258 - 259, Feb 2004.

Vishal Saxena -42-

Exercise

Compare the latches with respect to

Static power dissipation

Dynamic and static Offsets

Kickback noise at the input

Number of clock phases

Maximum achievable clock speed

Vishal Saxena -43-

References

1. Rudy van de Plassche, CMOS Integrated Analog-to-Digital and Digital-to-Analog

Converters, 2nd Ed., Springer, 2005.

2. N. Krishnapura, Analog IC Design, IIT Madras, 2008.

3. Y. Chiu, Data Converters Lecture Slides, UT Dallas 2012.

4. B. Boser, Analog-Digital Interface Circuits Lecture Slides, UC Berkeley 2011.

Vishal Saxena -44-

Vous aimerez peut-être aussi

- Comparators 2017Document44 pagesComparators 2017Justin LinPas encore d'évaluation

- Chap 12Document13 pagesChap 12GagnePas encore d'évaluation

- Two Stage CompensationDocument26 pagesTwo Stage CompensationIndranil SarkarPas encore d'évaluation

- CMOS OP AMP Design Techniques and Recent ExamplesDocument42 pagesCMOS OP AMP Design Techniques and Recent ExamplesGagnePas encore d'évaluation

- ECEN474/704: (Analog) VLSI Circuit Design Spring 2018: Lecture 13: Folded Cascode & Two Stage Miller OTADocument25 pagesECEN474/704: (Analog) VLSI Circuit Design Spring 2018: Lecture 13: Folded Cascode & Two Stage Miller OTAUdai ValluruPas encore d'évaluation

- Modeling The DAB Converter - V10Document244 pagesModeling The DAB Converter - V10Fernando Sobrino-Manzanares MasPas encore d'évaluation

- Lecture23 160311 PDFDocument30 pagesLecture23 160311 PDF張唯靖Pas encore d'évaluation

- HVDC Interconnection With VSCDocument32 pagesHVDC Interconnection With VSCRatilal M JadavPas encore d'évaluation

- ELEC 401 Analog CMOS Integrated Circuit Design Design Project: Opamp Design Due: Thursday, December 23, 2021, by 11:59pmDocument3 pagesELEC 401 Analog CMOS Integrated Circuit Design Design Project: Opamp Design Due: Thursday, December 23, 2021, by 11:59pmSteveFarra100% (1)

- INVERTERDocument15 pagesINVERTERAndrea ChiarappaPas encore d'évaluation

- The StrongARM Latch A Circuit For All SeasonsDocument6 pagesThe StrongARM Latch A Circuit For All SeasonsAram ShishmanyanPas encore d'évaluation

- Two Types of MOS Transistors: NMOS and PMOSDocument19 pagesTwo Types of MOS Transistors: NMOS and PMOSRamsPas encore d'évaluation

- Low Voltage Recycling Folded Cascode OTA with Novel CMRR MagnifierDocument6 pagesLow Voltage Recycling Folded Cascode OTA with Novel CMRR MagnifierSudheer RajaPas encore d'évaluation

- 607 Lect 8 Bulk Driven Circuits 2009Document57 pages607 Lect 8 Bulk Driven Circuits 2009Avinash B RajPas encore d'évaluation

- ProposalDocument22 pagesProposalGodfrey ArchibongPas encore d'évaluation

- Space Vector ModulationDocument40 pagesSpace Vector Modulationprasanna_btech06Pas encore d'évaluation

- Differential Amplifiers and Common Mode Feedback Stabilization TechniquesDocument41 pagesDifferential Amplifiers and Common Mode Feedback Stabilization TechniquesSiddharthJainPas encore d'évaluation

- Full Wave Rectifier: Instruction CircuitDocument1 pageFull Wave Rectifier: Instruction CircuitAtharv LokhandePas encore d'évaluation

- Modelling Load Flow and Short Circuit ScenariosDocument4 pagesModelling Load Flow and Short Circuit ScenariosCRISTIAN CAMILO MORALES SOLISPas encore d'évaluation

- Mosfet NotesDocument65 pagesMosfet NotesAnmol DubeyPas encore d'évaluation

- PWM Converters PrinciplesDocument19 pagesPWM Converters Principlesrichfron69Pas encore d'évaluation

- CMOS Analog Circuits: L16: Operational Amplifier-2Document16 pagesCMOS Analog Circuits: L16: Operational Amplifier-2Epili Rajkiran SarabaPas encore d'évaluation

- Lecture14 Ee474 Miller Ota PDFDocument22 pagesLecture14 Ee474 Miller Ota PDFShanPas encore d'évaluation

- Ren 84021 DST 20150923Document20 pagesRen 84021 DST 20150923MOHSENPas encore d'évaluation

- 2stage Op-Amp EE 435 Lab 5 Spring 2014Document2 pages2stage Op-Amp EE 435 Lab 5 Spring 2014Senthil KumarPas encore d'évaluation

- kmz10b 3Document8 pageskmz10b 3Naur AvilaPas encore d'évaluation

- Ipeueukal) :: Dseial GainDocument21 pagesIpeueukal) :: Dseial Gainaditya narayan shuklaPas encore d'évaluation

- 1-V Continuously Tunable CMOS Bulk-Driven Transconductor For G - C FiltersDocument4 pages1-V Continuously Tunable CMOS Bulk-Driven Transconductor For G - C FiltersPrince PhilipPas encore d'évaluation

- 2007 - Performance Characteristics of The Reduced Common Mode Voltage Near State PWM MethodDocument10 pages2007 - Performance Characteristics of The Reduced Common Mode Voltage Near State PWM MethodNguyễn Nhật TưởngPas encore d'évaluation

- The Cross-Coupled Pair-Part Ii: A Circuit For All SeasonsDocument4 pagesThe Cross-Coupled Pair-Part Ii: A Circuit For All Seasonsshatadal chatterjeePas encore d'évaluation

- Assignment 06Document2 pagesAssignment 06Anchal Debnath ee21b017Pas encore d'évaluation

- OTA CMFFDocument27 pagesOTA CMFFakv_vikramPas encore d'évaluation

- Tugas Vlsi: Nama: Fachmy Faizal P. Nim: 201310130311079 Kelas: T. Elektro 6BDocument11 pagesTugas Vlsi: Nama: Fachmy Faizal P. Nim: 201310130311079 Kelas: T. Elektro 6BpavelzaPas encore d'évaluation

- PWM Control of 3phase VsiDocument65 pagesPWM Control of 3phase VsiOm prakashPas encore d'évaluation

- Lecture23 MOS SH 6upDocument3 pagesLecture23 MOS SH 6upnadeemjuttPas encore d'évaluation

- Design of CMOS Low Dropout Voltage RegulatorDocument32 pagesDesign of CMOS Low Dropout Voltage RegulatorDr. Sampatrao L PinjarePas encore d'évaluation

- 607 Lect 12 LDODocument58 pages607 Lect 12 LDOmikeshinoda2011Pas encore d'évaluation

- Half Wave Rectifier - Multisim LiveDocument1 pageHalf Wave Rectifier - Multisim LiveMalhar NityanandPas encore d'évaluation

- Full Wave Rectifier: Instruction CircuitDocument2 pagesFull Wave Rectifier: Instruction CircuitPriyaharshini RaviPas encore d'évaluation

- Mosfet Multi Stage Amplifier DrawingDocument1 pageMosfet Multi Stage Amplifier DrawingMohamed AmirPas encore d'évaluation

- 607 Lect 12 LdoDocument58 pages607 Lect 12 Ldojackal1710Pas encore d'évaluation

- EE539 Analog Integrated Circuit Design Common Mode Feedback CircuitsDocument14 pagesEE539 Analog Integrated Circuit Design Common Mode Feedback CircuitsMostafa M. SamiPas encore d'évaluation

- Short circuit calculations and impedance determinationDocument28 pagesShort circuit calculations and impedance determinationHemo A AlsharifPas encore d'évaluation

- Half Wave Rectifier: Instruction CircuitDocument2 pagesHalf Wave Rectifier: Instruction Circuitsahilsagar 2K20A1470Pas encore d'évaluation

- Differential Amplifiers and Common Mode FeedbackDocument41 pagesDifferential Amplifiers and Common Mode FeedbackChhaya SoniPas encore d'évaluation

- SLA707xM Series: 2-Phase Unipolar Stepper Motor DriverDocument20 pagesSLA707xM Series: 2-Phase Unipolar Stepper Motor DriverKatherine EsperillaPas encore d'évaluation

- CS EE380 Lec03 Expt2Document24 pagesCS EE380 Lec03 Expt2Rajneesh YadavPas encore d'évaluation

- CMOS Analog Circuits: L14: Differential Amplifier-2Document53 pagesCMOS Analog Circuits: L14: Differential Amplifier-2DivijPas encore d'évaluation

- Single Event Transients in Linear Integrated CircuitsDocument80 pagesSingle Event Transients in Linear Integrated CircuitsSaqib Ali KhanPas encore d'évaluation

- 22.power MOSFETDocument35 pages22.power MOSFETArpan ChoudhuryPas encore d'évaluation

- UHMWPE-CNT SonicationDocument247 pagesUHMWPE-CNT SonicationOlivia WinataPas encore d'évaluation

- VLSIDesign-17EC63 M1Document75 pagesVLSIDesign-17EC63 M1veena_scPas encore d'évaluation

- Lecture11 2007Document15 pagesLecture11 2007prabhatpremPas encore d'évaluation

- Graduate Course EE8407: Bin Wu ProfessorDocument40 pagesGraduate Course EE8407: Bin Wu ProfessorDeepan0507Pas encore d'évaluation

- assignment08_a2fbfa33423ddbf5a6efb3d07c98ffddDocument4 pagesassignment08_a2fbfa33423ddbf5a6efb3d07c98ffddshivamshah1910Pas encore d'évaluation

- Diagrama Unifilar: LP-1, LP-2, LP-3 LP-4, LP-5, LP-6Document1 pageDiagrama Unifilar: LP-1, LP-2, LP-3 LP-4, LP-5, LP-6miguel ninoPas encore d'évaluation

- Clippers & Clampers: A Guide to Diode Application CircuitsDocument56 pagesClippers & Clampers: A Guide to Diode Application CircuitsRamya RPas encore d'évaluation

- Design and analysis of MOS differential pair circuitsDocument6 pagesDesign and analysis of MOS differential pair circuitsAnuj JainPas encore d'évaluation

- Elec. Devices Lab Manual 2-1Document98 pagesElec. Devices Lab Manual 2-1Paramesh WaranPas encore d'évaluation

- ELECTRONIC DEVICES AND CIRCUITS LAB MANUALDocument94 pagesELECTRONIC DEVICES AND CIRCUITS LAB MANUALvamshi krishnaPas encore d'évaluation

- DE Lec 33Document12 pagesDE Lec 33Paramesh WaranPas encore d'évaluation

- 1580719993php8g9tQQ PDFDocument7 pages1580719993php8g9tQQ PDFParamesh WaranPas encore d'évaluation

- Digital Communications: Lab Manual (Student Copy)Document78 pagesDigital Communications: Lab Manual (Student Copy)dhileepan DilipPas encore d'évaluation

- 669purl EC GATE 2020 Session (02-02-20)Document33 pages669purl EC GATE 2020 Session (02-02-20)venkatPas encore d'évaluation

- CombinationalDocument9 pagesCombinationalParamesh WaranPas encore d'évaluation

- EDCLABDocument80 pagesEDCLABAmbikaPas encore d'évaluation

- Monday Lab QPDocument6 pagesMonday Lab QPParamesh WaranPas encore d'évaluation

- DE-LEC-Boolean Algebra-1Document19 pagesDE-LEC-Boolean Algebra-1Paramesh WaranPas encore d'évaluation

- Op Amp Application (Logarithmic / Anti Logarithmic) Answer KeysDocument15 pagesOp Amp Application (Logarithmic / Anti Logarithmic) Answer KeysAlpha VictorPas encore d'évaluation

- Op-Amp - Part - 1 Answer + Correction + Sol PDFDocument21 pagesOp-Amp - Part - 1 Answer + Correction + Sol PDFHimanshu guptaPas encore d'évaluation

- Tancet Maths PDFDocument8 pagesTancet Maths PDFParamesh WaranPas encore d'évaluation

- 1580719993php8g9tQQ PDFDocument7 pages1580719993php8g9tQQ PDFParamesh WaranPas encore d'évaluation

- CircuitsDocument474 pagesCircuitsSriramPas encore d'évaluation

- An Energy Efficient Adaptive Sampling Algorithm in A Sensor Network For Automated Water Quality MonitoringDocument14 pagesAn Energy Efficient Adaptive Sampling Algorithm in A Sensor Network For Automated Water Quality MonitoringParamesh WaranPas encore d'évaluation

- Assignment - 1 Basics of VLSI: Submitted By: Name - Roll no.-M.Tech VLSI SystemsDocument5 pagesAssignment - 1 Basics of VLSI: Submitted By: Name - Roll no.-M.Tech VLSI SystemsParamesh WaranPas encore d'évaluation

- Adaptive Sampling With The Ensemble Transform KalmDocument18 pagesAdaptive Sampling With The Ensemble Transform KalmParamesh WaranPas encore d'évaluation

- A-High Frequency Sampling Monitoring System For Environmenal and Structural Applications PartADocument31 pagesA-High Frequency Sampling Monitoring System For Environmenal and Structural Applications PartAParamesh WaranPas encore d'évaluation

- Indian Institute of Information Technology Tiruchirappalli Department of Electronics & Communication EngineeringDocument3 pagesIndian Institute of Information Technology Tiruchirappalli Department of Electronics & Communication EngineeringParamesh WaranPas encore d'évaluation

- DSP AssignmentDocument8 pagesDSP AssignmentParamesh WaranPas encore d'évaluation

- DSP AssignmentDocument2 pagesDSP AssignmentParamesh WaranPas encore d'évaluation

- DFT, FFT, Filter Design and Discrete-Time Systems ProblemsDocument2 pagesDFT, FFT, Filter Design and Discrete-Time Systems ProblemsParamesh WaranPas encore d'évaluation

- DSPWCDocument2 pagesDSPWCParamesh WaranPas encore d'évaluation

- DSP QPDocument54 pagesDSP QPParamesh WaranPas encore d'évaluation

- BlockDocument28 pagesBlockParamesh WaranPas encore d'évaluation

- Indian Institute of Information Technology Tiruchirappalli Department of Electronics & Communication EngineeringDocument2 pagesIndian Institute of Information Technology Tiruchirappalli Department of Electronics & Communication EngineeringParamesh WaranPas encore d'évaluation

- Multi RateDocument4 pagesMulti RateParamesh WaranPas encore d'évaluation

- PassDocument1 pagePassParamesh WaranPas encore d'évaluation

- Performance AppraisalsDocument73 pagesPerformance AppraisalsSaif HassanPas encore d'évaluation

- 3B Adverbial PhrasesDocument1 page3B Adverbial PhrasesSarah IPas encore d'évaluation

- 59-33 ATO Implementation Journal KSA 100Document18 pages59-33 ATO Implementation Journal KSA 100nicolas valentinPas encore d'évaluation

- Chapter 1. Introduction To TCPIP NetworkingDocument15 pagesChapter 1. Introduction To TCPIP NetworkingPoojitha NagarajaPas encore d'évaluation

- Adina CFD FsiDocument481 pagesAdina CFD FsiDaniel GasparinPas encore d'évaluation

- Endocrine Hypothyroidism HyperthyroidismDocument16 pagesEndocrine Hypothyroidism HyperthyroidismJeel MohtaPas encore d'évaluation

- Untitled DocumentDocument2 pagesUntitled DocumentClaudia WinPas encore d'évaluation

- 4 Reasons To Walk With GodDocument2 pages4 Reasons To Walk With GodNoel Kerr CanedaPas encore d'évaluation

- Apostles CreedDocument141 pagesApostles Creedjerome mecca0% (2)

- The City - Populus' As A Self-Governing CorporationDocument24 pagesThe City - Populus' As A Self-Governing Corporation马寅秋Pas encore d'évaluation

- Ad844 PDFDocument20 pagesAd844 PDFkavi_mishra92Pas encore d'évaluation

- Culture of BMWDocument6 pagesCulture of BMWhk246100% (1)

- Logic Puzzles Freebie: Includes Instructions!Document12 pagesLogic Puzzles Freebie: Includes Instructions!api-507836868Pas encore d'évaluation

- 5 - Econ - Advanced Economic Theory (Eng)Document1 page5 - Econ - Advanced Economic Theory (Eng)David JackPas encore d'évaluation

- Week 1 Amanda CeresaDocument2 pagesWeek 1 Amanda CeresaAmanda CeresaPas encore d'évaluation

- Pragmatic Marketing FrameworkDocument2 pagesPragmatic Marketing FrameworkohgenryPas encore d'évaluation

- Vadiyanatha AstakamDocument4 pagesVadiyanatha AstakamRaga MalikaPas encore d'évaluation

- APCHG 2019 ProceedingsDocument69 pagesAPCHG 2019 ProceedingsEnrico SocoPas encore d'évaluation

- Intermediate Reading Comprehension Test 03Document5 pagesIntermediate Reading Comprehension Test 03MZPas encore d'évaluation

- To Sir With LoveDocument2 pagesTo Sir With LoveRamita Udayashankar100% (2)

- G10 ICT Lesson1 - Types and Parts of ComputerDocument4 pagesG10 ICT Lesson1 - Types and Parts of ComputerJOHN RIMMON TAQUISO0% (1)

- The Forty Nine StepsDocument312 pagesThe Forty Nine Stepsoldnic67% (3)

- Source: Sonia S. Daquila. The Seeds of RevolutionDocument6 pagesSource: Sonia S. Daquila. The Seeds of RevolutionJulliena BakersPas encore d'évaluation

- PIC16 F 1619Document594 pagesPIC16 F 1619Francisco Martinez AlemanPas encore d'évaluation

- Skellig - Chapters 16-20 QuestionsDocument1 pageSkellig - Chapters 16-20 Questionselishasantos0% (1)

- Semi-Detailed Lesson Plan Template: Pagsanjan Intergrated National High School 8Document3 pagesSemi-Detailed Lesson Plan Template: Pagsanjan Intergrated National High School 8Mae Ganate RoblesPas encore d'évaluation

- Corporation Law Quiz AnswersDocument3 pagesCorporation Law Quiz AnswerswivadaPas encore d'évaluation

- Aiatsoymeo2016t06 SolutionDocument29 pagesAiatsoymeo2016t06 Solutionsanthosh7kumar-24Pas encore d'évaluation

- Simple Past Tense The Elves and The Shoemaker Short-Story-Learnenglishteam - ComDocument1 pageSimple Past Tense The Elves and The Shoemaker Short-Story-Learnenglishteam - ComgokagokaPas encore d'évaluation

- What's The Line Between Middle Class, Upper Middle Class, and Upper Class in Britain - QuoraDocument11 pagesWhat's The Line Between Middle Class, Upper Middle Class, and Upper Class in Britain - QuoraFaizan ButtPas encore d'évaluation