Académique Documents

Professionnel Documents

Culture Documents

Procesador de Audio APA2172 Main Sony LCD

Transféré par

Antonio ChavezCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Procesador de Audio APA2172 Main Sony LCD

Transféré par

Antonio ChavezDroits d'auteur :

Formats disponibles

APA2172

Stereo, Differential Input Cap-Free Line Driver

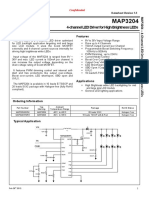

Features General Description

Operating Voltage: 2.3V~5.5V The APA2172 is a stereo, differential input, single supply,

Differential Input and cap-free line driver, which is available in SOP-14 and

Ground Reference Output TSSOP-14 packages.

The APA2172 is ground-reference output, and doesnt

- No Output Capacitor Required (for DC Blocking)

- Save the PCB Space need the output capacitors for DC blocking. The advan-

tages of eliminating the output capacitor are saving the

- Reduce the BOM Costs

cost, eliminating component height, and improving the

- Improve the Low Frequency Response

Low Noise and THD+N

low frequency response.

The external gain setting is recommended using from

- SNR > 108dB

1V/V to 10V/V. High PSRR provides increased immu-

- Noise < 8Vrms

nity to noise and RF rectification. APA2172 has shutdown

- THD+N < 0.02% at 20Hz~20kHz

and under-voltage detector function for Depop solution.

Output Voltage Swing Can Reach 2.1Vrms/Ch into The APA2172 is capable of driving 2.1Vrms at 3.3V into

2.5k at VDD=3.3V 2.5k load, and provides short-circuit and thermal pro-

High PSRR: 80dB at 217Hz tection.

Fast Start-up Time: 500s

Integrate the De-Pop Circuitry

Simplified Application Circuit

Thermal and Short-Circuit Protection

Surface-Mount Packaging

- SOP-14

- TSSOP-14

Lead Free and Green Devices Available

(RoHS Compliant)

Stereo Stereo

Input Signal APA2172 Line-Out

Applications Signal

Set-Top Boxes

CD/DVD Players

LCD TVs

HTIBs (Home Theater in Box)

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and

advise customers to obtain the latest version of relevant information to verify before placing orders.

Copyright ANPEC Electronics Corp. 1 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Pin Configuration

RINP 1 14 LINP RINP 1 14 LINP

RINN 2 13 LINN RINN 2 13 LINN

ROUT 3 12 LOUT ROUT 3 12 LOUT

GND 4 APA2172 11 UVP GND 4 APA2172 11 UVP

SDN 5 10 PGND SDN 5 10 PGND

VSS 6 9 VDD VSS 6 9 VDD

CPN 7 8 CPP CPN 7 8 CPP

TSSOP-14 SOP-14

(Top View) (Top View)

Ordering and Marking Information

APA2172 Package Code

O : TSSOP-14 K : SOP-14

Assembly Material Operating Ambient Temperature Range

I : -40 to 85 oC

Handling Code

Handling Code

Temperature Range TR : Tape & Reel

Assembly Material

Package Code G : Halogen and Lead Free Device

APA2172 XXXXX - Date Code

APA2172 O : XXXXX

APA2172 K : APA2172

XXXXX XXXXX - Date Code

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which

are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for

MSL classification at lead-free peak reflow temperature. ANPEC defines Green to mean lead-free (RoHS compliant) and halogen

free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by

weight).

Absolute Maximum Ratings (Note 1)

Symbol Parameter Rating Unit

VPGND_GND PGND to GND Voltage -0.3 to 0.3

VDD Supply Voltage (VDD to GND and PGND) -0.3 to 6.0

VSDN Input Voltage (SDN to GND) VGND-0.3 to VDD+0.3

VSS VSS to GND and PGND Voltage -6.0 to 0.3 V

VOUT ROUT and LOUT to GND Voltage VSS-0.3 to VDD+0.3

VCPP CPP to PGND Voltage VPGND-0.3 to VDD+0.3

VCPN CPN to PGND Voltage VSS-0.3 to VPGND+0.3

TJ Maximum Junction Temperature 150

o

TSTG Storage Temperature Range -65 to +150 C

TSDR Maximum Soldering Temperature Range, 10 Seconds 260

PD Power Dissipation Internally Limited W

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

Copyright ANPEC Electronics Corp. 2 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Thermal Characteristics

Symbol Parameter Typical Value Unit

(Note 2)

Thermal Resistance - Junction to Ambient

JA

O

TSSOP-14 120 C/W

SOP-14 120

Note 2: Please refer to Thermal Pad Consideration. 2 layered 5 in2 printed circuit boards with 2oz trace and copper through several

thermal vias. The thermal pad is soldered on the PCB.

Recommended Operating Conditions

Range

Symbol Parameter Unit

Min. Max.

VDD Supply Voltage 2.3 5.5

VIH High Level Threshold Voltage SDN 1.0 - V

VIL Low Level Threshold Voltage SDN - 0.35

o

TA Operating Ambient Temperature Range -40 85 C

o

TJ Operating Junction Temperature Range -40 125 C

RL Load Resistance 16 100k

Electrical Characteristics

o

VDD=3.3V, VGND=VPGND=0V, VSDN=VDD, CCPF=CCPO=1F, Ci=1F, RL=2.5k, TA=25 C, Ri=10k, Rf=20k (unless other-

wise noted)

APA2172

Symbol Parameter Test Conditions Unit

Min. Typ. Max.

IDD VDD Supply Current - 10 15 mA

ISD VDD Shutdown Current VSDN=0V - 1 5 A

Il Input Current SDN - 0.1 - A

CHARGE PUMP

fOSC Switching Frequency 400 500 600 kHz

Req Equivalent Resistance - 21 25

DRIVERS

AVO Open Loop Voltage Gain 80 100 - dB

GW Unity Gain Bandwidth 8 10 - MHz

VSR Slew Rate - 4.5 - V/s

VOS Output Offset Voltage VDD=2.3V to 5.5V, RL = 2.5k -5 - 5 mV

VN Output Noise Ri=10k, Rf=10k - 8 15 Vrms

Tstart-up Start-up Time - 500 - s

VDD=2.3V to 5.5V, Vrr=200mVrms

fin= 217Hz -80 -60

PSRR Power Supply Rejection Ratio - dB

fin= 1kHz -80 -60

fin= 20kHz -50 -45

CL Maximum Capacitive Load - 220 - pF

VESD ESD Protection OUTR, OUTL - 8 - kV

Copyright ANPEC Electronics Corp. 3 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Electrical Characteristics (Cont.)

o

VDD=3.3V, VGND=VPGND=0V, VSDN=VDD, CCPF=CCPO=1F, Ci=1F, RL=2.5k, TA=25 C, Ri=10k, Rf=20k (unless other-

wise noted)

APA2172

Symbol Parameter Test Conditions Unit

Min. Typ. Max.

THD+N=1%, fin=1kHz

Output Voltage (Stereo, In

VO RL=2.5k 2.0 2.1 - V

Phase)

RL=100k - 2.3

THD+N=1%, fin=1kHz

- 15 -

RL=32

Output Power (Stereo, In

PO mW

Phase)

VDD=5V

THD+N=1%, fin=1kHz - 40 -

RL=32

VO=2Vrms, RL=2.5k

fin=20Hz 0.02 -

-

fin=1kHz 0.001 0.002

Total Harmonic Distortion Plus fin=20kHz 0.02 -

THD+N %

Noise

Po=10mW, RL=32,fin=1kHz - 0.03 -

VDD=5V, Po=30mW, RL=32,

- 0.03 -

fin=1kHz

VO=2Vrms, RL=2.5k

fin=20Hz 100

Crosstalk Channel Separation - - dB

fin=1kHz 100

fin=20kHz 90

VO=2Vrms, RL=2.5k, Ri=10k,

S/N Signal to Noise Ratio Rf=10k, 102 108 - dB

With A-weighting Filter

Thermal Shutdown Protection o

TSD - 150 - C

Temperature

UVP FUNCTION

External Under Voltage

VUVP - 1.25 - V

Detection

External Under Voltage

IHYS - 5.0 - A

Detection Hysteresis Current

Copyright ANPEC Electronics Corp. 4 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Typical Operating Characteristics

THD+N vs. Output Power THD+N vs. Output Power

10 10

In phase

RL=32

Cin=2.2

f=1kHz

Av=2V/V

1 1

THD+N (%)

THD+N (%)

VDD=3.3V

VDD=5V

VDD=3.3V

0.1 VDD=5V 0.1 out phase

RL=32

Cin=2.2

f=1kHz

Av=2V/V

0.01 0.01

0 10 20 30 40 50 60 0 20 40 60 80 100

Output Power (mW) Output Power (mW)

THD+N vs. Output Voltage THD+N vs. Output Voltage

10 10

In phase In phase

RL=600 RL=10k

Cin=2.2 Cin=2.2

1 f=1kHz 1 f=1kHz

Av=2V/V Av=2V/V

THD+N (%)

THD+N (%)

VDD=2.3V VDD=3.3V

VDD=3.3V 0.1

0.1

VDD=2.3V

VDD=5V 0.01

0.01 VDD=5V

0.001

0.001

0 1 2 3 4 0 1 2 3 4

Output Voltage (V) Output Voltage (V)

THD+N vs. Output Voltage THD+N vs. Frequency

10 1

In phase In phase

RL=100k VDD=3.3V

Cin=2.2 RL=32

1 f=1kHz Cin=2.2

Av=2V/V Av=2V/V

0.1

THD+N (%)

THD+N (%)

Po=1mW

0.1

VDD=3.3V

VDD=2.3V

Po=10mW

Po=5mW

0.01

0.01

VDD=5V

0.001

0.002

0 1 2 3 4 20 100 1k 10k 20k

Output Voltage (V) Frequency (Hz)

Copyright ANPEC Electronics Corp. 5 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Typical Operating Characteristics

THD+N vs. Frequency THD+N vs. Frequency

1 1

In phase In phase

VDD=5V VDD=3.3V

RL=32 RL=600

Cin=2.2 Cin=2.2

Av=2V/V Av=2V/V

0.1

0.1

THD+N (%)

THD+N (%)

Po=3mW

Po=15mW Po=30mW 0.01

Vo=1.8Vrms

0.01

0.002 0.001

20 100 1k 10k 20k 20 100 1k 10k 20k

Frequency (Hz) Frequency (Hz)

THD+N vs. Frequency THD+N vs. Frequency

1 1

In phase In phase

VDD=3.3V VDD=3.3V

RL=10k RL=100k

Cin=2.2 Cin=2.2

Av=2V/V Av=2V/V

0.1 0.1

THD+N (%)

THD+N (%)

0.01 0.01

Vo=1.8Vrms Vo=1.8Vrms

0.001 0.001

20 100 1k 10k 20k 20 100 1k 10k 20k

Frequency (Hz) Frequency (Hz)

Frequency Response Frequency Response

+10 +0 +10 +0

-50 -50

+8 +8

Gain Gain -100

-100

+6 +6

Phase(Deg)

Phase(Deg)

Gain(dB)

Gain(dB)

-150 -150

+4 +4

-200 Phase -200

Phase

+2 -250 +2 -250

VDD=3.3V VDD=3.3V

RL=600 RL=10k

+0 Cin=2.2 -300

+0 Cin=2.2 -300

Vo=2Vrms Vo=2Vrms

Av=2V/V -350 Av=2V/V -350

-2 -2

10 100 1k 10k 200k 10 100 1k 10k 200k

Frequency (Hz) Frequency (Hz)

Copyright ANPEC Electronics Corp. 6 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Typical Operating Characteristics (Cont.)

Frequency Response Crosstalk vs. Frequency

+10 +0 -60

VDD=3.3V

-50 RL=600

+8 -70 AV=-1V/V

Gain -100 Ci=1F

+6 -80 VO=1Vrms

Crosstalk (dB)

Phase(Deg)

Gain(dB)

-150

+4 -90

-200

Phase

+2 -250 -100

VDD=3.3V Right to Left

RL=100k

-300

+0 Cin=2.2 -110

Vo=2Vrms

Av=2V/V -350 Left to Right

-2

10 100 1k 10k 200k -120

20 100 1k 20k

Frequency (Hz) Frequency (Hz)

Crosstalk vs. Frequency Output Noise Voltage vs. Frequency

-60 20

VDD=3.3V VDD=3.3V

RL=100k RL=600

-70

Output Noise Voltage (Vrms)

AV=-1V/V AV=-1V/V

Ci=1F 15 Ci=1F

VO=1Vrms A-Weighting

Crosstalk (dB)

-80

Left channel

-90

10 Right channel

-100

Right to Left

5

-110

Left to Right

-120 0

20 100 1k 20k 20 100 1k 20k

Frequency (Hz) Frequency (Hz)

Output Noise Voltage vs. Frequency PSRR vs. Frequency

20 +0

VDD=3.3V VDD=3.3V

Power Supply Rejection Ratio (dB)

RL=100k RL=600

-20 AV=-1V/V

AV=-1V/V

Output Noise Voltage (Vrms)

Ci=1F Ci=1F

15 Vrr=0.2Vpp

A-Weighting -40

Left channel

-60

10

Right channel

Right channel

-80

Left channel

5 -100

0 -120

20 100 1k 20k 20 100 1k 20k

Frequency (Hz) Frequency (Hz)

Copyright ANPEC Electronics Corp. 7 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Typical Operating Characteristics (Cont.)

PSRR vs. Frequency Output Voltage FFT vs. Frequency

+0 +0

VDD=3.3V VDD=3.3V

Power Supply Rejection Ratio (dB)

RL=100k -20 RL=600

-20 AV=-1V/V AV=-1V/V

Output Voltage FFT (dBr)

Ci=1F VO=-60dB to 2Vrms

Vrr=0.2Vpp

-40

-40

-60

-60

Right channel

-80

-80 -100

Left channel

-120

-100

-140

-12020 100 1k 20k 0k 5k 10k 15k 20k

Frequency (Hz) Frequency (Hz)

Supply Current vs. Supply Voltage GSM Power Supply Rejection vs. Frequency

Supply Voltage (dBV)

10 +0

9 AV=-2V/V -25

No Load

8 -50

-75

Supply Current (mA)

7

-100

6 -125

5 +0 -150

Output Voltage (dBV)

4 -25

-50

3

-75

2 -100

1 -125

0 -150

0.0 1.0 2.0 3.0 4.0 5.0 5.5 0 400 800 1.2k 1.6k 2k

Supply Voltage (V) Frequency (Hz)

GSM Power Supply Rejection vs. Time

VDD

V LOUT

2

VROUT

3

CH1: VDD, 500mV/Div, DC, Offset=3.3V

CH2: VLOUT, 20mV/Div, DC

CH3: VROUT, 20mV/Div, DC

TIME:2ms/Div

Copyright ANPEC Electronics Corp. 8 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Operating Waveforms

Output Transient at Power On Output Transient at Power Off

VDD

VDD

1 1

V ROUT VLOUT

2 2

V LOUT VROUT

3 3

CH1: VDD, 1V/Div, DC CH1: VDD, 1V/Div, DC

CH2: VLOUT, 20mV/Div, DC CH2: VLOUT, 20mV/Div, DC

CH3: VROUT, 20mV/Div, DC CH3: VROUT, 20mV/Div, DC

TIME:10ms/Div TIME:2ms/Div

Shutdown Release Shutdown

VSD

VS D

1 1

2 2

VROUT VROUT

3 3

VLOUT VLOUT

CH1: VSD, 1V/Div, DC CH1: VSD, 1V/Div, DC

CH2: VLOUT, 1V/Div, DC CH2: VLOUT, 1V/Div, DC

CH3: VROUT, 1V/Div, DC CH3: VROUT, 1V/Div, DC

TIME:1ms/Div TIME:1ms/Div

Copyright ANPEC Electronics Corp. 9 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Pin Description

PIN

I/O/P FUNCTION

NO. NAME

1 RINP I Right channel non-inverting input.

2 RINN I Right channel inverting input.

3 ROUT O Right channel output.

4 GND P Signal ground.

Shutdown mod control input signal, pull low for shutdown headphone driver. This pin should

5 SDN I

be connect a 100 Protection Resistor.

6 VSS P Headphone driver negative power supply.

7 CPN I/O Charge pump flying capacitor negative connection.

8 CPP I/O Charge pump flying capacitor positive connection.

9 VDD P Supply voltage input.

10 PGND P Power ground.

11 UVP I Under voltage protection input. Floating or Pull H to disable this function.

12 LOUT O Left channel output.

13 LINN I Left channel inverting input.

14 LINP I Left channel non-inverting input.

Block Diagram

RINN

ROUT

RINP

LINP

LOUT

LINN

Under Voltage UVP

Thermal

and Over Detection Circuit

Current

Protection VDD

SDN Shutdown Power CPP

Circuit and Charge

Depop Pump

Circuit

CPN

GND PGND VSS

Copyright ANPEC Electronics Corp. 10 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Typical Application Circuit

Line Driver Amplifier

RFB

1. Inverting

RFB

CIN

1F RIN

R-CH

R-CH RINN

ROUT Output

Input

RINP

System

Power

CIN LINP L-CH

1F RIN LOUT Output

L-CH R1

LINN

Input 3k

Under Voltage UVP

Thermal R2

and Over Detection Circuit R3 1k

Current 50k

Protection VDD

LDO

RSD

Shutdown SDN 100 Power CPP 1F 10F

Shutdown

Control Circuit and Charge

Depop Pump CCPF

Circuit 1F

CPN

GND PGND VSS

CCPO

1F

2. Non-Inverting RFB

RFB

CX

1F RIN

R-CH

RINN

ROUT Output

R-CH RINP

Input

CIN

RX

1F System

CIN Power

1F RX

L-CH LINP L-CH

Input LOUT Output

LINN R1

3k

CX RIN Under Voltage UVP

Thermal R2

1F and Over Detection Circuit R3 1k

Current 50k

Protection VDD

RSD LDO

100 CPP 1F 10F

Shutdown SDN Shutdown Power

Control Circuit and Charge

Depop Pump CCPF

Circuit 1F

CPN

GND PGND VSS

CCPO

1F

Copyright ANPEC Electronics Corp. 11 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Typical Application Circuit (Cont.)

Line Driver Amplifier (Cont.)

3. Differential RFB

RFB

CIN

1F RIN

R-CH

RINN

R-CH ROUT Output

Input RINP

CIN RIN

RFB

1F System

CIN Power

1F RIN RFB

LINP L-CH

L-CH LOUT Output

LINN R1

Input

3k

CIN RIN

Under Voltage UVP

1F Thermal R2

and Over Detection Circuit R3 1k

Current 50k

Protection VDD

RSD LDO

100 CPP 10F

Shutdown SDN Shutdown Power 1F

Control Circuit and Charge

Depop Pump CCPF

Circuit 1F

CPN

GND PGND VSS

CCPO

1F

Second-Order Active Low-Pass Filter

1. Differential

C1

R2

C3

R1 R3 R-CH

RINN

R-CH ROUT Output

Input C2 R3 RINP Cout

R1 C1 C1 220pF

C3 R2

System

Power

C3 C1

R1 R2 R2 C1 Cout

LINP L-CH

L-CH 220pF Output

C2 R3 R1

Input LINN LOUT 3k

R1 R3 C1

C3 Under Voltage UVP

Thermal R2

and Over Detection Circuit R3 1k

Current 50k

Protection VDD

LDO

RSD

100 Power CPP 1F 10F

Shutdown SDN Shutdown

Circuit and Charge

Control Depop Pump CCPF

Circuit 1F

CPN

GND PGND VSS

CCPO

1F

Copyright ANPEC Electronics Corp. 12 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Typical Application Circuit (Cont.)

Second-Order Active Low-Pass Filter

2. Inverting

R2

C1

C3

R1 R3 R-CH

RINN

R-CH ROUT Output

Input C1 RINP Cout

C2 220pF

System

Power

R2

C1

C2 Cout L-CH

LINP

L-CH R1 R3 220pF Output

LINN R1

Input LOUT 3k

C1 UVP

C3 Thermal Under Voltage R2

and Over Detection Circuit R3 1k

Current 50k

Protection VDD

LDO

RSD

100 Power CPP 1F 10F

Shutdown SDN Shutdown

Circuit and Charge

Control Depop Pump CCPF

Circuit 1F

CPN

GND PGND VSS

CCPO

1F

Copyright ANPEC Electronics Corp. 13 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Function Description

Line Driver Operation Shutdown Function

In order to reduce power consumption while not in use,

VDD

the APA2172 contains shutdown controllers to externally

VOUT turn off the amplifier bias circuitry. This shutdown feature

VDD/2 turns the amplifier off when logic low is placed on the

SDN pins for the APA2172. The trigger point between a

logic high is 1.0V and logic low level is 0.35V. It is recom-

GND

mended to switch between ground and the supply volt-

Conventional Line Driver age VDD to provide maximum device performance. By

switching the SDN pins to a low level, the amplifier enters

a low-consumption current circumstance, charge pump

VDD is disabled, and IDD for the APA2172 is in shutdown mode.

In normal operating, the APA2172s SDN pins should be

pulled to a high level to keep the IC out of the shutdown

VOUT

mode. The SDN pins should be tied to a definite voltage

GND

to avoid unwanted circumstance changes.

Under-Voltage Protection

External under voltage detection can be used to shut-

VSS

down the APA2172 before an input device can generate a

pop. The shutdown threshold at the UVP pin is 1.25V.

Cap-free Line Driver

The user selects a resistor divider to obtain the shut-

Figure 1. Cap-free Operation down threshold and hysteresis for the specific application.

The thresholds can be determined as below:

The APA2172s line drivers use a charge pump to invert

VUVP = (1.25-6AxR3) x (R1+R2)/R2

the positive power supply (VDD) to negative power supply

Hysteresis = 5A x R3 x (R1+R2)/R2

(VSS), see figure1. The headphone drivers operate at this

With the condition: R3>>R1//R2

bipolar power supply (VDD and VSS) and the outputs refer-

For example, to obtain VUVP=3.8V and 1V hysteresis, R1=

ence refers to the ground. This feature eliminates the

3k, R2=1k and R3=50k.

output capacitor that is using in conventional single-ended

headphone drive amplifier. Compare with the single

Vsystem

power supply amplifier, the power supply range has al-

most doubled.

R1

Thermal Protection 3k

R3

The thermal protection circuit limits the junction tempera- 50k

UVP Pin

ture of the APA2172. When the junction temperature ex- 1.25V

R2

ceeds TJ=+150OC, a thermal sensor turns off the driver, 1k 6A

allowing the devices to cool. The thermal sensor allows

the driver to start-up after the junction temperature down

about 125OC. The thermal protection is designed with a

25OC hysteresis to lower the average TJ during continu- Figure 2. Under-Voltage Protection

ous thermal overload conditions, increasing lifetime of

the ICs.

Copyright ANPEC Electronics Corp. 14 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Application Information

Using The APA2172 As A Second-Order Filter Input Capacitor, Ci

Several audio DACs used today require an external low- Ci Ri Rf

pass filter to remove out-of-band noise. This is possible

with the APA2172, as it can be used like a standard Op-

erational Amplifier. Several filter topologies can be

implemented, both single-ended and differential. In Fig-

ure 3, a multi-feedback (MFB) with differential input and

single-ended input is shown. Figure 4. Typical Application Circuit

An ac-coupling capacitor to remove dc content from the In the typical application, an input capacitor, Ci, is required

source is shown; it serves to block any dc content from to allow the amplifier to bias the input signal to the proper

the source and lowers the dc-gain to 1, helping reducing DC level for optimum operation. In this case, Ci and the

the output dc-offset to minimum. minimum input impedance Ri from a high-pass filter with

the corner frequency are determined in the following

Inverting Input Differential Input

R2 equation:

R2

Cx

Cx C3 R1 R3 Cy 6pF 1

C3 R1 R3 Cy 6pF In - fc (highpass ) = (4)

In C2 C1 Out

2RiCi

C2 C1 Out Cout

Cout C3 R1 R3 C1 The value of Ci must be considered carefully because it

In + 220pF

220pF

R2

directly affects the low frequency performance of the

Cx+Cy=C1 Cx+Cy=C1 circuit. Ri is the external input resistance that typical value

Cy:internal Capacitance(6pF) Cy:internal Capacitance(6pF)

is 10k and the specification calls for a flat bass re-

Figure 3. Second-Order Active Low-Pass Filter sponse down to 20Hz. Equation is reconfigured as below:

Table 1: Filter Specifications. 1

Ci = (5)

2Rifc(highpass)

High Low

Gain C1 C2 C3 R1 R2 R3

Pass Pass

(V/V) (pF) (pF) (F) (k) (k) (k) When the input resistance variation is considered, the Ci

(Hz) (kHz)

-1 1.6 40 100 680 10 10 10 24 is 0.8F, so a value in the range of 1F to 2.2F would be

chosen. A further consideration for this capacitor is the

-1.5 1.3 40 68 680 15 8.2 12 30

leakage path from the input source through the input net-

-2 1.6 60 33 150 6.8 15 30 47

work (Ri + Rf, Ci) to the load.

-2 1.6 30 47 470 6.8 15 30 43

This leakage current creates a DC offset voltage at the

-3.33 1.2 30 33 470 10 13 43 43 input to the amplifier that reduces useful headroom, es-

-10 1.5 30 22 1000 22 4.7 47 27 pecially in high gain applications. For this reason, a low

leakage tantalum or ceramic capacitor is the best choice.

For Inverting Input, The overall gain is:

When polarized capacitors are used, the negative side of

R2

AV = (1) the capacitor should face the amplifiers input in most

R1

applications because the DC level of the amplifiers in-

The high pass filters cutoff frequency is:

put is held at GND. Please note that it is important to

1

fc(highpass) = (2) confirm the capacitor polarity in the application.

2R1C3

The low pass filters cutoff frequency is: Input Resistor, Ri

1 The gain of the APA2172 is be set by the external input

fc(lowpass) = (3)

2 R2R3C1C2 resistor (Ri) and external feedback resistor (Rf). Please

see the figure 4.

Copyright ANPEC Electronics Corp. 15 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Application Information (Cont.)

Input Resistor, Ri (Cont.) Charge Pump Output Capacitor, CCPO

Rf The output capacitors value affects the power ripple di-

Gain ( A V ) = (6)

Ri rectly at CVSS (VSS). Increasing the value of output capaci-

The external gain setting is recommended using from tor reduces the power ripple. The ESR of output capacitor

-1V/V to -10V/V, and the Ri is in the range from 1k to affects the load transient of CVSS (VSS). Lower ESR and

47k. Its recommended to use 1% tolerance resistor or greater than 1F ceramic capacitor is a recommendation.

better. Keep the input trace as short as possible to limit

the noise injection. Layout Recommendation

The gain is recommended to set -1V/V, and Ri is 10k,

and Rf is 10k.

1.5mm

Feedback Resistor, Rf

0.7mm

Refer the figure 4, the external gain is setting by Ri and Rf;

and the gain setting is recommended using from -1V/V to

1.27mm

-10V/V. The Rf is in the range from 4.7k to 100k. Its

recommended to use 1% tolerance resistor or better.

Power Supply Decoupling, Cs

The APA2172 is a high-performance CMOS audio ampli-

fier that requires adequate power supply decoupling to

ensure the output total harmonic distortion (THD+N) is

as low as possible. Power supply decoupling also pre-

vents the oscillations being caused by long lead length

5.0mm

between the amplifier and the speaker.

The optimum decoupling is achieved by using two differ-

ent types of capacitors that target on different types of SOP-14 Land Pattern Recommendation

noise on the power supply leads. For higher frequency

transients, spikes, or digital hash on the line, a good low

equivalent-series-resistance (ESR) ceramic capacitor,

4.7mm

typically 0.1F, is placed as close as possible to the de-

1.7mm 1.7mm

vice VDD and PVDD lead for the best performance. For

filtering lower frequency noise signals, a large alumi- 0.35mm

num electrolytic capacitor of 10F or greater placed near

the audio power amplifier is recommended.

Charge Pump Flying Capacitor, CCPF

The flying capacitor affects the load transient of the charge

pump. If the capacitors value is too small, then that will 0.65mm

degrade the charge pumps current driver capability and

the performance of line drive amplifier.

Increasing the flying capacitors value will improve the

TSSOP-14 Land Pattern Recommendation

load transient of charge pump. It is recommended using

the low ESR ceramic capacitors (X7R type is recommend-

ed) above 1F.

Copyright ANPEC Electronics Corp. 16 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Package Information

TSSOP-14

D

SEE VIEW A

E1

e b E

c

0.25

A2

GAUGE PLANE

SEATING PLANE

A1

VIEW A L

S TSSOP-14

Y

M MILLIMETERS INCHES

B

O

L MIN. MAX. MIN. MAX.

A 1.20 0.047

A1 0.05 0.15 0.002 0.006

A2 0.80 1.05 0.031 0.041

b 0.19 0.30 0.007 0.012

c 0.09 0.20 0.004 0.008

D 4.90 5.10 0.193 0.201

E 6.20 6.60 0.244 0.260

E1 4.30 4.50 0.169 0.177

e 0.65 BSC 0.026 BSC

L 0.45 0.75 0.018 0.030

0 0 8 0 8

Note : 1. Follow from JEDEC MO-153 AB-1.

2. Dimension "D" does not include mold flash, protrusions

or gate burrs. Mold flash, protrusion or gate burrs shall not

exceed 6 mil per side.

3. Dimension "E1" does not include inter-lead flash or protrusions.

Inter-lead flash and protrusions shall not exceed 10 mil per side.

Copyright ANPEC Electronics Corp. 17 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Package Information

SOP-14

SEE VIEW A

E1

E

h X 45

e b c

A2

0.25

GAUGE PLANE

A1

SEATING PLANE

L

VIEW A

S SOP-14

Y

M MILLIMETERS INCHES

B

O

L MIN. MAX. MIN. MAX.

A 1.75 0.069

A1 0.10 0.25 0.004 0.010

A2 1.25 0.049

b 0.31 0.51 0.012 0.020

c 0.17 0.25 0.007 0.010

D 8.55 8.75 0.337 0.344

E 5.80 6.20 0.228 0.244

E1 3.80 4.00 0.150 0.157

e 1.27 BSC 0.050 BSC

h 0.25 0.50 0.010 0.020

L 0.40 1.27 0.016 0.050

0 0 8 0 8

Note: 1. Follow JEDEC MS-012 AB.

2. Dimension D does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion or gate burrs shall not exceed 6 mil per side.

3. Dimension E does not include inter-lead flash or protrusions.

Inter-lead flash and protrusions shall not exceed 10 mil per side.

Copyright ANPEC Electronics Corp. 18 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Carrier Tape & Reel Dimensions

OD0 P0 P2 P1 A

E1

F

W

B0

K0 A0 A

B OD1 B

SECTION A-A

T

SECTION B-B

d

H

A

T1

Application A H T1 C d D W E1 F

16.4+2.00 13.0+0.50

330.02.00 50 MIN. 1.5 MIN. 20.2 MIN. 12.00.30 1.750.10 5.500.10

-0.00 -0.20

TSSOP-14 P0 P1 P2 D0 D1 T A0 B0 K0

1.5+0.10 0.6+0.00

4.000.10 8.000.10 2.000.10 1.5 MIN. 6.400.20 5.200.20 1.600.20

-0.00 -0.40

Application A H T1 C d D W E1 F

16.4+2.00 13.0+0.50

330.02.00 50 MIN. 1.5 MIN. 20.2 MIN. 16.00.30 1.750.10 7.500.10

-0.00 -0.20

SOP-14 P0 P1 P2 D0 D1 T A0 B0 K0

1.5+0.10 0.6+0.00

4.00.10 8.00.10 2.00.10 1.5 MIN. 6.400.20 9.000.20 2.100.20

-0.00 -0.40

(mm)

Devices Per Unit

Package Type Unit Quantity

TSSOP-14 Tape & Reel 2500

SOP-14 Tape & Reel 2500

Copyright ANPEC Electronics Corp. 19 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Taping Direction Information

TSSOP-14

USER DIRECTION OF FEED

SOP-14

USER DIRECTION OF FEED

Copyright ANPEC Electronics Corp. 20 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Classification Profile

Classification Reflow Profiles

Profile Feature Sn-Pb Eutectic Assembly Pb-Free Assembly

Preheat & Soak

100 C 150 C

Temperature min (Tsmin)

150 C 200 C

Temperature max (Tsmax)

60-120 seconds 60-120 seconds

Time (Tsmin to Tsmax) (ts)

Average ramp-up rate

3 C/second max. 3 C/second max.

(Tsmax to TP)

Liquidous temperature (TL) 183 C 217 C

Time at liquidous (tL) 60-150 seconds 60-150 seconds

Peak package body Temperature

See Classification Temp in table 1 See Classification Temp in table 2

(Tp)*

Time (tP)** within 5C of the specified

20** seconds 30** seconds

classification temperature (Tc)

Average ramp-down rate (Tp to Tsmax) 6 C/second max. 6 C/second max.

Time 25C to peak temperature 6 minutes max. 8 minutes max.

* Tolerance for peak profile Temperature (Tp) is defined as a supplier minimum and a user maximum.

** Tolerance for time at peak profile temperature (tp) is defined as a supplier minimum and a user maximum.

Copyright ANPEC Electronics Corp. 21 www.anpec.com.tw

Rev. A.8 - Aug., 2013

APA2172

Classification Reflow Profiles (Cont.)

Table 1. SnPb Eutectic Process Classification Temperatures (Tc)

3 3

Package Volume mm Volume mm

Thickness <350 350

<2.5 mm 235 C 220 C

2.5 mm 220 C 220 C

Table 2. Pb-free Process Classification Temperatures (Tc)

3 3 3

Package Volume mm Volume mm Volume mm

Thickness <350 350-2000 >2000

<1.6 mm 260 C 260 C 260 C

1.6 mm 2.5 mm 260 C 250 C 245 C

2.5 mm 250 C 245 C 245 C

Reliability Test Program

Test item Method Description

SOLDERABILITY JESD-22, B102 5 Sec, 245C

HOLT JESD-22, A108 1000 Hrs, Bias @ Tj=125C

PCT JESD-22, A102 168 Hrs, 100%RH, 2atm, 121C

TCT JESD-22, A104 500 Cycles, -65C~150C

HBM MIL-STD-883-3015.7 VHBM2KV

MM JESD-22, A115 VMM200V

Latch-Up JESD 78 10ms, 1tr100mA

Customer Service

Anpec Electronics Corp.

Head Office :

No.6, Dusing 1st Road, SBIP,

Hsin-Chu, Taiwan

Tel : 886-3-5642000

Fax : 886-3-5642050

Taipei Branch :

2F, No. 11, Lane 218, Sec 2 Jhongsing Rd.,

Sindian City, Taipei County 23146, Taiwan

Tel : 886-2-2910-3838

Fax : 886-2-2917-3838

Copyright ANPEC Electronics Corp. 22 www.anpec.com.tw

Rev. A.8 - Aug., 2013

Vous aimerez peut-être aussi

- Features General Description: Ultra-Low On-Resistance, 6A Dual Load Switch With Soft StartDocument21 pagesFeatures General Description: Ultra-Low On-Resistance, 6A Dual Load Switch With Soft StartLuis CarlosPas encore d'évaluation

- APL3523A: Features General DescriptionDocument21 pagesAPL3523A: Features General DescriptionAkrab MustofaPas encore d'évaluation

- DatasheetDocument21 pagesDatasheetziya tutuPas encore d'évaluation

- Anpec Elec APW7301KAI TRG - C115136Document20 pagesAnpec Elec APW7301KAI TRG - C115136Bawantha Prasad MihirangaPas encore d'évaluation

- APL5607A - 600ma Linear Regulator For DC Fan Speed ControlDocument16 pagesAPL5607A - 600ma Linear Regulator For DC Fan Speed ControlLangllyPas encore d'évaluation

- Apl3533 AnpecDocument21 pagesApl3533 Anpecdeddy anjaPas encore d'évaluation

- General Description Features: High Precision Low Cost MCM Power SwitchDocument10 pagesGeneral Description Features: High Precision Low Cost MCM Power SwitchNguyễn TrungPas encore d'évaluation

- Apl5916 AnpecDocument20 pagesApl5916 Anpecايهاب فوزيPas encore d'évaluation

- Multi-Phase PWM Controller For CPU Core Power Supply: General Description FeaturesDocument22 pagesMulti-Phase PWM Controller For CPU Core Power Supply: General Description FeaturesJose SamaPas encore d'évaluation

- AP2132Document12 pagesAP2132Jose Barroso GuerraPas encore d'évaluation

- DS NAU8220 DataSheet EN Rev2.0Document21 pagesDS NAU8220 DataSheet EN Rev2.0Fay AgodoloPas encore d'évaluation

- Features General Description: Stereo 2.6W Audio Amplifier (With Gain Control)Document26 pagesFeatures General Description: Stereo 2.6W Audio Amplifier (With Gain Control)Jaroslaw BielinskiPas encore d'évaluation

- 1581 DatasheetDocument17 pages1581 Datasheettekchan2002Pas encore d'évaluation

- 2A, 18V, 800Khz Synchronous Step-Down Converter: General Description FeaturesDocument15 pages2A, 18V, 800Khz Synchronous Step-Down Converter: General Description FeaturesJose Carlos SoaresPas encore d'évaluation

- 3A, 18V, 700Khz Acot Synchronous Step-Down Converter: Features General DescriptionDocument14 pages3A, 18V, 700Khz Acot Synchronous Step-Down Converter: Features General DescriptionVasil StoyanovPas encore d'évaluation

- ISL6269 Data SheetDocument14 pagesISL6269 Data SheetSummer SpringPas encore d'évaluation

- PAM8610Document15 pagesPAM8610chandraPas encore d'évaluation

- NE/SA/SE5521 LVDT Signal Conditioner: Description Pin ConfigurationsDocument5 pagesNE/SA/SE5521 LVDT Signal Conditioner: Description Pin ConfigurationsAriel SanusiPas encore d'évaluation

- Dual 105 MW Headphone Amplifier: General Description Key SpecificationsDocument18 pagesDual 105 MW Headphone Amplifier: General Description Key Specificationscharly36Pas encore d'évaluation

- Datasheet Ic CE DEDocument15 pagesDatasheet Ic CE DEBersama UkhuwahPas encore d'évaluation

- sp3232 PDFDocument22 pagessp3232 PDFheribertosfaPas encore d'évaluation

- RF LDMOS Wideband Integrated Power Amplifier: MMRF2004NBR1Document19 pagesRF LDMOS Wideband Integrated Power Amplifier: MMRF2004NBR1bulli babuPas encore d'évaluation

- Low EMI 15W Stereo Class D Audio Amplifier: Features General DescriptionDocument14 pagesLow EMI 15W Stereo Class D Audio Amplifier: Features General DescriptionAjay VaishPas encore d'évaluation

- Features Gereral Description: Class AB Stereo Headphone DriverDocument10 pagesFeatures Gereral Description: Class AB Stereo Headphone DriverraveendraPas encore d'évaluation

- Multi-Phase DC/DC Controller For CPU Core Power Supply: General Description FeaturesDocument14 pagesMulti-Phase DC/DC Controller For CPU Core Power Supply: General Description FeaturesTeles SilvaPas encore d'évaluation

- LED Step-Up Converter Drives Up to Five White LEDsDocument9 pagesLED Step-Up Converter Drives Up to Five White LEDsBudi PrayitnoPas encore d'évaluation

- Cost-Effective, 2A Peak Sink/Source Bus Termination RegulatorDocument14 pagesCost-Effective, 2A Peak Sink/Source Bus Termination Regulatoronc3h 112Pas encore d'évaluation

- 4-Channel Led Driver For High Brightness Leds: General Description FeaturesDocument11 pages4-Channel Led Driver For High Brightness Leds: General Description FeaturesTeles SilvaPas encore d'évaluation

- Aca1206 AnadigicsDocument16 pagesAca1206 AnadigicsMike GhanemPas encore d'évaluation

- High Voltage 8-CH LED Driver: Features General DescriptionDocument13 pagesHigh Voltage 8-CH LED Driver: Features General DescriptionSetiawan Abdul RochimPas encore d'évaluation

- Single Synchronous Buck Controller: RT8202L/MDocument19 pagesSingle Synchronous Buck Controller: RT8202L/MDenis DenisovPas encore d'évaluation

- TS04Document18 pagesTS048819133Pas encore d'évaluation

- Dac 8411Document38 pagesDac 8411jsmith012xPas encore d'évaluation

- AD009-041 Remote Controller: 1. General DescriptionsDocument14 pagesAD009-041 Remote Controller: 1. General DescriptionsSuchitel DelmondePas encore d'évaluation

- FT 28Document3 pagesFT 28joako garciaPas encore d'évaluation

- DatasheetDocument15 pagesDatasheetMindSet MarcosPas encore d'évaluation

- Bd9470xxx eDocument38 pagesBd9470xxx eJose GargaglionePas encore d'évaluation

- 4A, 21V, 500Khz Synchronous Step-Down Converter: General DescriptionDocument17 pages4A, 21V, 500Khz Synchronous Step-Down Converter: General DescriptionJose MartinezPas encore d'évaluation

- Rt8816a-06 Gtx1070 Gigabyte MemoriasDocument21 pagesRt8816a-06 Gtx1070 Gigabyte Memoriastechgamebr85Pas encore d'évaluation

- DS8816ADocument21 pagesDS8816AAgustin AyalaPas encore d'évaluation

- Dual-Phase PWM Controller With PWM-VID Reference: General Description FeaturesDocument21 pagesDual-Phase PWM Controller With PWM-VID Reference: General Description FeaturesДмитрий НичипоровичPas encore d'évaluation

- LD 7575Document18 pagesLD 7575Ernesto SandovalPas encore d'évaluation

- ALD1103 Dual N-Channel and Dual P-Channel Matched Mosfet PairDocument9 pagesALD1103 Dual N-Channel and Dual P-Channel Matched Mosfet PairTomás Bautista OrdóñezPas encore d'évaluation

- RT9293Document13 pagesRT9293Bijan AmiriPas encore d'évaluation

- Ds8204a 05Document19 pagesDs8204a 05marcelo Chiu LeonPas encore d'évaluation

- Embedded ASIC Macrocell: Power Management RE028 Fixed 4.5V 30 Ma LDO Voltage RegulatorDocument9 pagesEmbedded ASIC Macrocell: Power Management RE028 Fixed 4.5V 30 Ma LDO Voltage RegulatorHILLPas encore d'évaluation

- Ob 2269 CapDocument13 pagesOb 2269 Caporkun burkayPas encore d'évaluation

- APW8720BDocument22 pagesAPW8720BAlbertPas encore d'évaluation

- As15 FDocument28 pagesAs15 FHamza Abbasi AbbasiPas encore d'évaluation

- RT9018ADocument12 pagesRT9018Abusamawan wayanPas encore d'évaluation

- SP3222E SP3232E SipexDocument20 pagesSP3222E SP3232E SipexZaegor100% (1)

- Features General Description: Low Dropout 600ma Linear Regulator For DC Fan ControlDocument13 pagesFeatures General Description: Low Dropout 600ma Linear Regulator For DC Fan ControlTimuçin İLTERPas encore d'évaluation

- TDI TDO ISP Connector Target Device Target SystemDocument2 pagesTDI TDO ISP Connector Target Device Target SystembrahimPas encore d'évaluation

- Features Description: LTC2368-16 16-Bit, 1Msps, Pseudo-Differential Unipolar SAR ADC With 94.7dB SNRDocument24 pagesFeatures Description: LTC2368-16 16-Bit, 1Msps, Pseudo-Differential Unipolar SAR ADC With 94.7dB SNRrotenolabsPas encore d'évaluation

- Apw 7165 CDocument20 pagesApw 7165 Cterry panPas encore d'évaluation

- NE5230, SA5230, SE5230 Low Voltage Operational Amplifier: PDIP 8 N Suffix CASE 626 SOIC 8 D Suffix CASE 751Document18 pagesNE5230, SA5230, SE5230 Low Voltage Operational Amplifier: PDIP 8 N Suffix CASE 626 SOIC 8 D Suffix CASE 751Marcelo OemPas encore d'évaluation

- CXD1175AM/AP: 8-Bit 20MSPS Video A/D Converter (CMOS)Document21 pagesCXD1175AM/AP: 8-Bit 20MSPS Video A/D Converter (CMOS)raviPas encore d'évaluation

- PLLDocument23 pagesPLLtestzopPas encore d'évaluation

- Sony Cdx-Gt35u Gt39u Gt39ueDocument38 pagesSony Cdx-Gt35u Gt39u Gt39ueShirley Antezana100% (1)

- Comparador Dual Usado en Plasma LG KIA393P - S - F - PDFDocument5 pagesComparador Dual Usado en Plasma LG KIA393P - S - F - PDFAntonio ChavezPas encore d'évaluation

- Configuracion de Cables VariosDocument2 pagesConfiguracion de Cables VariosAntonio ChavezPas encore d'évaluation

- Diagrama de Amplificador TX-SR706Document120 pagesDiagrama de Amplificador TX-SR706Antonio ChavezPas encore d'évaluation

- TLO74CNDocument12 pagesTLO74CNEverson CorreaPas encore d'évaluation

- SMR40000Document2 pagesSMR40000Ramon MartinezPas encore d'évaluation

- Agilent DC Power Supply HandbookDocument126 pagesAgilent DC Power Supply HandbookFrancisco Rodriguez MartinezPas encore d'évaluation

- Manual de Manual de Usuario Autoestereo Kenwood KVT-514Usuario Autoestereo Kenwood KVT-514Document104 pagesManual de Manual de Usuario Autoestereo Kenwood KVT-514Usuario Autoestereo Kenwood KVT-514Antonio ChavezPas encore d'évaluation

- Notes On The Troubleshooting and Repair of Compact Disc Players and CDROM DrivesDocument215 pagesNotes On The Troubleshooting and Repair of Compact Disc Players and CDROM DrivesAntonio ChavezPas encore d'évaluation

- IGBT de Plasma Samsung RJP30E2DPK 360V - 35amp PDFDocument7 pagesIGBT de Plasma Samsung RJP30E2DPK 360V - 35amp PDFAntonio ChavezPas encore d'évaluation

- Aoc l32w831Document13 pagesAoc l32w831Anderson BachPas encore d'évaluation

- Circuito en Fuente TV LCD Mustek N3856VGDocument13 pagesCircuito en Fuente TV LCD Mustek N3856VGAntonio ChavezPas encore d'évaluation

- Diagrama de TV Proyeccion Sony KP-53V90Document120 pagesDiagrama de TV Proyeccion Sony KP-53V90Antonio ChavezPas encore d'évaluation

- LG 32LC4D 32LC45 32LC46 Ld73aDocument28 pagesLG 32LC4D 32LC45 32LC46 Ld73ablownupPas encore d'évaluation

- MP1472 r1.0 PDFDocument13 pagesMP1472 r1.0 PDFAdyel PujolPas encore d'évaluation

- Transistor Fuentes Philips 2SC5344Document4 pagesTransistor Fuentes Philips 2SC5344Antonio ChavezPas encore d'évaluation

- CI Procesador de Audio STV8258DSXDocument157 pagesCI Procesador de Audio STV8258DSXAntonio ChavezPas encore d'évaluation

- 4614 PDFDocument7 pages4614 PDFshafiuddin7326Pas encore d'évaluation

- Regulador de Voltaje Lineal 3.3v G1084-33Document8 pagesRegulador de Voltaje Lineal 3.3v G1084-33Antonio Chavez100% (1)

- Bias Power Supply For TV and Monitor TFT LCD Panels: FeaturesDocument28 pagesBias Power Supply For TV and Monitor TFT LCD Panels: Featuresmitesh12123Pas encore d'évaluation

- TL084Document13 pagesTL084RobertoEulogioChavezRamosPas encore d'évaluation

- MP1472 r1.0 PDFDocument13 pagesMP1472 r1.0 PDFAdyel PujolPas encore d'évaluation

- Oscilador de Fuente TV LCD STR-A6069HDocument13 pagesOscilador de Fuente TV LCD STR-A6069HAntonio ChavezPas encore d'évaluation

- Oscilador de TV Plasma Samsung MC34067P - MC33067PDocument17 pagesOscilador de TV Plasma Samsung MC34067P - MC33067PAntonio ChavezPas encore d'évaluation

- IGBT de Plasma Samsung RJP30E2DPK 360V - 35amp PDFDocument7 pagesIGBT de Plasma Samsung RJP30E2DPK 360V - 35amp PDFAntonio ChavezPas encore d'évaluation

- Mosfet Doble Superficial Canal N 30V 8amp AO4854Document6 pagesMosfet Doble Superficial Canal N 30V 8amp AO4854Antonio ChavezPas encore d'évaluation

- Mosfet Doble Superficial Canal N 30V 8amp AO4854Document6 pagesMosfet Doble Superficial Canal N 30V 8amp AO4854Antonio ChavezPas encore d'évaluation

- UF4001 - UF4007: Fast RectifiersDocument3 pagesUF4001 - UF4007: Fast RectifiersAndré Frota PaivaPas encore d'évaluation

- Oscilador Booster Led Sony BD9397EFVDocument30 pagesOscilador Booster Led Sony BD9397EFVAntonio Chavez100% (1)

- PLC - Modicon m221 - Tm221ce16tDocument18 pagesPLC - Modicon m221 - Tm221ce16tBabeh BabehPas encore d'évaluation

- Balancer and Integrated Hardware ProtectorDocument12 pagesBalancer and Integrated Hardware ProtectorMarian VerdePas encore d'évaluation

- 74LVC1G08 DiodesDocument16 pages74LVC1G08 DiodesRafael Roel Robles BaezPas encore d'évaluation

- TOSHIBA IGBT DatasheetDocument6 pagesTOSHIBA IGBT DatasheetRameshPas encore d'évaluation

- VSM6800+ Serial Monitoring Distribution Amplifier: Installation and Operation ManualDocument46 pagesVSM6800+ Serial Monitoring Distribution Amplifier: Installation and Operation ManualLaurentiu IacobPas encore d'évaluation

- The Specifications of SC6138A: Details PDFDocument1 pageThe Specifications of SC6138A: Details PDFAjay PranPas encore d'évaluation

- Zelio Control RM22UA32MRDocument7 pagesZelio Control RM22UA32MRsreekanth naiduPas encore d'évaluation

- M6700-M6800-M7100-M7200 Series Serivice Manual (V5.15)Document101 pagesM6700-M6800-M7100-M7200 Series Serivice Manual (V5.15)Prakash Prakash APas encore d'évaluation

- P40 Agile: P14N, P14D, P94VDocument8 pagesP40 Agile: P14N, P14D, P94VudhayPas encore d'évaluation

- 1 Cable CleatsDocument20 pages1 Cable CleatsAzam Faiez MokhtarPas encore d'évaluation

- Hotel Room Controllers - HRCPBG28RDocument2 pagesHotel Room Controllers - HRCPBG28RHùng ĐỗPas encore d'évaluation

- Series 8264: Ex D Enclosure System Made of Light Metal or Stainless Steel, "Flameproof Enclosure"Document20 pagesSeries 8264: Ex D Enclosure System Made of Light Metal or Stainless Steel, "Flameproof Enclosure"rifal1990Pas encore d'évaluation

- Vivace KB426 16SDocument2 pagesVivace KB426 16Smedtsl.cppPas encore d'évaluation

- LM 78 L 05Document21 pagesLM 78 L 05peyuco3333Pas encore d'évaluation

- A Global Perspective On E-Waste RecyclingDocument16 pagesA Global Perspective On E-Waste RecyclingĐỗ Xuân HuyPas encore d'évaluation

- Datasheet Sn74ls05nDocument18 pagesDatasheet Sn74ls05nabdelazizlotfy9857Pas encore d'évaluation

- Datasheet vp251Document20 pagesDatasheet vp251Alexandre Da Silva PintoPas encore d'évaluation

- Ves Masina Beko - UputstvoDocument80 pagesVes Masina Beko - Uputstvovlada63Pas encore d'évaluation

- Compra de Productos 1v1Document6 pagesCompra de Productos 1v1amordidas SexShopPas encore d'évaluation

- 1N6267 Fagor PDFDocument8 pages1N6267 Fagor PDFHyacinthe Bertrand RazafindramenaPas encore d'évaluation

- Polylac® Pa-747Document3 pagesPolylac® Pa-747vicentePas encore d'évaluation

- Geforce RTX 2080 Super User GuideDocument29 pagesGeforce RTX 2080 Super User GuideMaher Al AbbasiPas encore d'évaluation

- KT 0936 MB 9Document3 pagesKT 0936 MB 9iaj31582Pas encore d'évaluation

- SJ-20100828173230-003 - NetNumen U31 (V12.10.30) Counters Reference (HSS Volume) - 291256Document144 pagesSJ-20100828173230-003 - NetNumen U31 (V12.10.30) Counters Reference (HSS Volume) - 291256Tawhid AlamPas encore d'évaluation

- Dell Vostro 15 3510 p112f p112f003 European Union - Declaration of Conformity En-UsDocument2 pagesDell Vostro 15 3510 p112f p112f003 European Union - Declaration of Conformity En-UsFederico Giannuzzi0% (1)

- Pressure Switches - Square D™ NEMA - 9013FHG42J59XDocument3 pagesPressure Switches - Square D™ NEMA - 9013FHG42J59XCésar David Pedroza DíazPas encore d'évaluation

- Synchronous 4-Bit Binary CounterDocument17 pagesSynchronous 4-Bit Binary Counteryogendra.shethPas encore d'évaluation

- 76 MTFP50 5 CDocument68 pages76 MTFP50 5 CasPas encore d'évaluation

- Features: Slls115E - October 1980 - Revised October 2007Document27 pagesFeatures: Slls115E - October 1980 - Revised October 2007Iván GissiPas encore d'évaluation

- LEVIS RSL 2010 EnglishDocument48 pagesLEVIS RSL 2010 EnglishHasan SozeriPas encore d'évaluation