Académique Documents

Professionnel Documents

Culture Documents

CH 3 - Logique Séquentielle PDF

Transféré par

Iddir YuderTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

CH 3 - Logique Séquentielle PDF

Transféré par

Iddir YuderDroits d'auteur :

Formats disponibles

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

CHAPITRE III

LOGIQUE SQUENTIELLE

Par :

Khaled Hassine

Khaled.hassine@fsg.rnu.tn

26/10/2016 Khaled Hassine 1 Khaled Hassine

26/10/2016 2

PLAN PLAN

Gnralits Gnralits

Prsentation des bascules Prsentation des bascules

Analyse dun circuit squentiel Analyse dun circuit squentiel

Conception dun circuit squentiel Conception dun circuit squentiel

Les registres et les compteurs Les registres et les compteurs

26/10/2016 Khaled Hassine 3 26/10/2016 Khaled Hassine 4

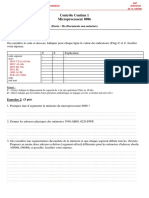

Cours Circuits Logiques 1

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Schma gnral dun circuit

Introduction combinatoire

Les oprateurs que nous avons vus dans le X0 Y0

chapitre prcdent sont des oprateurs X1 Y1

lmentaires dits boolens car ils ralisent les

oprations logiques de l'algbre de Boole. : :

: :

Les circuits construits partir de ces oprateurs

sont dits circuits combinatoires (Combinatory Ym-1

circuit) dont les sorties dpendent uniquement de Xn-1

ltat des entres et l'apparition des donnes

l'entre du circuit entrane le passage de chaque

sortie l'tat dfini par la fonction logique

correspondante.

26/10/2016 Khaled Hassine 5 26/10/2016 Khaled Hassine 6

Notion de mmoire Dfinition dune bascule

Soit un circuit combinatoire permettant de signaler une Une bascule est un oprateur susceptible de :

coupure ou un court-circuit dans un systme de basculer, c'est dire, de changer d'tat sur

production. La sortie du circuit alimente une sonnerie commande

d'alarme par l'intermdiaire d'un amplificateur. Ce

circuit dclenche, le cas chant, la sonnerie d'alarme de conserver le nouvel tat jusqu' l'apparition

pendant la courte dure du court-circuit. d'une nouvelle commande.

Il est donc souhaitable de disposer d'un circuit qui Une bascule est donc une mmoire

conserve l'information (en d'autres termes un circuit lmentaire permettant de sauvegarder un

avec mmoire) afin que la personne concerne (le bit.

gardien par exemple) puisse le dtecter.

Ce circuit est dit fonction mmoire ou fonction

bascule, en rfrence son composant de base.

26/10/2016 Khaled Hassine 7 26/10/2016 Khaled Hassine 8

Cours Circuits Logiques 2

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Gnralits sur les circuits Schma gnral dun circuit

squentiels squentiel

Les oprateurs bascules permettent la ralisation X0

Circuits

Y0

X1 Y1

des circuits squentiels (Sequentials circuits). combinatoires

:

: :

Un circuit squentiel est un assemblage de :

i 0, m 1

circuits logiques et de circuits de mmorisations Xn-1

Ym-1

Yi f i ( X j ,Vk )

pour

j 0, n 1

Z r f r ( X j ,Vk ) k 0, l 1

(les bascules) lmentaires. Z0

r 0, p 1

:

Les circuits squentiels sont des circuits dont les

Zl-1

sorties dpendent non seulement de ltat des V0

Elments

entres mais aussi et surtout de ltat du systme mmoires

Vp-1

aux instants passs.

26/10/2016 Khaled Hassine 9 26/10/2016 Khaled Hassine 10

Circuit synchrone et asynchrone Horloge

Lorsque les changements d'tat des divers composants d'un On associe souvent aux circuits squentiels une entre

circuit squentiel se produisent des instants qui dpendent supplmentaire dite entre d'horloge (dite Clock et not CP).

des temps de rponse des autres composants et des temps Cette horloge fournit une succession priodique d'impulsions de

de propagation des signaux on parle de logique largeur tp, suppose petite devant la priode T. Une telle bascule est

squentielle asynchrone. qualifie de synchrone.

On note Qn la valeur de la sortie Q pendant le nime intervalle

Cependant les retards peuvent ne pas tre identiques pour prcdant la nime impulsion et Qn+1 la valeur correspondante dans

toutes les variables binaires et conduire certains alas. l'intervalle suivant la nime impulsion.

Ceux-ci peuvent tre vits en synchronisant la squence Dans le cas o le circuit serait sans horloge, on dit quil fonctionne

des diverses oprations logiques sur les signaux priodiques en mode asynchrone. L'avantage principal du mode synchrone est

provenant d'une horloge. La logique squentielle est alors d'tre insensible aux parasites en dehors des impulsions d'horloge.

dite synchrone : tous les changements d'tat sont

synchroniss sur un signal de contrle.

26/10/2016 Khaled Hassine 11 26/10/2016 Khaled Hassine 12

Cours Circuits Logiques 3

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Horloge Automates de Moore et de Mealy

Si la conception des circuits combinatoires repose sur

l'algbre de Boole, les circuits squentiels reposent,

quant eux, sur la thorie des automates finis.

Les automates finis sont des tres mathmatiques

composs d'un nombre fini d'lments et notamment

T est de l'ordre de 70 s et le temps de des mmoires.

maintien de l'tat 1 est de l'ordre de 10 s. Il existe principalement deux classes d'automates finis :

l'automate de Moore

l'automate de Mealy.

26/10/2016 Khaled Hassine 13 26/10/2016 Khaled Hassine 14

Automate de Moore Automate de Mealy

Les sorties l'instant t+1 tiennent compte des Les sorties l'instant t+1 tiennent compte des

tats l'instant t+1, c'est dire, on commence tats l'instant t.

par calculer les nouveaux tats et partir de Ceci revient calculer en parallle les

ces derniers, on calcule les sorties. nouveaux tats et les sorties.

Entre Sortie

E ntre E tat d e

L o g iq u e L o g iq u e S o r t ie Logique

c o m b in a t o ir e la u t o m a t e c o m b in a t o ir e

Q combinatoire

Etat de

lautomate

Q

26/10/2016 Khaled Hassine 15 26/10/2016 Khaled Hassine 16

Cours Circuits Logiques 4

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Dfinition et principe de

PLAN fonctionnement

Gnralits Une bascule (flip-flop) a pour rle de

mmoriser une information lmentaire. C'est

une mmoire 1 bit.

Prsentation des bascules

Une bascule possde deux sorties

complmentaires, notes : Q et Q. Ce type

Analyse dun circuit squentiel de circuit est encore appel circuit bistable.

La mmorisation fait appel un verrou (latch)

Conception dun circuit squentiel ou systme de blocage.

Les registres et les compteurs

26/10/2016 Khaled Hassine 17 26/10/2016 Khaled Hassine 18

Principe de verrou dans une

bascule

Diffrents types de

A Q bascules

Bascule RS

Bascule D

Bascule JK

B Q

Bascule T

Ce verrou permet de conserver un tat, il faut maintenant savoir

comment charger cet tat

Bascule matre esclave

26/10/2016 Khaled Hassine 19 26/10/2016 Khaled Hassine 20

Cours Circuits Logiques 5

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Bascule RS

Diffrents types de La bascule RS dispose de deux entres

bascules R : Reset : Mise zro

S : Set : Mise 1

Bascule RS deux sorties Q et Q'.

Bascule D La sortie Q de la porte 1 est rinjecte l'entre de la

Bascule JK porte 2 et inversement.

Bascule T

Bascule matre esclave

26/10/2016 Khaled Hassine 21 26/10/2016 Khaled Hassine 22

Bascule RS Bascule RS Synchrone

S Q

3 1

R Q

S Q

CP

Q Q'

Q 2

S R

R 4

Le fonctionnement de la bascule synchrone dpend de la prsence de l'impulsion d'horloge

(CP) : aussi longtemps que CP est 0, les sorties des portes 3 et 4 restent 1 indiffremment

des variations des entres S et R. Les sorties Q et Q' restent alors inchanges. Une fois CP

passe la valeur 1, les informations venant de S et R peuvent modifier les sorties des portes 1

et 2.

26/10/2016 Khaled Hassine 23 26/10/2016 Khaled Hassine 24

Cours Circuits Logiques 6

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Fonction de la bascule RS Cas ou S=R=1

Si S = 1 et R = 1, l'tat est dit indtermin car on est en

S R Q(t) Q'(t) Q(t+1) Q'(t+1) Observations train de forcer mettre la bascule en mme temps l'tat 1

1 0 0 1 1 0 et l'tat 0.

l'tat Set. "Set for 1" Q peut tre dans ce cas gal Q' et ceci dpend de l'ordre

1 0 1 0 1 0 d'arrive des entres la bascule.

0 1 0 1 0 1 En effet, si on applique S = 1 et R = 0 ou S = 0 et R = 1, on

l'tat Clear impose l'tat de la sortie Q respectivement 1 ou 0,

0 1 1 0 0 1 l'autre sortie prenant la valeur complmentaire. Cet tat se

maintient lorsque les deux entres retournent 0. La

0 0 0 1 0 1

configuration S = R = 1 est proscrire car ici elle impose

sans changement

0 0 1 0 1 0 les deux sorties dans l'tat 0, ce qui est inconsistant

logiquement avec notre dfinition.

26/10/2016 Khaled Hassine 25 26/10/2016 Khaled Hassine 26

Caractristiques de la

bascule RS

Diffrents types de

bascules

S R Qt+1 Commentaire

0 0 Qt Pas de changement

0 1 0 Mise zro (Clear) Bascule RS

1 0 1 Mise 1 (Set)

Bascule D

1 1 ? Etat indtermin

Bascule JK

Q(t 1) R SQ(t ) S R R( S SQ(t )) R( S Q(t )) Bascule T

Bascule matre esclave

26/10/2016 Khaled Hassine 27 26/10/2016 Khaled Hassine 28

Cours Circuits Logiques 7

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Schma de la bascule D

Principe de base asynchrone

La bascule D est obtenue aprs une lgre Q(t) Q(t)

D S D

modification de la bascule RS en insrant un

inverseur entre S et R. Q(t)

Q(t)

R

On interdit ainsi les tats ou S=R et en

particulier ltat indtermin S=R=1.

On appelle lunique entre D.

26/10/2016 Khaled Hassine 29 26/10/2016 Khaled Hassine 30

Caractristiques de la bascule D

Diffrents types de

D S R Qt+1 Commentaire bascules

0 0 1 0 Mise zro

Bascule RS

1 1 0 1 Mise 1

Bascule D

Q(t 1) D Bascule JK

Bascule T

Bascule matre esclave

26/10/2016 Khaled Hassine 31 26/10/2016 Khaled Hassine 32

Cours Circuits Logiques 8

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Principe de base Schma de la bascule JK

La bascule JK est un perfectionnement de la

bascule RS. Le cas indtermin de cette Q(t) Q(t)

S J

J

dernire (S et R gaux 1) est dfini dans la

CP

bascule JK, par une inversion des tats des K R

Q(t) K

Q(t

)

sorties en asservissant les entres R et S aux

sorties

S JQ

R KQ

26/10/2016 Khaled Hassine 33 26/10/2016 Khaled Hassine 34

Table de vrit de la bascule Fonction caractristique de la

JK bascule JK

J K Q(t) S R Q(t+1) Comment Commentaire

0 0 0 0 0 Q(t) Pas de JK 00 01 11 10

Q(t)

0 0 1 0 0 Q(t) changement Q

0 1 0 0 0 Q(t)=0 0 0 0 1 1

0 Mise zro 1 1 0 0 1

0 1 1 0 1 0

1 0 0 1 0 1

1 Mise 1

Q (t 1) J Q KQ

1 0 1 0 0 Q(t)=1

1 1 0 1 0 1

Q(t) tat invers

1 1 1 0 1 0

26/10/2016 Khaled Hassine 35 26/10/2016 Khaled Hassine 36

Cours Circuits Logiques 9

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Principe de base

Diffrents types de Pour une bascule J-K, nous constatons que si

bascules J=K=1, l'tat de la sortie est invers chaque

cycle d'horloge.

Bascule RS La bascule T a une seule entre appele

Bascule D "Trigger" (mot anglais pour dire

Bascule JK dclenchement) est obtenue par connexion des

entres J et K une mme source.

Bascule T Il est pour cela parfois dit la bascule

Bascule matre esclave complment.

26/10/2016 Khaled Hassine 37 26/10/2016 Khaled Hassine 38

Schma et tableau

caractristique de la bascule JK

Diffrents types de

T S

Q(t)

T

Q(t)

bascules

Bascule RS

CP

R

Bascule D

T J K Qt+1 Commentaire

Bascule JK

0 0 0 Qt Pas de changement Bascule T

1 1 1 Q't tat invers Bascule matre esclave

26/10/2016 Khaled Hassine 39 26/10/2016 Khaled Hassine 40

Cours Circuits Logiques 10

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Exemple d'une bascule matre

Composition esclave.

La bascule matre esclave est forme de deux S

Q(t)

S

Q(t)

R

bascules relies la mme horloge mais le top

d'horloge de la premire bascule (le matre) est R Q(t) R Q(t)

S

l'oppos du top d'horloge de la deuxime

CP

bascule (l'esclave).

26/10/2016 Khaled Hassine 41 26/10/2016 Khaled Hassine 42

Fonctionnement Preset et Clear

Le fonctionnement de cette bascule est comme suit : Les entres asynchrones (utiliser en absence

lorsque le top d'horloge est en front montant (=1), il permet

aux donnes de passer de la bascule matre alors que le top de signal d'horloge) Pr (Preset) et Cr (Clear)

d'horloge de la bascule esclave est gale 0, et donc les

donnes ne passent pas la bascule esclave. permettent d'assigner l'tat initial de la

En front descendant de l'horloge (=0), les donnes ne bascule, par exemple la mise sous tension

passent pas au matre mais les sorties de la bascule matre

passe aux entres de l'esclave. pour viter tout ala.

L'objectif est de garantir le passage des informations En fonctionnement normal, ces deux entres

sans transformation ventuelle du un ventuel bruit

ou toute perturbation comme "le problme de course" doivent tre maintenues 1.

(Race problem).

26/10/2016 Khaled Hassine 43 26/10/2016 Khaled Hassine 44

Cours Circuits Logiques 11

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Preset et Clear Table dexcitation des bascules

Les tables caractristiques des bascules spcifient le

prochain tat quand les entres et l'tat actuel sont connus.

Pr Cr Q Or, durant la conception d'un processus (circuit logique),

les tats de transitions (prsent et prochain) sont souvent

1 1 Q connus et ce sont les entres qui sont dterminer pour

assurer la transition voulue.

0 1 0 Pour cette raison, il nous faut une table qui donne les

entres ncessaires pour une transition d'tats donne.

1 0 1 Cette table est dite table d'excitation de la bascule (ou du

circuit combinatoire). Elle est donc constitue de deux

colonnes Qt et Qt+1 et une colonne pour chaque entre. Il y

a quatre transitions (4 lignes) pour aller de Qt Qt+1.

26/10/2016 Khaled Hassine 45 26/10/2016 Khaled Hassine 46

Tables d'excitation des bascules PLAN

Bascule RS Bascule D Bascule JK Bascule T Gnralit

Qt Qt+1 S R D J K T

0 0 0 X 0 0 X 0

Prsentation des bascules

0 1 1 0 1 1 X 1

1 0 0 1 0 X 1 1

1 1 X 0 1 X 0 0 Analyse dun circuit squentiel

Par exemple, pour la bascule J-K, pour obtenir la transition 0 1 il faut

que l'entre J soit dans l'tat 1, quelque soit l'tat de l'entre K. Conception dun circuit squentiel

J = K = 1 qui inverse l'tat de la bascule ou

J = 1 et K = 0 qui charge 1 dans la bascule.

Une croix indique que l'tat de l'entre considre est indiffrent : 0 ou 1. Les registres et les compteurs

26/10/2016 Khaled Hassine 47 26/10/2016 Khaled Hassine 48

Cours Circuits Logiques 12

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Dmarche suivre Premire et deuxime tape

Lanalyse de circuit squentiel (Analysis of Premire tape :

clocked sequential circuits) consiste trouver Trouver les quations caractristiques de chaque

bascule qui montre ltat futur de la bascule en

les quations caractristiques ou les fonction des entres et ltat des autres bascules du

diagrammes temporels qui dcrivent le travail circuit.

du circuit squentiel. Lensemble des quations caractristiques des

diffrentes bascules sappelle quations dtats (State

En dautres termes, trouver les tats futurs et equation).

les sorties du circuit squentiel en fonction de Deuxime tape :

ces entres et ces tats prsents. Trouver les quations des sorties en fonction des

entres et ltat actuel des bascule.

On suit pour une dmarche 4 tapes

26/10/2016 Khaled Hassine 49 26/10/2016 Khaled Hassine 50

Troisime tape Quatrime tape

Trouver la table dtat (dite aussi la table de Trouver le diagramme de transition du

vrit) du circuit qui contient 4 colonnes circuit qui est une autre forme de la table

montrant ltat actuel des bascules, les entres dtat qui permet de faciliter le suivi ltat du

(X1, X2, ..., Xn), les tats futures et les sorties. circuit squentiel et qui contient 2m cercles

reprsentant les diffrents tats possibles des

bascules et on relie entre elles par des liens

Entres Etats prsents Prochains tats Les sorties montrant les conditions de passage dun tat

X1, X2, ..., Xn A1, A2, ..., Am A1, A2, ..., Am Y1, Y2, ..., Yl un autre (les entres suivies de / suivi des

sorties).

26/10/2016 Khaled Hassine 51 26/10/2016 Khaled Hassine 52

Cours Circuits Logiques 13

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Exemple base de bascule D Premire tape : quations

et JK caractristiques des bascules

X Lentre de la bascule A est : DA = B(X+A)

Lentre de la bascule B est : J B X A

D Q

A

Q

K B X

Les quations caractristiques des bascules :

K Q

A(t 1) B ( X A)

B B (t 1) J B KB ( X A) B XB

J Q

( XA X A) B XB XAB X B A XB

Y

XAB X AB XB X ( AB B ) X AB

CP

Deux bascules : la premire A de type D et la deuxime B de type JK X ( A B ) X AB

Une entre X et une sortie Y.

X ( A B) X ( A B) X ( A B)

26/10/2016 Khaled Hassine 53 26/10/2016 Khaled Hassine 54

Troisime tape : table

Deuxime tape dtats du circuit

Lquation caractristique de la sortie A(t) B(t) X A(t+1) B(t+1) Y

Y est : 0 0 0 0 1 1

0 0 1 0 0 0

0 1 0 0 0 0

Y XA (t 1) X B (t 1) 0 1 1 1 1 1

1 0 0 0 0 0

1 0 1 0 1 0

1 1 0 1 0 0

1 1 1 1 1 1

26/10/2016 Khaled Hassine 55 26/10/2016 Khaled Hassine 56

Cours Circuits Logiques 14

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Quatrime tape : Le Exemple base de bascule

diagramme dtats RS

1/0

Q' Q Q' Q

00 0/1

X/Y

A B

0/0

0/0

01 R S R

11 S

1/0 CP

RA SA RB SB

1/1

0/1 1/1

10 X Y

26/10/2016 Khaled Hassine 57 26/10/2016 Khaled Hassine 58

Premire tape : quations Premire tape : quations

caractristiques des bascules caractristiques des bascules

Les entres des bascules : Les quations caractristiques des bascules :

RA X QB QA (t 1) RA ( S A QA (t )) X QB (t )( XQB (t ) QA (t ))

S A XQB ( X QB (t ))( XQB (t ) QA (t )) XQB (t ) XQA (t ) QB (t )QA (t )

X (QB (t ) QA (t )) QB (t )QA (t )

RB X Q A QB (t 1) RB ( S B QB (t ))

S B X Q A XQA (t )( X QA (t ) QB (t ))

XQA (t )QB (t )

26/10/2016 Khaled Hassine 59 26/10/2016 Khaled Hassine 60

Cours Circuits Logiques 15

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Troisime tape : table

Deuxime tape dtats du circuit

QA(t) QB(t) X SA RA QA(t+1) SB RB QB(t+1) Y

Lquation caractristique de la sortie Y est :

0 0 0 0 0 0 0 0 0 0

0 0 1 0 1 0 1 0 1 1

Y X A(t 1)

0 1 0 1 0 1 0 0 1 0

0 1 1 0 0 0 1 0 1 1

1 0 0 0 0 1 0 1 0 0

1 0 1 0 1 0 0 0 0 1

1 1 0 1 0 1 0 1 0 0

1 1 1 0 0 1 0 0 1 0

26/10/2016 Khaled Hassine 61 26/10/2016 Khaled Hassine 62

Quatrime tape : Le

diagramme dtats PLAN

0/0

QAQB

Gnralit

X/Y

00

1/1

1/1

Prsentation des bascules

0/0 01

11

Analyse dun circuit squentiel

1/0 1/1

0/0 Conception dun circuit squentiel

10 0/0

Les registres et les compteurs

26/10/2016 Khaled Hassine 63 26/10/2016 Khaled Hassine 64

Cours Circuits Logiques 16

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Etapes de conception dun circuit

Gnralits squentiel

Lors de la conception dun circuit squentiel, on part du diagramme Comprendre le fonctionnement du circuit et le traduire

dtats ou la table dtats pour obtenir le circuit squentiel ventuellement en un diagramme de transition.

correspondant qui contient deux parties :

une purement combinatoire

Dtermination de la table dtat qui montre les tats futurs

un ensemble de bascule en nombre de log ( N ) (le plus petit entier

2

et les sorties en fonction des entres et des tats prsents.

suprieur ou gal - Least integer greater then or equal) o N est le Rduction du nombre dtats.

nombre dtats diffrents.

Dtermination du nombre de bascules ncessaires et donner

Le type de bascule est dtermin en fonction du fonctionnement du un nom chacune.

circuit et en gnral on choisit :

la bascule T ou JK pour la conception des compteurs, Dtermination du type de bascule et de la table dexcitation

la bascule D pour la conception des registres et mmoire du circuit.

les bascules RS et JK pour les problmes dordre gnral. Dtermination des quations dentres des bascules et des

On prfre toujours lutilisation des bascules T et D pour leurs quations de sortie.

simplicits (ils disposent d'une seule entre). Conception (dessin) du circuit (du logigramme) dsir.

26/10/2016 Khaled Hassine 65 26/10/2016 Khaled Hassine 66

Exemple Table dtats

Etat prsent X Etat suivant Y

Concevoir le circuit squentiel du diagramme suivant : a 0 a 0

0/0 a 1 b 1

X/Y b 0 d 0

a

1/0 1/1 b 1 f 0

1/0 b

f c 0 a 0

0/0 c 1 e 1

0/1 1/0 d 0 e 0

0/0 d 1 c 0

e 1/1

c e 0 f 1

0/1 e 1 f 0

1/0 f 0 e 1

0/0 d f 1 a 0

26/10/2016 Khaled Hassine 67 26/10/2016 Khaled Hassine 68

Cours Circuits Logiques 17

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Dtermination des bascules Table dexcitation

Etat prsent Etat futur Excitation bascules

Nombres : X Cn Bn An Cn+1 Bn+1 An+1 TC TB TA Y

Le diagramme d'tat comporte 6 tats, il nous faut 0 a 0 0 0 a 0 0 0 0 0 0 0

donc 3 bascules notes C, B et A (C de poids fort et A 1 a 0 0 0 b 0 0 1 0 0 1 1

de poids faible). 0 b 0 0 1 d 0 1 1 0 1 0 0

On dsigne l'tat a par 000 et f par 101. 1 b 0 0 1 f 1 0 1 1 0 0 0

0 c 0 1 0 a 0 0 0 0 1 0 0

Types : 1 c 0 1 0 e 1 0 0 1 1 0 1

On a certainement besoin d'un lment logique qui a 0 d 0 1 1 e 1 0 0 1 1 1 0

la capacit de complmentation. 1 d 0 1 1 c 0 1 0 0 1 1 0

0 e 1 0 0 f 1 0 1 0 0 1 1

Cet lment peut tre l'une de deux bascules T ou JK. 1 e 1 0 0 f 1 0 1 0 0 1 0

On choisit la bascule T, elle est la plus simple 0 f 1 0 1 e 1 0 0 0 0 1 1

puisqu'elle ncessite une seule entre. 1 f 1 0 1 a 0 0 0 1 0 1 0

26/10/2016 Khaled Hassine 69 26/10/2016 Khaled Hassine 70

Equations dentres des bascules quations dentres des bascules

et les quations de sortie et les quations de sortie

Pour les bascules A et B Pour la bascule C et la sortie Y

QBQA 00 01 11 10 QBQA 00 01 11 10 QBQA 00 01 11 10 QBQA 00 01 11 10

XQC XQC XQC XQC

00 0 0 1 0 00 0 0 0 0

00 0 0 1 0 00 0 1 1 1 01 0 0 X X 01 1 1 X X

01 1 1 X X 01 0 0 X X 11 0 1 X X 11 0 0 X X

10 0 1 0 1 10 1 0 0 1

11 1 1 X X 11 0 0 X X

10 1 0 1 0 10 0 0 1 1 TC XQAQB XQAQB XQBQA Y XQC X QC QA

TA XQAQB QC QQ TB QB X QC QA X(QA QB) XQAQB

B A

26/10/2016 Khaled Hassine 71 26/10/2016 Khaled Hassine 72

Cours Circuits Logiques 18

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Conception du circuit PLAN

Gnralit

Y X QC QB X QC Q A

Prsentation des bascules

T A X Q A QB QC QB QC QB Q A

TB QB QC X QC Q A Analyse dun circuit squentiel

TC XQ A QB QC QB (Q A X )

Conception dun circuit squentiel

Les registres et les compteurs

26/10/2016 Khaled Hassine 73 26/10/2016 Khaled Hassine 74

Dfinition dun registre Dfinition dun compteur

Les informations et les rsultats intermdiaires manipuls Un compteur est un registre qui change d'tat

par l'unit centrale sont rangs dans des dispositifs squentiellement sous l'effet d'une impulsion

(modules de mmorisation internes au processeur) appels

registres. d'entre.

Ces derniers reprsentent l'unit de base manipule par Cette impulsion peut provenir d'un gnrateur

l'unit centrale. En particulier, aucune opration ne se fait d'impulsions (Clock Pulse) ou d'une autre source

directement sur les cellules mmoire. Celles-ci sont externe, des intervalles de temps rguliers ou

recopies dans des registres avant d'tre traites par le alatoirement.

processeur.

Les registres permettent, en effet, de ranger les instructions, Les compteurs sont trs utiles dans un ordinateur,

les adresses, les donnes ou les rsultats issus de l'unit de en particulier pour le squencement des

traitement. Un cas particulier des registres est le compteur. instructions excutes.

26/10/2016 Khaled Hassine 75 26/10/2016 Khaled Hassine 76

Cours Circuits Logiques 19

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Conception dun compteur binaire

synchrone

On souhaite concevoir un compteur binaire 3

Exemples bits qui compte donc de 0 7. Cest un

compteur complet.

Conception dun compteur

On dispose pour ce faire, de trois bascules A0,

Conception dun dcompteur

A1, A2 (A0 est celle de poids faible).

Conception dun registre

26/10/2016 Khaled Hassine 77 26/10/2016 Khaled Hassine 78

Conditions de complmentation

des bascules au prochain compte Observations

Etat prsent (t) Etat futur (t+1)

On a certainement besoin d'un lment logique qui a la

A2 A1 A0 A2 A1 A0 capacit de complmentation. Cet lment peut tre l'une

0 0 0 0 0 0 1 A0 doit passer de 0 1. de deux bascules T ou JK. On choisit la bascule T, elle est

la plus simple puisqu'elle ncessite une variable d'entre.

1 0 0 1 0 1 0 A0 et A1 changent d'tat.

Le bit le moins significatif est complment chaque

2 0 1 0 0 1 1 A0 doit passer de 0 1. impulsion d'horloge. L'entre de la bascule contenant le bit

3 0 1 1 1 0 0 Toutes les bascules changent d'tat. de poids faible (A0) doit tre donc maintenu constamment

1.

4 1 0 0 1 0 1 Seule A0 change d'tat.

Chacun des autres bits est complment au prochain top

5 1 0 1 1 1 0 A0 et A1 changent d'tat. d'horloge si tous les bits moins significatifs qui le prcdent

6 1 1 0 1 1 1 A0 doit passer de 0 1. sont l'tat 1. L'entre de la bascule A1 est donc A0 et celle

de A2 est le couple A0 A1 reli par une porte ET.

7 1 1 1 0 0 0 Toutes les bascules changent d'tat.

26/10/2016 Khaled Hassine 79 26/10/2016 Khaled Hassine 80

Cours Circuits Logiques 20

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Table dexcitation Logigramme

Etat prsent (t) Etat futur (t+1) Entre des bascules A1A0 00 01 11 10 A1A0 00 01 11 10

A2 A1 A0 A2 A1 A0 T2 T1 T0 A2 A2

0 0 0 0 0 0 1 0 0 1 0 1 1 0 1

1 1 1 1 1

1 0 0 1 0 1 0 0 1 1

T1 A0 T2 A1 A0

2 0 1 0 0 1 1 0 0 1

Q' Q Q' Q

3 0 1 1 1 0 0 1 1 1 Q' Q

4 1 0 0 1 0 1 0 0 1

5 1 0 1 1 1 0 0 1 1 A2 A1 A0

6 1 1 0 1 1 1 0 0 1 T T T

7 1 1 1 0 0 0 1 1 1 1

CP

26/10/2016 Khaled Hassine 81 26/10/2016 Khaled Hassine 82

Dcompteur

Dans un dcompteur, aussi dit compteur binaire

Exemples rebours (Binary Down Counter), le compte ou le

contenu du compteur est rduit (dcrment) de 1

chaque nouvelle impulsion.

Conception dun compteur

On s'intresse la conception d'un dcompteur 4 bits.

Conception dun dcompteur L'tat de dpart est toutes les bascules 1 (soit 1111= 15).

Conception dun registre Par la suite, chaque nouvelle impulsion, la valeur

numrique contenue dans le dcompteur dcrot.

Ainsi, les tats binaires successifs parcourus sont : 14, 13,

...

26/10/2016 Khaled Hassine 83 26/10/2016 Khaled Hassine 84

Cours Circuits Logiques 21

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Evolution du dcompteur Observations

Etat prsent Etat futur Observations

A3 A2 A1 A0 A3 A2 A1 A0 Comme pour le compteur, on a besoin d'un lment logique

15 1 1 1 1 1 1 1 0 A0 doit passer de 0 1. qui a la capacit de complmentation, soit la bascule T.

14 1 1 1 0 1 1 0 1 A0 et A1 changent d'tat. Le bit le moins significatif est complment chaque

13 1 1 0 1 1 1 0 0 A0 doit passer de 0 1.

12 1 1 0 0 1 0 1 1 Toutes les bascules changent d'tat.

impulsion d'horloge. L'entre de la bascule contenant le bit

11 1 0 1 1 1 0 1 0 Seule A0 change d'tat. de poids faible (A0) doit donc maintenue constamment 1.

10 1 0 1 0 1 0 0 1 A0 et A1 changent d'tat. Chacun des autres bits est complment au prochain top

9 1 0 0 1 1 0 0 0 A0 doit passer de 0 1. d'horloge si tous les bits moins significatifs que lui sont

8 1 0 0 0 0 1 1 1 Toutes les bascules changent d'tat.

7 0 1 1 1 0 1 1 0 A0 doit passer de 0 1.

l'tat 0. L'entre de la bascule A1 est A'0 et celle de A2 et le

6 0 1 1 0 0 1 0 1 A0 et A1 changent d'tat. couple A'0 A'1 reli par une porte ET. L'entre de A3 et le

5 0 1 0 1 0 1 0 0 A0 doit passer de 0 1. couple A'0 A'1A'2 reli par une porte ET.

4 0 1 0 0 0 0 1 1 Toutes les bascules changent d'tat.

3 0 0 1 1 0 0 1 0 Seule A0 change d'tat.

2 0 0 1 0 0 0 0 1 A0 et A1 changent d'tat.

1 0 0 0 1 0 0 0 0 A0 doit passer de 0 1.

0 0 0 0 0 1 1 1 1 Toutes les bascules changent d'tat.

26/10/2016 Khaled Hassine 85 26/10/2016 Khaled Hassine 86

Table dexcitation Equations dentre des bascules

A3 A2 A1 A0 A3 A2 A1 A0 TA3 TA2 TA1 TA0 QBQA 00 01 11 10 QBQA 00 01 11 10

15 1 1 1 1 1 1 1 0 1 QDQC QDQC

14 1 1 1 0 1 1 0 1 1 1

00 1 1 1 1 00 1 1

13 1 1 0 1 1 1 0 0 1

01 1 1 1 1 01 1 1

12 1 1 0 0 1 0 1 1 1 1 1

11 1 0 1 1 1 0 1 0 1 11 1 1 1 1 11 1 1

10 1 0 1 0 1 0 0 1 1 1 10 1 1 1 1 10 1 1

9

8

1

1

0

0

0

0

1

0

1

0

0

1

0

1

0

1 1 1 1

1

1

TA 1 TB Q A

7 0 1 1 1 0 1 1 0 1 QBQA 00 01 11 10 QBQA 00 01 11 10

6 0 1 1 0 0 1 0 1 1 1 QDQC QDQC

5 0 1 0 1 0 1 0 0 1 00 1 00 1

4 0 1 0 0 0 0 1 1 1 1 1

01 1 01

3 0 0 1 1 0 0 1 0 1

11 1 11

2 0 0 1 0 0 0 0 1 1 1

10 1 10 1

1 0 0 0 1 0 0 0 0 1

0 0 0 0 0 1 1 1 1 1 1 1 1

TC QB Q A TD QC QB Q A

26/10/2016 Khaled Hassine 87 26/10/2016 Khaled Hassine 88

Cours Circuits Logiques 22

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Logigramme dun dcompteur Compteur dcompteur

Q' Q Q' Q Q' Q Q' Q

A3 A1 A0

A2

T T T

T

Count

CP

26/10/2016 Khaled Hassine 89 26/10/2016 Khaled Hassine 90

Compteur dcompteur

Exemples

Conception dun compteur

Conception dun dcompteur

Conception dun registre

26/10/2016 Khaled Hassine 91 26/10/2016 Khaled Hassine 92

Cours Circuits Logiques 23

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Schma conceptuel dun

Conception des registres registre

Les oprations possibles effectues sur les registres sont : Horloge

le chargement Mode Entre parallle

Sens

En parallle : tous les bits de l'information sont chargs

Initialisation

simultanment.

En srie : l'information se prsente "bit aprs bit" sur le bit de poids Entre Entre

fort ou celui de poids faible pour tre charge en n cycles d'horloge (n srie srie

est la taille du registre) par dcalages successifs.

le dcalage : un registre capable de dcaler l'information binaire Les diffrentes entres de commande pilotant les registres sont les

qu'il contient, aussi bien gauche qu' droite, est appel registre suivantes :

dcalage ou glissement. Signal de commande ou signal d'horloge.

Mode de fonctionnement (dcalage ou chargement).

Ces oprations sont slectionnes par l'intermdiaire d'une Sens de dcalage (droite ou gauche) ou de chargement (srie ou

commande dite mode. Une fois le mode choisi, la parallle).

commande est synchronise par le signal dHorloge. ventuellement, des mises en conditions initiales telle que la

remise zro du contenu du registre.

26/10/2016 Khaled Hassine 93 26/10/2016 Khaled Hassine 94

Exemple dun registre dcalage 3

Composition dun registre bits

Un registre de taille n bits se compose de n bascules et des portes qui Afin d'obtenir un registre disposant des oprations suivantes : dcalage

rgissent et contrle l'opration de dcalage. droite (DD), dcalage gauche (DG), chargement parallle (ChPa) et pas

Bien que les ordinateurs fonctionnent gnralement en mode parallle de changement (PaCh), il suffit d'utiliser un dcodeur 2x4 permettant de

(chargement de tous les bits en un top d'horloge), ils utilisent aussi les coder ces quatre oprations.

oprations de dcalage pour des oprations particulires (multiplication et Une entre Clear pour la mise zro de toutes les bascules du registre.

division en particulier) qui sont des oprations en srie. Une entre CP de l'horloge de synchronisation.

Considrons titre d'exemple, un registre dcalage 4 bits. On souhaite Une entre srie pour les dcalages droite (SR : Shift Right), connecte la

stocker l'information binaire 1011 par des dcalages successifs droite. bascule la plus gauche (A2) et dont le rle est de supporter le bit insrer

Pour cela, lors d'une opration de dcalage droite.

A chaque impulsion d'horloge CP, un bit est amen par l'entre en srie et en Une entre srie pour le dcalage gauche (SL : Shift Left), connecte la

mme temps le bit le plus droite est extrait de la ligne de sortie en srie. bascule la plus droite (A0) et dont le rle est de supporter le bit insrer lors

d'une opration de dcalage gauche.

Avec la mme impulsion, les autres bits du registre sont dcals droite d'une

position. n lignes de sorties parallles, une par bascule du registre permettant d'extraire

son contenu instantanment, les sorties Q des diffrentes bascules.

Aprs la quatrime impulsion, l'information binaire 1011 est introduite dans le

registre. n lignes d'entres parallles, une par bascule du registre, notes I0, I1, I2,

permettant son ventuel chargement en parallle.

26/10/2016 Khaled Hassine 95 26/10/2016 Khaled Hassine 96

Cours Circuits Logiques 24

Facult des Sciences de Gabes 26/10/2016

Dpartement dinformatique

Q' Q Q' Q Q' Q

A2 A1 A0

D D D

C lear

CP

SR

I2

I1

I0

SL

P aC h DD DG C hP a

F0

26/10/2016

F1 Khaled Hassine 97 26/10/2016 Khaled Hassine 98

D co d eu r 2 x 4

Cours Circuits Logiques 25

Vous aimerez peut-être aussi

- Logique CombinatoireDocument11 pagesLogique CombinatoireAnseea Popescu100% (1)

- 6-2-Logique SéquentielleDocument48 pages6-2-Logique Séquentiellelmons saroutPas encore d'évaluation

- C Compteurs AsynchronesDocument7 pagesC Compteurs AsynchronesTaoufiqBaouchPas encore d'évaluation

- ChapitreiiicircuitssquentielsDocument101 pagesChapitreiiicircuitssquentielsMohamed LadhariPas encore d'évaluation

- Devoir de Synthèse N°1 - Génie Électrique Système de Triage Automatique - 3ème Technique (2011-2012) MR Abdallah RaouafiDocument4 pagesDevoir de Synthèse N°1 - Génie Électrique Système de Triage Automatique - 3ème Technique (2011-2012) MR Abdallah Raouafiibrahim abdelaliPas encore d'évaluation

- Cours LogiqueDocument11 pagesCours LogiqueMohamed Anouar ChakerPas encore d'évaluation

- E C Bascules D 3 Merged FAITDocument9 pagesE C Bascules D 3 Merged FAITMohamed MathématicienPas encore d'évaluation

- Bascule CRDocument5 pagesBascule CRAbdourazak AbouPas encore d'évaluation

- M18 - Logique Combinatoire GE-ESADocument136 pagesM18 - Logique Combinatoire GE-ESAMohammed Amine Kened50% (4)

- Manuel D'activitéDocument192 pagesManuel D'activitéfehmi001100% (1)

- Compte Rendu PLL2 PDFDocument4 pagesCompte Rendu PLL2 PDFSafouane ElPas encore d'évaluation

- Serie 1Document9 pagesSerie 1OMAR ENNAJIPas encore d'évaluation

- 09 C5 RR-Les BasculesDocument14 pages09 C5 RR-Les BasculesRida LaglilPas encore d'évaluation

- Solution Série 1 EDB 2019Document11 pagesSolution Série 1 EDB 2019عمر عمريPas encore d'évaluation

- Corrige TD06Document4 pagesCorrige TD06ulrichsiriacPas encore d'évaluation

- Logique Séquentielle PDFDocument12 pagesLogique Séquentielle PDFMoetez Fellah100% (1)

- Chap 3 Les CompteursDocument10 pagesChap 3 Les CompteursAhmed BelhadjPas encore d'évaluation

- 12.logique Sequentielle EtudiantDocument21 pages12.logique Sequentielle EtudiantAymaniJuventunoPas encore d'évaluation

- Devoir de Synthèse N°1 - Technologie - 3ème Technique (2010-2011) MR Abdallah RaouafiDocument4 pagesDevoir de Synthèse N°1 - Technologie - 3ème Technique (2010-2011) MR Abdallah RaouafiOthman TmarPas encore d'évaluation

- Les Machines A Courant ContinuDocument10 pagesLes Machines A Courant ContinuEpsp MedPas encore d'évaluation

- A22-Opérations D'arithmétique Binaire - v19 - 2Document6 pagesA22-Opérations D'arithmétique Binaire - v19 - 2Rafik Ben AmorPas encore d'évaluation

- Exercice de Logique Sequentielle PDFDocument30 pagesExercice de Logique Sequentielle PDFmohcenPas encore d'évaluation

- Serie Exo AutomatismesDocument8 pagesSerie Exo AutomatismesSalimMalekPas encore d'évaluation

- 02 Logiques SequentiellesDocument8 pages02 Logiques SequentiellesMohamed aziz ben sassiPas encore d'évaluation

- Bascules Exos PDFDocument2 pagesBascules Exos PDFbenhasamPas encore d'évaluation

- E Bascules DDocument4 pagesE Bascules DTaoufiqBaouchPas encore d'évaluation

- Serie D'exercices 4 BASCULES 2021-2022Document3 pagesSerie D'exercices 4 BASCULES 2021-2022Manel AsnicarPas encore d'évaluation

- PDF LogicseqDocument25 pagesPDF LogicseqYassine FalahPas encore d'évaluation

- TP1 LogiqueDocument5 pagesTP1 LogiqueasmaPas encore d'évaluation

- Chapitre 4 SLDocument12 pagesChapitre 4 SLHENSCHEL ShadracPas encore d'évaluation

- Bascul 1Document37 pagesBascul 1Abdou Khadre KarePas encore d'évaluation

- 2008 - 3 - Logique SequentiellerDocument17 pages2008 - 3 - Logique SequentiellerfieeaPas encore d'évaluation

- Les CompteursDocument7 pagesLes CompteursSoufiane AggourPas encore d'évaluation

- 2SI - 04a Logique Combinatoire Approfondissement Cours TDDocument7 pages2SI - 04a Logique Combinatoire Approfondissement Cours TDRamzi TarchouniPas encore d'évaluation

- Devoir de Contrôle N°1 - Génie Électrique LECTEUR DE GLYCEMIE - Bac Technique (2015-2016) MR Lazhar KHELILDocument7 pagesDevoir de Contrôle N°1 - Génie Électrique LECTEUR DE GLYCEMIE - Bac Technique (2015-2016) MR Lazhar KHELILeya meftahPas encore d'évaluation

- EMD0203Document11 pagesEMD0203FouadHbPas encore d'évaluation

- Bascule D: Exercice 1Document4 pagesBascule D: Exercice 1Ziad AicPas encore d'évaluation

- Cours D'électrocinétiqueDocument29 pagesCours D'électrocinétiqueOnanda BouliPas encore d'évaluation

- Registres Et CompteursDocument11 pagesRegistres Et CompteursMaher ZaraiPas encore d'évaluation

- Chap 4 Les Circuits SequentielsDocument17 pagesChap 4 Les Circuits SequentielsKycelle Mbouzeko100% (1)

- TD - Bascules JK-1Document3 pagesTD - Bascules JK-1Ziad AicPas encore d'évaluation

- Devoir de Synthèse N°1 - Génie Électrique Tri de Boitiers - Bac Technique (2014-2015) MR YagoubiDocument8 pagesDevoir de Synthèse N°1 - Génie Électrique Tri de Boitiers - Bac Technique (2014-2015) MR YagoubiFethi BenmassoudePas encore d'évaluation

- Chap 3 Les BasculesDocument20 pagesChap 3 Les BasculesAhmed BelhadjPas encore d'évaluation

- Partie Genie Electrique: Nom: ... Prénom: . . N°: . . 4STDocument4 pagesPartie Genie Electrique: Nom: ... Prénom: . . N°: . . 4STHakim SaidiPas encore d'évaluation

- 07 - Initiation À La Logique SéquentielleDocument12 pages07 - Initiation À La Logique SéquentielleRafiRafiPas encore d'évaluation

- 4.logique SéquentielleDocument22 pages4.logique SéquentiellefatimahamdiPas encore d'évaluation

- 1-Circuit Intégré: 74XX83:: Document Constructeur Des Circuits Intégrés Utilisés Dans Carte de CommandeDocument3 pages1-Circuit Intégré: 74XX83:: Document Constructeur Des Circuits Intégrés Utilisés Dans Carte de CommandeHakim SaidiPas encore d'évaluation

- Suite - Logique Séquentielle (Chapitre 6 - Chapitre 7 - Chapitre 8) - (Les Bascules - Les CompteursDocument15 pagesSuite - Logique Séquentielle (Chapitre 6 - Chapitre 7 - Chapitre 8) - (Les Bascules - Les CompteursFares ChetouhPas encore d'évaluation

- Canbus EnseirbDocument32 pagesCanbus EnseirbalmisPas encore d'évaluation

- CC1-Microprocesseur 8086-2020-2021-7 Janvier 2021Document3 pagesCC1-Microprocesseur 8086-2020-2021-7 Janvier 2021gffPas encore d'évaluation

- Supports4 PapierDocument32 pagesSupports4 PapierDominique MalikPas encore d'évaluation

- PdfjoinerDocument28 pagesPdfjoinerMohamed TalhiOuiPas encore d'évaluation

- Chapitre5 IFT1215 2xDocument35 pagesChapitre5 IFT1215 2xAyouba BoubakariPas encore d'évaluation

- Chapitre 2Document25 pagesChapitre 2Md Idir HocinePas encore d'évaluation

- Rapport de Stage ONCFDocument15 pagesRapport de Stage ONCFSafouane El100% (6)

- Logique Combinatoire Et Séquentielle Dr. Bouchikha HocineDocument4 pagesLogique Combinatoire Et Séquentielle Dr. Bouchikha HocineMohamed AlPas encore d'évaluation

- Cours Fpga PDFDocument63 pagesCours Fpga PDFمحمد الأمير الحازمي100% (1)

- Génie Électrique - Exercices Et Problèmes Corrigés - Les Grandes-1 - NodrmDocument353 pagesGénie Électrique - Exercices Et Problèmes Corrigés - Les Grandes-1 - Nodrmartagnax13Pas encore d'évaluation

- Dafeur AbdelhakrimDocument85 pagesDafeur AbdelhakrimADJE JEAN MARCPas encore d'évaluation

- Le Bus CanDocument32 pagesLe Bus CanDragon1700Pas encore d'évaluation

- Correction TD 2Document4 pagesCorrection TD 2Hicham UiiPas encore d'évaluation

- Chapitre 1 1 Systeme de Numeration Et Codage Des InformationsDocument16 pagesChapitre 1 1 Systeme de Numeration Et Codage Des InformationsIddir YuderPas encore d'évaluation

- Sujet Examen Algo 1 Section A DDocument1 pageSujet Examen Algo 1 Section A DIddir YuderPas encore d'évaluation

- Sujet Examen Algo 1 Section A DDocument1 pageSujet Examen Algo 1 Section A DIddir YuderPas encore d'évaluation

- Chapitre 2 2 Les RegistresDocument5 pagesChapitre 2 2 Les RegistresIddir YuderPas encore d'évaluation

- Chapitre 1 2 Algebre de Boole Et Fonctions LogiquesDocument10 pagesChapitre 1 2 Algebre de Boole Et Fonctions LogiquesMc R-OnePas encore d'évaluation

- Chapitre 2 4 Synthese Des CompteursDocument10 pagesChapitre 2 4 Synthese Des CompteursIddir YuderPas encore d'évaluation

- Chapitre 2 4 Synthese Des CompteursDocument34 pagesChapitre 2 4 Synthese Des CompteursIddir YuderPas encore d'évaluation

- Chapitre 1 1 Systeme de Numeration Et Codage Des InformationsDocument16 pagesChapitre 1 1 Systeme de Numeration Et Codage Des InformationsIddir YuderPas encore d'évaluation

- Chapitre 2 4 Synthese Des CompteursDocument9 pagesChapitre 2 4 Synthese Des CompteursIddir YuderPas encore d'évaluation

- Chapitre 1 2 Algebre de Boole Et Fonctions LogiquesDocument20 pagesChapitre 1 2 Algebre de Boole Et Fonctions LogiquesIddir YuderPas encore d'évaluation

- Dspace CDC AdteDocument25 pagesDspace CDC AdteIddir YuderPas encore d'évaluation

- Chapitre 1 2 Algebre de Boole Et Fonctions LogiquesDocument10 pagesChapitre 1 2 Algebre de Boole Et Fonctions LogiquesMc R-OnePas encore d'évaluation

- Chapitre 2 4 Synthese Des CompteursDocument10 pagesChapitre 2 4 Synthese Des CompteursIddir YuderPas encore d'évaluation

- Chapitre 1 3 Representation Et Simplification Des Fonctions Logiques CombinatoiresDocument11 pagesChapitre 1 3 Representation Et Simplification Des Fonctions Logiques CombinatoiresIddir Yuder100% (1)

- Chapitre 1 2 Algebre de Boole Et Fonctions LogiquesDocument10 pagesChapitre 1 2 Algebre de Boole Et Fonctions LogiquesMc R-OnePas encore d'évaluation

- Tout Sur Les Réseaux Sans Fil - DunodDocument131 pagesTout Sur Les Réseaux Sans Fil - Dunodmajd001Pas encore d'évaluation

- td1 Asd Correction 141128025939 Conversion Gate02 PDFDocument9 pagestd1 Asd Correction 141128025939 Conversion Gate02 PDFIddir YuderPas encore d'évaluation

- Bascule CRDocument5 pagesBascule CRAbdourazak AbouPas encore d'évaluation

- Chapitre 2 4 Synthese Des CompteursDocument10 pagesChapitre 2 4 Synthese Des CompteursIddir YuderPas encore d'évaluation

- RESEAUX Ednum PDFDocument375 pagesRESEAUX Ednum PDFadresserPas encore d'évaluation

- CH 3 - Logique SéquentielleDocument25 pagesCH 3 - Logique SéquentielleIddir YuderPas encore d'évaluation

- Comparatif Entre WordPress Joomla Drupal m4Document8 pagesComparatif Entre WordPress Joomla Drupal m4Iddir YuderPas encore d'évaluation

- Archi OrdiDocument35 pagesArchi OrdiFogape TitiPas encore d'évaluation