Académique Documents

Professionnel Documents

Culture Documents

Informe Previo N 5

Transféré par

GRINGEKOTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Informe Previo N 5

Transféré par

GRINGEKODroits d'auteur :

Formats disponibles

CIRCUITOS DIGITALES I FIEE - UNMSM

UN

CIRCUITOS CODIFICADORES

MS

Y DECODIFICADORES

M

Alumno : Vsquez Cueva Hubert Stalin

Cdigo : 12190033

Profesor : Ing. Oscar Casimiro Pariasca

Curso : Circuitos Digitales I

Semestre : 2014 - I

Hubert Stalin Vsquez Cueva Pgina 1

CIRCUITOS DIGITALES I FIEE - UNMSM

INFORME PREVIO N5

1. Qu es un circuito codificador y un decodificador? Explique

CODIFICADOR

Es un circuito combinacional formado por 2 a la n entradas y n salidas cuya funcin es

tal que cuando una sola entrada adopta un determinado valor lgico (0 o 1 , segn las

propiedades del circuito) las salidas representan en binario el nmero de orden de la

entrada que adopte el valor activo.

Los codificadores comerciales construidos con tecnologa MSI son prioritarios, esto

quiere decir que la combinacin presente a la salida ser la correspondiente a la entrada

activa de mayor valor decimal.

El diseo de un codificador se realiza como el de cualquier circuito combinacional.

DECODIFICADOR

Son circuitos combinacionales de N entradas y un nmero de salidas menor o igual a

2^n. Bsicamente funciona de manera que al aparecer una combinacin binaria en sus

entradas, se activa una sola de sus salidas (no siempre).

Los codificadores realizan la funcin inversa a los codificadores. Un decodificador

selecciona una de las salidas dependiendo de la combinacin binaria presente a la

entrada.

2. Disear un circuito codificador de teclado decimal al cdigo BCD. Un

codificador es un circuito combinacional integrado que tiene hasta 2^n

entradas y n salidas y la funcin que desempea es mostrar en la

salida la combinacin correspondiente al cdigo binario de la entrada

activada.

Se entender mejor con un ejemplo: En una calculadora cuando pulsamos cualquiera

de las diez teclas numricas de una calculadora estamos marcando un nmero decimal,

pero el calculador opera con nmero en binario. Para expresar en binario del 1 al 10,

Hubert Stalin Vsquez Cueva Pgina 2

CIRCUITOS DIGITALES I FIEE - UNMSM

necesitamos al menos cuatro bits, ya que con tres solamente podramos establecer 2^3

=8 combinaciones posibles (es decir del 0 al 7) y no podramos codificar los diez

dgitos necesarios (faltaran el 8 y el 9).

Por tanto emplearemos 4 salidas. Como con 4 salidas (4 bits) tenemos 16

combinaciones y empleamos 10 (del 0 al 9), o bien dejaremos seis combinaciones sin

emplear, o las utilizaremos para codificar cualquier otra funcin representada en alguna

de las teclas de la calculadora (el +, el -, el , el , el = y la ; por ejemplo)

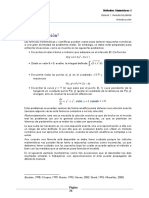

La tabla de verdad del codificador ser:

A partir de la tabla se deduce que la salida S1 ser 1 si lo es la entrada A9, la A7, la

A5, la A3, la A1, de ah que la ecuacin lgica que corresponde a esta salida sea la

suma de las entradas 1, 3, 5, 7 y 9. Si seguimos analizando la tabla obtendremos, de

forma anloga, las ecuaciones que tienen que cumplir las salidas S2, S3 y S4.

En el caso de se activasen ms de una entrada estaramos ante el dilema de qu entrada

debera codificarse?, o se producira una seal de error en la salida, por ello los

codificadores pueden ser sin prioridad, (no suelen emplearse), y los codificadores con

prioridad, generalmente a la entrada ms significativa, en este caso la tabla de verdad

sera:

Hubert Stalin Vsquez Cueva Pgina 3

CIRCUITOS DIGITALES I FIEE - UNMSM

Es decir si por cualquier circunstancia se activase ms de una entrada simultneamente,

el codificador presentar en la salida la correspondiente al cdigo de la entrada que

tenga asignado un mayor peso, es decir la ms significativa, resultando indiferente los

valores que tomasen las otras entradas menos significativas.

En la figura adjunta se muestra el circuito integrado combinacional correspondiente a

un codificador con prioridad de 9 entradas y cuatro salidas.

3. Analizar la operacin del decodificador 74LS47 y su uso con un display

de siete segmentos de nodo comn. Cmo hallara experimentalmente

cada uno de los terminales de un display de siete segmentos de nodo

comn?

Muchas presentaciones numricas en dispositivos de visualizacin utilizan una

configuracin de 7 segmentos para formar los caracteres decimales de 0 a 9 y algunas

veces los caracteres hexadecimales de A a F. Cada segmento est hecho de un material

que emite luz (Display) cuando pasa corriente a travs de l, los patrones de segmentos

que sirven para presentar los diversos dgitos.

El decodificador 7447 est diseado para activar segmentos especficos, aun de

cdigos de entrada mayores que 1001 (9). La figura N 2 muestra las representaciones

para los cdigos desde 0000 hasta 1111. Note que un cdigo de entrada de 1111 borrar

todos los segmentos.

Hubert Stalin Vsquez Cueva Pgina 4

CIRCUITOS DIGITALES I FIEE - UNMSM

Figura N 2. Modelos de segmentos para todos los posibles cdigos de

entrada.

El decodificador BCD a decimal, tiene su tabla de verdad, y es la siguiente:

Los decodificadores pueden ser de dos tipos:

No Excitadores. Se denominan as a un tipo de decodificadores cuyas salidas

solo pueden acoplarse a otros circuitos digitales de la misma familia integrada,

ya que dan una corriente muy pequea en dichas salidas, incapaz de activar

ningn otro componente.

Decodificadores Excitadores. Son aquellos cuyas salidas dan suficiente

corriente como para atacar, no solo a otros circuitos integrados de la misma

familia, sino tambin a otros dispositivos, tales como displays, lmparas, rels,

transductores, etc.

Un decodificador muy comn es el de siete segmentos, este circuito combinacional

activa simultneamente varias salidas, decodifica la informacin de entrada en BCD a

un cdigo de siete segmentos adecuado para que se muestre en un display de siete

segmentos, es el procedimiento empleado en todas las calculadoras, los relojes

digitales, etc.

Hubert Stalin Vsquez Cueva Pgina 5

CIRCUITOS DIGITALES I FIEE - UNMSM

Su tabla de verdad sera:

En las imgenes siguientes puedes ver, qu segmentos estn encendidos en dos

nmeros, el 6 y el 7. En el 7, como indica la tabla de verdad, estn encendidos el a, el b y el

c (encendido quiere decir en este caso valor lgico a 1)

En el 6, estn apagados el a y el b (apagado quiere decir valor lgico a cero)

Hubert Stalin Vsquez Cueva Pgina 6

CIRCUITOS DIGITALES I FIEE - UNMSM

4. Dibuje el diagrama lgico de un decodificador completo de 2 bits.

Repita para un decodificador de 3 bits. Utiliza compuertas lgicas

bsicas y tambin un decodificador comercial. (74155 , 74139 y

74138)

5. El circuito a estudiar es el siguiente:

Hubert Stalin Vsquez Cueva Pgina 7

CIRCUITOS DIGITALES I FIEE - UNMSM

Obtenemos la ecuacin de cada una de las salidas y realizamos su tabla de verdad:

Hubert Stalin Vsquez Cueva Pgina 8

CIRCUITOS DIGITALES I FIEE - UNMSM

Con estas tablas se demuestra el circuito inicialmente analizado.

Para le decodificador de 3 bits, el circuito es el siguiente:

:

6. Analizar la operacin del decodificador 74LS155 como un decodificador

dual 2 x 4 como un decodificador simple de 3 x 8. Verifique el

funcionamiento del CI. 74LS138, CI. 74LS139 y CI. 74LS154

CIRCUITO INTEGRADO TTL 74155 DOBLE DECODIFICADOR

2:4/DEMULTIPLEXOR DE 1:4.

Este circuito integrado contiene dos de multiplexores 1:4, que tambin pueden

funcionar como decodificadores 2 a 4.

La relacin de pines de este integrado es la siguiente:

A y B: entradas de seleccin comunes a los dos demultiplexores activas a nivel alto

(5V).

1G y 2G: entradas de inhibicin o STROBE de los demultiplexores 1 y 2

respectivamente, activas a nivel bajo (0V).

1C y 2C: entradas del dato de los demultiplexores 1 y 2 respectivamente. 1C es activa a

nivel alto (5V) y 2C es activa a nivel bajo (0V).

1Y0, 1Y1, 1Y2, 1Y3: salidas del demultiplexor 1 activas a nivel bajo (0V).

Hubert Stalin Vsquez Cueva Pgina 9

CIRCUITOS DIGITALES I FIEE - UNMSM

2Y0, 2Y1, 2Y2, 2Y3: salidas del demultiplexor 2 activas a nivel bajo (5V).

Con esta lgica en los pines, el dato 1C est invertido en las salidas 1Y0, 1Y1, 1Y2,

1Y3, mientras que el dato 2C no lo est en 2Y0, 2Y1, 2Y2, 2Y3.

La tabla de verdad y el montaje del demultiplexor 1 es la siguiente:

Podemos observar que cuando la entrada del Strobe (1G) est a 0 y la del dato (1C)

est a 1, el demultiplexor 1 se comporta como un decodificador de dos entradas (A y

B) y cuatro salidas activas a nivel bajo.

CIRCUITO INTEGRADO TTL 74138 DECODIFICADOR 3:8/DEMULTIPLEXOR

DE 1:8.

Este circuito integrado contiene un demultiplexor 1:8, que tambin puede funcionar

como decodificador 3 a 8.

La relacin de pines de este integrado es la siguiente:

A , B y C: entradas de seleccin activas a nivel alto (5V).

E3 : entrada de validacin o de dato activa a nivel alto (5V).

E2 y E1: entradas de validacin activas a nivel bajo (0V).

Y0, Y1, Y2, Y3, Y4, Y5, Y6, Y7: salidas del demultiplexor activas a nivel bajo

(0V).

La tabla de verdad y el montaje del demultiplexor es la siguiente:

Hubert Stalin Vsquez Cueva Pgina 10

CIRCUITOS DIGITALES I FIEE - UNMSM

Para que el circuito funcione como demultiplexor la entrada E3 tiene que estar a 1 y

una de las otras dos (E2 E1) a 0. Si E2=0 el dato se introduce por E1 y si E1=0 el

dato se introduce por E2. En ambos casos el dato es activo a nivel bajo al igual que las

salidas.

Para realizar la decodificacin las variables de validacin deben valer E1=0, E2=0 y

E3=1.

Al estar la salida seleccionada a nivel bajo (0V) para visualizar la demultiplexacin

o la decodificacin colocamos el LED de tal manera que se encienda cuando hay 0V

a la salida y se apague con 5V en la salida.

CIRCUITO INTEGRADO TTL 74154 DECODIFICADOR 4:16/DEMULTIPLEXOR

DE 1:16.

Este circuito integrado contiene un demultiplexor 1:16, que tambin puede

funcionar como decodificadores 4 a 16.

La relacin de pines de este integrado es la siguiente:

A, B, C y D: entradas de seleccin activas a nivel alto (5V).

G1 y G2: entradas de validacin o datos activas a nivel bajo (0V).

Y0, Y1, Y2, Y3, Y4, Y5, Y6, Y7, Y8, Y9, Y10, Y11, Y12, Y13, Y14, Y15:

salidas del demultiplexor activas a nivel bajo (0V).

La tabla de verdad y el montaje del demultiplexor es la siguiente:

Hubert Stalin Vsquez Cueva Pgina 11

CIRCUITOS DIGITALES I FIEE - UNMSM

Al estar la salida seleccionada a nivel bajo (0V) para visualizar la demultiplexacin

o la decodificacin colocamos el LED de tal manera que se encienda cuando hay 0V

a la salida y se apague con 5V en la salida.

Podemos observar que cuando las entradas de validacin G1 y G2 estn a 0 (nivel

bajo 0V), las entradas de seleccin marcan la salida activa a nivel bajo (0),

funcionando como un decodificador 4 a 16.

Cuando G1=0, podemos introducir el dato por G2 (activo a nivel bajo 0V) y

obtenerlo en la salida seleccionada por A, B, C y D tambin a nivel bajo (0V). Lo

mismo ocurre si G2 = 0, ahora el dato podemos introducirlo por G1 (activo a nivel

bajo 0V) y obtenerlo en la salida seleccionada por A, B, C y D tambin a nivel bajo

(0V). Este funcionamiento sera como demultiplexor 1:16.

Cuando G1 = G2 = 1, todas las salidas estn inactivas a nivel alto (5V), actuando

G1 y G2 como entradas de inhibicin del circuito integrado.

Hubert Stalin Vsquez Cueva Pgina 12

CIRCUITOS DIGITALES I FIEE - UNMSM

7. En la figura se muestra un circuito decodificador de 5 bits que utiliza

el CI 74HC154. Explicar su funcionamiento. Explique cmo funciona si

el nmero binario es A4A3A2A1A0? Qu resultado obtendremos en

las salidas si la entrada binaria es 10110?

Hubert Stalin Vsquez Cueva Pgina 13

CIRCUITOS DIGITALES I FIEE - UNMSM

El circuito tiene cortocircuitadas sus entradas de habilitacin, pero al segundo

decodificador la habilitacin con respecto al primero es opuesto, es decir, solamente un

decodificador est activo a la vez, por otro lado se tienen 4 bits de entrada y por

consiguiente 16 combinaciones posibles, por lo tanto si aplicamos los datos 10110,

primero notamos que el primer decodificador queda inhabilitado, mientras que el

segundo queda habilitado, la combinacin correspondiente a los bits A3A2A1A0 es

0110 que corresponde a la ubicacin nmero 6, que para el segundo decodificador es la

numero 22, entonces tendremos la activacin(salida 0) del puerto 22 del

decodificador de 5 bits.

8. Un circuito combinacional tiene 3 entradas X, Y, Z y 3 salidas F1, F2,

F3 donde:

9. F1 = XZ +/X /Y /Z F2 = /X Y + X /Y /Z F3 = X Y + /X /Y Z

Nota : /X = X negado, etc, etc.

Implementar con un CI decodificador 74LS155 y compuertas bsicas.

A) F1 = XZ +/X /Y /Z

Hubert Stalin Vsquez Cueva Pgina 14

CIRCUITOS DIGITALES I FIEE - UNMSM

F1 = XYZ+X/YZ+/X/Y/Z

F1 = /((/X+/Y+/Z)(/X+Y+/Z)(X+Y+Z)

B) F2 = /X Y + X /Y /Z

F2 = /XYZ+/XY/Z+X/Y/Z

F2 = /((X+/Y+/Z)(X+/Y+Z)(/X+Y+Z))

C) F3 = X Y + /X /Y Z

F3 = XYZ+XY/Z+/X/YZ

F3 = /((/X+/Y+/Z)( /X+/Y+Z)(X+Y+/Z))

El circuito deseado ser:

10. Disear las siguientes funciones lgicas de una o ms salidas, usando

decodificadores 74LS138 74LS139 binarios y compuertas NAND

(74LS10, 74LS20, 74LS30, etc):

a) Fa = x, y, z (2, 4, 7)

b) Fb = a, b, c, d (2, 4, 6, 14)

Hubert Stalin Vsquez Cueva Pgina 15

CIRCUITOS DIGITALES I FIEE - UNMSM

c) Fc = w, x, y (1, 3, 5, 6) y Gc = w, x, y (2, 3, 4, 7)

d) Fd = w, x, y, z (0, 1, 2, 3, 5, 7, 11, 13)

a) Fa = x, y, z (2, 4, 7)

Como queremos implementar con compuertas NAND tenemos que expresarlo

como Maxterm: Fa = x, y, z (0, 1, 3, 5, 6) pero esta funcin que unida mediante

una puerta AND, para hacer que sea unida por una puerta NAND, tomamos la

funcin negada Maxterm: /Fa = x, y, z (2, 4, 7), como notamos los datos

corresponden a los mismos como si estuviesen en minterm, entonces el circuito es

la siguiente:

b) Fb = a, b, c, d (2, 4, 6, 14)

Entonces procediendo como en el ejercicio anterior, la funcin negada y expresada

como maxterm es la siguiente: /Fb = a, b, c, d (2, 4, 6, 14), la que tambin

quedara unida finalmente con compuerta NAND:

Hubert Stalin Vsquez Cueva Pgina 16

CIRCUITOS DIGITALES I FIEE - UNMSM

c) Fc = w, x, y (1, 3, 5, 6) y Gc = w, x, y (2, 3, 4, 7)

Tomando nuevamente los maxterm de las funciones negadas se tiene:

/Fc = w, x, y (1, 3, 5, 6) y /Gc = w, x, y (2, 3, 4, 7), y el circuito seria:

Hubert Stalin Vsquez Cueva Pgina 17

CIRCUITOS DIGITALES I FIEE - UNMSM

d) Fd = w, x, y, z (0, 1, 2, 3, 5, 7, 11, 13)

Tomando nuevamente el maxterm de la funcin negada se tiene:

/Fd = w, x, y, z (0, 1, 2, 3, 5, 7, 11, 13), el circuito seria:

Hubert Stalin Vsquez Cueva Pgina 18

CIRCUITOS DIGITALES I FIEE - UNMSM

Hubert Stalin Vsquez Cueva Pgina 19

CIRCUITOS DIGITALES I FIEE - UNMSM

BIBLIOGRAFA

http://html.rincondelvago.com/codificadores-y-

decodificadores_multiplexores-y-demultiplexores.html

http://e-

ducativa.catedu.es/44700165/aula/archivos/repositorio/4750/4923/html/

2_decodificadores.html

http://es.scribd.com/doc/43220345/Decodificador-7447

http://electronica-teoriaypractica.com/circuito-7447-ttl/

https://www.google.com.pe/url?

sa=t&rct=j&q=&esrc=s&source=web&cd=3&cad=rja&uact=8&sqi=2&v

ed=0CDMQFjAC&url=http%3A%2F%2Fww2.educarchile.cl%2FUserFiles

%2FP0029%2FFile%2FObjetos_Didacticos%2FELO_02_TEL

%2FRecursos_Conceptuales

%2FDecodificador_7447.doc&ei=A4uWU9TKBM_lsASp9YIQ&usg=AFQjCN

F72zdiEc-sSFDNcf1D-

misMU1wWw&sig2=OEIqFBpcaJ_1TOjDDB9uIw&bvm=bv.68445247,d.cW

c

http://www.uco.es/organiza/departamentos/aceyte/electronica/rss01/OrC

AD/teoria/14.pdf

http://meteo.ieec.uned.es/www_Usumeteog/comp_comb_demultiplexores

.html

https://riunet.upv.es/bitstream/handle/10251/17421/v2_generacion_funci

ones_con_decos_salida_bajo.pdf?sequence=1

Hubert Stalin Vsquez Cueva Pgina 20

Vous aimerez peut-être aussi

- Formato de Celdas: General Numero Moneda Contabildad 1.5789 1.5789000 S/. 1.58 $ 1.58Document8 pagesFormato de Celdas: General Numero Moneda Contabildad 1.5789 1.5789000 S/. 1.58 $ 1.58GRINGEKOPas encore d'évaluation

- Nuevas TecnologiasDocument41 pagesNuevas TecnologiasRolando Silva UriartePas encore d'évaluation

- CIR1 C06 Condensadores y BobinasDocument18 pagesCIR1 C06 Condensadores y BobinasGRINGEKOPas encore d'évaluation

- Radio en LaceDocument2 pagesRadio en LaceGRINGEKOPas encore d'évaluation

- CIR1 - C01 - Conceptos Basicos PDFDocument20 pagesCIR1 - C01 - Conceptos Basicos PDFGRINGEKOPas encore d'évaluation

- 01 - Estadistica Relevante e Integrante Del CoesDocument8 pages01 - Estadistica Relevante e Integrante Del CoesGRINGEKOPas encore d'évaluation

- CIR1 - C07Transformada de Laplace en CircuitosaDocument43 pagesCIR1 - C07Transformada de Laplace en CircuitosaKevin Osorio100% (1)

- CIR1 - C08 - Circuitos de Primer OrdenDocument17 pagesCIR1 - C08 - Circuitos de Primer OrdenGRINGEKOPas encore d'évaluation

- Periodo de Concurrencia Limitada de Telefónica Del PerúDocument4 pagesPeriodo de Concurrencia Limitada de Telefónica Del PerúGRINGEKOPas encore d'évaluation

- Marco Legales de Las Telecomnicaciones ChinoDocument3 pagesMarco Legales de Las Telecomnicaciones ChinoGRINGEKOPas encore d'évaluation

- CIR1 C02 Leyes BasicasDocument15 pagesCIR1 C02 Leyes BasicasAngel Alvaro GonzalesPas encore d'évaluation

- Modelo Osi y TCPDocument2 pagesModelo Osi y TCPGRINGEKOPas encore d'évaluation

- Coeficientes de Asociaci N Pearson y Spearman en SPSSDocument19 pagesCoeficientes de Asociaci N Pearson y Spearman en SPSSNelson JiménezPas encore d'évaluation

- CIR1 - C10 - Amplificadores Operacionales PDFDocument25 pagesCIR1 - C10 - Amplificadores Operacionales PDFGRINGEKOPas encore d'évaluation

- Fundamentos Teoricos de RadiocomunicacionesDocument36 pagesFundamentos Teoricos de RadiocomunicacionesFrank ElizaldePas encore d'évaluation

- IntE - Potencia 2016Document41 pagesIntE - Potencia 2016GRINGEKOPas encore d'évaluation

- Clase2 IIDocument32 pagesClase2 IIdanielPas encore d'évaluation

- Modulacià N LinealDocument45 pagesModulacià N LinealGRINGEKOPas encore d'évaluation

- Arrancadores SuavesDocument1 pageArrancadores SuavesGRINGEKO100% (1)

- Cal - Num - Sistemas de Ecucaciones Lineales - Pres4 PDFDocument43 pagesCal - Num - Sistemas de Ecucaciones Lineales - Pres4 PDFGRINGEKOPas encore d'évaluation

- Ejemplo de Propagacion Del ErrorDocument4 pagesEjemplo de Propagacion Del ErrorGRINGEKOPas encore d'évaluation

- Celso 1Document3 pagesCelso 1GRINGEKOPas encore d'évaluation

- Tarea LinealesDocument1 pageTarea LinealesGRINGEKOPas encore d'évaluation

- 1.analisis Del ErrorDocument18 pages1.analisis Del ErrorAltair A. Jaulis CondePas encore d'évaluation

- Makinas Elctrikas Labo 7Document5 pagesMakinas Elctrikas Labo 7GRINGEKOPas encore d'évaluation

- EXP.2 LAB 3campo ElectricoDocument10 pagesEXP.2 LAB 3campo ElectricoDaniel JohnsonPas encore d'évaluation

- Metodo de Gauss Jordan EjercicioDocument3 pagesMetodo de Gauss Jordan EjercicioGRINGEKOPas encore d'évaluation

- Informe Multimetro DigitalDocument6 pagesInforme Multimetro DigitalGRINGEKOPas encore d'évaluation

- Filtros Activos de PotenciaDocument5 pagesFiltros Activos de PotenciaGRINGEKOPas encore d'évaluation

- Clase7 1Document57 pagesClase7 1GRINGEKOPas encore d'évaluation

- Automatismo Combinacional 7Document7 pagesAutomatismo Combinacional 7Johandry Carrillo100% (1)

- Herramientas de Lógica Computacional Taller SoluciónDocument9 pagesHerramientas de Lógica Computacional Taller SoluciónDairo ;-;Pas encore d'évaluation

- Convertidor Analógicodigital Con RetroalimentaciónDocument11 pagesConvertidor Analógicodigital Con Retroalimentaciónjony_campo100% (1)

- Estructura CondicionalDocument8 pagesEstructura CondicionalEdwin Zapata SullonPas encore d'évaluation

- Ejercicios de circuitos lógicos y tablas de verdadDocument4 pagesEjercicios de circuitos lógicos y tablas de verdadDaniePas encore d'évaluation

- Re-10-Lab-139 Sistemas Digitales Ii PDFDocument20 pagesRe-10-Lab-139 Sistemas Digitales Ii PDFoscar2 poma2Pas encore d'évaluation

- Capítulo 1 - Introducción A Los Circuitos LógicosDocument85 pagesCapítulo 1 - Introducción A Los Circuitos LógicosVladimir Emilio Tarqui CuquiPas encore d'évaluation

- Practica 3 Electronica DigitalDocument5 pagesPractica 3 Electronica DigitalJesus CortesPas encore d'évaluation

- Guía Digitales 2012Document143 pagesGuía Digitales 2012Fernando Jaramillo0% (1)

- Actividad de Aprendizaje Unidad 2Document20 pagesActividad de Aprendizaje Unidad 2yesica hernandezPas encore d'évaluation

- S POO Contenido NroDocument49 pagesS POO Contenido NroAnonymous DoQkZ1jPas encore d'évaluation

- Informe Final N°1Document11 pagesInforme Final N°1Hans HuamanPas encore d'évaluation

- Práctica 2. Puertas Lógicas de La Familia Lógica CMOSDocument7 pagesPráctica 2. Puertas Lógicas de La Familia Lógica CMOSE&GPas encore d'évaluation

- LOGICA DIGITAL Compuertas NAND, NOR, XOR y XNOR PDFDocument6 pagesLOGICA DIGITAL Compuertas NAND, NOR, XOR y XNOR PDFGisel AngiePas encore d'évaluation

- Clase 2 - Almacenamiento de DatosV3Document56 pagesClase 2 - Almacenamiento de DatosV3Samuel Santos Medina ToledoPas encore d'évaluation

- ElectroneumáticaDocument33 pagesElectroneumáticaJesúsDavidGonzálezCastañedaPas encore d'évaluation

- Clase 09 Prueba 1Document1 pageClase 09 Prueba 1Rey Valdés MarangunicPas encore d'évaluation

- Niveles de Organizacion de ComputadorasDocument78 pagesNiveles de Organizacion de ComputadorascereguPas encore d'évaluation

- Práctica de Electrónica DigitalDocument30 pagesPráctica de Electrónica DigitalA.JPas encore d'évaluation

- Manual SQL 1Document26 pagesManual SQL 1ediacebo1129100% (2)

- Capitulo 1 MicrocontroladoresDocument48 pagesCapitulo 1 MicrocontroladoresJOSE RODRIGUEZPas encore d'évaluation

- Estructuras Condicionales - CiclicasDocument14 pagesEstructuras Condicionales - CiclicasAlfredo KaleniuszkaPas encore d'évaluation

- Guía de estudio para Sistemas digitales y periféricosDocument6 pagesGuía de estudio para Sistemas digitales y periféricosjosalll6Pas encore d'évaluation

- Identificacion y Analisis de Circuitos IntegradosdocxDocument5 pagesIdentificacion y Analisis de Circuitos IntegradosdocxARCHIE SHOPPas encore d'évaluation

- Practica 2 Simulacion de Restador de 4 BitsDocument12 pagesPractica 2 Simulacion de Restador de 4 BitskorinaPas encore d'évaluation

- Informe Epi InfoDocument27 pagesInforme Epi InfoJosé GuamánPas encore d'évaluation

- Sistemas DigitalesDocument4 pagesSistemas DigitalesKelly VegaPas encore d'évaluation

- Práctica 2Document21 pagesPráctica 2Renato Beltran CaceresPas encore d'évaluation

- Examen Parcial de Sistemas Digitales y Arquitectura de Computadores 00Document5 pagesExamen Parcial de Sistemas Digitales y Arquitectura de Computadores 00erica yasury lozano suarezPas encore d'évaluation

- Ejercicios programación PIC16F84 control motoresDocument3 pagesEjercicios programación PIC16F84 control motoresRoberto Andres Ruiz Pereira100% (1)