Académique Documents

Professionnel Documents

Culture Documents

Timers 80C31

Transféré par

AlyoNovakCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Timers 80C31

Transféré par

AlyoNovakDroits d'auteur :

Formats disponibles

TEMPORIZADORES DEL 80C31

1. INTRODUCCION

En estas notas se examinan los temporizadores del 80C31. Se inicia con una simplificada vista de los

temporizadores como ellos son comnmente usados con microprocesadores o microcontroladores.

Un temporizador es una serie de flip-flops divisores por dos que reciben una seal de entrada como una

fuente de reloj. El reloj se aplica al primer flip-flop, el que divide a la frecuencia del reloj por 2. La

salida del primer flip-flop sirve de reloj del segundo flip-flop, el que tambin divide por 2, y as

sucesivamente. ya que cada etapa sucesiva divide by 2, un temporizador con n etapas divide a la

frecuencia de la entrada de reloj by 2n. la salida de la ltima etapa funciona como reloj del flip-flop con

la bandera que indica el desborde del temporizador, la cual es probada por el software o genera una

interrupcin. El valor binario en los flip-flops del temporizador pueden tomarse como un "conteo" del

nmero de pulsos de reloj (o " eventos") ya que el temporizador fue arrancado. Un timer de16 bits, por

ejemplo, contara desde 0000H hasta FFFFH. La bandera de desborde se hace 1 en el desborde del

contador de FFFFH a 0000H.

La operacin de un temporizador simple se ilustra en la Figura 1 para un timer de 3 bits. Cada etapa se

muestra como un flip-flop tipo D disparado por flanco negativo operando en el modo de divisin por

dos (i.e., la salida se conecta a la entrada D ). El flip-flop de bandera es simplemente un candado tipo D,

que se hace 1 por la ltima etapa del timer. Es evidente en el diagrama de tiempos en la Figura 1b que

la primera etapa (Q0) conmuta a una frecuencia 1/2 de la del reloj, la segunda etapa a 1/4 la frecuencia

del reloj, y as sucesivamente. El conteo se exhibe en decimal, y es verificado fcilmente al examinar el

estado del los tres flip-flops. Por ejemplo, el conteo "4" ocurre cuando Q0, = 1, Q1, = 0, y Q2,= 0 (410 =

l002).

Los temporizadores son usados en virtualmente todas las aplicaciones orientadas al control, y los

temporizadores del 8051 no son la excepcin. hay dos temporizadores de 16-bit cada uno con cuatro

modos de operacin. Un tercer temporizador de 16-bits con tres modos de operacin se aadi al 8052.

Los temporizadores se usan para (a) intervalos de tiempo, (b) conteo de eventos, o (c) generacin de

baud rates para el puerto serial. Cada uno es un timer de 16 bits, por tanto, la 16ava o ltima etapa

divide la frecuencia de la entrada de reloj por 216 = 65,536. En aplicaciones de intervalos de tiempo, un

temporizador se programa para desbordarse a un intervalo regular y hacer 1 a la bandera de desborde

del temporizador. la bandera es usada para sincronizar al programa para llevar a cabo una accin tal

como cotejar el estado de una entrada o de envo de datos hacia las salidas. Otras aplicaciones pueden

usar los pulsos regulares del temporizador para medir e tiempo transcurrido entre dos condiciones (e.g.,

medicin del ancho de un pulso).

Fig. 1 Temporizador de tres bits a) Diagrama b) Seales en el tiempo.

Profr. Salvador Saucedo 1

El conteo de eventos se usa para determinar el nmero de ocurrencias de un evento, ms que el medir el

lapso de tiempo entre eventos. Un "evento" es cualquier estmulo externo que provee una transicin 1 a

0 a la pata del chip 80C51. Los temporizadores pueden tambin proveer los relojes del baud rate para el

puerto interno serial del 80C51.

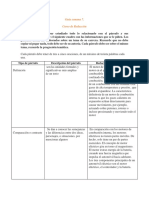

Los temporizadores del 8051 se acceden usando seis registros especiales de funcin. (Ver Tabla 1.) Un

5 SFR adicional proporciona acceso al tercer temporizador en el 8052.

2 REGISTRO de MODOS del TEMPORIZADOR (TMOD)

El registro TMOD contiene dos grupos de cuatro bits que fijan el modo de operacin par el

Temporizador 0 y el Temporizador 1. (Ver Tabla 2 y Tabla 3.)

TMOD no es bit-direccionable, ni necesita serlo. Generalmente, el es cargado una vez por el software al

inicio de un programa para iniciar el modo del temporizador . En lo sucesivo, el temporizador puede ser

parado, arrancado, y as na y otra vez al acceder a otros SFRs del temporizador.

Tabla 1. Registros de Funcin Especial de los Temporizadores

SFRs del Timer PROPOSITO DIRECCION BIT DIRECCIONABLE

TCON Control 88h Si

TMOD Modo 89h No

TL0 Temporizador 0 Byte bajo 8Ah No

TL1 Temporizador 1 Byte bajo 8Bh No

TH0 Temporizador 0 Byte alto 8Ch No

TH1 Temporizador 1 Byte alto 8Dh No

Tabla 2 Resumen del registro TMOD

BIT NOMBRE TEMPORIZADOR DESCRIPCION

7 GATE 1 Bit de compuerta. Si es 1 el temporizador

slo corre cuando INT 1 est en alto

6 C/ T 1 Bit selector Contador/Temporizador

1 = Contador de Eventos

0 = Intervalo de Tiempo

5 M1 1 Bit 1 del modo (ver tabla 3)

4 M0 1 Bit 0 del modo (ver tabla 3)

3 GATE 0 Bit de compuerta del temporizador 0

2 C/ T 0 Bit selector Contador/Temporizador del

temporizador 0

1 M1 0 Bit 1 del modo de temporizador 0

0 M0 0 Bit 0 del modo de temporizador 0

Tabla 3 Resumen de modos del temporizador

M1 M0 MODO DESCRIPCION

0 0 0 Modo de 13 Bits (modo 8048)

0 1 1 Modo de 16 Bits

1 0 2 Modo 8 Bits con auto recarga

1 1 3 Modo partido:

Temporizador 0: TL0 es un temporizador de 8

bits fijado por bits de modo del temporizador 0.

TH0 es un temporizador de 8 bits fijado por

bits de modo del temporizador 1.

3. REGISTRO de CONTROL del TEMPORIZADOR (TCON)

El registro TCON contiene bits de estatus y de control para el Temporizador 0 y para el Temporizador

1 (ver Tabla 4). Los cuatro bits superiores en TCON (TCON.4 a TCON.7) se usan para apagar y

encender los temporizadores (TR0, TR1), o para sealar el desborde de un temporizador (TF0, TF1).

Profr. Salvador Saucedo 2

Tales bits se usan extensivamente en los ejemplos en estas notas. Los cuatro bits ms bajos en TCON

(TCON.0 a TCON.3) no tienen nada que hacer con los temporizadores. Ellos se usan para detectar e

iniciar interrupciones externas. La discusin de esos bits se hizo en las notas del puerto serial.

Tabla 4 Resumen del registro TCON (Control del Temporizador)

BIT NOMBRE DIRECC. BIT DESCRIPCION

TCON.7 TF1 8FH Bandera de deborde del temporizador 1. El

hardware la hace 1, el software la hace 0 o

el hardware cuando salta a rutina de servicio a

interrupcin.

TCON.6 TR1 8EH Bit de Control del Temporizador 1

1 = Enciende al timer

0 = Apaga al timer

TCON.5 TF0 8DH Bandera de deborde del temporizador 0. El

hardware la hace 1, el software la hace 0 o

el hardware cuando salta a rutina de servicio a

interrupcin.

TCON.4 TR0 8CH Bit de Control del Temporizador 0

1 = Enciende al timer

0 = Apaga al timer

TCON.3 IE1 8BH Bandera de flanco de interrupcin externa 1. El

hardware la hace 1 al detectar flanco

negativo en INT 1 , el software la hace 0 o el

hardware cuando salta a rutina de servicio a

interrupcin.

TCON.2 IT1 8AH Bandera de tipo de interrupcin externa 1.

TCON.1 IE0 89H Bandera de flanco de interrupcin externa 0.

TCON.0 IT0 88H Bandera de tipo de interrupcin externa 0.

4 MODOS del Temporizador y bandera de Desborde

Cada temporizador se discute a continuacin. Ya que hay dos temporizadores en el 80C51, la notacin

"x" se usar para implicar ya sea al Temporizador 0 o al Temporizador 1; o sea. "THx" significa bien

TH1 o TH0 dependiendo del timer.

El arreglo de registros de temporizador TLx y THx y de banderas de desborde de temporizador TFx se

muestran en la Figura 2 para cada modo.

4.1 Modo Temporizador de 13 Bits (Modo 0)

El modo 0 es un temporizador en modo de 13-bit que provee compatibilidad con el predecesor del

8051, el microcontrolador de INTEL, el 8048. Este modo no es generalmente usado en diseos nuevos.

(ver Figura 2a.) El byte alto del temporizador (THx) se pone en cascada con los cinco bits menos

significativos del byte bajo (TLx) del temporizador para formar un timer de 13 bits. Los tres bits altos

de TLx no se usan.

Profr. Salvador Saucedo 3

Fig. 2 Modos de operacin de los temporizadores.

4.2 Modo Temporizador de 16 Bits (Modo 1)

El modo 1 es un temporizador en modo de 16 bits y es como el modo 0, excepto que el temporizador

est operando como un timer completo de 16 bits. El reloj se aplica a los registros alto y bajo

combinados del temporizador (TLx/THx). A medida que los pulsos del reloj son recibidos, la cuenta del

temporizador sube: 0000H, 0001H, 0002H, etc. Un desborde ocurre en la transicin FFFFH a 0000H

del conteo y hace 1 la bandera de desborde del temporizador. El temporizador contina el conteo. La

bandera de desborde es el bit TFx en TCON que es ledo o escrito mediante software. (ver Figura 2b.)

El bis ms significativo (MSB) del valor en los registros del temporizador es THx bit 7, y el bit menos

significativo (LSB) es TLx bit 0. El LSB conmuta con una frecuencia igual a la entrada de reloj dividida

por 2, mientras el MSB conmuta a una frecuencia igual a la entrada de reloj dividida por 65,536 (i.e..

Profr. Salvador Saucedo 4

216). Los registros del temporizador (TLx/THx) se pueden leer o escribir en cualquier tiempo por el

software.

4.3 Modo de 8 Bits con Auto Recarga (Modo 2)

El modo 2 es de 8 bits con auto recarga. El byte bajo del temporizador (TLx) opera como un

temporizador de 8 bits mientras el byte alto del temporizador (THx) guarda el valor de recarga. Cuando

el contador se desborda desde FFH a 00H, no slo es la bandera del temporizador que se hace 1, sino

que el valor en THx es cargado en TLx; el conteo contina desde este valor up hacia arriba hasta la

siguiente transicin de FFH a 00H, y as indefinidamente. Este modo es conveniente, ya que el

temporizador se desborda a intervalos especficos, peridicos, una vez que TMOD y THx han sido

iniciados. (ver Figura 2c.)

4.4 Modo de Temporizador partido (Modo 3)

El modo 3 es el temporizador partido y es diferente para cada timer. El temporizador 0 en modo 3 es

partido en dos temporizadores de 8 bits. TL0 y TH0 actan como temporizadores separados con

desbordes que hacen 1 los bits TF0 y TF1 respectivamente.

El temporizador 1 se detiene en modo 3, pero puede ser arrancado al ponerlo en uno de los otros modos.

La nica limitacin es que la bandera de desborde usual del Temporizador 1. TF1, no es afectada por

los desbordes del Temporizador 1, ya que ste est conectado a TH0.

El modo 3 brinda esencialmente un timer extra de 8 bits: El 8051 parece tener un tercer timer. Cuando

el temporizador 0 est en modo 3, el temporizador 1 puede detenerse y arrancarse al conmutarlo de su

propio modo 3. El puede todava ser usado por el puerto serial como un generador de baud rate, o l

puede usarse en cualquier manera que no requiera interrupciones (ya que no est ms conectado a

TF1).

5 Fuentes de Reloj

La figura 2 nos muestra como los temporizadores son excitados. Hay dos posibles fuentes de reloj,

seleccionadas al escribir al bit contador/temporizador (C/ T ) en TMOD cuando el temporizador es

iniciado. Una fuente de reloj es usada para producir intervalos de tiempo, la otra para contar eventos.

5.1 Generacin de Intervalos de Tiempo

Si C/ T = 0, la operacin continua del temporizador es seleccionada y el temporizador es avanzado

desde el oscilador interno. Una etapa para dividir por 12 se agrega para reducir la frecuencia de reloj a

valores razonables para la mayora de las aplicaciones. Cuando la operacin continua del temporizador

es seleccionada, el temporizador se usa para producir intervalos regulares de tiempo.

Los registros del temporizador (TLx/THx) incrementan a una tasa de 1/12avo la frecuencia del

oscilador interno: entonces, un cristal de 11.0592 MHz producir un reloj de 921,600 Hz. Los desbordes

del Temporizador ocurren tras un nmero fijo de pulsos del reloj, dependiendo en el valor inicial

cargado en los registros del temporizador, TLx/THx.

Fig. 3 Fuentes de seales de Reloj para el timer.

Profr. Salvador Saucedo 5

5.2 Conteo de Eventos

Si C/ T = 1, el temporizador es avanzado desde una fuente externa. En la mayor parte de las

aplicaciones, tal fuente externa suministra al temporizador con un pulso por la ocurrencia de un

"evento ya que temporizador est contando eventos. El nmero de eventos est determinado en

software al leer los registros del temporizador TLx/THx, ya que los valores de 16 bits en tales registros

se incrementan en la unidad por cada evento.

La fuente externa de reloj llega a travs de las patitas de las funciones alternativas del puerto 3. El bit 4

del puerto 3 (P3.4) sirve como la entrada externa de reloj para el temporizador 0 y es denotada por

"T0" en este contexto. P3.5, o "T1", es la entrada externa de reloj para el temporizador 1. (ver Figura

3). En aplicaciones de conteos, los registros del temporizador se incrementan en respuesta a una

transicin de 1 a 0 en la entrada externa. Tx. La entrada externa es muestreada durante S5P2 de cada

ciclo de mquina; luego, cuando la entrada exhibe un 1 en un ciclo y un 0 en el siguiente, el

contador es incrementado. El nuevo valor aparece en los registros del temporizador durante S3P1 del

ciclo que sigue a aqul en que la transicin es detectada. Ya que toma dos ciclos de mquina (2.17 s)

el reconocer una transicin de 1 a 0, la frecuencia mxima externa es 460 kHz (asumiendo una

operacin de 11.0592 MHz).

6. Arrancando, Deteniendo y Controlando los Temporizadores

La figura 2 ilustra las varias configuraciones para los registros TLx y THx del temporizador, y las

banderas, TFx, de desborde del temporizador. Las dos posibilidades para avanzar los temporizadores se

muestran en la figura 3. Ahora se demostrar como arrancar, parar, y controlar a los temporizadores.

El mtodo ms simple para arrancar y parar los temporizadores es con el bit de control de corrida, TRx,

en TCON. TRx es limpiado tras un reset del sistema; ello es, los temporizadores se deshabilitan

(parados) por default. TRx se hace 1 mediante software para echar a volar los temporizadores (ver

figura 4). Ya que TRx est en el registro bit-direccionable TCON, es fcil arrancar y detener los

temporizadores dentro de un programa. Por ejemplo, el temporizador 0 es arrancado mediante

SETB TR0

y detenido mediante

CLR TR0

El ensamblador llevar a cabo la necesaria conversin simbolica de "TR0 a la direccin correcta del

bit. SETB TR0 es exactamente lo mismo que SETB 8CH.

Fig. 4. Deteniendo y corriendo un Temporizador.

Otro mtodo para controlar los timers es con el bit GATE en TMOD y la entrada externa INTx .

Haciendo GATE = 1 permite al timer ser controlado mediante INTx . ello es til para medir ancho de

Profr. Salvador Saucedo 6

pulsos como sigue. Asumir que INT 0 es bajo pero pulsar alto por un periodo de tiempo a ser medido.

Iniciar al Timer 0 para modo 2, modo timer de 16-bit, con TL0/TH0 = 0000H, GATE = 1, y TR0 = 1.

Al subir INT 0 , el timer es "permitido" y es avanzado a una tasa de 921.6 kHz. Al bajar INT 0 , el timer

es "detenido" y la duracin del pulso en microsegundos es el conteo en TL0/TH0 multiplicado por

1.085. ( INT 0 Puede ser programado para generar una interrupcin cuando ella retorne a 0).

Para completar el cuadro, la figura 5 ilustra al Timer 0 operando en modo 1 como un timer de 16 bits.

As como los registros TL0/TH0 del timer y a la bandera de desborde TF0, el diagrama muestra las

posibilidades para las fuentes de reloj y para arrancar, detener, y controlar el timer.

Fig. 5. Temporizador 0 en el modo 1.

7 Inicializando y Accesando los Registros del TIMER

Los timers son usualmente iniciados una vez al comienzo de un programa para fijar el modo correcto de

operacin. En lo sucesivo, dentro del cuerpo de un programa, los timers se arrancan, detienen, lo bits de

bandera se prueban y limpian, los registros del temporizador son ledos o actualizados, etc., como

requiera la aplicacin.

TMOD es el primer registro iniciado, ya que l fija el modo de operacin. Por ejemplo, la siguiente

instruccin inicia al Timer 1 como un timer de 16-bits (modo 1) avanzado por el oscilador interno

(intervalo de tiempo):

MOV TMOD, #00010000B

El efecto de tal instruccin es hacer M1 = 0 y M0 = 1 para modo 1, deja a C/ T = 0 y GATE = 0 para

emplear el reloj interno, y limpiar los bits de modo del Timer 0. (Ver Tabla 2). Por supuesto, el timer

realmente no empieza a correr hasta que su bit de control de corrida, TR1, es puesto a 1.

Si un conteo inicial es necesario, los registros del timer TL1/TH1 deben tambin ser inicializados.

Recordando que los timers cuentan de modo ascendente y hacen 1 a la bandera de desborde en una

transicin de FFFFH a 0000H, un intervalo de 370 s debe programarse inicializando TL1/TH1 a 341

cuentas menos que 0000H. El valor correcto es -341 o FEABH. Las siguientes instrucciones hacen la

tarea:

MOV TL1, #0ABH

MOV TH1, #0FEH ; = FEABH = 65,195

El timer es entonces arrancado al poner el bit de control de corrida como sigue:

Profr. Salvador Saucedo 7

SETB TRl

La bandera de desborde es automticamente puesta a 1 370 s ms tarde. El software puede holgar en

un "lazo de espera" por 370 s usando una instruccin booleana de brinco condicional que retorna a si

misma en tanto la bandera d desborde no se haga 1:

WACHA: JNB TF1, WACHA

Cuando el timer se desborda, es necesario parar el timer y limpiar la bandera de desborde con software:

CLR TR1 ; lo detiene

CLR TF1 ; limpia bandera

7.1 Leyendo un Timer "en caliente"

En algunas aplicaciones, es necesario leer el valor en los registros del timer "en caliente". Existe un

problema potencial que es simple protegerse contra l en software. Dado que dos registros del timer

deben ser ledos, un "error de fase " puede ocurrir si el byte bajo se desborda en el byte alto entre las

dos operaciones de lectura. Un valor que nunca se tuvo puede ser ledo. La solucin es leer el byte alto

primero, luego el byte bajo, y entonces leer el byte alto otra vez. Si el byte alto ha cambiado, repetir las

operaciones de lectura. Las instrucciones siguientes leen los contenidos de los registros TL0/TH0 del

timer en los registros R6/R7, lidiando correctamente con tal problema.

REPITE: MOV A,TH0 ; Lee byte alto

MOV R6,TL0

CJNE A,TH0, REPITE

MOV R7,A

Ejemplo 1 Generacin de un tren de Pulsos a 38.5 kHz con 41% de Duty

El siguiente programa crea quince pulsos con periodo de cada onda igual a 26 s usando slo software.

En el campo de comentarios para cada instruccin se coloc el nmero de ciclos de mquina que toma

la instruccin. Al sumar los ciclos se obtiene que el periodo de la onda consta de 24 ciclos de mquina,

diez de ellos en alto y 14 en bajo. Como cada ciclo de mquina dura 1.085 s, el periodo es igual a

26.04 s, o sea 38.4 kHz. Se supone un cristal de 11.0592MHz.

MOV R2,#15

ACALL LAZO

NOP

...

LAZO:

SETB P1.0 ; 1 (14 EN BAJO)

ACALL DOS ; 2+7

CLR P1.0 ; 1 (10 EN ALTO)

NOP ; 1

NOP ; 1

ACALL DOS ; 2+7

DJNZ R2,LAZO ; 2

RET

DOS: MOV R3,#2 ; 1

LOOP: DJNZ R3,LOOP ; 2*2

RET ; 2 ( 7 CICLOS TOTAL)

Profr. Salvador Saucedo 8

La rutina dos toma siete ciclos, ms otros dos ciclos que toma la instruccin que la llama son nueve en

total. Por lo tanto el nmero de ciclos que est P1.0 en alto es igual a 10. Notar que al ejecutarse la

instruccin setb P1.0 la patita del puerto se hace 1 hasta el final del ciclo que tarda dicha

instruccin. El tren de 15 pulsos toma 390 s.

Ejemplo 2: Onda Cuadrada de 4.8 kHz

Escribir un programa usando al Timer 0 para crear una onda cuadrada de 4.8 kHz en P1.0.

Una onda cuadrada de 4800 Hz requiere un tiempo alto de 104.16 s y un tiempo bajo de 104.16 s.

Puesto que esta intervalo es menor que 277 s, el timer 0 en modo 2 puede usarse. Se supone un cristal

de 11.0592 MHz. Un desborde cada 104.16 s requiere un valor de recarga en TH0 de 96 cuentas

menos que 00H, o -96. Aqu est el programa:

ORG 100H

MOV TMOD, #02H ; 8 bits, modo de auto recarga

MOV TH0, #-96 ;-96 valor de recarga en TH0

SETB TR0 ; arranca al timer

BUC: JNB TF0, BUC ; espera el desborde

CLR TF0 ; limpia bandera del desborde del timer

CPL P1.0 ; conmuta bit del puerto

SJMP BUC ; repite

END

Este programa usa una instruccin para complementar el bit (CPL) en lugar de las instrucciones

booleanas SETB y CLR del ejemplo previo. Entre cada operacin de complemento, un retardo de 1/2 el

periodo deseado (104.16 s) es programado usando al Timer 0 en el modo de 8-bits con auto-recarga.

El valor de recarga puede ser especificado usando notacin decimal como -96, en vez de usar notacin

hexadecimal. El ensamblador realiza la conversin necesaria (0A0H). Notar que la bandera de desborde

del timer (TF0) debe ser explcitamente limpiada por el software despus de cada desborde.

Los intervalos de tiempo mayores que 277 s deben usar a timer en modo 1 de 16 bits. El retardo

mximo es 216 = 65,536 cuentas, alrededor de 71.1 milisegundos. El inconveniente del modo 1 es que

los registros del timer deben reiniciarse ras cada desborde, mientras que la recarga es automtica en el

modo 2.

Ejemplo 3: Onda Cuadrada de 600 Hz

Escribir un programa usando al Timer 0 para crear una onda cuadrada de 600 Hz en P1.0.

Una onda cuadrada de 600 Hz requiere un tiempo alto de 833.33 s y un tiempo bajo de 833.33 s.

Puesto que esta intervalo es mayor que 277 s, el timer 0 en modo 1 debe usarse. Se supone un cristal

de 11.0592 MHz. Un desborde cada 833.33 s requiere un valor de recarga en TH0 de 768 cuentas

menos que 0000H, o -768. Aqu est el programa:

5 0100 ORG 100H

6 0100 758901 MOV TMOD, #01H ; 16 bits, modo 1, sin recarga

7 0103 758CFD LAZO: MOV TH0, #0FDH ; valor de carga en TH0

8 0106 758A00 MOV TL0, #00H ; valor de carga en TL0

9 0109 D28C SETB TR0 ; arranca al timer

10 010B 308DFD BUC: JNB TF0, BUC ; espera el desborde

11 010E C28C CLR TR0 ; apaga el Timer

12 0110 C28D CLR TF0 ; limpia bandera del desborde

13 0112 B290 CPL P1.0 ; conmuta bit del puerto

14 0114 80ED SJMP LAZO ; repite

15 0116

16 0116 end

Profr. Salvador Saucedo 9

Existe un ligero error en la frecuencia del programa anterior. Tal error se debe al uso de instrucciones

extras insertadas tras el desborde del timer para poder reiniciarlo. Si se necesitan exactamente 600 Hz el

valor de carga se debe ajustar ligeramente para obtenerlo. El ensamblador realiza la conversin

necesaria para pasar el decimal -768 a hexadecimal (0FD00H). Notar que la bandera de desborde del

timer (TF0) debe ser explcitamente limpiada por el software despus de cada desborde.

Los intervalos de tiempo mayores que 71.1 ms deben usar a timer en modo 1 de 16 bits pero

combinndolo con un contador dentro de un bucle de software. El retardo mximo del modo 1, como ya

se dijo, es 216 = 65,536 cuentas de 1.085 s cada una, alrededor de 71.1 milisegundos.

Ejemplo 4. Tres Ondas Cuadradas Usando Interrupciones y un contador

Escribir un programa usando interrupciones para simultneamente crear tres ondas cuadradas:

una de 14.4 kHz, otra de 300 Hz y una ms de 15 Hz en P1.7, P1.6 y P1.5, respectivamente.

La configuracin de hardware con la temporizacin para las formas de onda deseadas se ofrece en la

Figura 6. Tal combinacin de salidas sera extremadamente difcil de generar en un sistema sin

interrupciones. El timer 0, provee sincronizacin para la seal de 14.4 kHz, opera en el modo 2, como

en el ejemplo previo: y el timer 1, provee sincronizacin para la onda de 300 Hz. Puesto que la seal de

300 Hz necesita 1.666 ms en alto y tambin 1.666 ms en bajo, el modo 2 no se puede usar para este

caso. (Recordar que 277 s es el mximo intervalo de tiempo en el modo 2 cuando el 80C31 opera a

11.0592 MHz.) Aqu est el programa:

1 0000 ORG 0

2 0000 802E SJMP MAIN

3 000B ORG 00BH ; vector del Timer 0

4 000B 8034 SJMP T0ISR

5 001B ORG 01BH ; vector del Timer 1

6 001B 8027 SJMP TlISR

7 001D

8 0030 ORG 0030H

9 0030 758912 MAIN: MOV TMOD,#12H ;Timer 1 = modo 1

10 0033 ;Timer 0 = modo 2

11 0033 758CE0 MOV TH0,#-32 ;14.4 kHz usando timer 0

12 0036 D28C SETB TR0

13 0038 D28F SETB TF1 ;fuerza interrupcion timer 1

14 003A 75A88A MOV IE,#8AH ;permite ambos timers interrumpan

15 003D 7C00 MOV R4,#0 ; inicia contador

16 003F 80FE SJMP $

17 0041

18 0041 B297 T0ISR: CPL P1.7

19 0043 32 RETI

20 0044

21 0044 C28E TlISR: CLR TR1 ; Apaga al timer

22 0046 758DFA MOV TH1, #HIGH(-1536) ; 1.666 ms tiempo alto &

23 0049 758B00 MOV TL1, #LOW(-1536) ; tiempo bajo igual

24 004C D28E SETB TR1 ; enciende al timer

25 004E B296 CPL P1.6

26 0050 0C INC R4 ; incrementa contador

27 0051 BC1404 CJNE R4,#20,FIN

28 0054 7C00 MOV R4,#0 ; reinicia contador

29 0056 B295 CPL P1.5

30 0058 32 FIN: RETI

31 0059 END

Aqu, el marco es para un programa completo que puede ser instalado en EPROM o ROM en un

producto basado en el 80C31. El programa principal y las ISRs se localizan encima de las localidades

de los vectores para el reset del sistema y ambas interrupciones, aunque la ISR para el timer 0 slo mide

tres bytes, por lo que bien pudo quedar a partir de la localidad 000BH. Las tres formas de ondas se

crean mediante instrucciones booleanas "CPL"; empero, los intervalos de tiempo necesitan mtodos

algo diferentes para cada uno.

Puesto que los registros TL1/TH1 deben ser recargados tras cada desborde (i.e. despus de cada

interrupcin), la ISR del timer 1 (a) detiene al timer, (b) recarga TL1/TH1, (c) arranca al timer, luego

(d) complementa al bit 6 del puerto 1, y si procede complementa el bit P1.5 para los 15 Hz. Notar

Profr. Salvador Saucedo 10

adems, que TL1/TH1 no son inicializados al principio del programa principal, a diferencia de TH0. Ya

que TL1/TH1 deben ser reiniciados tras cada desborde, TF1 se hace 1 en el programa principal por

software para "forzar" una interrupcin inicial tan pronto como las interrupciones sean encendidas. Esto

efectivamente hace que la forma de onda de 300 Hz se produzca.

Fig. 6. Formas de onda (sin escala) del ejemplo.

La ISR del Timer 0, como era de esperarse, simplemente complementa el bit 7 del puerto 1 y retorna,

mediante la instruccin RETI al programa principal. SJMP $ se usa en el programa principal para

abreviar la forma de ACA: SJMP ACA. Las dos formas son funcionalmente equivalentes. Notar que

las banderas de desborde TF0 y TF1 no son limpiadas explcitamente por el software, pues al usar

interrupciones dichas banderas son borradas por el hardware al saltar a la ISR (Rutina de Servicio a

Interrupcin) respectiva.

Ejemplo 5. Interfaz de un Buzzer

Un buzzer se conecta a P1.7 y un switch sin rebotes se conecta a P1.6. Escribir un programa que

lea el nivel lgico producido por el switch y suene el buzzer por un segundo por cada transicin

de1 a 0 detectada.

El buzzer en la figura 7 es un transductor piezo cermico que vibra cuando es estimulado con un voltaje

de CD. El objetivo aqu es generar un tono alrededor de 3.3 kHz a 5 voltios CD. Un inversor se usa

como driver pues el buzzer toma 8 mA de corriente. Como indican las caractersticas de CD del 8051 en

el manual, las patas del Puerto 1 pueden sumir un mximo de 1.6 mA. Crear retardos de software es uno

de las ms comunes tareas de programacin dadas a estudiantes de microprocesadores. El mtodo usual

de decrementar un contador dentro de un bucle no es necesario en el 8031, pues cuenta con timers

propios. Una subrutina de 1 segundo de retardo usando al Timer 0 se muestra en este ejemplo.

Profr. Salvador Saucedo 11

Fig. 7 Ejemplo del zumbador.

La transicin de 1 a 0 en P1.6 es detectada esperando por un 1 (JNB P1.6, LAZO) y luego

esperando por un 0 (JB P1.6, WACHA). Veamos el programa:

2 0000 CIENTO EQU 100 ;100x9217*1.085 us = 1 SEG

3 0000 CUENTA EQU 9217

4 0100 ORG 100h

5 0100 758901 MOV TMOD,#0lH ;usa timer 0 en modo 1

6 0103 3096FD LAZO: JNB P1.6,LAZO ;espera por 1 en entr.

7 0106 2096FD WACHA: JB P1.6,WACHA ;espera por 0 en entr.

8 0109 D297 SETB P1.7 ; ARRANCA AL BUZZER

9 010B 120112 CALL DELAY ; espera 1 segundo

10 010E C297 CLR P1.7 ; APAGA AL BUZZER

11 0110 80F1 SJMP LAZO

12 0112 7F64 DELAY: MOV R7, #CIENTO

13 0114 758C24 OTRA: MOV TH0,#HIGH CUENTA

14 0117 758A01 MOV TL0,#LOW CUENTA

15 011A D28C SETB TR0

16 011C 308DFD ACA: JNB TF0, ACA

17 011F C28D CLR TF0

18 0121 C28C CLR TR0

19 0123 DFEF DJNZ R7,OTRA

20 0125 22 RET

21 0126 END

Hay dos situaciones no manejadas en el ejemplo visto. Primero, si la entrada conmuta durante el

segundo que el buzzer est sonando, la transicin no es detectada, ya que el software est ocupado en la

rutina delay. Segundo, si la entrada conmuta rpidamente en fraccin de milisegundo la transicin

puede ser no detectada tanto por las instrucciones JNB y JB.

PROBLEMAS

1. Escribir un programa para el 80C31 que produzca una onda casi cuadrada en P1.5 de 48.5

kHz, sin usar los timers.

2. Escribir un programa en el 80C31 que produzca una onda cuadrada en P1.2 de 12.5 kHz,

usando el timer 0.

3. Modificar el ejemplo 3 para que la frecuencia sea de 440 Hz.

4. Modificar ejemplo 1 para obtener una frecuencia de 30.8 kHz con 40% de duty,

tiempo _ alto

duty= 100 %.

periodo

5. Modificar ejemplo 4 para que la onda en P1.5 sea de 60Hz.

6. Programar el timer 1 para tener un baud rate de 19,200 bps en el puerto serial.

7. Modificar ejemplo 5 para que el buzzer suene en una deteccin si y la siguiente no.

8. Usar interrupciones en el timer 0, modo 1, para generar en P1.5 un periodo de 20 ms con

33% de duty.

Profr. Salvador Saucedo 12

9. Programar el timer 0 como contador de eventos, usando interrupciones, para implementar

un reloj en tiempo real que se actualice cada segundo. Poner en RAM interna la hora del da

en hh:mm:ss, en las localidades 60h a 62h. Usar el circuito del diagrama siguiente.

10. Aadir el circuito dado del problema anterior al cableado de la prctica 5 que corre al

programa monitor, pero usando la entrada INT 0 y programar la interrupcin externa. Enviar

el tiempo real a exhibirse en la pantalla de la PC, cada 5 segundos.

Profr. Salvador Saucedo 13

Profr. Salvador Saucedo 14

Vous aimerez peut-être aussi

- Ejercicios Resueltos de Ingenieria EconomicaDocument35 pagesEjercicios Resueltos de Ingenieria EconomicaJohnnye EspinozaPas encore d'évaluation

- Amortizacion EjemploDocument5 pagesAmortizacion EjemploAlyoNovakPas encore d'évaluation

- ¿Como Se Suman Los Fasores en Forma Polar?Document2 pages¿Como Se Suman Los Fasores en Forma Polar?AlyoNovakPas encore d'évaluation

- Guia-Tarea Semana 11Document3 pagesGuia-Tarea Semana 11AlyoNovakPas encore d'évaluation

- Windows 7 HP KeyDocument4 pagesWindows 7 HP KeyAlyoNovakPas encore d'évaluation

- Motores y Generadores de I DCDocument20 pagesMotores y Generadores de I DCAlyoNovakPas encore d'évaluation

- Guia-Tarea Semana 11Document3 pagesGuia-Tarea Semana 11AlyoNovakPas encore d'évaluation

- Tarea s9Document3 pagesTarea s9AlyoNovakPas encore d'évaluation

- Reporte Llenado de TanquesDocument3 pagesReporte Llenado de Tanquesdaniel leon100% (2)

- Tarea s9Document4 pagesTarea s9AlyoNovakPas encore d'évaluation

- Diapositivas Medidores de Nivel Instrumentacion IndustrialDocument23 pagesDiapositivas Medidores de Nivel Instrumentacion IndustrialAlyoNovakPas encore d'évaluation

- Tema 3 NivelDocument40 pagesTema 3 NivelAlyoNovakPas encore d'évaluation

- T94 PDFDocument286 pagesT94 PDFAlyoNovakPas encore d'évaluation

- Greguris Montilla Video-SODocument8 pagesGreguris Montilla Video-SOLis DiPas encore d'évaluation

- Tecnologia de La Informacion en Los NegociosDocument10 pagesTecnologia de La Informacion en Los Negocioscarlos andresrodriguez gaonaPas encore d'évaluation

- Unidad 1. El Microprocesador (CPU)Document53 pagesUnidad 1. El Microprocesador (CPU)Ismael Casarrubias GPas encore d'évaluation

- Partes de La Computadora: El CpuDocument20 pagesPartes de La Computadora: El CpuJulia PeraltaPas encore d'évaluation

- La Placa BaseDocument7 pagesLa Placa BaseElianita RuizPas encore d'évaluation

- Cot m3145Document5 pagesCot m3145jeremy pedrazaPas encore d'évaluation

- Modulos I2c y DciDocument5 pagesModulos I2c y Dcikapri1001Pas encore d'évaluation

- ArduinoLeerYEscribirDatosEnTarjetaSD de Arduino PDFDocument61 pagesArduinoLeerYEscribirDatosEnTarjetaSD de Arduino PDFdanielgtvoPas encore d'évaluation

- Sistemas Basados en MicroprocesadoresDocument16 pagesSistemas Basados en MicroprocesadoresHector InbacuanPas encore d'évaluation

- Diseño de Red - Astucuri Quispe Freddy - Ing - SistemasDocument24 pagesDiseño de Red - Astucuri Quispe Freddy - Ing - SistemasFred Randhal Astucuri QuispePas encore d'évaluation

- Windows NT4Document218 pagesWindows NT4Mario MaldonadoPas encore d'évaluation

- EnsayoDocument4 pagesEnsayocarlos cesarPas encore d'évaluation

- Generacion de Una Señal VgaDocument3 pagesGeneracion de Una Señal VganikolayeyPas encore d'évaluation

- Tabla CablesDocument2 pagesTabla Cablesfatima SanchezPas encore d'évaluation

- Tema3 Iso VirtualizacionDocument17 pagesTema3 Iso VirtualizacionCésar Augusto Cabrera GarcíaPas encore d'évaluation

- Informe Plataforma GoogleDocument13 pagesInforme Plataforma GoogleMagician PeruPas encore d'évaluation

- Como Saber Si Tu Nueva Xbox 360 Lleva Placa JasperDocument2 pagesComo Saber Si Tu Nueva Xbox 360 Lleva Placa JasperJefferson LlerenaPas encore d'évaluation

- Lista Ledacom 20 Septiembre 2023Document15 pagesLista Ledacom 20 Septiembre 2023JimmyArangoPas encore d'évaluation

- Boletin Imprentas y Maquinas FiscalesDocument28 pagesBoletin Imprentas y Maquinas FiscalesGrupo Contable ACTPas encore d'évaluation

- MarcosGarcíaTarea 2.ErroresBIOSDocument4 pagesMarcosGarcíaTarea 2.ErroresBIOSmarquitos.mgfPas encore d'évaluation

- Autómatas Programables2Document62 pagesAutómatas Programables2Alexis GonzalezPas encore d'évaluation

- Previo 1 Dispositivos de Almacenamiento y de Entrada/SalidaDocument2 pagesPrevio 1 Dispositivos de Almacenamiento y de Entrada/SalidaIanVnPas encore d'évaluation

- Fujitsu Maintenance Basic Storage WBTDocument8 pagesFujitsu Maintenance Basic Storage WBTJose AcevedoPas encore d'évaluation

- Cap. IV. - Entrada-Salida PDFDocument36 pagesCap. IV. - Entrada-Salida PDFgustavo.d dddamadorPas encore d'évaluation

- Cuestionario de 100 Preguntas InformaticaDocument16 pagesCuestionario de 100 Preguntas InformaticaPedro Edward Estrada LopezPas encore d'évaluation

- Examen TecnicaDocument2 pagesExamen TecnicaJosePas encore d'évaluation

- Caracteristicas de UPA PDFDocument55 pagesCaracteristicas de UPA PDFEsquisof95% (20)

- Ejercicios de Paquetes de Software Semana 3Document10 pagesEjercicios de Paquetes de Software Semana 3Lester LópezPas encore d'évaluation

- Cap 2 CoulourisDocument34 pagesCap 2 CoulourisAurora Rodriguez Bermudez0% (1)