Académique Documents

Professionnel Documents

Culture Documents

Infineon BSC093N04LSG DS v02 01 en

Transféré par

arafatasgharTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Infineon BSC093N04LSG DS v02 01 en

Transféré par

arafatasgharDroits d'auteur :

Formats disponibles

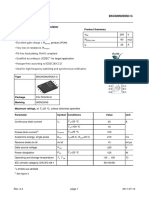

BSC093N04LS G

OptiMOS3 Power-Transistor Product Summary

Features VDS 40 V

Fast switching MOSFET for SMPS RDS(on),max 9.3 mW

Optimized technology for DC/DC converters ID 49 A

Qualified according to JEDEC1) for target applications PG-TDSON-8

N-channel; Logic level

Excellent gate charge x R DS(on) product (FOM)

Very low on-resistance R DS(on)

Superior thermal resistance

100% Avalanche tested

Pb-free plating; RoHS compliant

Halogen-free according to IEC61249-2-21

Type Package Marking

BSC093N04LS G PG-TDSON-8 093N04LS

Maximum ratings, at T j=25 C, unless otherwise specified

Parameter Symbol Conditions Value Unit

Continuous drain current ID V GS=10 V, T C=25 C 49 A

V GS=10 V, T C=100 C 31

V GS=4.5 V, T C=25 C 40

V GS=4.5 V,

26

T C=100 C

V GS=10 V, T A=25 C,

13

R thJA=50 K/W 2)

Pulsed drain current3) I D,pulse T C=25 C 196

Avalanche current, single pulse4) I AS T C=25 C 40

Avalanche energy, single pulse E AS I D=40 A, R GS=25 W 10 mJ

Gate source voltage V GS 20 V

1)

J-STD20 and JESD22

Rev. 2.1 page 1 2013-05-21

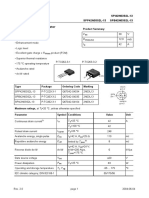

BSC093N04LS G

Maximum ratings, at T j=25 C, unless otherwise specified

Parameter Symbol Conditions Value Unit

Power dissipation P tot T C=25 C 35 W

T A=25 C,

2.5

R thJA=50 K/W 2)

Operating and storage temperature T j, T stg -55 ... 150 C

IEC climatic category; DIN IEC 68-1 55/150/56

Parameter Symbol Conditions Values Unit

min. typ. max.

Thermal characteristics

Thermal resistance, junction - case R thJC bottom - - 3.6 K/W

top 20

Device on PCB R thJA 6 cm2 cooling area2) - - 50

Electrical characteristics, at T j=25 C, unless otherwise specified

Static characteristics

Drain-source breakdown voltage V (BR)DSS V GS=0 V, I D=1 mA 40 - - V

Gate threshold voltage V GS(th) V DS=V GS, I D=14 A 1.2 - 2

V DS=40 V, V GS=0 V,

Zero gate voltage drain current I DSS - 0.1 1 A

T j=25 C

V DS=40 V, V GS=0 V,

- 10 100

T j=125 C

Gate-source leakage current I GSS V GS=20 V, V DS=0 V - 10 100 nA

Drain-source on-state resistance R DS(on) V GS=4.5 V, I D=20 A - 11.0 13.7 mW

V GS=10 V, I D=40 A - 7.8 9.3

Gate resistance RG - 1 - W

|V DS|>2|I D|R DS(on)max,

Transconductance g fs 34 67 - S

I D=40 A

2)

Device on 40 mm x 40 mm x 1.5 mm epoxy PCB FR4 with 6 cm2 (one layer, 70 m thick) copper area for drain

connection. PCB is vertical in still air.

3)

See figure 3 for more detailed information

4)

See figure 13 for more detailed information

Rev. 2.1 page 2 2013-05-21

BSC093N04LS G

Parameter Symbol Conditions Values Unit

min. typ. max.

Dynamic characteristics

Input capacitance C iss - 1400 1900 pF

V GS=0 V, V DS=20 V,

Output capacitance C oss - 340 450

f =1 MHz

Reverse transfer capacitance Crss - 16 -

Turn-on delay time t d(on) - 3.6 - ns

Rise time tr V DD=20 V, V GS=10 V, - 2.4 -

Turn-off delay time t d(off) I D=30 A, R G,ext=1.6 W - 16 -

Fall time tf - 2.8 -

Gate Charge Characteristics5)

Gate to source charge Q gs - 4.9 - nC

Gate charge at threshold Q g(th) - 2.3 -

Gate to drain charge Q gd V DD=20 V, I D=30 A, - 2.0 -

Q sw V GS=0 to 10 V

Switching charge - 4.6 -

Gate charge total Qg - 18 24

Gate plateau voltage V plateau - 3.5 - V

V DD=20 V, I D=30 A,

Gate charge total Qg - 8.6 11.4 nC

V GS=0 to 4.5 V

V DS=0.1 V,

Gate charge total, sync. FET Q g(sync) - 17 -

V GS=0 to 10 V

Output charge Q oss V DD=20 V, V GS=0 V - 13 -

Reverse Diode

Diode continuous forward current IS - - 29 A

T C=25 C

Diode pulse current I S,pulse - - 196

V GS=0 V, I F=40 A,

Diode forward voltage V SD - 0.9 1.2 V

T j=25 C

V R=20 V, I F=I S,

Reverse recovery charge Q rr - 15 - nC

di F/dt =400 A/s

5)

See figure 16 for gate charge parameter definition

Rev. 2.1 page 3 2013-05-21

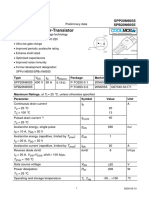

BSC093N04LS G

1 Power dissipation 2 Drain current

P tot=f(T C) I D=f(T C); V GS10 V

40 50

35

40

30

25

30

Ptot [W]

ID [A]

20

20

15

10

10

0 0

0 40 80 120 160 0 40 80 120 160

TC [C] TC [C]

3 Safe operating area 4 Max. transient thermal impedance

I D=f(V DS); T C=25 C; D =0 Z thJC=f(t p)

parameter: t p parameter: D =t p/T

103 10

limited by on-state

resistance

1 s

0.5

102

10 s

1

0.2

100 s

ZthJC [K/W]

0.1

DC

ID [A]

101 0.05

0.02

1 ms

0.01

0.1

10 ms

single pulse

100

10-1 0.01 0 0 0 0 0 0 1

10-1 100 101 102 10-6 10-5 10-4 10-3 10-2 10-1 100

VDS [V] tp [s]

Rev. 2.1 page 4 2013-05-21

BSC093N04LS G

5 Typ. output characteristics 6 Typ. drain-source on resistance

I D=f(V DS); T j=25 C R DS(on)=f(I D); T j=25 C

parameter: V GS parameter: V GS

120 20

3.5 V

5V

4.5 V

100 10 V

16

4V

80

RDS(on) [mW]

12 4.5 V

4V

ID [A]

60 5V

10 V

8

40

3.5 V

4

20

3.2 V

3V

2.8 V

0 0

0 1 2 3 0 10 20 30 40 50

VDS [V] ID [A]

7 Typ. transfer characteristics 8 Typ. forward transconductance

I D=f(V GS); |V DS|>2|I D|R DS(on)max g fs=f(I D); T j=25 C

parameter: T j

120 120

100 100

80 80

gfs [S]

ID [A]

60 60

40 40

20 20

150 C

25 C

0 0

0 1 2 3 4 5 0 40 80 120 160

VGS [V] ID [A]

Rev. 2.1 page 5 2013-05-21

BSC093N04LS G

9 Drain-source on-state resistance 10 Typ. gate threshold voltage

R DS(on)=f(T j); I D=40 A; V GS=10 V V GS(th)=f(T j); V GS=V DS; I D=14 A

16 2.5

2

12

98 %

RDS(on) [mW]

1.5

VGS(th) [V]

8 typ

4

0.5

0 0

-60 -20 20 60 100 140 180 -60 -20 20 60 100 140 180

Tj [C] Tj [C]

11 Typ. capacitances 12 Forward characteristics of reverse diode

C =f(V DS); V GS=0 V; f =1 MHz I F=f(V SD)

parameter: T j

104 1000

103 Ciss

Coss 150 C, 98%

100

25 C

C [pF]

IF [A]

102

150 C

25 C, 98%

Crss 10

101

100 1

0 10 20 30 40 0.0 0.5 1.0 1.5 2.0

VDS [V] VSD [V]

Rev. 2.1 page 6 2013-05-21

BSC093N04LS G

13 Avalanche characteristics 14 Typ. gate charge

I AS=f(t AV); R GS=25 W V GS=f(Q gate); I D=30 A pulsed

parameter: T j(start) parameter: V DD

100 12

20 V

10 8V

32 V

8

25 C

VGS [V]

IAV [A]

100 C

10 6

125 C

1 0

0.1 1 10 100 1000 0 4 8 12 16 20

tAV [s] Qgate [nC]

15 Drain-source breakdown voltage 16 Gate charge waveforms

V BR(DSS)=f(T j); I D=1 mA

45

V GS

Qg

40

35

VBR(DSS) [V]

30 V gs(th)

25

Q g(th) Q sw Q gate

20 Q gs Q gd

-60 -20 20 60 100 140 180

Tj [C]

Rev. 2.1 page 7 2013-05-21

BSC093N04LS G

Package Outline PG-TDSON-8

PG-TDSON-8: Outline

Footprint

Rev. 2.1 page 8 2013-05-21

BSC093N04LS G

Package Outline

PG-TDSON-8: Tape

Dimensions in mm

Rev. 2.1 page 9 2013-05-21

BSC093N04LS G

Published by

Infineon Technologies AG

81726 Munich, Germany

2009 Infineon Technologies AG

All Rights Reserved.

Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of

conditions or characteristics. With respect to any examples or hints given herein, any typical

values stated herein and/or any information regarding the application of the device,

Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind,

including without limitation, warranties of non-infringement of intellectual property rights

of any third party.

Information

For further information on technology, delivery terms and conditions and prices, please

contact the nearest Infineon Technologies Office

(www.infineon.com).

Warnings

Due to technical requirements, components may contain dangerous substances. For information

on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with

the express written approval of Infineon Technologies, if a failure of such components can

reasonably be expected to cause the failure of that life-support device or system or to affect

the safety or effectiveness of that device or system. Life support devices or systems are

intended to be implanted in the human body or to support and/or maintain and sustain

and/or protect human life. If they fail, it is reasonable to assume that the health of the user

or other persons may be endangered.

Rev. 2.1 page 10 2013-05-21

Vous aimerez peut-être aussi

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsD'EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsPas encore d'évaluation

- MOS™2 Power-Transistor: Product SummaryDocument10 pagesMOS™2 Power-Transistor: Product SummaryHermilio ValdizanPas encore d'évaluation

- Solution Manual for an Introduction to Equilibrium ThermodynamicsD'EverandSolution Manual for an Introduction to Equilibrium ThermodynamicsPas encore d'évaluation

- 079N03LS InfineonDocument10 pages079N03LS Infineonnemesis 81Pas encore d'évaluation

- DatasheetDocument10 pagesDatasheettcm sumbagselPas encore d'évaluation

- MOS 2 Power-Transistor: Features Product SummaryDocument11 pagesMOS 2 Power-Transistor: Features Product Summarydoraemon007Pas encore d'évaluation

- MOS 3 Power-Transistor: Features Product SummaryDocument11 pagesMOS 3 Power-Transistor: Features Product Summarydoraemon007Pas encore d'évaluation

- Mosfet: Powermanagement&MultimarketDocument10 pagesMosfet: Powermanagement&MultimarketcesarPas encore d'évaluation

- MOS 3 Power-Transistor: Features Product SummaryDocument9 pagesMOS 3 Power-Transistor: Features Product Summaryluis alberto perez monteroPas encore d'évaluation

- BSC059N03SDocument13 pagesBSC059N03SBan NeoPas encore d'évaluation

- MOS 2 Power-Transistor: Features Product SummaryDocument11 pagesMOS 2 Power-Transistor: Features Product SummaryAntonioNobregaPas encore d'évaluation

- MOS 2 Power-Transistor: Features Product SummaryDocument10 pagesMOS 2 Power-Transistor: Features Product SummarydiegooliveiraEEPas encore d'évaluation

- MOS 2 Power-Transistor: Features Product SummaryDocument10 pagesMOS 2 Power-Transistor: Features Product SummaryBlendwerk AntikunstPas encore d'évaluation

- 06n03la Mosfet Canal NDocument9 pages06n03la Mosfet Canal NRene RuizPas encore d'évaluation

- IPP60R299CPDocument10 pagesIPP60R299CPfreddyPas encore d'évaluation

- MOS 2 Power-Transistor: Features Product SummaryDocument10 pagesMOS 2 Power-Transistor: Features Product SummaryCesarPas encore d'évaluation

- Ipa90r500c3 - 1.0 Mosfet TransistorDocument10 pagesIpa90r500c3 - 1.0 Mosfet TransistorWilinton PissoPas encore d'évaluation

- Infineon IPP040N06N DS v02 - 02 en - MOS PDFDocument9 pagesInfineon IPP040N06N DS v02 - 02 en - MOS PDFDương Trần BìnhPas encore d'évaluation

- 5 R 140 PDocument10 pages5 R 140 PAnkurPas encore d'évaluation

- Coolmos Power Transistor: Features Product SummaryDocument11 pagesCoolmos Power Transistor: Features Product SummaryrobssonmcPas encore d'évaluation

- MOS 2 Power-Transistor: Features Product SummaryDocument10 pagesMOS 2 Power-Transistor: Features Product SummaryJuan Carlos ChavezPas encore d'évaluation

- Coolmos Power Transistor: Features Product SummaryDocument10 pagesCoolmos Power Transistor: Features Product Summarysunil beedasseePas encore d'évaluation

- Infineon BSC600N25NS3G - DS v02 - 04 en PDFDocument9 pagesInfineon BSC600N25NS3G - DS v02 - 04 en PDFBladePas encore d'évaluation

- Ipd06n03la Ipf06n03la Ips06n03la Ipu06n03laDocument12 pagesIpd06n03la Ipf06n03la Ips06n03la Ipu06n03laVictor QueroPas encore d'évaluation

- Coolmos Power Transistor: Features Product SummaryDocument10 pagesCoolmos Power Transistor: Features Product SummaryjoelpalzaPas encore d'évaluation

- SPP 17N80C3Document10 pagesSPP 17N80C3isaiasvaPas encore d'évaluation

- Coolmos Power Transistor: Features Product SummaryDocument10 pagesCoolmos Power Transistor: Features Product SummaryFélix NicolauPas encore d'évaluation

- Coolmos Power Transistor: Features Product SummaryDocument10 pagesCoolmos Power Transistor: Features Product Summarysigit raharjoPas encore d'évaluation

- Coolmos Power Transistor: Please Note The New Package Dimensions Arccording To PCN 2009-134-ADocument11 pagesCoolmos Power Transistor: Please Note The New Package Dimensions Arccording To PCN 2009-134-AErasmo Franco SPas encore d'évaluation

- SPP B 42N03S2L-13 040604-98441Document11 pagesSPP B 42N03S2L-13 040604-98441run awayPas encore d'évaluation

- IPB042N10N3 IPi045N10N3 IPP045N10N3 042N10N 045N10NDocument11 pagesIPB042N10N3 IPi045N10N3 IPP045N10N3 042N10N 045N10Nyang yangPas encore d'évaluation

- Coolmos Power Transistor: Features Product SummaryDocument10 pagesCoolmos Power Transistor: Features Product Summarysaom09Pas encore d'évaluation

- MOS 3 Power-Transistor: Features Product SummaryDocument11 pagesMOS 3 Power-Transistor: Features Product SummaryDeepak KamalPas encore d'évaluation

- Coolmos Power Transistor: Features Product SummaryDocument10 pagesCoolmos Power Transistor: Features Product SummaryLuis Aguirre CaballeroPas encore d'évaluation

- Infineon SPP04N80C3 DS v02 91 enDocument10 pagesInfineon SPP04N80C3 DS v02 91 entombeanPas encore d'évaluation

- SSP20N60S5Document9 pagesSSP20N60S5Milton AlvesPas encore d'évaluation

- Coolmos Power Transistor: Features Product SummaryDocument10 pagesCoolmos Power Transistor: Features Product SummaryHeeranand ChandwaniPas encore d'évaluation

- MOS Power-Transistor: Features Product SummaryDocument10 pagesMOS Power-Transistor: Features Product SummaryNadeem naderPas encore d'évaluation

- (200V, 110A) IPP110N20NA - IPB107N20NA DS v02 - 01 enDocument10 pages(200V, 110A) IPP110N20NA - IPB107N20NA DS v02 - 01 enbillylu06Pas encore d'évaluation

- Please Note The New Package Dimensions Arccording To PCN 2009-134-ADocument11 pagesPlease Note The New Package Dimensions Arccording To PCN 2009-134-Aالكترونيات يافاPas encore d'évaluation

- Coolmos Power Transistor: Features Product SummaryDocument10 pagesCoolmos Power Transistor: Features Product SummaryJorge Luis Gonzalez CintraPas encore d'évaluation

- Coolmos Power Transistor: Features Product SummaryDocument10 pagesCoolmos Power Transistor: Features Product Summaryاحسن طاہرPas encore d'évaluation

- BSC0923NDI InfineonDocument14 pagesBSC0923NDI InfineonEzequielPas encore d'évaluation

- Datasheet de Um Componente A Qual Não Me Recordo o Nome Agora.Document9 pagesDatasheet de Um Componente A Qual Não Me Recordo o Nome Agora.Anthony AndreyPas encore d'évaluation

- Dsa 00324548Document10 pagesDsa 00324548Herman Girius FonkouaPas encore d'évaluation

- Infineon IPB160N04S2 - 03 DS v01 - 00 enDocument8 pagesInfineon IPB160N04S2 - 03 DS v01 - 00 enMuhammad Januar SusantoPas encore d'évaluation

- SIPMOS Small-Signal-Transistor Technical Data SheetDocument9 pagesSIPMOS Small-Signal-Transistor Technical Data SheetElves MattosPas encore d'évaluation

- MOS 2 Power-Transistor: Features Product SummaryDocument10 pagesMOS 2 Power-Transistor: Features Product SummaryAnderson CarrielPas encore d'évaluation

- SPP08P06P SPB08P06P: Features Product SummaryDocument8 pagesSPP08P06P SPB08P06P: Features Product SummaryСтефан ТасиќPas encore d'évaluation

- MOS 2 Power-Transistor: Features Product SummaryDocument12 pagesMOS 2 Power-Transistor: Features Product SummarySandroCezardeAraujoPas encore d'évaluation

- Sipmos Power Transistor BUZ 100S: V R I V TDocument9 pagesSipmos Power Transistor BUZ 100S: V R I V TlumilanisPas encore d'évaluation

- 032N06NDocument9 pages032N06NPaulo Henrique SPas encore d'évaluation

- Power Transistor: Cool MOS™Document9 pagesPower Transistor: Cool MOS™Juan Carlos Anguiano NegretePas encore d'évaluation

- Infineon IAUC50N08S5L096 DataSheet v01 - 01 ENDocument10 pagesInfineon IAUC50N08S5L096 DataSheet v01 - 01 ENAnjuPas encore d'évaluation

- Sipmos Power Transistor: DS D DS (On)Document9 pagesSipmos Power Transistor: DS D DS (On)valkovPas encore d'évaluation

- Infineon IPD80N04S3 - 06 DS v01 - 00 en PDFDocument9 pagesInfineon IPD80N04S3 - 06 DS v01 - 00 en PDFDanny Alexander Bodegas pinedaPas encore d'évaluation

- Infineon SPW32N50C3 DS v02 - 05 en PDFDocument12 pagesInfineon SPW32N50C3 DS v02 - 05 en PDFHưng HQPas encore d'évaluation

- Infineon_BSO110N03MS_DS_v01_01_en-3160638 (1)Document10 pagesInfineon_BSO110N03MS_DS_v01_01_en-3160638 (1)Junior Souza JrPas encore d'évaluation

- CoolMOS SPA11N60CFDDocument12 pagesCoolMOS SPA11N60CFDĆazim SinanagićPas encore d'évaluation

- 32N50C3 Mos PDFDocument11 pages32N50C3 Mos PDFHưng HQPas encore d'évaluation

- Analyze An Issue 1Document1 pageAnalyze An Issue 1arafatasgharPas encore d'évaluation

- Analyze An Issue Practice Issue 1Document1 pageAnalyze An Issue Practice Issue 1arafatasgharPas encore d'évaluation

- MATLAB Workshop GuideDocument35 pagesMATLAB Workshop GuidearafatasgharPas encore d'évaluation

- InTech-Optimal Design of A Multifunctional Reactor For Catalytic Oxidation of Glucose With Fast Catalyst DeactivationDocument25 pagesInTech-Optimal Design of A Multifunctional Reactor For Catalytic Oxidation of Glucose With Fast Catalyst DeactivationarafatasgharPas encore d'évaluation

- Analyze An ArgumentDocument1 pageAnalyze An ArgumentarafatasgharPas encore d'évaluation

- Sun2014 PDFDocument3 pagesSun2014 PDFarafatasgharPas encore d'évaluation

- Advertisement For The Position of Managing Director NTDCDocument1 pageAdvertisement For The Position of Managing Director NTDCarafatasgharPas encore d'évaluation

- Practice Test 1: Analytical Writing Part 1. Analyze An Issue 30 MinutesDocument1 pagePractice Test 1: Analytical Writing Part 1. Analyze An Issue 30 MinutesMohit SinghalPas encore d'évaluation

- Lab Alert Heating Test - TransformersDocument2 pagesLab Alert Heating Test - TransformersarafatasgharPas encore d'évaluation

- Pension Papers Complete For Fresh RetirementDocument19 pagesPension Papers Complete For Fresh RetirementarafatasgharPas encore d'évaluation

- Ayaat e Mutaarza Aur Un Ka HalDocument418 pagesAyaat e Mutaarza Aur Un Ka HalarafatasgharPas encore d'évaluation

- Distance 12Document4 pagesDistance 12arafatasgharPas encore d'évaluation

- Electronic NotepadDocument17 pagesElectronic Notepadarindom83Pas encore d'évaluation

- From The Heart To The Heart July 2015Document83 pagesFrom The Heart To The Heart July 2015arafatasgharPas encore d'évaluation

- Final Exam LCS ObjectiveDocument2 pagesFinal Exam LCS ObjectivearafatasgharPas encore d'évaluation

- Thesis Text Zina G PDFDocument97 pagesThesis Text Zina G PDFarafatasgharPas encore d'évaluation

- Quickcmc3: Test ModuleDocument4 pagesQuickcmc3: Test ModulearafatasgharPas encore d'évaluation

- 5 TeleroboticsDocument28 pages5 TeleroboticsarafatasgharPas encore d'évaluation

- MCQ Exam Control SystemsDocument12 pagesMCQ Exam Control SystemsarafatasgharPas encore d'évaluation

- Strategic Reserve Time TemplatesDocument2 pagesStrategic Reserve Time TemplatespcmtpcmtPas encore d'évaluation

- Ee 701 Lecture NotesDocument261 pagesEe 701 Lecture NotesarafatasgharPas encore d'évaluation

- Introduction To VLSI SystemDocument16 pagesIntroduction To VLSI SystemPrabakaran RajendranPas encore d'évaluation

- Rad e Rawafiz (Refutation of Ithna Ashari Creed)Document63 pagesRad e Rawafiz (Refutation of Ithna Ashari Creed)arafatasgharPas encore d'évaluation

- Principles of Steady State Converter AnalysisDocument45 pagesPrinciples of Steady State Converter AnalysisarafatasgharPas encore d'évaluation

- Save Your Family Before They BurnDocument79 pagesSave Your Family Before They BurnarafatasgharPas encore d'évaluation

- Reactive SubsumptiveDocument42 pagesReactive SubsumptivearafatasgharPas encore d'évaluation

- Converter ClassificationDocument16 pagesConverter ClassificationarafatasgharPas encore d'évaluation

- Diode Reverse Recovery TimeDocument11 pagesDiode Reverse Recovery TimeshounakroyPas encore d'évaluation

- Converter ClassificationDocument16 pagesConverter ClassificationarafatasgharPas encore d'évaluation

- UAV Course SyllabusDocument3 pagesUAV Course Syllabushindaputra374100% (3)

- RefrigerationDocument11 pagesRefrigerationBroAmirPas encore d'évaluation

- Guide: Royal Lepage Estate Realty BrandDocument17 pagesGuide: Royal Lepage Estate Realty BrandNazek Al-SaighPas encore d'évaluation

- Roof Slab of Guard RoomDocument3 pagesRoof Slab of Guard RoomAditya KumarPas encore d'évaluation

- POSSIBILITIES OF LOW VOLTAGE DC SYSTEMSDocument10 pagesPOSSIBILITIES OF LOW VOLTAGE DC SYSTEMSTTaanPas encore d'évaluation

- Tutorial Ip 2 Win EnglishDocument25 pagesTutorial Ip 2 Win EnglishGarry Zein0% (1)

- Battery Testing and MaintenanceDocument23 pagesBattery Testing and MaintenanceMormor Omerta0% (1)

- 7.qad-Dpr-11 ImteDocument4 pages7.qad-Dpr-11 ImteDhinakaranPas encore d'évaluation

- Library Management System Project ReportDocument50 pagesLibrary Management System Project ReportSURAJ GAMINGPas encore d'évaluation

- Msds Thinner 21-06Document8 pagesMsds Thinner 21-06ridhowibiiPas encore d'évaluation

- Ficha Tecnica 750 GPMDocument156 pagesFicha Tecnica 750 GPMByron Chele0% (2)

- Nazneen Wahab CVDocument5 pagesNazneen Wahab CVRavi MittalPas encore d'évaluation

- Amptec Issue 7Document8 pagesAmptec Issue 7Linda Turner-BoothPas encore d'évaluation

- Cisco As5300 Voice GatewayDocument12 pagesCisco As5300 Voice GatewayAbderrahmane AbdmezianePas encore d'évaluation

- Programmability in SPSS 16 & 17, Jon PeckDocument36 pagesProgrammability in SPSS 16 & 17, Jon PeckJasmin MaricPas encore d'évaluation

- 13-2021مواصفات الفنية لقطع غيار المكيفاتDocument4 pages13-2021مواصفات الفنية لقطع غيار المكيفاتTawfeeq Al-HababbiPas encore d'évaluation

- Nec 2006Document59 pagesNec 2006loots69Pas encore d'évaluation

- Abstracts Book Nanotech 2013Document151 pagesAbstracts Book Nanotech 2013felipe de jesus juarez torresPas encore d'évaluation

- Brief Summary of The Original COCOMO ModelDocument5 pagesBrief Summary of The Original COCOMO ModelTirthajit SinhaPas encore d'évaluation

- Mathcad - Ampacity CalculationDocument76 pagesMathcad - Ampacity CalculationAlex Ribeiro100% (4)

- Power Plant Engineering by G.R.nagpalDocument729 pagesPower Plant Engineering by G.R.nagpalGoutham Peri74% (23)

- RELAY SEEDER PROTECTION GUIDE (P40 Agile CompactDocument23 pagesRELAY SEEDER PROTECTION GUIDE (P40 Agile CompactvinodlifePas encore d'évaluation

- Manuel Solaris Ccds1425-St Ccds1425-Dn Ccds1425-Dnx Ccds1425-Dn36en deDocument42 pagesManuel Solaris Ccds1425-St Ccds1425-Dn Ccds1425-Dnx Ccds1425-Dn36en deAllegra AmiciPas encore d'évaluation

- System Engineering Management Plan (SEMPDocument2 pagesSystem Engineering Management Plan (SEMPKatie WestPas encore d'évaluation

- GRC Fiori End User Guide Final - V2Document75 pagesGRC Fiori End User Guide Final - V2Subhash BharmappaPas encore d'évaluation

- MGS3750 28FDocument4 pagesMGS3750 28FAndi Z Pasuloi PatongaiPas encore d'évaluation

- JupaCreations BWCGDocument203 pagesJupaCreations BWCGsoudrack0% (1)

- Shipping Label GuideDocument41 pagesShipping Label GuidebriggantiiPas encore d'évaluation

- Search Engine Collocations Frequency PhrasesDocument2 pagesSearch Engine Collocations Frequency PhrasesDinda NoviarmachdaPas encore d'évaluation