Académique Documents

Professionnel Documents

Culture Documents

Powermos Transistor Irf730 Avalanche Energy Rated: Features Symbol Quick Reference Data

Transféré par

Carlos Morales AvilaTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Powermos Transistor Irf730 Avalanche Energy Rated: Features Symbol Quick Reference Data

Transféré par

Carlos Morales AvilaDroits d'auteur :

Formats disponibles

Philips Semiconductors Product specification

PowerMOS transistor IRF730

Avalanche energy rated

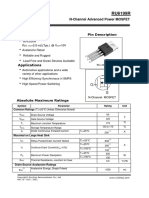

FEATURES SYMBOL QUICK REFERENCE DATA

Repetitive Avalanche Rated d

Fast switching VDSS = 400 V

High thermal cycling performance

Low thermal resistance ID = 7.2 A

g

RDS(ON) 1

s

GENERAL DESCRIPTION PINNING SOT78 (TO220AB)

N-channel, enhancement mode PIN DESCRIPTION

tab

field-effect power transistor,

intended for use in off-line switched 1 gate

mode power supplies, T.V. and

computer monitor power supplies, 2 drain

d.c. to d.c. converters, motor control

circuits and general purpose 3 source

switching applications.

tab drain

The IRF730 is supplied in the 1 23

SOT78 (TO220AB) conventional

leaded package.

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

VDSS Drain-source voltage Tj = 25 C to 150C - 400 V

VDGR Drain-gate voltage Tj = 25 C to 150C; RGS = 20 k - 400 V

VGS Gate-source voltage - 30 V

ID Continuous drain current Tmb = 25 C; VGS = 10 V - 7.2 A

Tmb = 100 C; VGS = 10 V - 4.6 A

IDM Pulsed drain current Tmb = 25 C - 29 A

PD Total dissipation Tmb = 25 C - 125 W

Tj, Tstg Operating junction and - 55 150 C

storage temperature range

AVALANCHE ENERGY LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134)

SYMBOL PARAMETER CONDITIONS MIN. MAX. UNIT

EAS Non-repetitive avalanche Unclamped inductive load, IAS = 4.8 A; - 290 mJ

energy tp = 0.23 ms; Tj prior to avalanche = 25C;

VDD 50 V; RGS = 50 ; VGS = 10 V; refer

to fig:17

EAR Repetitive avalanche energy1 IAR = 7.2 A; tp = 2.5 s; Tj prior to - 9.4 mJ

avalanche = 25C; RGS = 50 ; VGS = 10 V;

refer to fig:18

IAS, IAR Repetitive and non-repetitive - 7.2 A

avalanche current

1 pulse width and repetition rate limited by Tj max.

March 1999 1 Rev 1.000

Philips Semiconductors Product specification

PowerMOS transistor IRF730

Avalanche energy rated

THERMAL RESISTANCES

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

Rth j-mb Thermal resistance junction - - 1 K/W

to mounting base

Rth j-a Thermal resistance junction in free air - 60 - K/W

to ambient

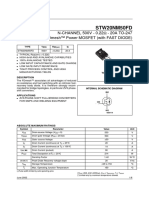

ELECTRICAL CHARACTERISTICS

Tj = 25 C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

V(BR)DSS Drain-source breakdown VGS = 0 V; ID = 0.25 mA 400 - - V

voltage

V(BR)DSS / Drain-source breakdown VDS = VGS; ID = 0.25 mA - 0.1 - %/K

Tj voltage temperature

coefficient

RDS(ON) Drain-source on resistance VGS = 10 V; ID = 3.6 A - 0.7 1

VGS(TO) Gate threshold voltage VDS = VGS; ID = 0.25 mA 2.0 3.0 4.0 V

gfs Forward transconductance VDS = 30 V; ID = 3.6 A 2 4 - S

IDSS Drain-source leakage currentVDS = 400 V; VGS = 0 V - 1 25 A

VDS = 320 V; VGS = 0 V; Tj = 125 C - 30 250 A

IGSS Gate-source leakage current VGS = 30 V; VDS = 0 V - 10 200 nA

Qg(tot) Total gate charge ID = 7.2 A; VDD = 320 V; VGS = 10 V - 52 62 nC

Qgs Gate-source charge - 3 5 nC

Qgd Gate-drain (Miller) charge - 26 30 nC

td(on) Turn-on delay time VDD = 200 V; RD = 27 ; - 12 - ns

tr Turn-on rise time RG = 12 - 33 - ns

td(off) Turn-off delay time - 93 - ns

tf Turn-off fall time - 42 - ns

Ld Internal drain inductance Measured from tab to centre of die - 3.5 - nH

Ld Internal drain inductance Measured from drain lead to centre of die - 4.5 - nH

Ls Internal source inductance Measured from source lead to source - 7.5 - nH

bond pad

Ciss Input capacitance VGS = 0 V; VDS = 25 V; f = 1 MHz - 620 - pF

Coss Output capacitance - 108 - pF

Crss Feedback capacitance - 63 - pF

SOURCE-DRAIN DIODE RATINGS AND CHARACTERISTICS

Tj = 25 C unless otherwise specified

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT

IS Continuous source current Tmb = 25C - - 7.2 A

(body diode)

ISM Pulsed source current (body Tmb = 25C - - 29 A

diode)

VSD Diode forward voltage IS = 7.2 A; VGS = 0 V - - 1.2 V

trr Reverse recovery time IS = 7.2 A; VGS = 0 V; dI/dt = 100 A/s - 270 - ns

Qrr Reverse recovery charge - 3.3 - C

March 1999 2 Rev 1.000

Philips Semiconductors Product specification

PowerMOS transistor IRF730

Avalanche energy rated

PD% Normalised Power Derating Zth j-mb, Transient thermal impedance (K/W) PHP3N60

120 1

D = 0.5

110

100 0.2

90

0.1

80 0.1 0.05

70

0.02

60

50

40 0.01

single pulse PD tp tp

30 D=

T

20

10 T

t

0 0.001

0 20 40 60 80 100 120 140 1us 10us 100us 1ms 10ms 100ms 1s

Tmb / C tp, pulse width (s)

Fig.1. Normalised power dissipation. Fig.4. Transient thermal impedance.

PD% = 100PD/PD 25 C = f(Tmb) Zth j-mb = f(t); parameter D = tp/T

ID% Normalised Current Derating ID, Drain current (Amps) PHP5N40

120 20

Tj = 25 C 10 V

110

7V

100

90 15 6.5 V

80

70 6V

60 10

50 5.5 V

40 5V

30 5

VGS = 4.5 V

20

10

0 0

0 20 40 60 80 100 120 140 0 5 10 15 20 25 30

Tmb / C VDS, Drain-Source voltage (Volts)

Fig.2. Normalised continuous drain current. Fig.5. Typical output characteristics.

ID% = 100ID/ID 25 C = f(Tmb); conditions: VGS 10 V ID = f(VDS); parameter VGS

ID, Drain current (Amps) PHP3N50 RDS(on), Drain-Source on resistance (Ohms) PHP5N40

100 2.5

4.5 V 5V 5.5 V VGS = 6 V Tj = 25 C

ID

S/ 2

6.5 V

VD

) =

ON tp = 10 us 7V

10 S( 10 V

RD 1.5

100 us

1

1 1 ms

DC 10 ms

0.5

0.1 0

10 100 1000 10000 0 5 10 15 20

VDS, Drain-source voltage (Volts) ID, Drain current (Amps)

Fig.3. Safe operating area. Tmb = 25 C Fig.6. Typical on-state resistance.

ID & IDM = f(VDS); IDM single pulse; parameter tp RDS(ON) = f(ID); parameter VGS

March 1999 3 Rev 1.000

Philips Semiconductors Product specification

PowerMOS transistor IRF730

Avalanche energy rated

ID, Drain current (Amps) PHP5N40 VGS(TO) / V

20

VDS > ID x RDS(on)max max.

Tj = 25 C 4

15 typ.

3

Tj = 150 C

min.

10

2

5 1

0 0

0 2 4 6 8 10 -60 -40 -20 0 20 40 60 80 100 120 140

VGS, Gate-Source voltage (Volts) Tj / C

Fig.7. Typical transfer characteristics. Fig.10. Gate threshold voltage.

ID = f(VGS); parameter Tj VGS(TO) = f(Tj); conditions: ID = 0.25 mA; VDS = VGS

gfs, Transconductance (S) PHP5N40 ID / A SUB-THRESHOLD CONDUCTION

7 1E-01

VDS > ID x RDS(on)max

Tj = 25 C

6

1E-02

5

150 C 2% typ 98 %

1E-03

4

3 1E-04

2

1E-05

1

0 1E-06

0 5 10 15 20 0 1 2 3 4

ID, Drain current (A) VGS / V

Fig.8. Typical transconductance. Fig.11. Sub-threshold drain current.

gfs = f(ID); parameter Tj ID = f(VGS); conditions: Tj = 25 C; VDS = VGS

a Normalised RDS(ON) = f(Tj) Junction capacitances (pF) PHP5N40

1000

Ciss

2

100

1 Coss

Crss

0

-60 -40 -20 0 20 40 60 80 100 120 140 10

1 10 100 1000

Tj / C VDS, Drain-Source voltage (Volts)

Fig.9. Normalised drain-source on-state resistance. Fig.12. Typical capacitances, Ciss, Coss, Crss.

a = RDS(ON)/RDS(ON)25 C = f(Tj); ID = 3.6 A; VGS = 10 V C = f(VDS); conditions: VGS = 0 V; f = 1 MHz

March 1999 4 Rev 1.000

Philips Semiconductors Product specification

PowerMOS transistor IRF730

Avalanche energy rated

VGS, Gate-Source voltage (Volts) PHP5N40 IF, Source-Drain diode current (Amps) PHP5N40

15 20

ID = 7.2 A VGS = 0 V

240 V

Tj = 25 C

80 V VDD = 320 V 15

10

10

150 C Tj = 25 C

5

5

0 0

0 10 20 30 40 50 60 70 80 0 0.2 0.4 0.6 0.8 1 1.2 1.4

Qg, Gate charge (nC) VSDS, Source-Drain voltage (Volts)

Fig.13. Typical turn-on gate-charge characteristics. Fig.16. Source-Drain diode characteristic.

VGS = f(QG); parameter VDS IF = f(VSDS); parameter Tj

Switching times (ns) PHP5N40

1000

VDD = 200 V Non-repetitive Avalanche current, IAS (A)

VGS = 10 V 10

RD = 27 Ohms

Tj = 25 C 25 C

Tj prior to avalanche = 125 C

100 td(off) 1

VDS

tf

tp

tr

ID

PHP7N40E

0.1

td(on) 1E-06 1E-05 1E-04 1E-03 1E-02

10

0 10 20 30 40 50 60

RG, Gate resistance (Ohms) Avalanche time, tp (s)

Fig.14. Typical switching times; td(on), tr, td(off), tf = f(RG) Fig.17. Maximum permissible non-repetitive

avalanche current (IAS) versus avalanche time (tp);

unclamped inductive load

Normalised Drain-source breakdown voltage

1.15

V(BR)DSS @ Tj

V(BR)DSS @ 25 C

Maximum Repetitive Avalanche Current, IAR (A)

10

1.1

Tj prior to avalanche = 25 C

1.05 125 C

1

0.95 0.1

0.9 PHP7N40E

0.01

0.85 1E-06 1E-05 1E-04 1E-03 1E-02

-100 -50 0 50 100 150

Tj, Junction temperature (C)

Avalanche time, tp (s)

Fig.15. Normalised drain-source breakdown voltage; Fig.18. Maximum permissible repetitive avalanche

V(BR)DSS/V(BR)DSS 25 C = f(Tj) current (IAR) versus avalanche time (tp)

March 1999 5 Rev 1.000

Philips Semiconductors Product specification

PowerMOS transistor IRF730

Avalanche energy rated

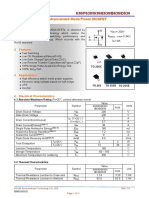

MECHANICAL DATA

Plastic single-ended package; heatsink mounted; 1 mounting hole; 3-lead TO-220 SOT78

E A

P A1

q

D1

L2(1) L1

Q

b1

L

1 2 3

b c

e e

0 5 10 mm

scale

DIMENSIONS (mm are the original dimensions)

(1)

UNIT A A1 b b1 c D D1 E e L L1 L2 P q Q

max.

mm 4.5 1.39 0.9 1.3 0.7 15.8 6.4 10.3 15.0 3.30 3.8 3.0 2.6

2.54 3.0

4.1 1.27 0.7 1.0 0.4 15.2 5.9 9.7 13.5 2.79 3.6 2.7 2.2

Note

1. Terminals in this zone are not tinned.

OUTLINE REFERENCES EUROPEAN

ISSUE DATE

VERSION IEC JEDEC EIAJ PROJECTION

SOT78 TO-220 97-06-11

Fig.19. SOT78 (TO220AB); pin 2 connected to mounting base (Net mass:2g)

Notes

1. This product is supplied in anti-static packaging. The gate-source input must be protected against static

discharge during transport or handling.

2. Refer to mounting instructions for SOT78 (TO220AB) package.

3. Epoxy meets UL94 V0 at 1/8".

March 1999 6 Rev 1.000

Philips Semiconductors Product specification

PowerMOS transistor IRF730

Avalanche energy rated

DEFINITIONS

Data sheet status

Objective specification This data sheet contains target or goal specifications for product development.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Product specification This data sheet contains final product specifications.

Limiting values

Limiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one

or more of the limiting values may cause permanent damage to the device. These are stress ratings only and

operation of the device at these or at any other conditions above those given in the Characteristics sections of

this specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information

Where application information is given, it is advisory and does not form part of the specification.

Philips Electronics N.V. 1999

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the

copyright owner.

The information presented in this document does not form part of any quotation or contract, it is believed to be

accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any

consequence of its use. Publication thereof does not convey nor imply any license under patent or other

industrial or intellectual property rights.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices or systems where malfunction of these

products can be reasonably expected to result in personal injury. Philips customers using or selling these products

for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting

from such improper use or sale.

March 1999 7 Rev 1.000

Vous aimerez peut-être aussi

- Powermos Transistors Irfp460 Avalanche Energy Rated: Features Symbol Quick Reference DataDocument7 pagesPowermos Transistors Irfp460 Avalanche Energy Rated: Features Symbol Quick Reference DataRio CandrapurwitaPas encore d'évaluation

- Powermos Transistors Php6N60E, Phb6N60E Avalanche Energy RatedDocument9 pagesPowermos Transistors Php6N60E, Phb6N60E Avalanche Energy RatedEmmanuel ZambranoPas encore d'évaluation

- IRF840 AdvancedPowerElectronicsDocument4 pagesIRF840 AdvancedPowerElectronicssheikh sheharyarPas encore d'évaluation

- N-Channel Trenchmos Transistor Irf530N: Features Symbol Quick Reference DataDocument7 pagesN-Channel Trenchmos Transistor Irf530N: Features Symbol Quick Reference DataLenin Cadillo GutierrezPas encore d'évaluation

- N-Channel Trenchmos Transistor Phx9Nq20T, Phf9Nq20T: Features Symbol Quick Reference DataDocument10 pagesN-Channel Trenchmos Transistor Phx9Nq20T, Phf9Nq20T: Features Symbol Quick Reference DatareparacionesdmaPas encore d'évaluation

- N-Channel Enhancement Mode Irfz48N Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz48N Trenchmos Transistor: General Description Quick Reference DataNixon MaldonadoPas encore d'évaluation

- N-Channel Trenchmos Transistor Psmn040-200W: Features Symbol Quick Reference DataDocument7 pagesN-Channel Trenchmos Transistor Psmn040-200W: Features Symbol Quick Reference DataRobert sibueaPas encore d'évaluation

- IRFZ24NDocument8 pagesIRFZ24NarcatusPas encore d'évaluation

- N-Channel Enhancement Mode Irfz44N Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz44N Trenchmos Transistor: General Description Quick Reference DataingucvPas encore d'évaluation

- Irf840 PDFDocument8 pagesIrf840 PDFAnonymous AssOOhqigPas encore d'évaluation

- IRF840Document8 pagesIRF840Apc CamPas encore d'évaluation

- SMK0860P: Switching Regulator ApplicationsDocument8 pagesSMK0860P: Switching Regulator ApplicationsBilier Diaz CabreraPas encore d'évaluation

- STP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetDocument8 pagesSTP40NF10L: N-CHANNEL 100V - 0.028 - 40A TO-220 Low Gate Charge Stripfet™ Power MosfetCarlos A AvilaPas encore d'évaluation

- IRF540Document9 pagesIRF540paul mathewPas encore d'évaluation

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectPas encore d'évaluation

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFRubenPas encore d'évaluation

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFbaharPas encore d'évaluation

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectPas encore d'évaluation

- Irf 540Document8 pagesIrf 540Tom TweedlePas encore d'évaluation

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFbaharPas encore d'évaluation

- N-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.055 - 22A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetCode Main ProjectPas encore d'évaluation

- IRF540 ST PDFDocument8 pagesIRF540 ST PDFbaharPas encore d'évaluation

- Buk455 200a PDFDocument8 pagesBuk455 200a PDFCarl Conter OnderPas encore d'évaluation

- Osg 65 R 125 HFDocument10 pagesOsg 65 R 125 HFmrromocom7Pas encore d'évaluation

- Enhancement Mode N-Channel Power MOSFET: OSG65R900xTFDocument10 pagesEnhancement Mode N-Channel Power MOSFET: OSG65R900xTFCube7 Geronimo100% (1)

- K2611 K2611 K2611 K2611: FeaturesDocument7 pagesK2611 K2611 K2611 K2611: FeaturesAndrew BanezPas encore d'évaluation

- K2611 K2611 K2611 K2611: FeaturesDocument7 pagesK2611 K2611 K2611 K2611: Featureskaung kyel zin aung zaw moePas encore d'évaluation

- RU6199R RuichipsDocument9 pagesRU6199R RuichipsAndres padillaPas encore d'évaluation

- 09 N 70 IDocument4 pages09 N 70 IIwan YogyaPas encore d'évaluation

- STK0765BF: Switching Regulator Applications FeaturesDocument8 pagesSTK0765BF: Switching Regulator Applications FeaturesHumberto AguilarPas encore d'évaluation

- STK0765BF: Switching Regulator Applications FeaturesDocument8 pagesSTK0765BF: Switching Regulator Applications Featuresmaksyd2Pas encore d'évaluation

- Important Notice: Kind RegardsDocument8 pagesImportant Notice: Kind Regardscarlosjamal95Pas encore d'évaluation

- Powermos Transistor Buk475-200A/B Isolated Version of Buk455-200A/BDocument7 pagesPowermos Transistor Buk475-200A/B Isolated Version of Buk455-200A/Bmaykel valdezPas encore d'évaluation

- Buz84 PDFDocument3 pagesBuz84 PDFmundomusicalmeriaPas encore d'évaluation

- N-Channel Advanced Power MOSFET Pin Description Features: D D D D D D DDocument8 pagesN-Channel Advanced Power MOSFET Pin Description Features: D D D D D D DJose Manuel DuartePas encore d'évaluation

- Advanced Power Electronics Corp.: AP2761I-ADocument4 pagesAdvanced Power Electronics Corp.: AP2761I-AAbelito JesusPas encore d'évaluation

- AP9972GSPDocument6 pagesAP9972GSPSantiago DiosdadoPas encore d'évaluation

- Advanced Power Electronics Corp.: AP2761I-ADocument4 pagesAdvanced Power Electronics Corp.: AP2761I-AM_YYYYPas encore d'évaluation

- Advanced Power Electronics Corp.: AP0403GHDocument5 pagesAdvanced Power Electronics Corp.: AP0403GHIulius CezarPas encore d'évaluation

- IRFP450Document8 pagesIRFP450Erick DavidPas encore d'évaluation

- KIA KIA KIA: 1.descriptionDocument5 pagesKIA KIA KIA: 1.descriptionzakreaPas encore d'évaluation

- Stw20Nm50Fd: N-Channel 500V - 0.22 - 20A To-247 Fdmesh™ Power Mosfet (With Fast Diode)Document8 pagesStw20Nm50Fd: N-Channel 500V - 0.22 - 20A To-247 Fdmesh™ Power Mosfet (With Fast Diode)Alassane Djido SowPas encore d'évaluation

- IRF820Document8 pagesIRF820ЫманалыPas encore d'évaluation

- Datasheet F630Document11 pagesDatasheet F630Lâm Bá NhãPas encore d'évaluation

- 2017032716183628Document9 pages2017032716183628МВВPas encore d'évaluation

- Smps Mosfet: IRF3515S IRF3515LDocument10 pagesSmps Mosfet: IRF3515S IRF3515LHaris FPas encore d'évaluation

- 70L02GHDocument8 pages70L02GHJtzabalaPas encore d'évaluation

- Buk9635-100a 1Document7 pagesBuk9635-100a 1Raul OsoPas encore d'évaluation

- N-CHANNEL 100V - 0.115 - 10A TO-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument8 pagesN-CHANNEL 100V - 0.115 - 10A TO-220 Low Gate Charge Stripfet™ Ii Power Mosfetfabio_sg100% (1)

- 9 N 90 eDocument7 pages9 N 90 eMarcelo Lopes NunesPas encore d'évaluation

- MOSFET 200V N-Channel RTW50N20D/RTA50N20D Spec SheetDocument10 pagesMOSFET 200V N-Channel RTW50N20D/RTA50N20D Spec SheetRaghunandan SubramanianPas encore d'évaluation

- Advanced Power Electronics Corp.: DescriptionDocument4 pagesAdvanced Power Electronics Corp.: DescriptionAntonio UrribarriPas encore d'évaluation

- NCE0218 Pb Free 18A 200V N-Channel Power MOSFETDocument7 pagesNCE0218 Pb Free 18A 200V N-Channel Power MOSFETRichard MachadoPas encore d'évaluation

- N-Channel Enhancement Mode Irfz44Ns Trenchmos Transistor: General Description Quick Reference DataDocument8 pagesN-Channel Enhancement Mode Irfz44Ns Trenchmos Transistor: General Description Quick Reference DataDaniel Orlando Carballo FernándezPas encore d'évaluation

- Datasheet RU190N10RDocument11 pagesDatasheet RU190N10Ralberto castañoPas encore d'évaluation

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsD'EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsPas encore d'évaluation

- Carrito Control RemotoDocument1 pageCarrito Control RemotoCarlos Morales AvilaPas encore d'évaluation

- Earth Station High Power AmplifiersDocument2 pagesEarth Station High Power AmplifiersCarlos Morales AvilaPas encore d'évaluation

- Earth Station High Power AmplifiersDocument7 pagesEarth Station High Power AmplifiersCarlos Burguillos FajardoPas encore d'évaluation

- Quiz Capitulo 6Document5 pagesQuiz Capitulo 6Carlos Morales AvilaPas encore d'évaluation

- Handbook of Operational Amplifier ApplicationsDocument94 pagesHandbook of Operational Amplifier Applicationshermiit89% (9)

- AP0141 SPICE Model Creation From User DataDocument23 pagesAP0141 SPICE Model Creation From User DatadrakenhavenPas encore d'évaluation

- Computer Book MaterialDocument69 pagesComputer Book MaterialAqib Asad100% (1)

- HCD-GRX10AV/HCD-RXD10AV Service ManualDocument98 pagesHCD-GRX10AV/HCD-RXD10AV Service ManualubdubPas encore d'évaluation

- PDFDocument6 pagesPDFridhoazhar megantaraPas encore d'évaluation

- Wireless World 1948 12Document78 pagesWireless World 1948 12Jan PranPas encore d'évaluation

- HAVSO2S0022GSMDocument2 pagesHAVSO2S0022GSMNISHANPas encore d'évaluation

- EC6502 Principles of Digital Signal ProcessingDocument320 pagesEC6502 Principles of Digital Signal ProcessinglazezijoPas encore d'évaluation

- Diode ExercisesDocument5 pagesDiode ExercisesbruhPas encore d'évaluation

- M863G Motherboard Manual ECS PCChips 863G 1 5E EnglishDocument38 pagesM863G Motherboard Manual ECS PCChips 863G 1 5E EnglishMeire Ellen MonteiroPas encore d'évaluation

- AMZ Motorola CP200 Radio XLS SpecsDocument2 pagesAMZ Motorola CP200 Radio XLS SpecsAmerizon WirelessPas encore d'évaluation

- Gpib and Ieee 488Document17 pagesGpib and Ieee 488communicationridersPas encore d'évaluation

- 05 - List of SymbolsDocument6 pages05 - List of Symbolsrajath RaviPas encore d'évaluation

- Cadence Tutorial C: Simulating DC and Timing CharacteristicsDocument10 pagesCadence Tutorial C: Simulating DC and Timing CharacteristicsMd. HasanuzzamanPas encore d'évaluation

- Example-1: Power AmplifierDocument2 pagesExample-1: Power AmplifierKahina ZitouniPas encore d'évaluation

- Programador AVR PDFDocument7 pagesProgramador AVR PDFGustavoFloresPas encore d'évaluation

- Indian Railway Standard for Universal Fail-Safe Block InterfaceDocument29 pagesIndian Railway Standard for Universal Fail-Safe Block Interfacema_purwoadiPas encore d'évaluation

- G7 8 CSS Explo Module 4Document27 pagesG7 8 CSS Explo Module 4Heart NicolePas encore d'évaluation

- Hexagonal Microstrip Patch AntennaDocument2 pagesHexagonal Microstrip Patch AntennaAli ZaidiPas encore d'évaluation

- Leader lsg-17 0.1..150mhz Signal GeneratorDocument13 pagesLeader lsg-17 0.1..150mhz Signal GeneratorTheodor EikePas encore d'évaluation

- Communication Systems Fundamentals and Design Methods PDFDocument2 pagesCommunication Systems Fundamentals and Design Methods PDFAngelaPas encore d'évaluation

- Assignment 1Document6 pagesAssignment 1Kavinesh Ananthan100% (1)

- STANAG 4203 HF Radio Conformance Test ProceduresDocument91 pagesSTANAG 4203 HF Radio Conformance Test ProceduresCường NguyễnPas encore d'évaluation

- Interfacing 8255 Ports as Input and OutputDocument4 pagesInterfacing 8255 Ports as Input and OutputPon KrithikhaPas encore d'évaluation

- Curriculum 2005Document67 pagesCurriculum 2005simardeepsingh3Pas encore d'évaluation

- Fully Supported PRO Audio (And Video) Hardware Interfaces For The AV LinuxDocument26 pagesFully Supported PRO Audio (And Video) Hardware Interfaces For The AV LinuxvgkkctndPas encore d'évaluation

- K35 Touchpanel ManualDocument15 pagesK35 Touchpanel ManualSamuel YipPas encore d'évaluation

- CADDY Users ManualDocument12 pagesCADDY Users ManualSara MckinneyPas encore d'évaluation

- 80 Watt KU Band BUC ManualDocument53 pages80 Watt KU Band BUC ManualspeedyeduPas encore d'évaluation

- Ee3311 SyllabusDocument6 pagesEe3311 Syllabuskumarsanjeev.net9511Pas encore d'évaluation