Académique Documents

Professionnel Documents

Culture Documents

TC7129 Multimeter

Transféré par

FelipePerezCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

TC7129 Multimeter

Transféré par

FelipePerezDroits d'auteur :

Formats disponibles

TC7129

4-1/2 Digit Analog-to-Digital Converters with

On-Chip LCD Drivers

Features: General Description:

Count Resolution: 19,999 The TC7129 is a 4-1/2 digit Analog-to-Digital Converter

Resolution on 200 mV Scale: 10 V (ADC) that directly drives a multiplexed Liquid Crystal

True Differential Input and Reference Display (LCD). Fabricated in high-performance, low-

power CMOS, the TC7129 ADC is designed specifi-

Low Power Consumption: 500 A at 9V

cally for high-resolution, battery-powered digital multi-

Direct LCD Driver for 4-1/2 Digits, Decimal Points, meter applications. The traditional dual-slope method

Low Battery Indicator, and Continuity Indicator of A/D conversion has been enhanced with a succes-

Overrange and Underrange Outputs sive integration technique to produce readings accu-

Range Select Input: 10:1 rate to better than 0.005% of full-scale and resolution

High Common Mode Rejection Ratio: 110 dB down to 10 V per count.

External Phase Compensation Not Required The TC7129 includes features important to multimeter

applications. It detects and indicates low battery condi-

Applications: tion. A continuity output drives an annunciator on the

display and can be used with an external driver to sound

Full-Featured Multimeters an audible alarm. Overrange and underrange outputs,

Digital Measurement Devices along with a range-change input, provide the ability to

create auto-ranging instruments. For snapshot read-

Device Selection Table ings, the TC7129 includes a latch-and-hold input to

freeze the present reading. This combination of features

Package Pin Temperature makes the TC7129 the ideal choice for full-featured

Package

Code Layout Range

multimeter and digital measurement applications.

TC7129CPL Normal 40-Pin PDIP 0C to +70C

TC7129CKW Formed 44-Pin PQFP 0C to +70C

TC7129CLW 44-Pin PLCC 0C to +70C

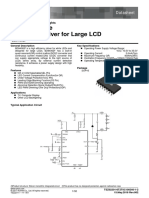

Typical Application

Low Battery Continuity

V+

5 pF

20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

TC7129 120 kHz

21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

330 k

*

0.1 F 10 pF

+ 0.1

1 F F 20 0.1 F

k

150 k V+

+ 10 k

9V 100 k

+

VIN

*Note: RC network between pins 26 and 28 is not required.

2002-2012 Microchip Technology Inc. DS21459E-page 1

TC7129

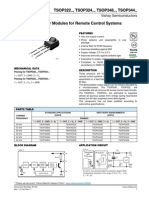

Package Types

40-Pin PDIP

OSC1 1 40 OSC2

OSC3 2 39 DP1

ANNUNICATOR 3 38 DP2

B1, C1, CONT 4 37 RANGE

A1, G1, D1 5 36 DGND

F1, E1, DP1 6 35 REF LO

B2, C2, LO BATT 7 34 REF HI

A2, G2, D2 8 33 IN HI

F2, E2, DP2 9 32 IN LO

B3, C3, MINUS 10 TC7129CPL 31 BUFF

Display A3, G3, D3 11 30 CREF-

Output

Lines F3, E3, DP3 12 29 CREF+

B4, C4, BC5 13 28 COMMON

A4, G4, D4 14 27 CONTINUITY

F4, E4, DP4 15 26 INT OUT

BP3 16 25 INT IN

BP2 17 24 V+

BP1 18 23 V-

VDISP 19 22 LATCH/HOLD

DP4/OR 20 21 DP3/UR

ANNUNCIATOR

44-Pin QFP 44-Pin PLCC

ANNUNCIATOR

B1, C1, CONT

B1, C1, CONT

A1, G1, D1

A1, G1, D1

RANGE

DGND

RANGE

OSC3

OSC1

OSC2

DGND

OSC3

OSC1

OSC2

DP1

DP2

NC

DP1

DP2

NC

6 5 4 3 2 1 44 43 42 41 40

44 43 42 41 40 39 38 37 36 35 34

F1, E1, DP1 1 33 REF LO F1, E1, DP1 7 39 REF LO

B2, C2, BATT 2 32 REF HI B2, C2, BATT 8 38 REF HI

A2, G2, D2 3 31 IN HI A2, G2, D2 9 37 IN HI

F2, E2, DP2 4 30 IN LO F2, E2, DP2 10 36 IN LO

B3, C3, MINUS 5 29 BUFF B3, C3, MINUS 11 35 BUFF

NC 6 28 NC NC 12 34 NC

TC7129CKW TC7129CLW

A3, G3, D3 7 27 CREF- A3, G3, D3 13 33 CREF-

F3, E3, DP3 8 26 CREF+ F3, E3, DP3 14 32 CREF+

B4, C4, BC5 9 25 COMMON B4, C4, BC5 15 31 COMMON

A4, G4, D4 10 24 CONTINUITY A4, G4, D4 16 30 CONTINUITY

F4, E4, DP4 11 23 INT OUT F4, E4, DP4 17 29 INT OUT

18 19 20 21 22 23 24 25 26 27 28

12 13 14 15 16 17 18 19 20 21 22

INT IN

DP4/OR

NC

DP3/UR

V+

BP1

V-

BP3

BP2

VDISP

LATCH/HOLD

INT IN

DP4/OR

NC

DP3/UR

V+

BP1

BP3

BP2

V-

LATCH/HOLD

VDISP

DS21459E-page 2 2002-2012 Microchip Technology Inc.

TC7129

1.0 ELECTRICAL *Stresses above those listed under Absolute Maximum

Ratings may cause permanent damage to the device. These

CHARACTERISTICS are stress ratings only and functional operation of the device

at these or any other conditions above those indicated in the

Absolute Maximum Ratings* operation sections of the specifications is not implied.

Exposure to Absolute Maximum Rating conditions for

Supply Voltage (V+ to V-)....................................... 15V extended periods may affect device reliability.

Reference Voltage (REF HI or REF LO) ........ V+ to V

Input Voltage (IN HI or IN LO) (Note 1).......... V+ to V

VDISP .......................................... V+ to (DGND 0.3V)

Digital Input (Pins 1, 2, 19, 20,

21, 22, 27, 37, 39, 40) .......................... DGND to V+

Analog Input (Pins 25, 29, 30) ....................... V+ to V

Package Power Dissipation (TA 70C)

Plastic DIP ..................................................... 1.23W

PLCC ............................................................. 1.23W

Plastic QFP .................................................... 1.00W

Operating Temperature Range ............... 0C to +70C

Storage Temperature Range.............. -65C to +150C

TC7129 ELECTRICAL SPECIFICATIONS

Electrical Characteristics: V+ to V = 9V, VREF = 1V, TA = +25C, fCLK = 120 kHz, unless otherwise indicated.

Pin numbers refer to 40-pin DIP.

Symbol Parameter Min Typ Max Unit Test Conditions

Input

Zero Input Reading 0000 0000 +0000 Counts VIN = 0V, 200 mV scale

Zero Reading Drift 0.5 V/C VIN = 0V, 0C < TA < +70C

Ratiometric Reading 9996 10000 Counts VIN = VREF = 1000 mV,

Range = 2V

Range Change Accuracy 0.9999 1.0000 1.0001 Ratio VIN = 1V on High Range,

VIN = 0.1V on Low Range

RE Rollover Error 1 2 Counts VIN = VIN+ = 199 mV

NL Linearity Error 1 Counts 200mV Scale

CMRR Common Mode Rejection Ratio 110 dB VCM = 1V, VIN = 0V,

200 mV scale

CMVR Common Mode Voltage Range (V-) + V VIN = 0V

1.5

(V+) 1 V 200 mV scale

eN Noise (Peak-to-Peak Value not 14 VP-P VIN = 0V

Exceeded 95% of Time) 200 mV scale

IIN Input Leakage Current 1 10 pA VIN = 0V, pins 32, 33

Scale Factor Temperature 2 7 ppm/C VIN = 199 mV,

Coefficient 0C < TA < +70C

External VREF = 0 ppm/C

Note 1: Input voltages may exceed supply voltages, provided input current is limited to 400 A. Currents above

this value may result in invalid display readings, but will not destroy the device if limited to 1 mA.

Dissipation ratings assume device is mounted with all leads soldered to printed circuit board.

2002-2012 Microchip Technology Inc. DS21459E-page 3

TC7129

TC7129 ELECTRICAL SPECIFICATIONS (CONTINUED)

Electrical Characteristics: V+ to V = 9V, VREF = 1V, TA = +25C, fCLK = 120 kHz, unless otherwise indicated.

Pin numbers refer to 40-pin DIP.

Symbol Parameter Min Typ Max Unit Test Conditions

Power

VCOM Common Voltage 2.8 3.2 3.5 V V+ to pin 28

Common Sink Current 0.6 mA Common = +0.1V

Common Source Current 10 A Common = -0.1V

DGND Digital Ground Voltage 4.5 5.3 5.8 V V+ to pin 36, V+ to V = 9V

Sink Current 1.2 mA DGND = +0.5V

Supply Voltage Range 6 9 12 V V+ to V

IS Supply Current Excluding 0.8 1.3 mA V+ to V = 9V

Common Current

fCLK Clock Frequency 120 360 kHz

VDISP Resistance 50 k VDISP to V+

Low Battery Flag Activation 6.3 7.2 7.7 V V+ to V

Voltage

Digital

Continuity Comparator Threshold 100 200 mV VOUT pin 27 = High

Voltages 200 400 mV VOUT pin 27 = Low

Pull-down Current 2 10 A Pins 37, 38, 39

Weak Output Current 3/3 A Pins 20, 21 sink/source

Sink/Source 3/9 A Pin 27 sink/source

Pin 22 Source Current 40 A

Pin 22 Sink Current 3 A

Note 1: Input voltages may exceed supply voltages, provided input current is limited to 400 A. Currents above

this value may result in invalid display readings, but will not destroy the device if limited to 1 mA.

Dissipation ratings assume device is mounted with all leads soldered to printed circuit board.

DS21459E-page 4 2002-2012 Microchip Technology Inc.

TC7129

2.0 PIN DESCRIPTIONS

Descriptions of the pins are listed in Table 2-1.

TABLE 2-1: PIN FUNCTION TABLE

Pin No. Pin No. Pin No.

Symbol Function

40-Pin PDIP 44-Pin PQFP 44-Pin PLCC

1 40 2 OSC1 Input to first clock inverter.

2 41 3 OSC3 Output of second clock inverter.

3 42 4 ANNUNCIATOR Backplane square wave output for driving annunciators.

4 43 5 B1, C1, CONT Output to display segments.

5 44 6 A1, G1, D1 Output to display segments.

6 1 7 F1, E1, DP1 Output to display segments.

7 2 8 B2 , C 2 , Output to display segments.

LO BATT

8 3 9 A2, G2, D2 Output to display segments.

9 4 10 F2, E2, DP2 Output to display segments.

10 5 11 B3, C3, MINUS Output to display segments.

11 7 13 A3, G3, D3 Output to display segments.

12 8 14 F3, E3, DP3 Output to display segments.

13 9 15 B4, C4, BC5 Output to display segments.

14 10 16 A4, D4, G4 Output to display segments.

15 11 17 F4, E4, DP4 Output to display segments.

16 12 18 BP3 Backplane #3 output to display.

17 13 19 BP2 Backplane #2 output to display.

18 14 20 BP1 Backplane #1 output to display.

19 15 21 VDISP Negative rail for display drivers.

20 16 22 DP4/OR Input: When high, turns on most significant decimal point.

Output: Pulled high when result count exceeds 19,999.

21 18 24 DP3/UR Input: Second-most significant decimal point on when high.

Output: Pulled high when result count is less than 1000.

22 19 25 LATCH/HOLD Input: When floating, ADC operates in Free Run mode. When

pulled high, the last displayed reading is held. When pulled low,

the result counter contents are shown incrementing during the

de-integrate phase of cycle.

Output: Negative going edge occurs when the data latches are

updated. Can be used for converter status signal.

23 20 26 V Negative power supply terminal.

24 21 27 V+ Positive power supply terminal and positive rail for display

drivers.

25 22 28 INT IN Input to integrator amplifier.

26 23 29 INT OUT Output of integrator amplifier.

27 24 30 CONTINUITY Input: When low, continuity flag on the display is off. When high,

continuity flag is on.

Output: High when voltage between inputs is less than +200 mV.

Low when voltage between inputs is more than +200 mV.

28 25 31 COMMON Sets common mode voltage of 3.2V below V+ for DE, 10X, etc.

Can be used as pre-regulator for external reference.

29 26 32 CREF+ Positive side of external reference capacitor.

30 27 33 CREF Negative side of external reference capacitor.

31 29 35 BUFFER Output of buffer amplifier.

32 30 36 IN LO Negative input voltage terminal.

33 31 37 IN HI Positive input voltage terminal.

34 32 38 REF HI Positive reference voltage.

35 33 39 REF LO Negative reference voltage

2002-2012 Microchip Technology Inc. DS21459E-page 5

TC7129

TABLE 2-1: PIN FUNCTION TABLE (CONTINUED)

Pin No. Pin No. Pin No.

Symbol Function

40-Pin PDIP 44-Pin PQFP 44-Pin PLCC

36 34 40 DGND Internal ground reference for digital section. See Section 4.2.1

5V Power Supply.

37 35 41 RANGE 3 A pull-down for 200 mV scale. Pulled high externally for 2V

scale.

38 36 42 DP2 Internal 3 A pull-down. When high, decimal point 2 will be on.

39 37 43 DP1 Internal 3 A pull-down. When high, decimal point 1 will be on.

40 38 44 OSC2 Output of first clock inverter. Input of second clock inverter.

6,17, 28, 39 12, 23, 34, 1 NC No connection.

DS21459E-page 6 2002-2012 Microchip Technology Inc.

TC7129

3.0 DETAILED DESCRIPTION The resistor and capacitor values are not critical; those

shown work for most applications. In some situations,

(All pin designations refer to 40-pin PDIP.) the capacitor values may have to be adjusted to

The TC7129 is designed to be the heart of a high- compensate for parasitic capacitance in the circuit. The

resolution analog measurement instrument. The only capacitors can be low-cost ceramic devices.

additional components required are a few passive Some applications can use a simple RC network

elements: a voltage reference, a LCD and a power instead of a crystal oscillator. The RC oscillator has

source. Most component values are not critical; more potential for jitter, especially in the least

substitutes can be chosen based on the information significant digit. See Section 4.5 RC Oscillator.

given below.

The basic circuit for a digital multimeter application is 3.2 Integrating Resistor (RINT)

shown in Figure 3-1. See Section 4.0 Typical Appli-

cations, for variations. Typical values for each The integrating resistor sets the charging current for

component are shown. The sections below give the integrating capacitor. Choose a value that provides

component selection criteria. a current between 5 A and 20 A at 2V, the maximum

full-scale input. The typical value chosen gives a

charging current of 13.3 A:

3.1 Oscillator (XOSC, CO1, CO2, RO)

EQUATION 3-1:

The primary criterion for selecting the crystal oscillator

is to choose a frequency that achieves maximum rejec- 2V

ICHARGE = 13.3 A

tion of line frequency noise. To do this, the integration 150 k

phase should last an integral number of line cycles.

The integration phase of the TC7129 is 10,000 clock Too high a value for RINT increases the sensitivity to

cycles on the 200 mV range and 1000 clock cycles on noise pickup and increases errors due to leakage

the 2V range. One clock cycle is equal to two oscillator current. Too low a value degrades the linearity of the

cycles. For 60 Hz rejection, the oscillator frequency integration, leading to inaccurate readings.

should be chosen so that the period of one line cycle

equals the integration time for the 2V range.

EQUATION 3-1:

1/60 second = 16.7 msec =

1000 clock cycles *2 OSC cycles/clock cycle

OSC Frequency

This equation gives an oscillator frequency of 120 kHz.

A similar calculation gives an optimum frequency of

100 kHz for 50 Hz rejection.

2002-2012 Microchip Technology Inc. DS21459E-page 7

TC7129

Low Battery Continuity

V+

5 pF CO1

20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

DP4 /OR

VDISP

ANNUNC

OSC3

OSC1

Display Drive Outputs

TC7129

CONTINUITY

120 Crystal

COMMON

kHz

INT OUT

DP3 /UR

LATCH/

REF LO

RANGE

REF HI

CREF+

DGND

INT IN

HOLD

CREF

OSC2

BUFF

IN LO

IN HI

DP2

DP1

V+

V

21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

330 k

CINT RO

0.1 F 10 pF CO2

CREF+ 0.1 RREF DREF

1 F F 20 CRF

V+

k 0.1 F

150 k CIF

RINT

+ 10 k

RBIAS RIF

9V 100 k

+

VIN

Figure 3-1: Standard Circuit.

3.3 Integrating Capacitor (CINT) The capacitor should have low dielectric absorption to

ensure good integration linearity. Polypropylene and

The charge stored in the integrating capacitor during Teflon capacitors are usually suitable. A good

the integrate phase is directly proportional to the input measurement of the dielectric absorption is to connect

voltage. The primary selection criterion for CINT is to the reference capacitor across the inputs by

choose a value that gives the highest voltage swing connecting:

while remaining within the high-linearity portion of the

integrator output range. An integrator swing of 2V is the Pin-to-Pin:

recommended value. The capacitor value can be 20 33 (CREF+ to IN HI)

calculated using the following equation: 30 32 (CREF to IN LO)

EQUATION 3-1: A reading between 10,000 and 9998 is acceptable;

t xI anything lower indicates unacceptably high dielectric

CINT = INT INT absorption.

VSWING

Where tINT is the integration time. 3.4 Reference Capacitor (CREF)

The reference capacitor stores the reference voltage

Using the values derived above (assuming 60 Hz during several phases of the measurement cycle. Low

operation), the equation becomes: leakage is the primary selection criterion for this com-

EQUATION 3-2: ponent. The value must be high enough to offset the

effect of stray capacitance at the capacitor terminals. A

value of at least 1 F is recommended.

CINT = 16.7 msec x 13.3 A = 0.1 A

2V

DS21459E-page 8 2002-2012 Microchip Technology Inc.

TC7129

3.5 Voltage Reference

(DREF, RREF, RBIAS, CRF) +5V

TC7129

The reference potentiometer (RREF) provides an

adjustment for adjusting the reference voltage; any

24

value above 20 k is adequate. The bias resistor

V+

(RBIAS) limits the current through DREF to less than 34

REF HI

150 A. The reference filter capacitor (CRF) forms an 0.1 F

RC filter with RBIAS to help eliminate noise. 35

REF LO

36 DGND

3.6 Input Filter (RIF, CIF) 28

COMMON

0.1 F

For added stability, an RC input noise filter is usually 33

included in the circuit. The input filter resistor value IN HI +

VIN

should not exceed 100 k. A typical RC time constant 32

value is 16.7 msec to help reject line frequency noise. 0.1 F IN LO

The input filter capacitor should have low leakage for a V

23

high-impedance input.

3.7 Battery -5V

The typical circuit uses a 9V battery as a power source.

However, any value between 6V and 12V can be used. Figure 4-1: Powering the TC7129 From

For operation from batteries with voltages lower than a 5V Power Supply.

6V and for operation from power supplies, see

Section 4.2 Powering the TC7129. 4.2.2 Low Voltage Battery Source

A battery with voltage between 3.8V and 6V can be

4.0 TYPICAL APPLICATIONS used to power the TC7129 when used with a voltage

doubler circuit, as shown in Figure 4-2. The voltage

doubler uses the TC7660 DC-to-DC voltage converter

4.1 TC7129 as a Replacement Part and two external capacitors.

The TC7129 is a direct pin-for-pin replacement part for

the ICL7129. Note, however, that the ICL7129 requires

a capacitor and resistor between pins 26 and 28 for 24

phase compensation. Since the TC7129 uses internal V+ 34

phase compensation, these parts are not required and, REF HI

36

in fact, must be removed from the circuit for stable +

DGND

operation. 3.8V 35

to REF LO

6V

COMMON 28

4.2 Powering the TC7129

TC7129 +

33

While the most common power source for the TC7129 IN HI

VIN

is a 9V battery, there are other possibilities. Some of 8 32

IN LO

the more common ones are explained below. 2

V

+ 23

4.2.1 5V Power Supply TC7660 10 F

4

Measurements are made with respect to power supply

5

ground. DGND (pin 36) is set internally to about 5V less

than V+ (pin 24); it is not intended to be a power supply 10 F

3

input and must not be tied directly to power supply +

ground. It can be used as a reference for external logic,

as explained in Section 4.3 Connecting to External Figure 4-2: Powering the TC7129 From

Logic, (see Figure 4-1). a Low-Voltage Battery.

2002-2012 Microchip Technology Inc. DS21459E-page 9

TC7129

4.2.3 +5V Power Supply

+

Measurements are made with respect to power supply V

ground. COMMON (pin 28) is connected to REF LO

(pin 35). A voltage doubler is needed, since the supply

voltage is less than the 6V minimum needed by the 24

TC7129. DGND (pin 36) must be isolated from power

supply ground (see Figure 4-3). External

Logic TC7129

+5V

36

DGND

ILOGIC

24

V+ 34 23

0.1 F

TC7129 V-

35

36

DGND 28

Figure 4-4: External Logic Referenced

0.1 F Directly to DGND.

33 +

VIN

8 32 V+

V+ 2 V

+ 23

10 F

TC7660 4 24

5

GND External

3 Logic

10 F

+

TC7129

Figure 4-3: Powering the TC7129 From 36

+ DGND

a +5V Power Supply.

ILOGIC

23

4.3 Connecting to External Logic

External logic can be directly referenced to DGND

(pin 36), provided that the supply current of the external V

logic does not exceed the sink current of DGND

(Figure 4-4). A safe value for DGND sink current is Figure 4-5: External Logic Referenced

1.2 mA. If the sink current is expected to exceed this to DGND with Buffer.

value, a buffer is recommended (see Figure 4-5).

4.4 Temperature Compensation

For most applications, VDISP (pin 19) can be connected

directly to DGND (pin 36). For applications with a wide

temperature range, some LCDs require that the drive

levels vary with temperature to maintain good viewing

angle and display contrast. Figure 4-6 shows two

circuits that can be adjusted to give temperature com-

pensation of about 10 mV/C between V+ (pin 24) and

VDISP. The diode between DGND and VDISP should

have a low turn-on voltage because VDISP cannot

exceed 0.3V below DGND.

DS21459E-page 10 2002-2012 Microchip Technology Inc.

TC7129

V+ V+

1N4148

39 k 39 k

24 24

200 k

TC7129 20 k 2N2222 TC7129

19 19

+ VDISP VDISP

5 k

36 36

DGND DGND

75 k 18 k

23 23

V V

Figure 4-6: Temperature Compensating Circuits.

4.5 RC Oscillator 4.6 Measuring Techniques

For applications in which 3-1/2 digit (100 V) resolution Two important techniques are used in the TC7129:

is sufficient, an RC oscillator is adequate. A recom- successive integration and digital auto-zeroing.

mended value for the capacitor is 51 pF. Other values Successive integration is a refinement to the traditional

can be used as long as they are sufficiently larger than dual-slope conversion technique.

the circuit parasitic capacitance. The resistor value is

calculated as: 4.7 Dual-Slope Conversion

EQUATION 4-1: A dual-slope conversion has two basic phases: inte-

0.45 grate and de-integrate. During the integrate phase, the

R= input signal is integrated for a fixed period of time; the

Freq * C

integrated voltage level is thus proportional to the input

For 120 kHz frequency and C = 51 pF, the calculated voltage. During the de-integrate phase, the integrated

value of R is 75 k. The RC oscillator and the crystal voltage is ramped down at a fixed slope, and a counter

oscillator circuits are shown in Figure 4-7. counts the clock cycles until the integrator voltage

crosses zero. The count is a measurement of the time

to ramp the integrated voltage to zero and is, therefore,

proportional to the input voltage being measured. This

count can then be scaled and displayed as a measure-

TC7129 ment of the input voltage. Figure 4-8 shows the phases

of the dual-slope conversion.

1 40 2

270 k Integrate De-integrate

5 pF 120 kHz 10 pF

V+ V+

Zero

Crossing

TC7129

Time

1 40 2

Figure 4-8: Dual-Slope Conversion.

75 k

51 pF The dual-slope method has a fundamental limitation.

The count can only stop on a clock cycle, so that mea-

surement accuracy is limited to the clock frequency. In

Figure 4-7: Oscillator Circuits. addition, a delay in the zero-crossing comparator can

add to the inaccuracy. Figure 4-9 shows these errors in

an actual measurement.

2002-2012 Microchip Technology Inc. DS21459E-page 11

TC7129

Integrate De-integrate

Overshoot due to zero-crossing between

clock pulses

Time Integrator Residue Voltage

Overshoot caused by comparator

delay of 1 clock pulse

Clock Pulses

Figure 4-9: Accuracy Errors in Dual-Slope Conversion.

Zero Integrate INT1 DE1

and Latch Integrate De-integrate REST X10 DE2 REST X10 DE3 Zero Integrate

TC7129

Integrator Residual Voltage

Note: Shaded area greatly expanded in time and amplitude.

Figure 4-10: Integration Waveform.

DS21459E-page 12 2002-2012 Microchip Technology Inc.

TC7129

4.8 Successive Integration 4.9 Digital Auto-Zeroing

The successive integration technique picks up where To eliminate the effect of amplifier offset errors, the

dual-slope conversion ends. The overshoot voltage TC7129 uses a digital auto-zeroing technique. After the

shown in Figure 4-9 (called the integrator residue input voltage is measured as described above, the

voltage) is measured to obtain a correction to the initial measurement is repeated with the inputs shorted

count. Figure 4-10 shows the cycles in a successive internally. The reading with inputs shorted is a

integration measurement. measurement of the internal errors and is subtracted

The waveform shown is for a negative input signal. The from the previous reading to obtain a corrected

sequence of events during the measurement cycle is measurement. Digital auto-zeroing eliminates the need

shown in Table 4-1. for an external auto-zeroing capacitor used in other

ADCs.

TABLE 4-1: MEASUREMENT CYCLE

SEQUENCE 4.10 Inside the TC7129

Phase Description Figure 4-11 shows a simplified block diagram of the

TC7129.

INT1 Input signal is integrated for fixed time (1000 clock

cycles on 2V scale, 10,000 on 200 mV).

DE1 Integrator voltage is ramped to zero. Counter

counts up until zero-crossing to produce reading

accurate to 3-1/2 digits. Residue represents an

overshoot of the actual input voltage.

REST Rest; circuit settles.

X10 Residue voltage is amplified 10 times and

inverted.

DE2 Integrator voltage is ramped to zero. Counter

counts down until zero-crossing to correct reading

to 4-1/2 digits. Residue represents an undershoot

of the actual input voltage.

REST Rest; circuit settles.

X10 Residue voltage is amplified 10 times and

inverted.

DE3 Integrator voltage is ramped to zero. Counter

counts up until zero-crossing to correct reading to

5-1/2 digits. Residue is discarded.

2002-2012 Microchip Technology Inc. DS21459E-page 13

TC7129

Low Battery Continuity

Backplane

Segment Drives Drives

TC7129 Annunciator

Drive

OSC1

Latch, Decode Display Multiplexer VDISP

OSC2

Up/Down Results Counter

OSC3

Sequence Counter/Decoder

Control Logic

RANGE DP1

L/H DP2

CONT UR/DP3

OR/DP4

V+

Analog Section

V REF HI

DGND REF LO

INT OUT

INT IN

COMMON IN IN BUFF

HI LO

Figure 4-11: TC7129 Functional Block Diagram.

CREF RINT CINT

REF HI REF LO

DE DE

Integrator X10

10

INT1 Comparator 1

pF

IN HI + Buffer + To Digital

DE- DE+ + Section

100 pF

DE+ DE ZI, X10 Comparator 2

Common

INT REST

INT1, INT2

IN LO

500 k

+

TC7129

V +

Continuity

200 mV Comparator

Continuity To Display Driver

Figure 4-12: Integrator Block Diagram.

DS21459E-page 14 2002-2012 Microchip Technology Inc.

TC7129

4.11 Integrator Section

The integrator section includes the integrator, compar-

ator, input buffer amplifier and analog switches (see

Table 4-2) used to change the circuit configuration

during the separate measurement phases described +

IN HI

earlier. (See Figure 4-12). Buffer

TABLE 4-2: SWITCH LEGENDS

Label Description COM

Label Meaning. TC7129

DE Open during all de-integrate phases.

DE Closed during all de-integrate phases when IN LO

input voltage is negative. 500 k

200 mV To Display Driver

DE+ Closed during all de-integrate phases when

V + (Not Latched)

input voltage is positive.

INT1 Closed during the first integrate phase CONT

(measurement of the input voltage).

INT2 Closed during the second integrate phase Figure 4-13: Continuity Indicator Circuit.

(measurement of the amplifier offset).

INT Open during both integrate phases.

REST Closed during the rest phase.

TC7129

ZI Closed during the zero integrate phase.

X10 Closed during the X10 phase.

X10 Open during the X10 phase.

500 k

The buffer amplifier has a common mode input voltage DP4/OR, Pin 20

range from 1.5V above V to 1V below V+. The integra- DP3/UR, Pin 21

tor amplifier can swing to within 0.3V of the rails. LATCH/HOLD Pin 22

However, for best linearity, the swing is usually limited CONTINUITY, Pin 27

to within 1V. Both amplifiers can supply up to 80 A of

output current, but should be limited to 20 A for good

linearity.

Figure 4-14: Input/Output Pin Schematic.

4.12 Continuity Indicator 4.13 Common and Digital Ground

The common and digital ground (DGND) outputs are

A comparator with a 200 mV threshold is connected

between IN HI (pin 33) and IN LO (pin 32). Whenever generated from internal Zener diodes. The voltage

the voltage between inputs is less than 200 mV, the between V+ and DGND is the internal supply voltage

for the digital section of the TC7129. Common can

CONTINUITY output (pin 27) will be pulled high,

activating the continuity annunciator on the display. source approximately 12 A; DGND has essentially no

The continuity pin can also be used as an input to drive source capability (see Figure 4-15).

the continuity annunciator directly from an external

source (see Figure 4-13).

A schematic of the input/output nature of this pin is also

shown in Figure 4-14.

2002-2012 Microchip Technology Inc. DS21459E-page 15

TC7129

4.17 LATCH/Hold

24

V+

The L/H output goes low during the last 100 cycles of

12 A 3.2V each conversion. This pulse latches the conversion

data into the display driver section of the TC7129. This

COM

28 pin can also be used as an input. When driven high, the

N 5V

display will not be updated; the previous reading is

+

Logic

displayed. When driven low, the display reading is not

Section latched; the sequence counter reading will be

displayed. Since the counter is counting much faster

36

DGND

than the backplanes are being updated, the reading

P shown in this mode is somewhat erratic.

TC7129

N

4.18 Display Driver

23

The TC7129 drives a triplexed LCD with three back-

V

planes. The LCD can include decimal points, polarity

sign and annunciators for continuity and low battery.

Figure 4-15: Digital Ground (DGND) and

Figure 4-16 shows the assignment of the display

Common Outputs. segments to the backplanes and segment drive lines.

The backplane drive frequency is obtained by dividing

4.14 Low Battery the oscillator frequency by 1200. This results in a back-

The low battery annunciator turns on when supply volt- plane drive frequency of 100 Hz for 60 Hz operation

age between V and V+ drops below 6.8V. The internal (120 kHz crystal) and 83.3 Hz for 50 Hz operation

(100 kHz crystal).

zener diode has a threshold of 6.3V. When the supply

voltage drops below 6.8V, the transistor tied to V turns Backplane waveforms are shown in Figure 4-17.

off pulling the Low Battery point high. These appear on outputs BP1, BP2, BP3 (pins 16, 17

and 18). They remain the same, regardless of the

4.15 Sequence and Results Counter segments being driven.

Other display output lines (pins 4 through 15) have

A sequence counter and associated control logic pro-

waveforms that vary depending on the displayed

vide signals that operate the analog switches in the

values. Figure 4-18 shows a set of waveforms for the

integrator section. The comparator output from the inte-

A, G, D outputs (pins 5, 8, 11 and 14) for several

grator gates the results counter. The results counter is

combinations of ON segments.

a six-section up/down decade counter that holds the

intermediate results from each successive integration. The ANNUNCIATOR DRIVE output (pin 3) is a square

wave, running at the backplane frequency (100 Hz or

4.16 Overrange and Underrange 83.3 Hz) with a peak-to-peak voltage equal to DGND

voltage. Connecting an annunciator to pin 3 turns it on;

Outputs connecting it to its backplane turns it off.

When the results counter holds a value greater than

19,999, the DP4/OR output (Pin 20) is driven high.

When the results counter value is less than 1000, the

DP3/UR output (Pin 21) is driven high. Both signals are

valid on the falling edge of LATCH/HOLD (L/H) and do

not change until the end of the next conversion cycle.

The signals are updated at the end of each conversion,

unless the L/H input (Pin 22) is held high. Pins 20 and

21 can also be used as inputs for external control of

decimal points 3 and 4. Figure 4-14 shows a schematic

of the input/output nature of these pins.

DS21459E-page 16 2002-2012 Microchip Technology Inc.

TC7129

Low Battery Continuity

BP1

BP2 Backplane

Connections

BP3

Low Battery Continuity

F4, E4, DP4 B1, C1, Continuity

A4, G4, D4 A1, G1, D1

B4, C4, BC4 F1, E1, DP1

F3, E3, DP3 B2, C2, Low Battery

A3, G3, D3 A2, G2, D2

B3, C3, MINUS F2, E2, DP2

Figure 4-16: Display Segment Assignments.

VDD

b Segment VH

Line

BP1 All Off VL

VDISP

VDD

a Segment VH

On

BP2 d, g Off VL

VDISP

VDD

a, g On VH

BP3

d Off

VL

VDISP

VDD

Figure 4-17: Backplane Waveforms. VH

All On

VL

VDISP

Figure 4-18: Typical Display Output

Waveforms.

2002-2012 Microchip Technology Inc. DS21459E-page 17

TC7129

5.0 PACKAGING INFORMATION

5.1 Package Marking Information

Package marking data not available a this time.

5.2 Taping Forms

Us er Direction of F eed

W, Width

P in 1 of C arrier

T ape

P in 1

P , P itch

S tandard R eel C omponent Orientation R evers e R eel C omponent Orientation

Component Taping Orientation for 44-Pin PQFP Devices

User Direction of Feed

Pin 1

P

Standard Reel Component Orientation

for 713 Suffix Device

Carrier Tape, Number of Components Per Reel and Reel Size

Package Carrier Width (W) Pitch (P) Part Per Full Reel Reel Size

44-Pin PQFP 24 mm 16 mm 500 13 in

Note: Drawing does not represent total number of pins.

DS21459E-page 18 2002-2012 Microchip Technology Inc.

TC7129

40-Lead Plastic Dual In-line (P) 600 mil Body (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located

at http://www.microchip.com/packaging

E1

2

n 1

A A2

L

c

B1

A1

eB B p

Units INCHES* MILLIMETERS

Dimension Limits MIN NOM MAX MIN NOM MAX

Number of Pins n 40 40

Pitch p .100 2.54

Top to Seating Plane A .160 .175 .190 4.06 4.45 4.83

Molded Package Thickness A2 .140 .150 .160 3.56 3.81 4.06

Base to Seating Plane A1 .015 0.38

Shoulder to Shoulder Width E .595 .600 .625 15.11 15.24 15.88

Molded Package Width E1 .530 .545 .560 13.46 13.84 14.22

Overall Length D 2.045 2.058 2.065 51.94 52.26 52.45

Tip to Seating Plane L .120 .130 .135 3.05 3.30 3.43

Lead Thickness c .008 .012 .015 0.20 0.29 0.38

Upper Lead Width B1 .030 .050 .070 0.76 1.27 1.78

Lower Lead Width B .014 .018 .022 0.36 0.46 0.56

Overall Row Spacing eB .620 .650 .680 15.75 16.51 17.27

Mold Draft Angle Top 5 10 15 5 10 15

Mold Draft Angle Bottom 5 10 15 5 10 15

* Controlling Parameter

Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010 (0.254mm) per side.

JEDEC Equivalent: MO-011

Drawing No. C04-016

2002-2012 Microchip Technology Inc. DS21459E-page 19

TC7129

44-Lead Plastic Leaded Chip Carrier (LW) Square (PLCC)

Note: For the most current package drawings, please see the Microchip Packaging Specification located

at http://www.microchip.com/packaging

E

E1

#leads=n1

D1 D

n 1 2

CH2 x 45 CH1 x 45

A3

A2 A

35

B1

c A1

B

p

E2 D2

Units INCHES* MILLIMETERS

Dimension Limits MIN NOM MAX MIN NOM MAX

Number of Pins n 44 44

Pitch p .050 1.27

Pins per Side n1 11 11

Overall Height A .165 .173 .180 4.19 4.39 4.57

Molded Package Thickness A2 .145 .153 .160 3.68 3.87 4.06

Standoff A1 .020 .028 .035 0.51 0.71 0.89

Side 1 Chamfer Height A3 .024 .029 .034 0.61 0.74 0.86

Corner Chamfer 1 CH1 .040 .045 .050 1.02 1.14 1.27

Corner Chamfer (others) CH2 .000 .005 .010 0.00 0.13 0.25

Overall Width E .685 .690 .695 17.40 17.53 17.65

Overall Length D .685 .690 .695 17.40 17.53 17.65

Molded Package Width E1 .650 .653 .656 16.51 16.59 16.66

Molded Package Length D1 .650 .653 .656 16.51 16.59 16.66

Footprint Width E2 .590 .620 .630 14.99 15.75 16.00

Footprint Length D2 .590 .620 .630 14.99 15.75 16.00

Lead Thickness c .008 .011 .013 0.20 0.27 0.33

Upper Lead Width B1 .026 .029 .032 0.66 0.74 0.81

Lower Lead Width B .013 .020 .021 0.33 0.51 0.53

Mold Draft Angle Top 0 5 10 0 5 10

Mold Draft Angle Bottom 0 5 10 0 5 10

* Controlling Parameter

Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010 (0.254mm) per side.

JEDEC Equivalent: MO-047

Drawing No. C04-048

DS21459E-page 20 2002-2012 Microchip Technology Inc.

TC7129

44-Lead Plastic Quad Flatpack (KW) 10x10x2.0 mm Body, 1.95/0.25 mm Lead Form (PQFP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located

at http://www.microchip.com/packaging

E

E1

D1 D

2

1

B

n

CHAMFER VARIES

c

A2 A

L A1 F

Units INCHES MILLIMETERS*

Dimension Limits MIN NOM MAX MIN NOM MAX

Number of Pins n 44 44

Pitch p .031 BSC 0.80 BSC

Overall Height A - - .096 - - 2.45

Molded Package Thickness A2 .077 .079 .083 1.95 2.00 2.10

Standoff A1 .010 - - 0.25 - -

Foot Length L .029 .035 .041 0.73 0.88 1.03

Footprint F .077 REF. 1.95 REF.

Foot Angle 0 3.5 7 0 3.5 7

Overall Width E .547 BSC 13.90 BSC

Overall Length D .547 BSC 13.90 BSC

Molded Package Width E1 .394 BSC 10.00 BSC

Molded Package Length D1 .394 BSC 10.00 BSC

Lead Thickness c .004 - .009 0.11 - 0.23

Lead Width B .012 - .018 0.30 - 0.45

Mold Draft Angle Top 5 - 16 5 - 16

Mold Draft Angle Bottom 5 - 16 5 - 16

* Controlling Parameter

Significant Characteristic

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

See ASME Y14.5M

REF: Reference Dimension, usually without tolerance, for information purposes only.

See ASME Y14.5M

JEDEC Equivalent: MO-112 AA-1 Revised 07-21-05

Drawing No. C04-119

2002-2012 Microchip Technology Inc. DS21459E-page 21

TC7129

6.0 REVISION HISTORY

Revision E (December 2012)

Added a note to each package outline drawing.

DS21459E-page 22 2002-2012 Microchip Technology Inc.

PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

PART NO. X XX XX Examples:

Device Temp. Pkg Taping a) TC7129CPL: 40-Pin PDIP

Direction b) DSTEMPCKW713: 44-Pin PQFP

Tape and Reel

c) DSTEMPCLW: 44-Pin PLCC

Device: DSTEMP: 4-1/2 Digit Analog-to-Digital Converter

Temperature: C = 0C to +70C

I = -25C to +85C

Package: PL = 40-Pin PDIP

KW = 40-Pin PQFP

LW = 44-Pin PLCC

JL = 40-Pin CDIP

Taping Direction: 713 = Standard Taping

2002-2012 Microchip Technology Inc. DS21459E-page 23

NOTES:

DS21459E-page 24 2002-2012 Microchip Technology Inc.

THE MICROCHIP WEB SITE CUSTOMER SUPPORT

Microchip provides online support via our WWW site at Users of Microchip products can receive assistance

www.microchip.com. This web site is used as a means through several channels:

to make files and information easily available to Distributor or Representative

customers. Accessible by using your favorite Internet

Local Sales Office

browser, the web site contains the following

information: Field Application Engineer (FAE)

Technical Support

Product Support Data sheets and errata,

application notes and sample programs, design Customers should contact their distributor,

resources, users guides and hardware support representative or field application engineer (FAE) for

documents, latest software releases and archived support. Local sales offices are also available to help

software customers. A listing of sales offices and locations is

General Technical Support Frequently Asked included in the back of this document.

Questions (FAQ), technical support requests, Technical support is available through the web site

online discussion groups, Microchip consultant at: http://microchip.com/support

program member listing

Business of Microchip Product selector and

ordering guides, latest Microchip press releases,

listing of seminars and events, listings of

Microchip sales offices, distributors and factory

representatives

CUSTOMER CHANGE NOTIFICATION

SERVICE

Microchips customer notification service helps keep

customers current on Microchip products. Subscribers

will receive e-mail notification whenever there are

changes, updates, revisions or errata related to a

specified product family or development tool of interest.

To register, access the Microchip web site at

www.microchip.com. Under Support, click on

Customer Change Notification and follow the

registration instructions.

2002-2012 Microchip Technology Inc. DS21459E-page 25

READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip

product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our

documentation can better serve you, please FAX your comments to the Technical Publications Manager at

(480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

TO: Technical Publications Manager Total Pages Sent ________

RE: Reader Response

From: Name

Company

Address

City / State / ZIP / Country

Telephone: (_______) _________ - _________ FAX: (______) _________ - _________

Application (optional):

Would you like a reply? Y N

Device: Literature Number: DS21459E

Questions:

1. What are the best features of this document?

2. How does this document meet your hardware and software development needs?

3. Do you find the organization of this document easy to follow? If not, why?

4. What additions to the document do you think would enhance the structure and subject?

5. What deletions from the document could be made without affecting the overall usefulness?

6. Is there any incorrect or misleading information (what and where)?

7. How would you improve this document?

DS21459E-page 26 2002-2012 Microchip Technology Inc.

Note the following details of the code protection feature on Microchip devices:

Microchip products meet the specification contained in their particular Microchip Data Sheet.

Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchips Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

Microchip is willing to work with the customer who is concerned about the integrity of their code.

Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as unbreakable.

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our

products. Attempts to break Microchips code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts

allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device Trademarks

applications and the like is provided only for your convenience The Microchip name and logo, the Microchip logo, dsPIC,

and may be superseded by updates. It is your responsibility to

FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro,

ensure that your application meets with your specifications.

PICSTART, PIC32 logo, rfPIC, SST, SST Logo, SuperFlash

MICROCHIP MAKES NO REPRESENTATIONS OR and UNI/O are registered trademarks of Microchip Technology

WARRANTIES OF ANY KIND WHETHER EXPRESS OR

Incorporated in the U.S.A. and other countries.

IMPLIED, WRITTEN OR ORAL, STATUTORY OR

OTHERWISE, RELATED TO THE INFORMATION, FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor,

INCLUDING BUT NOT LIMITED TO ITS CONDITION, MTP, SEEVAL and The Embedded Control Solutions

QUALITY, PERFORMANCE, MERCHANTABILITY OR Company are registered trademarks of Microchip Technology

FITNESS FOR PURPOSE. Microchip disclaims all liability Incorporated in the U.S.A.

arising from this information and its use. Use of Microchip Silicon Storage Technology is a registered trademark of

devices in life support and/or safety applications is entirely at Microchip Technology Inc. in other countries.

the buyers risk, and the buyer agrees to defend, indemnify and

Analog-for-the-Digital Age, Application Maestro, BodyCom,

hold harmless Microchip from any and all damages, claims,

chipKIT, chipKIT logo, CodeGuard, dsPICDEM,

suits, or expenses resulting from such use. No licenses are

dsPICDEM.net, dsPICworks, dsSPEAK, ECAN,

conveyed, implicitly or otherwise, under any Microchip

ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial

intellectual property rights.

Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB

Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code

Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit,

PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O,

Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA

and Z-Scale are trademarks of Microchip Technology

Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated

in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip

Technology Germany II GmbH & Co. & KG, a subsidiary of

Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their

respective companies.

2002-2012, Microchip Technology Incorporated, Printed in

the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620768389

QUALITY MANAGEMENT SYSTEM Microchip received ISO/TS-16949:2009 certification for its worldwide

headquarters, design and wafer fabrication facilities in Chandler and

CERTIFIED BY DNV Tempe, Arizona; Gresham, Oregon and design centers in California

and India. The Companys quality system processes and procedures

== ISO/TS 16949 ==

are for its PIC MCUs and dsPIC DSCs, KEELOQ code hopping

devices, Serial EEPROMs, microperipherals, nonvolatile memory and

analog products. In addition, Microchips quality system for the design

and manufacture of development systems is ISO 9001:2000 certified.

2002-2012 Microchip Technology Inc. DS21459E-page 27

Worldwide Sales and Service

AMERICAS ASIA/PACIFIC ASIA/PACIFIC EUROPE

Corporate Office Asia Pacific Office India - Bangalore Austria - Wels

2355 West Chandler Blvd. Suites 3707-14, 37th Floor Tel: 91-80-3090-4444 Tel: 43-7242-2244-39

Chandler, AZ 85224-6199 Tower 6, The Gateway Fax: 91-80-3090-4123 Fax: 43-7242-2244-393

Tel: 480-792-7200 Harbour City, Kowloon Denmark - Copenhagen

India - New Delhi

Fax: 480-792-7277 Hong Kong Tel: 45-4450-2828

Tel: 91-11-4160-8631

Technical Support: Tel: 852-2401-1200 Fax: 45-4485-2829

Fax: 91-11-4160-8632

http://www.microchip.com/ Fax: 852-2401-3431

India - Pune France - Paris

support

Australia - Sydney Tel: 91-20-2566-1512 Tel: 33-1-69-53-63-20

Web Address:

Tel: 61-2-9868-6733 Fax: 91-20-2566-1513 Fax: 33-1-69-30-90-79

www.microchip.com

Fax: 61-2-9868-6755 Germany - Munich

Atlanta Japan - Osaka

China - Beijing Tel: 49-89-627-144-0

Duluth, GA Tel: 81-6-6152-7160

Tel: 86-10-8569-7000 Fax: 49-89-627-144-44

Tel: 678-957-9614 Fax: 81-6-6152-9310

Fax: 86-10-8528-2104 Italy - Milan

Fax: 678-957-1455 Japan - Tokyo

China - Chengdu Tel: 39-0331-742611

Boston Tel: 81-3-6880- 3770

Tel: 86-28-8665-5511 Fax: 39-0331-466781

Westborough, MA Fax: 81-3-6880-3771

Fax: 86-28-8665-7889 Netherlands - Drunen

Tel: 774-760-0087 Korea - Daegu

Fax: 774-760-0088 China - Chongqing Tel: 82-53-744-4301 Tel: 31-416-690399

Tel: 86-23-8980-9588 Fax: 82-53-744-4302 Fax: 31-416-690340

Chicago

Itasca, IL Fax: 86-23-8980-9500 Spain - Madrid

Korea - Seoul

Tel: 630-285-0071 China - Hangzhou Tel: 34-91-708-08-90

Tel: 82-2-554-7200

Fax: 630-285-0075 Tel: 86-571-2819-3187 Fax: 82-2-558-5932 or Fax: 34-91-708-08-91

Cleveland Fax: 86-571-2819-3189 82-2-558-5934 UK - Wokingham

Independence, OH China - Hong Kong SAR Tel: 44-118-921-5869

Malaysia - Kuala Lumpur

Tel: 216-447-0464 Tel: 852-2943-5100 Fax: 44-118-921-5820

Tel: 60-3-6201-9857

Fax: 216-447-0643 Fax: 852-2401-3431 Fax: 60-3-6201-9859

Dallas China - Nanjing Malaysia - Penang

Addison, TX Tel: 86-25-8473-2460 Tel: 60-4-227-8870

Tel: 972-818-7423 Fax: 86-25-8473-2470 Fax: 60-4-227-4068

Fax: 972-818-2924

China - Qingdao Philippines - Manila

Detroit Tel: 86-532-8502-7355 Tel: 63-2-634-9065

Farmington Hills, MI

Fax: 86-532-8502-7205 Fax: 63-2-634-9069

Tel: 248-538-2250

Fax: 248-538-2260 China - Shanghai Singapore

Tel: 86-21-5407-5533 Tel: 65-6334-8870

Indianapolis Fax: 86-21-5407-5066 Fax: 65-6334-8850

Noblesville, IN

Tel: 317-773-8323 China - Shenyang Taiwan - Hsin Chu

Fax: 317-773-5453 Tel: 86-24-2334-2829 Tel: 886-3-5778-366

Fax: 86-24-2334-2393 Fax: 886-3-5770-955

Los Angeles

Mission Viejo, CA China - Shenzhen Taiwan - Kaohsiung

Tel: 949-462-9523 Tel: 86-755-8864-2200 Tel: 886-7-213-7828

Fax: 949-462-9608 Fax: 86-755-8203-1760 Fax: 886-7-330-9305

Santa Clara China - Wuhan Taiwan - Taipei

Santa Clara, CA Tel: 86-27-5980-5300 Tel: 886-2-2508-8600

Tel: 408-961-6444 Fax: 86-27-5980-5118 Fax: 886-2-2508-0102

Fax: 408-961-6445 China - Xian Thailand - Bangkok

Toronto Tel: 86-29-8833-7252 Tel: 66-2-694-1351

Mississauga, Ontario, Fax: 86-29-8833-7256 Fax: 66-2-694-1350

Canada China - Xiamen

Tel: 905-673-0699 Tel: 86-592-2388138

Fax: 905-673-6509 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040

11/29/12

Fax: 86-756-3210049

DS21459E-page 28 2002-2012 Microchip Technology Inc.

Vous aimerez peut-être aussi

- CLC5957 12-Bit, 70 MSPS Broadband Monolithic A/D Converter: General Description FeaturesDocument16 pagesCLC5957 12-Bit, 70 MSPS Broadband Monolithic A/D Converter: General Description FeaturesPeter SolyomPas encore d'évaluation

- TCL M113 Tmpa8809 MC4406 SMDocument90 pagesTCL M113 Tmpa8809 MC4406 SMYanto LufiPas encore d'évaluation

- TCL Chassis M113 SINGER SCT-29128 - Service - ManualDocument90 pagesTCL Chassis M113 SINGER SCT-29128 - Service - ManualAjith Priyalal75% (4)

- LA1781Document54 pagesLA1781Patricio Fernandez BarbaPas encore d'évaluation

- Features General Description: High-Speed High-Side MOSFET DriverDocument9 pagesFeatures General Description: High-Speed High-Side MOSFET DriverPaulo SilvaPas encore d'évaluation

- Pdiol 2008dec24 Supply An 01Document3 pagesPdiol 2008dec24 Supply An 01Roberto De Mesa PPas encore d'évaluation

- ADC10154Document23 pagesADC10154Niddu NidduPas encore d'évaluation

- PLCC-28: Vpwm-In Vpwm-Out NC Ain5-Spd NC NCDocument8 pagesPLCC-28: Vpwm-In Vpwm-Out NC Ain5-Spd NC NC肖磊Pas encore d'évaluation

- MP2225GJ-Z Circuito IntegratoDocument20 pagesMP2225GJ-Z Circuito IntegratoMimmo FracchiollaPas encore d'évaluation

- 8V To 35V, 3.0A 1ch Buck Converter With Integrated FET: DatasheetDocument21 pages8V To 35V, 3.0A 1ch Buck Converter With Integrated FET: DatasheetArdhi Purna bagasPas encore d'évaluation

- ICL7106, ICL7107, ICL7107S: 3 / Digit, LCD/LED Display, A/D Converters FeaturesDocument16 pagesICL7106, ICL7107, ICL7107S: 3 / Digit, LCD/LED Display, A/D Converters FeaturesStefano Romeu ZeplinPas encore d'évaluation

- ICL7106 and ICL7107 VoltmeterDocument16 pagesICL7106 and ICL7107 VoltmeterAntonino ScordatoPas encore d'évaluation

- Em2130l02 12873-1609280Document47 pagesEm2130l02 12873-1609280신덕기Pas encore d'évaluation

- Low-Voltage Input Boost Regulator For PIC Microcontrollers: Features General DescriptionDocument30 pagesLow-Voltage Input Boost Regulator For PIC Microcontrollers: Features General DescriptionPABLO ANDRES URIBE AGUDELOPas encore d'évaluation

- 数字硬件简卡英文Document11 pages数字硬件简卡英文johanes kharismaPas encore d'évaluation

- KWP2000 SIMULATOR MULTIPLE ECUDocument8 pagesKWP2000 SIMULATOR MULTIPLE ECU肖磊Pas encore d'évaluation

- Digital Electronics: - Safety - Introduction - Basic Types of MultivibratorsDocument29 pagesDigital Electronics: - Safety - Introduction - Basic Types of Multivibratorsahmad19782010Pas encore d'évaluation

- ICL7106, ICL7107, ICL7106S, ICL7107S: 3 / Digit, LCD/LED Display, A/D ConvertersDocument17 pagesICL7106, ICL7107, ICL7106S, ICL7107S: 3 / Digit, LCD/LED Display, A/D ConvertersDave MartzPas encore d'évaluation

- TC7106/A/TC7107/A: 3-1/2 Digit Analog-to-Digital ConvertersDocument32 pagesTC7106/A/TC7107/A: 3-1/2 Digit Analog-to-Digital ConvertersWai Yan LwinPas encore d'évaluation

- E Item 9 IDL800D-20B-E-PD-1Document1 pageE Item 9 IDL800D-20B-E-PD-1lusoegyi 1919Pas encore d'évaluation

- Datasheet TC7106-07Document27 pagesDatasheet TC7106-07zelgadis445Pas encore d'évaluation

- Di-91 Design Idea Tinyswitch-Iii: 12 W Universal Input CV AdapterDocument2 pagesDi-91 Design Idea Tinyswitch-Iii: 12 W Universal Input CV Adapterahmed chaouki ChamiPas encore d'évaluation

- TNY278PNDocument4 pagesTNY278PNJose BenavidesPas encore d'évaluation

- Speed Control of Motor - RKMS ProjectDocument34 pagesSpeed Control of Motor - RKMS ProjectAmit BarPas encore d'évaluation

- MCP33131/21/11-XX: 1 Msps/500 KSPS 16/14/12-Bit Single-Ended Input SAR ADCDocument54 pagesMCP33131/21/11-XX: 1 Msps/500 KSPS 16/14/12-Bit Single-Ended Input SAR ADCtrival001Pas encore d'évaluation

- GO1515 Voltage Controlled OscillatorDocument4 pagesGO1515 Voltage Controlled OscillatorMartinPas encore d'évaluation

- MCP 3008Document34 pagesMCP 3008Anita IonelaPas encore d'évaluation

- PLCC-28: NC Ain4-Rpm AIN3-O2VDocument8 pagesPLCC-28: NC Ain4-Rpm AIN3-O2V肖磊Pas encore d'évaluation

- ICL7106-7107 (Harris)Document16 pagesICL7106-7107 (Harris)cgmannerheimPas encore d'évaluation

- LTC 2499Document34 pagesLTC 2499m3rishorPas encore d'évaluation

- ISO 9141-2 ECU Simulator Features & Pin DescriptionDocument5 pagesISO 9141-2 ECU Simulator Features & Pin Description肖磊Pas encore d'évaluation

- FPD - M7 Boardspec 2012.12.17 - Ver1.3Document12 pagesFPD - M7 Boardspec 2012.12.17 - Ver1.3teveliskalvelisPas encore d'évaluation

- Bueno Eml 40ps Normaxgpon Onet1141lDocument32 pagesBueno Eml 40ps Normaxgpon Onet1141lJ. M. M.Pas encore d'évaluation

- Need of MicrocontrollerDocument18 pagesNeed of MicrocontrollerRaji PPas encore d'évaluation

- M35&36 Service Manual Parts GuideDocument96 pagesM35&36 Service Manual Parts GuideEugen BratuPas encore d'évaluation

- Analog Devices Circuits From The Process ControlDocument20 pagesAnalog Devices Circuits From The Process ControlDoru RazvanPas encore d'évaluation

- BD94062FDocument35 pagesBD94062FMazalan HectorPas encore d'évaluation

- ADu M7703024586Document22 pagesADu M7703024586Sergio MuriloPas encore d'évaluation

- High Efficiency 3A, 16V, 500Khz Synchronous Step Down ConverterDocument15 pagesHigh Efficiency 3A, 16V, 500Khz Synchronous Step Down ConverterkadirovPas encore d'évaluation

- An 477Document28 pagesAn 477radaresPas encore d'évaluation

- PLCC-28: FeaturesDocument5 pagesPLCC-28: Features肖磊Pas encore d'évaluation

- DZS900 User Manual-Heyuan IntelligenceDocument18 pagesDZS900 User Manual-Heyuan IntelligenceAntonio GarciaPas encore d'évaluation

- Snx-300 Service Manual (Eg)Document15 pagesSnx-300 Service Manual (Eg)Adriano CarvalhoPas encore d'évaluation

- J1850 VPWM ECU Simulator GuideDocument5 pagesJ1850 VPWM ECU Simulator Guide肖磊Pas encore d'évaluation

- Linear Technology LT2410 24bit - DatasheetDocument48 pagesLinear Technology LT2410 24bit - DatasheetdonatoPas encore d'évaluation

- EL2020Document14 pagesEL2020api-3825669Pas encore d'évaluation

- LM2405TDocument7 pagesLM2405TTeyfik koyuncuPas encore d'évaluation

- Integrated Circuits: 8-Bit Analog-to-Digital ConverterDocument19 pagesIntegrated Circuits: 8-Bit Analog-to-Digital ConverterСтанислав ИвановPas encore d'évaluation

- Description Features: Lt3746 32-Channel 20ma Led Driver With Buck ControllerDocument28 pagesDescription Features: Lt3746 32-Channel 20ma Led Driver With Buck ControllersuriantoPas encore d'évaluation

- Internal Guide: R.Valarmathi M.E., Lecturer, Department of EEE, DsecDocument26 pagesInternal Guide: R.Valarmathi M.E., Lecturer, Department of EEE, Dsecsetsindia3735Pas encore d'évaluation

- A Direct Digital Synthesis VFO For HF Bands: The Project in Few WordsDocument9 pagesA Direct Digital Synthesis VFO For HF Bands: The Project in Few WordsRafael SuarezPas encore d'évaluation

- Beginning Digital Electronics through ProjectsD'EverandBeginning Digital Electronics through ProjectsÉvaluation : 5 sur 5 étoiles5/5 (1)

- Linear IC Applications: A Designer's HandbookD'EverandLinear IC Applications: A Designer's HandbookÉvaluation : 4 sur 5 étoiles4/5 (1)

- Microprocessor System Design: A Practical IntroductionD'EverandMicroprocessor System Design: A Practical IntroductionPas encore d'évaluation

- 6MBI25L 120 Fuji ElectricDocument4 pages6MBI25L 120 Fuji ElectricFelipePerezPas encore d'évaluation

- 1mbi300n-120 Igbt ModuleDocument4 pages1mbi300n-120 Igbt ModuleFelipePerezPas encore d'évaluation

- LG 7184Document37 pagesLG 7184FelipePerezPas encore d'évaluation

- SiliconChipReview BitScope BS310Document4 pagesSiliconChipReview BitScope BS310FelipePerezPas encore d'évaluation

- MCP342X Datasheet PDFDocument58 pagesMCP342X Datasheet PDFFelipePerezPas encore d'évaluation

- Battery Indicator Hour MeterDocument1 pageBattery Indicator Hour MeterFelipePerezPas encore d'évaluation

- TCA 785 Phase Control IC for Thyristors, Triacs & TransistorsDocument16 pagesTCA 785 Phase Control IC for Thyristors, Triacs & TransistorsronaldotecnicoPas encore d'évaluation

- BLDC MotorControlDocument15 pagesBLDC MotorControlPradeep RajasekeranPas encore d'évaluation

- VF Control Pic16 0889bDocument24 pagesVF Control Pic16 0889barturo53Pas encore d'évaluation

- Daewoo CRT TV Service ManualDocument47 pagesDaewoo CRT TV Service ManualJorge G. Manzanero83% (6)

- DDocument392 pagesDTy Lê VănPas encore d'évaluation

- 4 20SC MaxSonar WR DatasheetDocument12 pages4 20SC MaxSonar WR DatasheetFelipePerez100% (1)

- BATTERY INDICATOR HOUR METER Parsic Italia PDFDocument1 pageBATTERY INDICATOR HOUR METER Parsic Italia PDFFelipePerezPas encore d'évaluation

- An-8201 FCM8201 Three-Phase Sine-Wave BLDC Motor ControllerDocument25 pagesAn-8201 FCM8201 Three-Phase Sine-Wave BLDC Motor ControllerFelipePerezPas encore d'évaluation

- Ka3525a 1010657Document9 pagesKa3525a 1010657FelipePerezPas encore d'évaluation

- Ft232bm Usb UartDocument24 pagesFt232bm Usb UartFelipePerezPas encore d'évaluation

- 9.3. Intake and Exhaust SystemDocument11 pages9.3. Intake and Exhaust SystemChristian Icaza SamaniegoPas encore d'évaluation

- AN1916 3phase BLDC Motor ControlDocument12 pagesAN1916 3phase BLDC Motor Controlchristopher_samsoonPas encore d'évaluation

- 9.4. Lubrication and MaintenanceDocument15 pages9.4. Lubrication and MaintenanceChristian Icaza SamaniegoPas encore d'évaluation

- Neral InformationDocument17 pagesNeral InformationChristian Icaza SamaniegoPas encore d'évaluation

- 9.1. Cooling SystemDocument17 pages9.1. Cooling SystemChristian Icaza SamaniegoPas encore d'évaluation

- 9.2. Engine MechanicalDocument67 pages9.2. Engine MechanicalFelipePerezPas encore d'évaluation

- Compresor GrasoDocument60 pagesCompresor GrasoFelipePerezPas encore d'évaluation

- Siemens LOGO Ethernet PDFDocument5 pagesSiemens LOGO Ethernet PDFWaldemar DominguezPas encore d'évaluation

- Data SheetDocument16 pagesData SheetMelani LarraínPas encore d'évaluation

- But12Af Silicon Diffused Power Transistor: General DescriptionDocument1 pageBut12Af Silicon Diffused Power Transistor: General DescriptionFelipePerezPas encore d'évaluation

- DMR 63PK PDFDocument11 pagesDMR 63PK PDFFelipePerezPas encore d'évaluation

- Nordson EFD 736HPA NV Installation Guide PDFDocument4 pagesNordson EFD 736HPA NV Installation Guide PDFFelipePerezPas encore d'évaluation

- Tsop 348Document7 pagesTsop 348FelipePerezPas encore d'évaluation

- Applications of Kinetic Methods in Thermal Analysis: A ReviewDocument13 pagesApplications of Kinetic Methods in Thermal Analysis: A ReviewAakash BharadwajPas encore d'évaluation

- Design of Seismic-Resistant Steel Building Structures: 1. Introduction and Basic PrinciplesDocument107 pagesDesign of Seismic-Resistant Steel Building Structures: 1. Introduction and Basic PrinciplesRamilArtates100% (3)

- CFPA E Guideline No 30 2013 FDocument25 pagesCFPA E Guideline No 30 2013 FMarcy LanePas encore d'évaluation

- Equipment Calibration/Maintenance: APPENDIX D - USFWS QA Program (5/04)Document5 pagesEquipment Calibration/Maintenance: APPENDIX D - USFWS QA Program (5/04)Defry Farhandinata100% (1)

- As 1833-2002 Austenitic Cast IronDocument6 pagesAs 1833-2002 Austenitic Cast IronSAI Global - APACPas encore d'évaluation

- Method Statement For LV Cables & Wires InstallationDocument6 pagesMethod Statement For LV Cables & Wires InstallationUmaira ZainalPas encore d'évaluation

- Full Download Ebook Ebook PDF Media and Communication in Canada Networks Culture Technology Audience Ninth 9th Edition PDFDocument42 pagesFull Download Ebook Ebook PDF Media and Communication in Canada Networks Culture Technology Audience Ninth 9th Edition PDFlillie.christopher194100% (38)

- Introduction To Treatment of Tannery EffluentsDocument69 pagesIntroduction To Treatment of Tannery EffluentsVíctor Villarreal La TorrePas encore d'évaluation

- BCS 031 PDFDocument37 pagesBCS 031 PDFGurjeet KaurPas encore d'évaluation

- Demo Teaching The FINALDocument41 pagesDemo Teaching The FINALjay lure baguioPas encore d'évaluation

- Week 4 Lower Reading Level Lesson PlanDocument3 pagesWeek 4 Lower Reading Level Lesson Planapi-533472774Pas encore d'évaluation

- Full Download Test Bank For Sociology 12th Edition Schaefer PDF Full ChapterDocument33 pagesFull Download Test Bank For Sociology 12th Edition Schaefer PDF Full Chaptergossamersnowshedq2dq100% (18)

- Slobin (2003)Document18 pagesSlobin (2003)Keith WheelerPas encore d'évaluation

- Updated-PdpDocument540 pagesUpdated-Pdpapi-648810768Pas encore d'évaluation

- PH127 Lectures Nov. 2022 4Document212 pagesPH127 Lectures Nov. 2022 4dicksonjohnxpPas encore d'évaluation

- MicroscopeDocument5 pagesMicroscopePrashant SinghalPas encore d'évaluation

- Geological Considerations in TunnellingDocument8 pagesGeological Considerations in Tunnellingpaul macharia100% (1)

- Direct Shear Box and Ring Shear Test: Why Internal Friction VariesDocument17 pagesDirect Shear Box and Ring Shear Test: Why Internal Friction VariesBarry OcayPas encore d'évaluation

- Green Disposable Diaper Market and Material AnalysisDocument136 pagesGreen Disposable Diaper Market and Material AnalysisNatan DerejePas encore d'évaluation

- Psychrometric Chart Analysis of Air-Water SampleDocument4 pagesPsychrometric Chart Analysis of Air-Water SampleJanry EfriyantoPas encore d'évaluation

- Decimal Fractions: Important Concepts and FormulaeDocument12 pagesDecimal Fractions: Important Concepts and FormulaechaostheoristPas encore d'évaluation

- 7.2 - EquilibriumDocument2 pages7.2 - EquilibriumLaura Warner0% (1)

- Lessons From LagaanDocument14 pagesLessons From LagaanNeha MhatrePas encore d'évaluation

- Cultural Lesson PlanDocument4 pagesCultural Lesson Planapi-247943642Pas encore d'évaluation

- Manifesting Fields of Reality by Aaity OlsonDocument2 pagesManifesting Fields of Reality by Aaity OlsonCarol McLeod100% (1)

- VI Sem. B.SC Maths - Elective Course - Graph Theory PDFDocument89 pagesVI Sem. B.SC Maths - Elective Course - Graph Theory PDFEduar CastañedaPas encore d'évaluation

- Economic Impact of Toyota Motor Manufacturing, Texas: Jim WisemanDocument12 pagesEconomic Impact of Toyota Motor Manufacturing, Texas: Jim WisemansengsenPas encore d'évaluation

- Mindray-Mindray DP-10 Ultrasound - 1 PCDocument6 pagesMindray-Mindray DP-10 Ultrasound - 1 PCAlfredo SalarPas encore d'évaluation

- The Research and Development of The Future Fashion Design: QIU Chunyan HU YueDocument5 pagesThe Research and Development of The Future Fashion Design: QIU Chunyan HU YueAva shinePas encore d'évaluation