Académique Documents

Professionnel Documents

Culture Documents

10 1 1 551 3131

Transféré par

Ratheesh KumarTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

10 1 1 551 3131

Transféré par

Ratheesh KumarDroits d'auteur :

Formats disponibles

23rd International Conference on Electricity Distribution Lyon, 15-18 June 2015

Paper 0480

ADVANCED VECTOR SHIFT ALGORITHM FOR ISLANDING DETECTION

Murali KANDAKATLA Hannu LAAKSONEN Sudheer BONELA

ABB GISL India ABB Oy Finland ABB GISL - India

murali.kandakatla@in.abb.com hannu.laaksonen@fi.abb.com b.sudheer@in.abb.com

The focus of this paper is on development of traditional

ABSTRACT passive islanding detection based on voltage vector shift.

In order to improve the reliability of vector shift based Voltage vector shift is still used for islanding detection in

many countries, although in Europe some countries, such

islanding detection an advanced vector shift algorithm has as Germany and Denmark, have forbidden its use for LOM

been developed. This algorithm can use all three phase detection due to its sensitivity to nuisance tripping.

voltages or a positive sequence voltage for vector shift However, in order to improve the reliability of vector shift

detection and will not cause nuisance tripping of DG units based islanding detection (no or less nuisance tripping of

due to other network disturbances. To validate the DG units due to other network events), an advanced vector

developed algorithm, a medium-voltage (MV) distribution shift algorithm has been developed and is presented in this

network with DG units has been modelled in the PSCAD paper.

simulation software. The algorithm is validated for its This algorithm uses all three phase voltages or positive

dependability, stability and fast operation with simulated sequence voltage for vector shift detection and will not

real islanding and different non-islanding events like cause nuisance tripping of DG units due to other network

faults, capacitor switching and connection of a parallel disturbances.

transformer. To validate the developed algorithm, a MV distribution

network with DG units has been modelled in the PSCAD

INTRODUCTION simulation software. The algorithm is validated for its

dependability, stability and fast operation with simulated

One of the key protection functionalities in Smart Grids real islanding and different non-islanding events like

will be reliable detection of islanding (or loss-of-mains, faults, capacitor switching and connection of a parallel

LOM). Although the trend in new grid codes is to require transformer. The developed vector shift algorithm is also

fault-ride-through (FRT) capability from distributed implemented to the intelligent electronic device (IED) and

generation (DG) units and possibly also to allow island the behavior of the algorithm is validated by injecting the

operation, there is still a need to reliably detect the simulated COMTRADE-files through an IED test setup.

islanding situation to make the correct operations, such as,

change the setting group of a DG interconnection relay or In the following sections, the basic vector shift principle

change the control principles and parameters of a DG unit. and the developed advanced vector shift algorithm are

Non-detection zone (NDZ) near power balance situations shown first. After that, the study network and example

and unwanted DG trips due to other network events simulation results are presented followed by conclusions.

(nuisance tripping) have been the major challenges with

traditional passive local islanding detection methods. If the PROPOSED ADVANCED VECTOR SHIFT

number of DG units in the distribution networks increases,

as is expected in the future, the risk of power balance ALGORITHM

situations will also increase. Therefore, the risk of possible Basic vector shift principle

operation in the NDZ of the traditional passive islanding

detection methods also will increase. In addition, f, U and The principle of voltage vector shift after islanding is

rate-of-change-of-frequency (ROCOF) will be used more explained with the help of the following system example.

often for defining the DG unit FRT requirements in the Figure 1 shows a synchronous generator equipped with a

new grid codes to enable utility grid stability supporting vector shift relay operating in parallel with a distribution

functionalities from DG units [1], [2]. network.

Due to the above-mentioned reasons in [1], a new, future-

proof, passive islanding detection algorithm without NDZ _ _ _

V Is VS Relay CB IGr

has been proposed. On the other hand, in [2] it has been Xd Grid

proposed that centralized active network management

functionalities (CANM) at the MV level, like voltage

control or losses minimization, could in the future include _

an algorithm which, in real time, confirms the operation of EI _

LOAD

VT

reliable islanding detection, even based on passive

methods like voltage phase angle-based methods or

voltage vector shift. The algorithm proposed in [2]

continuously ensures that there is enough reactive power

unbalance that the operation point remains constantly Figure 1. Equivalent circuit of a synchronous generator operating in

outside the NDZ of the used islanding detection method. parallel with the grid

CIRED 2015 1/5

23rd International Conference on Electricity Distribution Lyon, 15-18 June 2015

Paper 0480

When the generator current Is is passing through the voltages (when all three phase voltage are used). The

generator reactance Xd, there is a voltage difference V vector shift algorithm is blocked, when any of the

between the terminal voltage VT and the generator internal measured voltages drop below or increase above the

voltage EI (Figure 1). Consequently, there is a threshold values.

displacement angle between the terminal voltage and START

generator internal voltage. The phasor diagram is shown in U_AB Signal

Figure 2(a). After the circuit breaker opens, the system U_BC Signal

AngDif_AB = ABS(FFT angle(U_AB)t=0 FFT angle(U_AB)t= 2cycles old)

AngDif_BC = ABS(FFT angle(U_BC)t=0 FFT angle(U_BC)t= 2cycles old)

consisting of the generator and load becomes islanded. At U_CA Signal AngDif_CA = ABS(FFT angle(U_CA)t=0 FFT angle(U_CA)t= 2cycles old)

U1 Signal AngDif_U1 = ABS(FFT angle(U1)t=0 FFT angle(U1)t= 2cycles old)

this same time instant, the synchronous generator begins Fm - Measured

to feed a larger (or smaller) load because the current IGr frequency

FN - Nominal IF {(Fm)t=0 (Fm)t=5 cycles old} < 0.001 FN, THEN FStable = (Fm)t=5 cycles old

frequency CorrectionAngle = (FN -FStable)x2x360.

provided by the grid is interrupted. Due to this, the angular

difference between VT and EI is suddenly increased (or

decreased) and the terminal voltage phasor changes its Fstable > FN + 2.5 Hz

YES

OR

position as shown in Figure 2(b). The sudden vector shift Fstable < FN 2.5 Hz

due to islanding can also be seen in the voltage waveform

NO

in Figure 2(c). VSAng_AB = AngDif_AB + CorrectionAngle

VSAng_BC = AngDif_BC + CorrectionAngle

VSAng_CA = AngDif_CA + CorrectionAngle

VSAng_U1 = AngDif_U1 + CorrectionAngle

YES VSAng_AB > NO

Vector shift angle

YES VSAng_BC > NO

OR AND

Vector shift angle

YES VSAng_CA > NO

Vector shift angle

U_AB Signal

U_CA Signal

U_BC Signal

U1 Signal

Out of three phases, if any one of the phase detects vector shift, the

Occurrence of LOM algorithm is initiated.

V(t)

Vector shift algorithm

blocking based on measured

voltages UV Block After detection of Vector shift

in first phase, with in 10 ms YES

OR

is any of the blocking conditions

t activated?

OV Block

U_AB or U_BC or

U_CA

< Under voltage value NO

(c) Change in angle

After detection of Vector shift

Figure 2. Internal and terminal voltage phasors: (a) before islanding (b) in first phase, with in 1 cycle time NO

are all the three phases detected

after islanding. (c) vector shift in voltage waveform U_AB or U_BC or the vector shift ?

U_CA

Generally, vector shift relays measure the duration of each > Over voltage value

As a blocking condition is detected, the algorithm

is blocked internally and the binary output

cycle of the voltage signal from each phase. The duration INT_BLKD is activated.

of the present cycle is compared with the previous cycle YES

(which is considered as reference). In an islanding This confirms the ISLANDING condition.

The algorithm Issues a binary pulse of fixed 100 ms Vector shift operate

situation, the cycle duration is either shorter or longer OPERATE

depending if there is excess or deficit of active power in

the islanded system. If the measured vector shift angle

STOP

in the terminal voltage exceeds a predetermined threshold

Figure 3. Flowchart of the developed advanced vector shift algorithm

, a trip signal is immediately sent to the circuit breaker.

Some further analysis and comparisons related to different VALIDATION OF DEVELOPED NEW

vector shift algorithms etc. can be found from references VECTOR SHIFT ALGORITHM

[3]-[5].

Study network

Advanced vector shift algorithm A typical MV distribution network with DG units has been

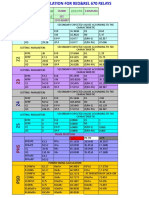

The proposed advanced vector shift algorithm is presented modelled in the PSCAD simulation software (Figure 4). In

in the form of a flowchart in Figure 3. This new algorithm the study network, the HV network is at 110 kV, the MV

uses all three phase voltages or a positive sequence voltage network at 21 kV and the LV network at 0.4 kV voltage

for vector shift detection. The developed algorithm takes levels. The load is mainly constant impedance-based

simultaneously into account the behavior of voltage and passive load (cos()=0.965 with larger MV island and

frequency, adapts to steady-state frequency variations and cos()=0.98 with smaller MV island and cos()=0.9725

has time-dependent correlation checks between phase with cable lines), and small part of the load is constant

CIRED 2015 2/5

23rd International Conference on Electricity Distribution Lyon, 15-18 June 2015

Paper 0480

power load. The system line types and line parameters are vector shift angle behaviour and binary output signals

also presented in Figure 4. Simulations were done with a (operate and internal blocking) for vector shift algorithm

directly connected synchronous generator (SG) based DG are presented.

unit at the MV feeder and other DG units as well as de- Voltage magnitude in three phases

Voltage(pu)

centralized compensation coils were disconnected (Figure 1

U AB

U BC

4). U CA

0.8

19.9 20 20.1 20.2 20.3 20.4 20.5

Time(s)

Vector shift angle detected in three phases

Angle(Degrees)

30

VSAng AB

20

VSAng BC

10

VSAng CA

0

19.9 20 20.1 20.2 20.3 20.4 20.5

Time(s)

Vector shift algorithm Operate and Blocked signals

Binary outputs

1

OPERATE

0.5 INT BLKD

0

19.9 20 20.1 20.2 20.3 20.4 20.5

Time(s)

Figure 5. Vector shift algorithm operation during islanding in small

power unbalance

From Figure 5, it can be seen that after islanding at 20.0 s,

the vector shift angles start to increase in all three phases.

After the detected vector shift angle has increased above

the pick-up setting, the algorithm issues an OPERATE

pulse output at around 20.25 s, because no blocking

Figure 4. Study network used in PSCAD simulations conditions have been activated.

The advanced vector shift algorithm is tested for its Islanding in Large Power Unbalance

dependability and stability in different simulation cases. This case is similar to the previous one, but the power

The simulated islanding cases consist of testing the unbalance before islanding is now larger (Figure 6).

dependability of the algorithm in cases where the Voltage magnitude in three phases

algorithm is supposed to operate. All these islanding cases 1

Voltage(pu)

U AB

0.5 U BC

are simulated by opening the MV feeder CB (A in Figure U CA

4) or the recloser CB (B in Figure 4) at time 20.0 s and 0

19.9 20 20.1 20.2 20.3 20.4 20.5

Time(s)

by closing the CB 0.3 s later i.e. at 20.3 s. The faults and Vector shift angle detected in three phases

Angle(Degrees)

200

other network disturbances related simulation cases, i.e. VSAng AB

100 VSAng BC

cases where the algorithm should not operate, were done 0

VSAng CA

19.9 20 20.1 20.2 20.3 20.4 20.5

to test the stability of the algorithm. Time(s)

Vector shift algorithm Operate and Blocked signals

Binary outputs

During the PSCAD simulations from different cases, the 1

OPERATE

0.5 INT BLKD

phase-to-phase voltage measurements (UAB, UBC, UCA)

0

from the MV network and the LV network are recorded to 19.9 20 20.1 20.2

Time(s)

20.3 20.4 20.5

a COMTRADE-file format. The proposed algorithm is Figure 6. Vector shift algorithm operation during islanding in large

tested with these voltage measurements from different power unbalance

simulated cases and the results are presented in the

following sections. During the testing, the algorithm pick- From Figure 6, one can see that after islanding at 20.0 s,

up value setting, i.e. vector shift angle, was 5 degrees and the vector shift angles start to increase in all three phases.

the algorithm blocking settings for undervoltage was 0.80 When compared with the islanding in small power

pu and for overvoltage 1.2 pu. unbalance, the vector shift can now be detected faster as

expected. In this case, the algorithm issues an OPERATE

Real Islanding Cases pulse output at around 20.05 s.

Islanding in Small Power Unbalance Faults and Other Network Disturbances

When islanding in small power unbalance, the local Phase-to-Earth Fault

generation is a bit larger (or smaller) than the local load in In this case, the phase-to-earth (A-G) fault for 150 ms, is

the MV network. When the generation is larger than the applied in the middle of the same MV feeder (viii in

load, the power is exported to the utility grid. Respectively, Figure 4), i.e. 15 km from the recloser CB. Fault resistance

if the local generation is smaller than the local load, then Rf = 1000 . In Figure 7, phase-to-phase voltage

the deficit power is imported from the utility grid. magnitudes, voltage vector shift angle behavior and binary

However, results for the vector shift algorithm are similar output signals for vector shift Operate and blocking are

in both cases if the size of the power unbalance is equal. In presented.

Figure 5, phase-to-phase voltage magnitudes, voltage From Figure 7, it can be observed that during the A-G

CIRED 2015 3/5

23rd International Conference on Electricity Distribution Lyon, 15-18 June 2015

Paper 0480

Voltage magnitude in three phases

fault, the vector shift angles are only 0.3 degrees in two

Voltage(pu)

1 U AB

phase-to-phase voltages (UAB, UCA). Because the detected 0.5 U BC

vector shift angles are less than the pick-up setting and the U CA

0

19.9 20 20.1 20.2 20.3 20.4 20.5

vector shift is not detected in all three phases, the Time(s)

Vector shift angle detected in three phases

Angle(Degrees)

developed vector shift algorithm is not operated. 80

VSAng AB

40 VSAng BC

Voltage magnitude in three phases

0.97 VSAng CA

Voltage(pu)

U AB 0

19.9 20 20.1 20.2 20.3 20.4 20.5

0.96 U BC Time(s)

U CA Vector shift algorithm Operate and Blocked signals

Binary outputs

0.95

19.9 20 20.1 20.2 20.3 20.4 20.5 1

Time(s)

OPERATE

Vector shift angle detected in three phases 0.5 INT BLKD

Angle(Degrees)

0.4 0

VSAng AB 19.9 20 20.1 20.2 20.3 20.4 20.5

0.2 VSAng BC Time(s)

VSAng CA

0

19.9 20 20.1 20.2 20.3 20.4 20.5

Figure 9. Vector shift algorithm behavior during A-B-C fault at the

Time(s) beginning of the adjacent MV feeder

Vector shift algorithm Operate and Blocked signals

Binary outputs

1

OPERATE From Figure 9, one can see that during the A-B-C fault, all

0 INT BLKD

-1

three phase-to-phase voltages vector shift angles are

19.9 20 20.1 20.2 20.3 20.4 20.5

Time(s) significantly above the pick-up setting (5 degrees). But the

Figure 7. Vector shift algorithm behavior during A-G fault in the three phase-to-phase voltage magnitudes are below the set

middle of the same MV feeder undervoltage value (0.8 pu), which caused activation of the

Phase-to-Phase Fault algorithm internal block (INT_BLKD). Due to this internal

In this case, the phase-to-phase (A-B) fault for 150 ms is blocking the developed vector shift algorithm is not

applied in the middle of the adjacent MV feeder (ix in operated.

Figure 4). Fault resistance Rf = 5 . The results are 30% Voltage Dip in HV Network

presented in Figure 8. In this case, the 3-phase 30 % voltage dip is simulated in a

Voltage magnitude in three phases 110 kV HV network (xi in Figure 4). The results are

1

Voltage(pu)

U AB presented in Figure 10.

U BC

0.8

U CA Voltage magnitude in three phases

19.9 20 20.1 20.2 20.3 20.4 20.5 1

Voltage(pu)

Time(s) U AB

Vector shift angle detected in three phases 0.8 U BC

Angle(Degrees)

10 U CA

VSAng AB 0.6

19.9 20 20.1 20.2 20.3 20.4 20.5

5 VSAng BC Time(s)

VSAng CA Vector shift angle detected in three phases

0

Angle(Degrees)

19.9 20 20.1 20.2 20.3 20.4 20.5 4

Time(s) VSAng AB

Vector shift algorithm Operate and Blocked signals 2 VSAng BC

Binary outputs

1 VSAng CA

OPERATE 0

0.5 INT BLKD 19.9 20 20.1 20.2 20.3 20.4 20.5

Time(s)

0 Vector shift algorithm Operate and Blocked signals

Binary outputs

19.9 20 20.1 20.2 20.3 20.4 20.5

Time(s) 1

OPERATE

0.5 INT BLKD

Figure 8. Vector shift algorithm behavior during A-B fault in the

0

middle of the adjacent MV feeder 19.9 20 20.1 20.2 20.3 20.4 20.5

Time(s)

From Figure 8, it can be seen that during the A-B fault, the Figure 10. Vector shift algorithm behavior during a 3-phase 30%

UAB, UCA voltages vector shift angles are above the pick- voltage dip in HV network

up setting (5 degrees), but the vector shift angle of UBC is From Figure 10, it can be observed that during a 30 %

below the setting. The UAB voltage magnitude is just below voltage dip in the HV network, all three phase-to-phase

the set undervoltage value (0.8 pu), which caused voltage magnitudes are below the set undervoltage value

activation of the algorithm internal block (INT_BLKD). (0.8 pu), which caused activation of the algorithm internal

Due to these issues, the developed vector shift algorithm is block (INT_BLKD).

not operated.

Capacitor Switching at HV/MV Substation

Three-Phase Fault In this case, the capacitor switching at the HV/MV

In this case, the 3-phase (A-B-C) fault with fault resistance substation is simulated (iv in Figure 4).The results are

Rf = 1 for 150 ms is applied at the beginning of the presented in Figure 11.

adjacent MV feeder (x in Figure 4). The results are

shown in Figure 9.

CIRED 2015 4/5

23rd International Conference on Electricity Distribution Lyon, 15-18 June 2015

Paper 0480

Voltage magnitude in three phases

1 reduce DG unit nuisance tripping because it is stable

Voltage(pu)

U AB

U BC during various network disturbances like faults, capacitor

U CA

0.95

19.9 20 20.1 20.2 20.3 20.4 20.5

switching and connection of parallel transformer.

Time(s)

Vector shift angle detected in three phases Although the proposed vector shift algorithm guarantees

Angle(Degrees)

1.5

VSAng AB

1

VSAng BC

fast and reliable islanding detection in nearly all

0.5

0

VSAng CA operational conditions when the DG unit is running in

19.9 20 20.1 20.2 20.3 20.4 20.5

Time(s) parallel with the utility grid supply, certain cases may still

Vector shift algorithm Operate and Blocked signals

cause mal-operations. If the power unbalance before

Binary outputs

1

OPERATE

0 INT BLKD islanding is very small and the detected vector shift angle

-1

19.9 20 20.1 20.2 20.3 20.4 20.5

is therefore also small, the function may not operate. This

Time(s)

means that the vector shift algorithm, like many traditional

Figure 11. Vector shift algorithm behavior during capacitor switching

event

passive islanding detection methods, still has NDZ near a

power balance situation. Therefore, other passive methods

From Figure 11, it can be seen that during capacitor for detecting the islanding without NDZ should be further

switching, the voltage magnitudes are stable around 1 pu developed. Potential methods to deal with this NDZ issue

and the vector shift angles around 1 degree. The detected could be, for example, the multi-criteria based passive

vector shift angles are less than the setting and vector shift islanding detection method [1] or use of active MV

is not detected in all three phases. Due to these issues the network management [2].

proposed vector shift algorithm is not operated.

Connection of Parallel Transformer at HV/MV REFERENCES

Substation [1] H. Laaksonen, 2012, "New Multi-Criteria Based

In this case, parallel transformer at the HV/MV substation Algorithm for Islanding Detection in Smart Grids",

is connected to the system (v in Figure 4). The results are IEEE PES ISGT Europe 2012, Berlin, Germany.

presented in Figure 12. [2] H. Laaksonen, 2014, "Reliable Islanding Detection

Voltage magnitude in three phases with Active MV Network Management", CIRED

0.97

Voltage(pu)

U AB Workshop, 11-12 June 2014, Rome.

0.965 U BC

U CA [3] A. Beddoes, P. Thomas, M. Gosden, 2005, "Loss of

0.96

19.9 20 20.1 20.2 20.3 20.4 20.5 Mains Protection Relay Performances when

Time(s)

Vector shift angle detected in three phases Subjected to Network Disturbances/Events", CIRED

Angle(Degrees)

1

VSAng AB

0.5 VSAng BC

18th International conference on electricity

VSAng CA distribution, 6-9 June 2005, Turin.

0

19.9 20 20.1 20.2 20.3 20.4 20.5

Time(s) [4] W. Freitas, Z. Huang, W. Xu, 2005, "A Practical

Vector shift algorithm Operate and Blocked signals

Binary outputs

1

OPERATE

Method for Assesing the Effectiveness of Vector

0 INT BLKD Surge Relays for Distributed Generation

-1

19.9 20 20.1 20.2 20.3 20.4 20.5 Applications", IEEE Transcations on Power

Time(s)

Delivery, vol. 20, no. 1

Figure 12. Vector shift algorithm behavior when connecting a parallel

transformer [5] W. Freitas, W. Xu, 2005, "Comparative Analysis

Between ROCOF and Vector Surge Relays for

From Figure 12, one can see that when connecting a Distributed Generation Applications", IEEE

parallel transformer, the voltage magnitudes are stable Transcations on Power Delivery, vol. 20, no. 2

around 1 pu and the vector shift angles around 0.5 degrees.

The detected vector shift angles are less than the setting

and therefore the proposed vector shift algorithm is not

operated.

CONCLUSIONS

In this paper a new advanced vector shift algorithm is

presented to improve the dependability and stability of the

voltage vector shift based islanding detection. The

developed algorithm can adaptively correct the measured

vector shift angle based on the steady-state frequency

variations, which makes the algorithm immune to steady-

state frequency variations. Based on the presented test

results, it can be concluded that the developed algorithm

successfully detects the islanding condition during small

and large power unbalances. In addition, the algorithm can

CIRED 2015 5/5

Vous aimerez peut-être aussi

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Testing of Transformer Diff - RelayDocument25 pagesTesting of Transformer Diff - Relaydeepak2628Pas encore d'évaluation

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- 10 1 1 551 3131Document29 pages10 1 1 551 3131Ratheesh KumarPas encore d'évaluation

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Curvas SobrecorrienteDocument9 pagesCurvas SobrecorrienteAnova2Pas encore d'évaluation

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- 10 1 1 551 3131Document5 pages10 1 1 551 3131Ratheesh KumarPas encore d'évaluation

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- Testing of Transformer Diff - RelayDocument25 pagesTesting of Transformer Diff - Relaydeepak2628Pas encore d'évaluation

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- CIRED2015 0480 FinalDocument178 pagesCIRED2015 0480 FinalRatheesh KumarPas encore d'évaluation

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- SA2008-000355 en Universal Testing Method For Power Transformer DifferentiaDocument15 pagesSA2008-000355 en Universal Testing Method For Power Transformer DifferentiaRatheesh KumarPas encore d'évaluation

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Direction A LocDocument4 pagesDirection A LocRatheesh KumarPas encore d'évaluation

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- RTU Training DIGSI Training DIGSI001 5Document97 pagesRTU Training DIGSI Training DIGSI001 5Ratheesh KumarPas encore d'évaluation

- Direction A LocDocument4 pagesDirection A LocRatheesh KumarPas encore d'évaluation

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Microsoft Word - STATOR PROTECTION. Final ReportDocument11 pagesMicrosoft Word - STATOR PROTECTION. Final ReportHari Krishna.MPas encore d'évaluation

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- Back To The Basics CTDocument4 pagesBack To The Basics CTAnonymous OCDJg17ZPas encore d'évaluation

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- 04 Fault CalculationsDocument31 pages04 Fault CalculationsRatheesh KumarPas encore d'évaluation

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- 04 Fault CalculationsDocument15 pages04 Fault Calculationsapi-3750225100% (1)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

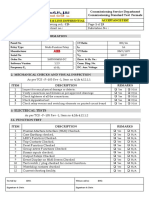

- Commissioning of Electrical SystemsDocument14 pagesCommissioning of Electrical SystemsRatheesh Kumar100% (1)

- Relay Characteristic AngleDocument14 pagesRelay Characteristic AngleAji Istanto Rambono100% (1)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- AcSELerator QuickSet Designer SEL 5031 IDocument2 pagesAcSELerator QuickSet Designer SEL 5031 IRatheesh KumarPas encore d'évaluation

- Commissioning of Electrical SystemsDocument7 pagesCommissioning of Electrical SystemsRatheesh KumarPas encore d'évaluation

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- Commissioning Service Department Commissioning Standard Test Formats Description: Numerical Line Differential Protection Relay 7Sd522Document27 pagesCommissioning Service Department Commissioning Standard Test Formats Description: Numerical Line Differential Protection Relay 7Sd522Rajesh Sawale100% (1)

- Field and VectoresDocument27 pagesField and VectoresMyameSiramePas encore d'évaluation

- Abb Rec670 Cap Bank ProtnDocument11 pagesAbb Rec670 Cap Bank ProtnRatheesh KumarPas encore d'évaluation

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Ret 670 Calculation Gsu3-87uatDocument33 pagesRet 670 Calculation Gsu3-87uatRatheesh KumarPas encore d'évaluation

- Sec Calc Fault Locator For Red Rel 670Document3 pagesSec Calc Fault Locator For Red Rel 670ZokiPas encore d'évaluation

- Red670 Distance Line DifferentialDocument23 pagesRed670 Distance Line DifferentialRatheesh KumarPas encore d'évaluation

- 7ut - Transformer Diff Relay TestDocument25 pages7ut - Transformer Diff Relay TestAnoss Olier100% (2)

- TR Differential Ret670 Y YDocument19 pagesTR Differential Ret670 Y Ym khPas encore d'évaluation

- Sel-411l - Line DifferentialDocument21 pagesSel-411l - Line DifferentialRatheesh KumarPas encore d'évaluation

- Final Test: RET 670 Transformer Differential 1/3-Phase Pickup CalculationDocument10 pagesFinal Test: RET 670 Transformer Differential 1/3-Phase Pickup CalculationAnoss OlierPas encore d'évaluation

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- TM GUIDE (Basic Competencies)Document19 pagesTM GUIDE (Basic Competencies)Emelito T. ColentumPas encore d'évaluation

- Brochure Delegation Training For LeadersDocument6 pagesBrochure Delegation Training For LeadersSupport ALProgramsPas encore d'évaluation

- Thetford c250 InstallationDocument19 pagesThetford c250 InstallationCatalin Bejan100% (1)

- What Is StevedoringDocument10 pagesWhat Is StevedoringMinhaj KmPas encore d'évaluation

- Busch, Buchmüller, LeyendeckerDocument29 pagesBusch, Buchmüller, LeyendeckerAkis PanPas encore d'évaluation

- NCS V5 1.0 Layer Name FormatDocument4 pagesNCS V5 1.0 Layer Name FormatGouhar NayabPas encore d'évaluation

- High Performance ComputingDocument294 pagesHigh Performance Computingsorinbazavan100% (1)

- Determining Load Ratios For Technical Rescue Systems and EquipmentDocument2 pagesDetermining Load Ratios For Technical Rescue Systems and EquipmentAhmad Zubair Rasuly0% (1)

- Final Project Report by Himanshu Yadav Student of Fostiima Business SchoolDocument55 pagesFinal Project Report by Himanshu Yadav Student of Fostiima Business Schoolak88901Pas encore d'évaluation

- Business English IDocument8 pagesBusiness English ILarbi Ben TamaPas encore d'évaluation

- Perfil Clinico de Pacientes Con Trastornos de La Conducta AlimentariaDocument44 pagesPerfil Clinico de Pacientes Con Trastornos de La Conducta AlimentariaFrida PandoPas encore d'évaluation

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Combustion FundamentalsDocument30 pagesCombustion FundamentalsPrem SagarPas encore d'évaluation

- Chinese MedicineDocument16 pagesChinese MedicineTrisPas encore d'évaluation

- Jerehy's ReportDocument65 pagesJerehy's Reportkupetroleum3Pas encore d'évaluation

- Otis C. Mitchell - Hitler-s-Stormtroopers-and-the-Attack-on-the-German-Republic-1919-1933 PDFDocument201 pagesOtis C. Mitchell - Hitler-s-Stormtroopers-and-the-Attack-on-the-German-Republic-1919-1933 PDFbodyfull100% (2)

- Data Iep Goals and Objectives ExampleDocument4 pagesData Iep Goals and Objectives Exampleapi-455438287100% (2)

- RULE 130 Rules of CourtDocument141 pagesRULE 130 Rules of CourtalotcepilloPas encore d'évaluation

- Under The SHODH Program For ResearchDocument3 pagesUnder The SHODH Program For ResearchSurya ShuklaPas encore d'évaluation

- Argumentative EssayDocument7 pagesArgumentative EssayHoang Thi Huyen DieuPas encore d'évaluation

- FPA 03-A.01 Permohonan Akreditasi LP LK LI LM PUP PBADocument595 pagesFPA 03-A.01 Permohonan Akreditasi LP LK LI LM PUP PBAabimanyubawonoPas encore d'évaluation

- Helena HelsenDocument2 pagesHelena HelsenragastrmaPas encore d'évaluation

- Nemo Outdoor 8.40 User Guide PDFDocument392 pagesNemo Outdoor 8.40 User Guide PDFXxbugmenotxXPas encore d'évaluation

- Another Look at Pistis ChristouDocument17 pagesAnother Look at Pistis Christouakimel100% (1)

- Metric Conversion WorksheetDocument3 pagesMetric Conversion WorksheetKaiden HughesPas encore d'évaluation

- Power Factor Improvement SystemDocument25 pagesPower Factor Improvement SystemBijoy SahaPas encore d'évaluation

- Body LanguageDocument17 pagesBody LanguageAR PiZaPas encore d'évaluation

- SocialPolitical and Cultural ChangeDocument8 pagesSocialPolitical and Cultural ChangeChristine Mae BeramoPas encore d'évaluation

- Position Trading Maximizing Probability of Winning TradesDocument91 pagesPosition Trading Maximizing Probability of Winning Tradescarlo bakaakoPas encore d'évaluation

- Glorious Mysteries 1Document5 pagesGlorious Mysteries 1Vincent safariPas encore d'évaluation

- Heat Cured ElastomersDocument40 pagesHeat Cured ElastomerslberrierPas encore d'évaluation

- Build a Mathematical Mind - Even If You Think You Can't Have One: Become a Pattern Detective. Boost Your Critical and Logical Thinking Skills.D'EverandBuild a Mathematical Mind - Even If You Think You Can't Have One: Become a Pattern Detective. Boost Your Critical and Logical Thinking Skills.Évaluation : 5 sur 5 étoiles5/5 (1)

- Basic Math & Pre-Algebra Workbook For Dummies with Online PracticeD'EverandBasic Math & Pre-Algebra Workbook For Dummies with Online PracticeÉvaluation : 4 sur 5 étoiles4/5 (2)

- Quantum Physics: A Beginners Guide to How Quantum Physics Affects Everything around UsD'EverandQuantum Physics: A Beginners Guide to How Quantum Physics Affects Everything around UsÉvaluation : 4.5 sur 5 étoiles4.5/5 (3)

- Mathematical Mindsets: Unleashing Students' Potential through Creative Math, Inspiring Messages and Innovative TeachingD'EverandMathematical Mindsets: Unleashing Students' Potential through Creative Math, Inspiring Messages and Innovative TeachingÉvaluation : 4.5 sur 5 étoiles4.5/5 (21)

- Calculus Workbook For Dummies with Online PracticeD'EverandCalculus Workbook For Dummies with Online PracticeÉvaluation : 3.5 sur 5 étoiles3.5/5 (8)