Académique Documents

Professionnel Documents

Culture Documents

Datasheet - Ta3020

Transféré par

Dawid MleczkoTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Datasheet - Ta3020

Transféré par

Dawid MleczkoDroits d'auteur :

Formats disponibles

Tr i path Technol ogy, I nc.

- Techni cal I nfor m ati on

TA3020

STEREO 300W (4) CLASS-T DIGITAL AUDIO AMPLIFIER DRIVER

USING DIGITAL POWER PROCESSING (DPP T M ) TECHNOLOGY

Technical Information Revision 2 November 2001

GENERAL DESCRIPTION

The TA3020 is a two-channel, 300W (4) per channel Amplifier Driver IC that uses

TM

Tripaths proprietary Digital Power Processing (DPP ) technology. Class-T amplifiers

offer both the audio fidelity of Class-AB and the power efficiency of Class-D amplifiers.

APPLICATIONS FEATURES

Audio/Video Amplifiers & Receivers C l a s s - T a r c h i te c tu r e

Pro-audio Amplifiers Proprietary Digital Power Processing technology

Automobile Power Amplifiers Audiophile Sound Quality

Subwoofer Amplifiers 0.02% THD+N @ 50W, 8

0.03% IHF-IM @ 30W, 8

BENEFITS High Efficiency

Reduced system cost with smaller/less 95% @ 150W @ 8

expensive power supply and heat sink 90% @ 275W @ 4

Signal fidelity equal to high quality Class- Supports wide range of output power levels

AB amplifiers Up to 300W/channel (4), single-ended outputs

High dynamic range compatible with Up to 1000W (4), bridged outputs

digital media such as CD and DVD Output over-current protection

Over- and under-voltage protection

48-pin DIP (dual-inline package)

TYPICAL PERFORMANCE

THD+N versus Output Power versus Supply Voltage

RL = 4

10

f = 1kHz

5 BBM = 80nS

BW = 22Hz - 22kHz

2

39V 45V 54V

1

THD+N (%)

0.5

0.2

0.1

0.05

0.02

0.01

1 2 5 10 20 50 100 200 500

Output Power (W)

1 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

Absolute Maximum Ratings (Note 1)

SYMBOL PARAMETER Value UNITS

VPP, VNN Supply Voltage +/- 70 V

V5 Positive 5 V Bias Supply 6 V

Voltage at Input Pins (pins 12-16, 18, 19-26, 29-33, 37) -0.3V to (V5+0.3V)

VN10 Voltage for FET drive VNN+13 V

TSTORE Storage Temperature Range -55 to 150 C

TA Operating Free-air Temperature Range (Note 2) -40 to 85 C

TJ Junction Temperature 150 C

ESDHB ESD Susceptibility Human Body Model (Note 3)

All pins TBD V

ESDMM ESD Susceptibility Machine Model (Note 4)

All pins TBD V

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

See the table below for Operating Conditions.

Note 2: This is a target specification. Characterization is still needed to validate this temperature range.

Note 3: Human body model, 100pF discharged through a 1.5K resistor.

Note 4: Machine model, 220pF 240pF discharged through all pins.

Operating Conditions (Note 5)

SYMBOL PARAMETER MIN. TYP. MAX. UNITS

VPP, VNN Supply Voltage +/- 15 +/-45 +/- 65 V

V5 Positive 5 V Bias Supply 4.5 5 5.5 V

VN10 Voltage for FET drive (Volts above VNN) 9 10 12 V

Note 5: Recommended Operating Conditions indicate conditions for which the device is functional.

See Electrical Characteristics for guaranteed specific performance limits.

2 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

Electrical Characteristics (Note 6)

TA = 25 C. See Application/Test Circuit on page 7. Unless otherwise noted, the supply voltage is VPP=|VNN|=45V.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNITS

Iq Quiescent Current VPP = +45V 90 mA

(No load, BBM0=1,BBM1=0, VNN = -45V 90 mA

Mute = 0V) V5 = 5V 45 TBD mA

VN10 = 10V 200 TBD mA

IMUTE Mute Supply Current VPP = +45V 1 mA

(No load, Mute = 5V) VNN = -45V 1 mA

V5 = 5V 20 TBD mA

VN10 = 10V 1 mA

VIH High-level input voltage (MUTE) 3.5 V

VIL Low-level input voltage (MUTE) 1.0 V

VOH High-level output voltage (HMUTE) IOH = 3mA 4.0 V

VOL Low-level output voltage (HMUTE) IOL = 3mA 0.5 V

VOFFSET Output Offset Voltage No Load, MUTE = Logic low -TBD TBD mV

0.1% RFBA, RFBB, RFBC resistors

IOC Over Current Sense Voltage TBD TBD 1.0 TBD V

Threshold

IVPPSENSE VPPSENSE Threshold Currents Over-voltage turn on (muted) 162 TBD A

Over-voltage turn off (mute off) TBD 154 A

Under-voltage turn off (mute off) 79 TBD A

Under-voltage turn on (muted) TBD 72 A

VVPPSENSE Threshold Voltages with Over-voltage turn on (muted) TBD TBD V

RVPPSENSE = XXK Over-voltage turn off (mute off) TBD TBD V

Under-voltage turn off (mute off) TBD TBD V

Under-voltage turn on (muted) TBD TBD V

IVNNSENSE VNNSENSE Threshold Currents Over-voltage turn on (muted) 174 TBD A

Over-voltage turn off (mute off) TBD 169 A

Under-voltage turn off (mute off) 86 TBD A

Under-voltage turn on (muted) TBD 77 A

VVNNSENSE Threshold Voltages with Over-voltage turn on (muted) TBD TBD V

RVNNSENSE = XXK Over-voltage turn off (mute off) TBD TBD V

Under-voltage turn off (mute off) TBD TBD V

Under-voltage turn on (muted) TBD TBD V

Note 6: Minimum and maximum limits are guaranteed but may not be 100% tested.

Note 7: These supply voltages are calculated using the IVPPSENSE and IVNNSENSE values shown in the Electrical

Characteristics table. The typical voltage values shown are calculated using a RVPPSENSE and RVNNSENSE

value of 422kohm without any tolerance variation. The minimum and maximum voltage limits shown include

either a +1% or 1% (+1% for Over-voltage turn on and Under-voltage turn off, -1% for Over-voltage turn off

and Under-voltage turn on) variation of RVPPSENSE or RVNNSENSE off the nominal 422kohm and 392kohm

values. These voltage specifications are examples to show both typical and worst case voltage ranges for a

given RVPPSENSE and RVNNSENSE resistor values of 422kohm and 392kohm. Please refer to the

Application Information section for a more detailed description of how to calculate the over and under voltage

trip voltages for a given resistor value.

Note 8: The fact that the over-voltage turn on specifications exceed the absolute maximum of +/-70V for

the TA3020 does not imply that the part will work at these elevated supply voltages. It also does

not imply that the TA3020 is tested or guaranteed at these supply voltages. The supply voltages

are simply a calculation based on the process spread of the IVPPSENSE and IVNNSENSE

currents (see note 7). The supply voltage must be maintained below the absolute maximum of

+/-70V or permanent damage to the TA3020 may occur.

3 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

Performance Characteristics Single Ended

TA = 25 C. Unless otherwise noted, the supply voltage is VPP=|VNN|=45V, the input frequency is 1kHz and the

measurement bandwidth is 20kHz. See Application/Test Circuit.

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNITS

POUT Output Power THD+N = 0.1%, RL = 8 100 W

(continuous RMS/Channel) RL = 4 190 W

THD+N = 1%, RL = 8 120 W

RL = 4 220 W

THD + N Total Harmonic Distortion Plus POUT = 50W/Channel, RL = 8 0.02 %

Noise

IHF-IM IHF Intermodulation Distortion 19kHz, 20kHz, 1:1 (IHF), RL = 8 0.03 %

POUT = 30W/Channel

SNR Signal-to-Noise Ratio A Weighted, RL = 4, 102 dB

POUT = 275W/Channel

CS Channel Separation 0dBr = 30W, RL = 8, f = 1kHz 97 dB

Power Efficiency POUT = 150W/Channel, RL = 8 95 %

AV Amplifier Gain POUT = 10W/Channel, RL = 4 TBD V/V

See Application / Test Circuit

AVERROR Channel to Channel Gain Error POUT = 10W/Channel, RL = 4 0.5 dB

See Application / Test Circuit

eNOUT Output Noise Voltage A Weighted, no signal, input shorted, 260 V

DC offset nulled to zero

TA3020 Pinout

48-pin Dip

(Top View)

VN10 1 48 LO1

LO2 2 47 LO1COM

LO2COM 3 46 HO1COM

HO2COM 4 45 HO1

HO2 5 44 OCS1HN

OCS2LN 6 43 OCS1HP

OCS2LP 7 42 OCS1LP

OCS2HP 8 41 OCS1LN

OCS2HN 9 40 VBOOT1

VBOOT2 10 39 VNN

NC 11 38 NC

OCR2 12 37 OCR1

FBKOUT1 13 36 NC

FBKGND1 14 35 V5

HMUTE 15 34 AGND

FBKOUT2 16 33 OCR1

DCOMP 17 32 REF1

FBKGND2 18 31 OCR2

BIASCAP 19 30 VNNSENSE

INV2 20 29 VPPSENSE

OAOUT2 21 28 AGND

BBM0 22 27 V5

BBM1 23 26 OAOUT1

MUTE 24 25 INV1

4 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

Pin Description

Pin Function Description

1 VN10 Floating supply input for the FET drive circuitry. This voltage must be stable

and referenced to VNN.

2,48 LO2, LO1 Low side gate drive output (Channel 2 & 1)

3,47 LO2COM, LO1COM Kelvin connection to source of low-side transistor (Channel 2 & 1)

4,46 HO2COM, HO1COM Kelvin connection to source of high-side transistor (Channel 2 & 1)

5,45 HO2, HO1 High side gate drive output (Channel 2 & 1)

6, 7 OCS2LN, OCS2LP Over Current Sense inputs, Channel 2 low-side

8, 9 OCS2HP, OCS2HN Over Current Sense inputs, Channel 2 high-side

10, 40 VBOOT2, VBOOT1 Bootstrapped voltage to supply drive to gate of high-side FET

(Channel 2 & 1)

12, 31 OCR2 Over-current threshold adjustment (Channel 2)

13, 16 FBKOUT1, FBKOUT2 Switching feedback (Channels 1 & 2)

14, 18 FBKGND1, FBKGND2 Ground Kelvin feedback (Channels 1 & 2)

15 HMUTE Logic Output. A logic high indicates both amplifiers are muted, due to the

mute pin state, or a fault such as an overcurrent, undervoltage, or

overvoltage condition.

17 DCOMP Internal mode selection. This pin must be grounded for proper device

operation.

19 BIASCAP Bandgap reference times two (typically 2.5VDC). Used to set the common

mode voltage for the input op amps. This pin is not capable of driving external

circuitry.

20, 25 INV2, INV1 Inverting inputs of Input Stage op amps. (Channels 2 & 1)

21, 26 OAOUT2, OAOUT1 Outputs of Input Stage op amps. (Channels 2 & 1)

22, 23 BBM0, BBM1 Break-before-make timing control to prevent shoot-through in the output FETs.

24 MUTE Logic input. A logic high puts the amplifier in mute mode. Ground pin if not

used. Please refer to the section, Mute Control, in the Application Information.

27, 35 V5 5V power supply input.

28,34 AGND Analog ground.

29 VPPSENSE Positive supply voltage sense input. This pin is used for both over and

under voltage sensing for the VPP supply.

30 VNNSENSE Negative supply voltage sense input. This pin is used for both over and under

voltage sensing for the VNN supply.

32 REF Used to set internal bias currents. The pin voltage is typically 1.1V.

33, 37 OCR1 Over-current threshold adjustment (Channel 1)

39 VNN Negative supply voltage.

41, 42 OCS1LN, OCS1LP Over Current Sense inputs, Channel 1 low-side

43, 44 OCS1HP, OCS1HN Over Current Sense inputs, Channel 1 high-side

11, 36, NC Not connected (bonded) internally. To minimize coupling between pins, tie

38 these pins to AGND (pin34).

5 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

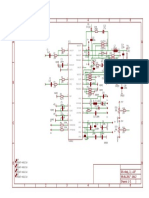

Application/Test Circuit

TA3 0 2 0

43 OCS1HP VPP

CS + CS

RS 0.1uF DB MUR120 330uF

OAOUT1 26 0.01, 1W VN10

44 OCS1HN

RB 250

CI

RF 40 VBOOT1

3.3uF V5 RG QO

20K CHBR CHBR

+ INV1 25 5.6, 1W CB + CBAUX

- 45 HO1 0.1uF 33uF

RI + 0.1uF 47uF

ROFB 46 HO1COM +

49.9K 499K AGND

V5 (Pin 27) VN10 RG QO LO

ROFB Processing CO RZ

5.6, 1W 10uH

ROFA 499K & 48 LO1 0.22uF 20, 2W

10K COF Modulation 47 LO1COM CZ RL

Offset Trim 0.1uF 42 OCS1LP 0.22uF 4 or 8

Circuit RS

AGND (Pin 28) 0.01, 1W

41 OCS1LN

2.5V 37 OCR1 VNN

33 OCR1 CS CS

V5 (Pin 27) 0.1uF

+

330uF

CA 200K COCR ROCR

0.1uF 220pF 20K RFBA RFBA

BIASCAP 19 1K 1K

AGND

(Pin 28) *RFBC

(Pin 28)

13 FBKOUT1 13.3K

V5 14 FBKGND1

CFB *RFBC

5V *RFBB *RFBB 13.3K

150pF

1.07K 1.07K

MUTE 24

AGND (Pin 28)

(Pin 28) 15 HMUTE

RREF

8.25K, 1%

REF 32

(Pin 28)

OAOUT2 21 7 OCS2HP VPP

CS + CS

CI

RF RS 0.1uF DB MUR120 330uF

3.3uF V5 0.01, 1W VN10

20K 8 OCS2HN

+ INV2 20 RB 250

- 10 VBOOT2

RI +

RG

ROFB QO

49.9K AGND 5.6, 1W CHBR CHBR CB + CBAUX

499K 5 HO2 0.1uF 33uF 0.1uF 47uF

V5 (Pin 27) 4 HO2COM +

ROFB

ROFA 499K

VN10 RG QO LO

10K COF Processing CO RZ

5.6, 1W 10uH

Offset Trim 0.1uF & 2 LO2 0.22uF 20, 2W

Circuit 3 LO2COM

AGND (Pin 28) Modulation CZ RL

7 OCS2LP 0.22uF 4 or 8

BBM0 22 RS

8 OCS2LN 0.01, 1W

BBM1 23

12 OCR2 VNN

31 OCR2 CS CS

DCOMP 17

V5 (Pin 27) 0.1uF 330uF

+

COCR ROCR

220pF 20K RFBA RFBA

27 1K 1K

5V V5

AGND

CS (Pin 28) *RFBC

0.1uF 13.3K

28 16 FBKOUT2

AGND

18 FBKGND2

CFB *RFBC

35 *RFBB *RFBB 13.3K

V5 270pF

1.07K 1.07K

CS

0.1uF 34

AGND AGND (Pin 28)

*RVNN1 450K, 1% VN10 1 VN10

VNN

30 VNNSENSE CSW

0.1uF,35V

*RVPP1 450K, 1% VNN

29 VPPSENSE

VPP VNN 39 VNN

*RVNN2 1.35M, 1% NC 38

V5 11 NC NC 36

*RVPP1 450K, 1%

V5

F. BEAD Analog Ground

Power Ground

* The values of these components must be

adjusted based on supply voltage range.

See Application Information.

6 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

External Components Description (Refer to the Application/Test Circuit)

Components Description

RI Inverting input resistance to provide AC gain in conjunction with RF. This input is

biased at the BIASCAP voltage (approximately 2.5VDC).

RF Feedback resistor to set AC gain in conjunction with RI. Please refer to the Amplifier

Gain paragraph, in the Application Information section.

CI AC input coupling capacitor which, in conjunction with RI, forms a highpass filter at

fC = 1 (2RICI ) .

RFBA Feedback divider resistor connected to V5. This resistor is normally set at 1k.

RFBB Feedback divider resistor connected to AGND. This value of this resistor depends

on the supply voltage setting and helps set the TA3020 gain in conjunction with RI,

RF, RFBA, and RFBC. Please see the Modulator Feedback Design paragraphs in the

Application Information Section.

RFBC Feedback resistor connected from either the OUT1(OUT2) to FBKOUT1(FBKOUT2)

or speaker ground to FBKGND1(FBKGND2). The value of this resistor depends on

the supply voltage setting and helps set the TA3020 gain in conjunction with RI, RF,

RFBA,, and RFBB. It should be noted that the resistor from OUT1(OUT2) to

FBKOUT1(FBKOUT2) must have a power rating of greater than PDISS = VPP2 (2RFBC) .

Please see the Modulator Feedback Design paragraphs in the Application

Information Section.

CFB Feedback delay capacitor that both lowers the idle switching frequency and filters

very high frequency noise from the feedback signal, which improves amplifier

performance. The value of CFB should be offset between channel 1 and channel 2

so that the idle switching difference is greater than 40kHz. Please refer to the

Application / Test Circuit.

ROFA Potentiometer used to manually trim the DC offset on the output of the TA3020.

ROFB Resistor that limits the manual DC offset trim range and allows for more precise

adjustment.

RREF Bias resistor. Locate close to pin 32 and ground at pin 28.

CA BIASCAP decoupling capacitor. Should be located close to pin 19 and grounded at

pin 28.

DB Bootstrap diode. This diode charges up the bootstrap capacitors when the output is

low (at VNN) to drive the high side gate circuitry. A fast or ultra fast recovery diode

is recommended for the bootstrap circuitry. In addition, the bootstrap diode must be

able to sustain the entire VPP-VNN voltage. Thus, for most applications, a 150V (or

greater) diode should be used.

CB High frequency bootstrap capacitor, which filters the high side gate drive supply.

This capacitor must be located as close to pin 40 (VBOOT1) or pin10 (VBOOT2) for

reliable operation. The negative side of CB should be connected directly to the

HO1COM (pin 46) or HO2COM (pin 4). Please refer to the Application / Test Circuit.

CBAUX Bulk bootstrap capacitor that supplements CB during clipping events, which result

in a reduction in the average switching frequency.

RB Bootstrap resistor that limits CBAUX charging current during TA3020 power up

(bootstrap supply charging).

CSW VN10 generator filter capacitors. The high frequency capacitor (0.1uF) must be

located close to pin 1 (VN10) to maximize device performance.

CS Supply decoupling for the power supply pins. For optimum performance, these

components should be located close to the TA3020 and returned to their respective

ground as shown in the Application/Test Circuit.

RVNN1 Main overvoltage and undervoltage sense resistor for the negative supply (VNN).

Please refer to the Electrical Characteristics Section for the trip points as well as the

hysteresis band. Also, please refer to the Over / Under-voltage Protection section in

the Application Information for a detailed discussion of the internal circuit operation

and external component selection.

RVNN2 Secondary overvoltage and undervoltage sense resistor for the negative supply

(VNN). This resistor accounts for the internal VNNSENSE bias of 1.25V. Nominal

resistor value should be three times that of RVNN1. Please refer to the Over / Under-

voltage Protection section in the Application Information for a detailed discussion of

7 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

the internal circuit operation and external component selection.

RVPP1 Main overvoltage and undervoltage sense resistor for the positive supply (VPP).

Please refer to the Electrical Characteristics Section for the trip points as well as the

hysteresis band. Also, please refer to the Over / Under-voltage Protection section in

the Application Information for a detailed discussion of the internal circuit operation

and external component selection.

RVPP2 Secondary overvoltage and undervoltage sense resistor for the positive supply

(VPP). This resistor accounts for the internal VPPSENSE bias of 2.5V. Nominal

resistor value should be equal to that of RVPP1. Please refer to the Over / Under-

voltage Protection section in the Application Information for a detailed discussion of

the internal circuit operation and external component selection.

RS Over-current sense resistor. Please refer to the section, Setting the Over-current

Threshold, in the Application Information for a discussion of how to choose the value

of RS to obtain a specific current limit trip point.

ROCR Over-current trim resistor, which, in conjunction with RS, sets the current trip point.

Please refer to the section, Setting the Over-current Threshold, in the Application

Information for a discussion of how to calculate the value of ROCR.

COCR Over-current filter capacitor, which filters the overcurrent signal at the OCR pins to

account for the half-wave rectified current sense circuit internal to the TA3020. A

typical value for this component is 220pF. In addition, this component should be

located near pin 31 or pin 33 as possible.

CHBR Supply decoupling for the high current Half-bridge supply pins. These components

must be located as close to the output MOSFETs as possible to minimize output

ringing which causes power supply overshoot. By reducing overshoot, these

capacitors maximize both the TA3020 and output MOSFET reliability. These

capacitors should have good high frequency performance including low ESR and

low ESL. In addition, the capacitor rating must be twice the maximum VPP voltage.

Panasonic EB capacitors are ideal for the bulk storage (nominally 33uF) due to their

high ripple current and high frequency design.

RG Gate resistor, which is used to control the MOSFET rise/ fall times. This resistor

serves to dampen the parasitics at the MOSFET gates, which, in turn, minimizes

ringing and output overshoots. The typical power rating is 1 watt.

CZ Zobel capacitor, which in conjunction with RZ, terminates the output filter at high

frequencies. Use a high quality film capacitor capable of sustaining the ripple current

caused by the switching outputs.

RZ Zobel resistor, which in conjunction with CZ, terminates the output filter at high

frequencies. The combination of RZ and CZ minimizes peaking of the output filter

under both no load conditions or with real world loads, including loudspeakers which

usually exhibit a rising impedance with increasing frequency. Depending on the

program material, the power rating of RZ may need to be adjusted. The typical

power rating is 2 watts.

LO Output inductor, which in conjunction with CO, demodulates (filters) the switching

waveform into an audio signal. Forms a second order filter with a cutoff frequency

of f C = 1 ( 2 L O C O ) and a quality factor of Q = R L C O L O C O .

CO Output capacitor, which, in conjunction with LO, demodulates (filters) the switching

waveform into an audio signal. Forms a second order low-pass filter with a cutoff

frequency of f C = 1 ( 2 L O C O ) and a quality factor of Q = R L C O L O C O . Use

a high quality film capacitor capable of sustaining the ripple current caused by the

switching outputs.

8 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

Typical Performance

THD+N versus Output Power Efficiency versus Output Power

10

100

f = 1kHz RL = 8

5

BBM = 80nS 90

Vs =+28V RL = 4

2 BW = 22Hz - 22kHz 80

RL = 8 RL = 4

1 70

Efficiency (%)

0.5 60

THD+N (%)

50

0.2

40

0.1

f = 1kHz

30 BBM = 80nS

0.05 Vs =+28V

20 THD+N =<10%

0.02

10

0.01

2 5 10 20 50 100 200 0

Output Power (W) 0 20 40 60 80 100 120

Output Power (W)

Intermodulation Performance Intermodulation Performance

RL = 4 RL = 8

+0 +0

-10 19kHz, 20kHz, 1:1 -10 19kHz, 20kHz, 1:1

Pout = 40W/Channel Pout = 20W/Channel

-20 0dBr = 12.65Vrms -20 0dBr = 12.65Vrms

Vs = +28V Vs =+28V

-30

BW = 22Hz - 22kHz -30

BW = 22Hz - 22kHz

-40 -40

-50 -50

FFT (dBr)

-60 -60

FFT (dBr)

-70 -70

-80 -80

-90 -90

-100 -100

-110 -110

-120 -120

20 50 100 200 500 1k 2k 5k 10k 20k 20 50 100 200 500 1k 2k 5k 10k 20k

Frequency (Hz) Frequency (Hz)

Channel Separation versus Frequency

-40 Noise Floor

-45 -70

4

Pout = 40W/Channel @

-50

8

Pout = 20W/Channel @ VS =+28V

VS = +28V -75 BBM = 80nS

-55 BW = 22Hz - 22kHz 16K FFT

-60 -80 Fs = 48kHz

BW = 22Hz - 22kHz

-65

Channel Separation (dBr)

-85

Noise FFT (dBV)

-70

-75 -90

-80

-95

-85

RL = 4

-90

-100

-95

-100 -105

-105

RL = 8 -110

-110

-115 -115

-120

20 50 100 200 500 1k 2k 5k 10k 20k

-120

Frequency (Hz) 20 50 100 200 500 1k 2k 5k 10k 20k

Frequency (Hz)

9 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

Typical Performance

THD+N versus Frequency versus Break Before Make THD+N versus Frequency versus Break Before Make

RL = 4 RL = 8

10 10

Pout = 20W/Channel

5 Pout = 40W/Channel 5 Vs =+28V

Vs =+28V BW = 22Hz - 22kHz

BW = 22Hz - 22kHz

2 2

1 1

THD+N (%)

0.5 0.5

THD+N (%)

0.2 0.2

BBM = 120nS BBM = 120nS

0.1 0.1

0.05 0.05

0.02 0.02

BBM = 80nS

BBM = 80nS

0.01 0.01

20 50 100 200 500 1k 2k 5k 10k 20k 20 50 100 200 500 1k 2k 5k 10k 20k

Frequency (Hz) Frequency (Hz)

THD+N versus Frequency versus Bandwidth THD+N versus Frequency versus Bandwidth

RL = 4 RL = 8

10 10

Pout = 40W/Channel Pout = 20W/Channel

Vs =+28V Vs =+28V

5 5

BBM = 80nS BBM = 80nS

2 2

1 1

0.5 0.5

THD+N (%)

THD+N (%)

0.2 0.2

0.1 0.1

BW = 30kHz

0.05 0.05

BW = 30kHz

0.02 0.02

BW = 22kHz

BW = 22kHz

0.01 0.01

20 50 100 200 500 1k 2k 5k 10k 20k 20 50 100 200 500 1k 2k 5k 10k 20k

Frequency (Hz) Frequency (Hz)

THD+N versus Output Power versus Supply Voltage THD+N versus Output Power versus Supply Voltage

RL = 4 RL = 8

10 10

f = 1kHz f = 1kHz

5 BBM = 80nS 5 BBM = 80nS

BW = 22Hz - 22kHz BW = 22Hz - 22kHz

2 2

23V 28V 35V

23V 28V 35V

1 1

THD+N (%)

THD+N (%)

0.5 0.5

0.2 0.2

0.1 0.1

0.05 0.05

0.02 0.02

0.01 0.01

1 2 5 10 20 50 100 200 2 5 10 20 50 100 200

Output Power (W) Output Power (W)

10 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

Typical Performance

Efficiency versus Output Power

THD+N versus Output Power 100

10

f = 1kHz RL = 8

5 BBM = 80nS

Vs =+45V RL = 4

BW = 22Hz - 22kHz 80

2

RL = 8 RL = 4

1

Efficiency (%)

60

0.5

THD+N (%)

0.2

40

0.1

f = 1kHz

0.05 BBM = 80nS

20

Vs = +45V

THD+N<10%

0.02

0

0.01

2 5 10 20 50 100 200 500 0 50 100 150 200 250 300

Output Power (W) Output Power (W)

Intermodulation Performance Intermodulation Performance

RL = 4 RL = 8

+0

+0

19kHz, 20kHz, 1:1 -10 19kHz, 20kHz, 1:1

-10

Pout = 60W/Channel Pout = 30W/Channel

0dBr = 15.5Vrms 0dBr = 15.5Vrms

-20

-20

Vs = +45V Vs =+45V

BW = 22Hz - 22kHz BW = 22Hz - 22kHz

-30

-30

-40

-40

-50 -50

FFT (dBr)

FFT (dBr)

-60 -60

-70 -70

-80 -80

-90 -90

-100 -100

-110 -110

-120 -120

20 50 100 200 500 1k 2k 5k 10k 20k 20 50 100 200 500 1k 2k 5k 10k 20k

Frequency (Hz) Frequency (Hz)

Channel Separation versus Frequency

Noise Floor

-40 -70

-45 4

Pout = 60W/Channel @ VS = +/-45V

8

Pout = 30W/Channel @ BBM = 80nS

-50 VS = +45V -75

16kFFT

BW = 22Hz - 22kHz FS = 48kHz

-55

-80 BW = 22Hz-22kHz

-60

Channel Separation (dBr)

-65 -85

-70

Amplitude (dBV)

-90

-75

-80

-95

-85

RL = 4

-90 -100

-95

-105

-100

RL = 8

-105 -110

-110

-115

-115

-120

20 50 100 200 500 1k 2k 5k 10k 20k -120

20 50 100 200 500 1k 2k 5k 10k 20k

Frequency (Hz) Frequency (Hz)

11 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

Typical Performance

THD+N versus Frequency versus Break Before Make THD+N versus Frequency versus Break Before Make

RL = 4 RL = 8

10 10

Pout = 30W/Channel

Pout = 60W/Channel

Vs =+45V

5 Vs =+45V 5

BW = 20Hz - 22kHz

BW = 22Hz - 22kHz

2 2

1 1

THD+N (%)

THD+N (%)

0.5 0.5

0.2 0.2

BBM = 120nS

BBM = 120nS

0.1 0.1

0.05 0.05

BBM = 80nS

0.02 0.02

BBM = 80nS

0.01 0.01

20 50 100 200 500 1k 2k 5k 10k 20k 20 50 100 200 500 1k 2k 5k 10k 20k

Frequency (Hz) Frequency (Hz)

THD+N versus Frequency versus Bandwidth THD+N versus Frequency versus Bandwidth

RL = 4 RL = 8

10

10

Pout = 60W/Channel Pout = 30W/Channel

Vs =+45V 5 Vs =+45V

5

BBM = 80nS BBM = 80nS

2

2

1 1

0.5 0.5

THD+N (%)

THD+N (%)

0.2 0.2

BW = 30kHz

0.1 BW = 30kHz 0.1

0.05 0.05

0.02 BW = 22kHz 0.02

BW = 22kHz

0.01 0.01

20 50 100 200 500 1k 2k 5k 10k 20k 20 50 100 200 500 1k 2k 5k 10k 20k

Frequency (Hz) Frequency (Hz)

THD+N versus Output Power versus Supply Voltage THD+N versus Output Power versus Supply Voltage

RL = 4 RL = 8

10 10

f = 1kHz f = 1kHz

5 BBM = 80nS 5 BBM = 80nS

BW = 22Hz - 22kHz BW = 22Hz - 22kHz

2 2

39V 45V 54V 39V 45V 54V

1 1

THD+N (%)

THD+N (%)

0.5 0.5

0.2 0.2

0.1 0.1

0.05 0.05

0.02 0.02

0.01 0.01

1 2 5 10 20 50 100 200 500 2 5 10 20 50 100 200 500

Output Power (W) Output Power (W)

12 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

Application Information

Figure 1 is a simplified diagram of one channel (Channel 1) of a TA3020 amplifier to assist in understanding its

operation.

BBM0 22

43 OCS1HP VPP

BBM1 23 OVER

CURRENT CS DB

OAOUT1 26 RS VN10

DETECTION 44 OCS1HN

RB

40 VBOOT1

CI RI RF

V5 RG QO

+ INV1 25 CB +

- 45 HO1 CBAUX

+ 0.1uF

ROFB 46 HO1COM CHBR

AGND

V5 VN10 QO OUTPUT

Processing RG

ROFB 48 LO1 FILTER

ROFA & RL

Modulation 47 LO1COM

COF 2.5V

Offset Trim OVER 42 OCS1LP

Circuit CURRENT RS

CA

DETECTION 41 OCS1LN

BIASCAP 19

VNN

V5 33,37 OCR1 CS

V5

COCR ROCR

5V

MUTE 24 RFBA RFBA

RFBC

13 FBKOUT1

REF 32 14 FBKGND1

RREF CFB RFBC

RFBB RFBB

*RVNN1

VNNSENSE 30

VNN OVER/

*RVPP1 UNDER

VPPSENSE 29 VOLTAGE

VPP DETECTION

15 HMUTE

*RVNN2

V5

*RVPP1 1

VN10 VN10

V5

V5 27,35 CSW

5V

VNN

CS

AGND 28,34 VNN 39 VNN

F. BEAD Analog Ground

Power Ground

Figure 1: Simplified TA3020 Amplifier

TA3020 Basic Amplifier Operation

The audio input signal is fed to the processor internal to the TA3020, where a switching pattern is generated.

The average idle (no input) switching frequency is approximately 700kHz. With an input signal, the pattern is

spread spectrum and varies between approximately 200kHz and 1.5MHz depending on input signal level and

frequency. Complementary copies of the switching pattern are level-shifted by the MOSFET drivers and output

from the TA3020 where they drive the gates (HO1 and LO1) of external power MOSFETs that are connected

as a half bridge. The output of the half bridge is a power-amplified version of the switching pattern that

switches between VPP and VNN. This signal is then low-pass filtered to obtain an amplified reproduction of the

audio input signal.

The processor portion of the TA3020 is operated from a 5-volt supply. In the generation of the switching

patterns for the output MOSFETs, the processor inserts a break-before-make dead time between the turn-off

of one transistor and the turn-on of the other in order to minimize shoot-through currents in the MOSFETs. The

dead time can be programmed by setting the break-before-make control bits, BBM1 and BBM0. Feedback

information from the output of the half-bridge is supplied to the processor via FBKOUT1. Additional feedback

information to account for ground bounce is supplied via FBKGND1.

The MOSFET drivers in the TA3020 are operated from voltages obtained from VN10 and LO1COM for the low-

side driver, and VBOOT1 and HO1COM for the high-side driver. VN10 must be a regulated 10V above VNN.

N-Channel MOSFETs are used for both the top and bottom of the half bridge. The gate resistors, RG, are used

to control MOSFET slew rate and thereby minimize voltage overshoots.

13 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

Circuit Board Layout

The TA3020 is a power (high current) amplifier that operates at relatively high switching frequencies. The

output of the amplifier switches between VPP and VNN at high speeds while driving large currents. This high-

frequency digital signal is passed through an LC low-pass filter to recover the amplified audio signal. Since the

amplifier must drive the inductive LC output filter and speaker loads, the amplifier outputs can be pulled above

the supply voltage and below ground by the energy in the output inductance. To avoid subjecting the TA3020

to potentially damaging voltage stress, it is critical to have a good printed circuit board layout. It is

recommended that Tripaths layout and application circuit be used for all applications and only be deviated from

after careful analysis of the effects of any changes. Please refer to the TA3020 evaluation board document,

EB-TA3020, available on the Tripath website, at www.tripath.com.

The following components are important to place near either their associated TA3020 or output MOSFET pins.

The recommendations are ranked in order of layout importance, either for proper device operation or

performance considerations.

- The capacitors, CHBR, provide high frequency bypassing of the amplifier power supplies and will serve

to reduce spikes across the supply rails. Please note that both mosfet half-bridges must be

decoupled separately. In addition, the voltage rating for CHBR should be at least 150V as this

capacitor is exposed to the full supply range, VPP-VNN.

- CFB removes very high frequency components from the amplifier feedback signals and lowers the

output switching frequency by delaying the feedback signals. In addition, the value of CFB is different

for channel 1 and channel 2 to keep the average switching frequency difference greater than 40kHz.

This minimizes in-band audio noise. Locate these capacitors as close to their respective TA3020 pin

as possible.

- To minimize noise pickup and minimize THD+N, RFBC should be located as close to the TA3020 as

possible. Make sure that the routing of the high voltage feedback lines is kept far away from the

input op amps or significant noise coupling may occur. It is best to shield the high voltage feedback

lines by using a ground plane around these traces as well as the input section.

- CB, CSW provides high frequency bypassing for the VN10 and bootstrap supplies. Very high currents

are present on these supplies.

In general, to enable placement as close to the TA3020, and minimize PCB parasitics, the capacitors CFB, CB

and CSW should be surface mount types, located on the solder side of the board.

Some components are not sensitive to location but are very sensitive to layout and trace routing.

- To maximize the damping factor and reduce distortion and noise, the modulator feedback

connections should be routed directly to the pins of the output inductors. LO. Please refer to the EB-

TA3020This was done on the EB-TA3020 for additional information.

- The output filter capacitor, CO, and zobel capacitor, CZ, should be star connected with the load return.

The output ground feedback signal should be taken from this star point.

- The modulator feedback resistors, RFBA, RFBB, and RFBC, should all be grounded and attached to 5V

together. These connections will serve to minimize common mode noise via the differential

feedback. Please refer to the EB-TA3020 evaluation board for more information.

- The feedback signals that come directly from the output inductors are high voltage and high

frequency in nature. If they are routed close to the input nodes, INV1 and INV2, the high impedance

inverting opamp pins will pick up noise. This coupling will result in significant background noise,

especially when the input is AC coupled to ground, or an external source such as a CD player or

signal generator is connected. Thus, care should be taken such that the feedback lines are not

routed near any of the input section.

14 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

- To minimize the possibility of any noise pickup, the trace lengths of INV1 and INV2 should be kept as

short as possible. This is most easily accomplished by locating the input resistors, RI and the input

stage feedback resistors, RF as close to the TA3020 as possible. In addition, the offset trim resistor,

ROFB, which connects to either INV1,or INV2, should be located close to the TA3020 input section.

TA3020 Grounding

Proper grounding techniques are required to maximize TA3020 functionality and performance. Parametric

parameters such as THD+N, Noise Floor and Crosstalk can be adversely affected if proper grounding

techniques are not implemented on the PCB layout. The following discussion highlights some

recommendations about grounding both with respect to the TA3020 as well as general audio system design

rules.

The TA3020 is divided into two sections: the input section, which spans pin 12 through pin 37, and the output

(high voltage) section, which spans pin 1 through pin 10 and pin 39 through pin 48. On the TA3020 evaluation

board, the ground is also divided into distinct sections, one for the input and one for the output. To minimize

ground loops and keep the audio noise floor as low as possible, the input and output ground must be only

connected at a single point. Depending on the system design, the single point connection may be in the form

of a ferrite bead or a PCB trace.

The analog grounds, pin 28 and pin 34 must be connected locally at the TA3020 for proper device functionality.

The ground for the V5 power supply should connect directly to pin 28. Additionally, any external input circuitry

such as preamps, or active filters, should be referenced to pin 28.

For the power section, Tripath has traditionally used a star grounding scheme. Thus, the load ground returns

and the power supply decoupling traces are routed separately back to the power supply. In addition, any type

of shield or chassis connection would be connected directly to the ground star located at the power supply.

These precautions will both minimize audible noise and enhance the crosstalk performance of the TA3020.

The TA3020 incorporates a differential feedback system to minimize the effects of ground bounce and cancel

out common mode ground noise. As such, the feedback from the output ground for each channel needs to be

properly sensed. This can be accomplished by connecting the output ground sensing trace directly to the star

formed by the output ground return, output capacitor, CO, and the zobel capacitor, CZ. Refer to the Application /

Test Circuit for a schematic description.

TA3020 Amplifier Gain

The gain of the TA3020 is the product of the input stage gain and the modulator gain. Please refer to the

sections, Input Stage Design, and Modulator Feedback Design, for a complete explanation of how to determine

the external component values.

A VTA3020 = A VINPUTSTAG E * A V MODULATOR

R F R FBC * (R FBA + R FBB )

A VTA3020 + 1

RI R FBA * R FBB

For example, using a TA3020 with the following external components,

RI = 20k

RF = 20k

RFBA = 1k

RFBB = 1.13k

RFBC = 9.09k

20k 13.3k * (1.0k + 1.07k ) V

A VTA3020 + 1 = - 10.71

49.9k 1.0k * 1.07k V

15 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

Input Stage Design

The TA3020 input stage is configured as an inverting amplifier, allowing the system designer flexibility in setting

the input stage gain and frequency response. Figure 2 shows a typical application where the input stage is a

constant gain inverting amplifier. The input stage gain should be set so that the maximum input signal level will

drive the input stage output to 4Vpp.

The gain of the input stage, above the low frequency high pass filter point, is that of a simple inverting amplifier:

RF

A VINPUTSTAG E =

RI

Figure 2: Input Stage

TA3020

OAOUT1

V5

RF

CI RI

INV1 -

INPUT1

+

BIASCAP AGND

V5

+

INV2

-

RF

CI RI AGND

OAOUT2

INPUT2

Input Capacitor Selection

CIN can be calculated once a value for RIN has been determined. CIN and RIN determine the input low-frequency

pole. Typically this pole is set at 10Hz. CIN is calculated according to:

CIN = 1 / (2 x FP x RIN)

where: RIN = Input resistor value in ohms

FP = Input low frequency pole (typically 10Hz)

Modulator Feedback Design

The modulator converts the signal from the input stage to the high-voltage output signal. The optimum gain of

the modulator is determined from the maximum allowable feedback level for the modulator and maximum

supply voltages for the power stage. Depending on the maximum supply voltage, the feedback ratio will need

to be adjusted to maximize performance. The values of RFBA, RFBB and RFBC (see explanation below) define the

gain of the modulator. Once these values are chosen, based on the maximum supply voltage, the gain of the

modulator will be fixed even with as the supply voltage fluctuates due to current draw.

For the best signal-to-noise ratio and lowest distortion, the maximum modulator feedback voltage should be

approximately 4Vpp. This will keep the gain of the modulator as low as possible and still allow headroom so

that the feedback signal does not clip the modulator feedback stage.

Figure 3 shows how the feedback from the output of the amplifier is returned to the input of the modulator. The

input to the modulator (FBKOUT1/FBKGND1 for channel 1) can be viewed as inputs to an inverting differential

amplifier. RFBA and RFBB bias the feedback signal to approximately 2.5V and RFBC scales the large OUT1/OUT2

signal to down to 4Vpp.

16 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

1/2 TA3020

V5

RFBA RFBA

RFBC

Processing FBKOUT1 OUT1

& RFBC

FBKGND1 OUT 1 GROUND

Modulation

RFBB RFBB

AGND

Figure 3: Modulator Feedback

The modulator feedback resistors are:

R FBA = User specified, typically 1K

R FBA * VPP

R FBB =

(VPP - 4)

R FBA * VPP

R FBC =

4

R FBC * (R FBA + R FBB )

A V - MODULATOR +1

R FBA * R FBB

The above equations assume that VPP=|VNN|.

For example, in a system with VPPMAX=52V and VNNMAX=-52V,

RFBA = 1k, 1%

RFBB = 1.08k, use 1.07k, 1%

RFBC = 13.0k, use 13.3k, 1%

The resultant modulator gain is:

13.3k * (1.0k + 1.07k )

AV - MODULATOR + 1 = 26.73V/V

1.0k * 1.07k

Mute

When a logic high signal is supplied to MUTE, both amplifier channels are muted (both high- and low-side

transistors are turned off). When a logic level low is supplied to MUTE, both amplifiers are fully operational.

There is a delay of approximately 200 milliseconds between the de-assertion of MUTE and the un-muting of the

TA3020.

Turn-on & Turn-off Noise

If turn-on or turn-off noise is present in a TA3020 amplifier, the cause is frequently due to other circuitry

external to the TA3020. While the TA3020 has circuitry to suppress turn-on and turn-off transients, the

combination of the power supply and other audio circuitry with the TA3020 in a particular application may

17 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

exhibit audible transients. One solution that will completely eliminate turn-on and turn-off pops and clicks is to

use a relay to connect/disconnect the amplifier from the speakers with the appropriate timing at power on/off.

The relay can also be used to protect the speakers from a component failure (e.g. shorted output MOSFET),

which is a protection mechanism that some amplifiers have. Circuitry external to the TA3020 would need to be

implemented to detect these failures.

DC Offset

While the DC offset voltages that appear at the speaker terminals of a TA3020 amplifier are typically small,

Tripath recommends that any offsets during operation be nulled out of the amplifier with a circuit like the one

shown connected to IN1 and IN2 in the Test/Application Circuit.

It should be noted that the DC voltage on the output of a TA3020 amplifier with no load in mute will not be zero.

This offset does not need to be nulled. The output impedance of the amplifier in mute mode is approximately

10K. This means that the DC voltage drops to essentially zero when a typical load is connected.

HMUTE

The HMUTE pin is a 5V logic output that indicates various fault conditions within the device. These conditions

include: over-current, overvoltage and undervoltage. The HMUTE output is capable of directly driving an LED

through a series 2k resistor.

Over-current Protection

The TA3020 has over-current protection circuitry to protect itself and the output transistors from short-circuit

conditions. The TA3020 uses the voltage across a resistor RS (measured via OCS1HP, OCS1HN, OCS1LP

and OCS1LN) that is in series with each output MOSFET to detect an over-current condition. RS and ROCR are

used to set the over-current threshold. The OCS pins must be Kelvin connected for proper operation. See

Circuit Board Layout in Application Information for details.

When the voltage across ROCR becomes greater than VTOC (approximately 1.0V) the TA3020 will shut off the

output stages of its amplifiers. The occurrence of an over-current condition is latched in the TA3020 and can

be cleared by toggling the MUTE input or cycling power.

Setting Over-current Threshold

RS and ROCR determine the value of the over-current threshold, ISC:

ISC = 3580 x (VTOC IBIAS * ROCR)/(R OCR * RS)

ROCR = (3580 x VTOC)/(ISC * RS+3580 * IBIAS)

where:

RS and ROCR are in

VTOC = Over-current sense threshold voltage (See Electrical Characteristics Table)

= 1.0V typically

IBIAS = 20uA

For example, to set an ISC of 30A, ROCR = 9.63K and RS will be 10m.

As high-wattage resistors are usually only available in a few low-resistance values (10m, 25m and 50m),

ROCR can be used to adjust for a particular over-current threshold using one of these values for RS.

It should be noted that the addition of the bulk CHBR capacitor shown in the Application / Test Diagram will

increase the ISC level. Thus, it will be larger than the theoretical value shown above. Once the designer has

settled on a layout and specific CHBR value, the system ISC trip point can be adjusted by increasing the ROCR

value. The ROCR should be increased to a level that allows expected range of loads to be driven well into

clipping without current limiting while still protecting the output MOSFETs in case of a short circuit condition.

18 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

Over- and Under-Voltage Protection

The TA3020 senses the power rails through external resistor networks connected to VNNSENSE and

VPPSENSE. The over- and under-voltage limits are determined by the values of the resistors in the networks,

as described in the table Test/Application Circuit Component Values. If the supply voltage falls outside the

upper and lower limits determined by the resistor networks, the TA3020 shuts off the output stages of the

amplifiers. The removal of the over-voltage or under-voltage condition returns the TA3020 to normal operation.

Please note that trip points specified in the Electrical Characteristics table are at 25C and may change over

temperature.

The TA3020 has built-in over and under voltage protection for both the VPP and VNN supply rails. The

nominal operating voltage will typically be chosen as the supply center point. This allows the supply voltage

to fluctuate, both above and below, the nominal supply voltage.

VPPSENSE (pin 29) performs the over and undervoltage sensing for the positive supply, VPP. VNNSENSE

(pin 30) performs the same function for the negative rail, VNN. When the current through RVPPSENSE (or

RVNNSENSE) goes below or above the values shown in the Electrical Characteristics section (caused by changing

the power supply voltage), the TA3020 will be muted. VPPSENSE is internally biased at 2.5V and VNNSENSE

is biased at 1.25V.

Once the supply comes back into the supply voltage operating range (as defined by the supply sense

resistors), the TA3020 will automatically be unmuted and will begin to amplify. There is a hysteresis range on

both the VPPSENSE and VNNSENSE pins. If the amplifier is powered up in the hysteresis band the TA3020

will be muted. Thus, the usable supply range is the difference between the over-voltage turn-off and under-

voltage turn-off for both the VPP and VNN supplies. It should be noted that there is a timer of approximately

200mS with respect to the over and under voltage sensing circuit. Thus, the supply voltage must be outside of

the user defined supply range for greater than 200mS for the TA3020 to be muted.

Figure 4 shows the proper connection for the Over / Under voltage sense circuit for both the VPPSENSE and

VNNSENSE pins.

V5 VNN

TA3020

RVNN2 RVNN1

30

VNNSENSE

V5 VPP

RVNN2 RVPP1

29

VPPSENSE

Figure 4: Over / Under voltage sense circuit

The equation for calculating RVPP1 is as follows:

VPP

R VPP1 =

I VPPSENSE

Set R VPP2 = R VPP1 .

The equation for calculating RVNNSENSE is as follows:

19 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

VNN

R VNN1 =

I VNNSENSE

Set R VNN2 = 3 R VNN1 .

IVPPSENSE or IVNNSENSE can be any of the currents shown in the Electrical Characteristics table for

VPPSENSE and VNNSENSE, respectively.

The two resistors, RVPP2 and RVNN2 compensate for the internal bias points. Thus, RVPP1 and RVNN1 can be used

for the direct calculation of the actual VPP and VNN trip voltages without considering the effect of RVPP2 and

RVNN2.

Using the resistor values from above, the actual minimum over voltage turn off points will be:

VPP MIN_OV_TUR N_OFF = R VPP1 I VPPSENSE (MIN_OV_TU RN_OFF)

VNN MIN_OV_TUR N_OFF = ( R VNN1 I VNNSENSE (MIN_OV_TU RN_OFF) )

The other three trip points can be calculated using the same formula but inserting the appropriate IVPPSENSE (or

IVNNSENSE) current value. As stated earlier, the usable supply range is the difference between the minimum

overvoltage turn off and maximum under voltage turn-off for both the VPP and VNN supplies.

VPP RANGE = VPP MIN_OV_TUR N_OFF - VPP MAX_UV_TUR N_OFF

VNN RANGE = VNN MIN_OV_TUR N_OFF - VNN MAX_UV_TUR N_OFF

VN10 Supply

VN10 is an additional supply voltage required by the TA3020. VN10 must be 10 volts more positive than the

nominal VNN. VN10 must track VNN. Generating the VN10 supply requires some care.

The proper way to generate the voltage for VN10 is to use a 10V-postive supply voltage referenced to the VNN

supply. Figure 5 shows the correct way to power the TA3020:

VPP

VPP V5

5V

PGND AGND

VN10

VNN

10V

VNN

F. BEAD

Figure 5: Proper Power Supply Connection

One apparent method to generate the VN10 supply voltage is to use a negative IC regulator to drop PGND

down to 10V (relative to VNN). This method will not work since negative regulators only sink current into the

regulator output and will not be capable of sourcing the current required by VN10. Furthermore, problems can

arise since VN10 will not track movements in VNN.

Output Transistor Selection

The key parameters to consider when selecting what MOSFET to use with the TA3020 are drain-source

breakdown voltage (BVdss), gate charge (Qg), and on-resistance (RDS(ON)).

20 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

The BVdss rating of the MOSFET needs to be selected to accommodate the voltage swing between VSPOS and

VSNEG as well as any voltage peaks caused by voltage ringing due to switching transients. With a good circuit

board layout, a BVdss that is 50% higher than the VPP and VNN voltage swing is a reasonable starting point.

The BVdss rating should be verified by measuring the actual voltages experienced by the MOSFET in the final

circuit.

Ideally a low Qg (total gate charge) and low RDS(ON) are desired for the best amplifier performance.

Unfortunately, these are conflicting requirements since RDS(ON) is inversely proportional to Qg for a typical

MOSFET. The design trade-off is one of cost versus performance. A lower RDS(ON) means lower I2RDS(ON)

losses but the associated higher Qg translates into higher switching losses (losses = Qg x 10 x 1.2MHz). A

lower RDS(ON) also means a larger silicon die and higher cost. A higher RDS(ON) means lower cost and lower

switching losses but higher I2RDSON losses.

The following table lists BVdss, Qg and RDS(ON) for MOSFETs that Tripath has used with the

TA3020:

Manufacturer Manufacturers BVdss Qg RDS(ON) (Max)

Part Number (nanoCoulombs) (Ohms)

ST Microelectronics STW34NB20 200 60 0.075

ST Microelectronics STP19NB20 200 29 0.18

International Rectifier IRFB41N15D 150 67 0.045

International Rectifier IRFB31N20D 200 70 0.082

Fairchild FQA34N20 200 60 0.075

Gate Resistor Selection

The gate resistors, RG, are used to control MOSFET switching rise/fall times and thereby minimize voltage

overshoots. They also dissipate a portion of the power resulting from moving the gate charge each time the

MOSFET is switched. If RG is too small, excessive heat can be generated in the driver. Large gate resistors

lead to slower MOSFET switching, which requires a larger break-before-make (BBM) delay.

Break-Before-Make (BBM) Timing Control

The half-bridge power MOSFETs require a deadtime between when one transistor is turned off and the other is

turned on (break-before-make) in order to minimize shoot through currents. BBM0 and BBM1 are logic inputs

(connected to logic high or pulled down to logic low) that control the break-before-make timing of the output

transistors according to the following table.

BM1 BBM0 Delay

0 0 120 ns

0 1 80 ns

1 0 40 ns

1 1 0 ns

Table 1: BBM Delay

The tradeoff involved in making this setting is that as the delay is reduced, distortion levels improve but shoot-

through and power dissipation increase. Both the 40nS and 0nS settings are NOT recommended due the high

level of shoot-thru current that will result. Thus, BBM1 should be grounded in most applications. All typical

curves and performance information was done with using the 80ns or 120ns BBM setting. The actual amount

of BBM required is dependent upon other component values and circuit board layout, the value selected should

be verified in the actual application circuit/board. It should also be verified under maximum temperature and

power conditions since shoot-through in the output MOSFETs can increase under these conditions, possibly

requiring a higher BBM setting than at room temperature.

21 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

Output Filter Design

One advantage of Tripath amplifiers over PWM solutions is the ability to use higher-cutoff-frequency filters.

This means load-dependent peaking/droop in the 20kHz audio band potentially caused by the filter can be

made negligible. This is especially important for applications where the user may select a 4-Ohm or 8-Ohm

speaker. Furthermore, speakers are not purely resistive loads and the impedance they present changes over

frequency and from speaker model to speaker model.

Tripath recommends designing the filter as a 2nd order, 100kHz LC filter. Tripath has obtained good results

with LF = 11uH and CF = 0.22uF.

The core material of the output filter inductor has an effect on the distortion levels produced by a TA3020

amplifier. Tripath recommends low-mu type-2 iron powder cores because of their low loss and high linearity

(available from Micrometals, www.micrometals.com). The specific core used on the EB-TA3020 was a T106-2

wound with 29 turns of 16AWG wire.

Tripath also recommends that an RC damper be used after the LC low-pass filter. No-load operation of a

TA3020 amplifier can create significant peaking in the LC filter, which produces strong resonant currents that

can overheat the output MOSFETs and/or other components. The RC dampens the peaking and prevents

problems. Tripath has obtained good results with RD = 20 and CD = 0.22uF.

Bridging the TA3020

The TA3020 can be bridged by returning the signal from OAOUT1 to the input resistor at INV2. OUT1 will then

be a gained version of OAOUT1, and OUT2 will be a gained and inverted version of OAOUT1 (see Figure 6).

When the two amplifier outputs are bridged, the apparent load impedance seen by each output is halved, so

the current capability of the output MOSFETs, as well their power dissipation capability, must be accounted for

in the design. In addition, the higher peak currents caused by driving lower impedance loads will cause

additional ringing on the outputs. Thus, the layout and supply decoupling for low impedance (below 8 ohms)

bridged applications must be extremely good to minimize output ringing and to ensure proper amplifier

performance.

TA3020

OAOUT1

V5

RF

CI RI

INV1 -

INPUT

+

BIASCAP AGND

V5

20k

+

INV2

-

20k

AGND

OAOUT2

Figure 6: Input Stage Setup for Bridging

The switching outputs, OUT1 and OUT2, are not synchronized, so a common inductor may not be used with a

bridged TA3020. For this same reason, individual zobel networks must be applied to each output to load each

output and lower the Q of each common mode differential LC filter.

22 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

Low-frequency Power Supply Pumping

A potentially troublesome phenomenon in single-ended switching amplifiers is power supply pumping. This

phenomenon is caused by current from the output filter inductor flowing into the power supply output filter

capacitors in the opposite direction as a DC load would drain current from them. Under certain conditions

(usually low-frequency input signals), this current can cause the supply voltage to pump (increase in

magnitude) and eventually cause over-voltage/under-voltage shut down. Moreover, since over/under-voltage

are not latched shutdowns, the effect would be an amplifier that oscillates between on and off states. If a DC

offset on the order of 0.3V is allowed to develop on the output of the amplifier (see DC Offset Adjust), the

supplies can be boosted to the point where the amplifiers over-voltage protection triggers.

One solution to the pumping issue it to use large power supply capacitors to absorb the pumped supply current

without significant voltage boost. The low-frequency pole used at the input to the amplifier determines the value

of the capacitor required. This works for AC signals only.

A no-cost solution to the pumping problem uses the fact that music has low frequency information that is

correlated in both channels (it is in phase). This information can be used to eliminate boost by putting the two

channels of a TA3020 amplifier out of phase with each other. This works because each channel is pumping out

of phase with the other, and the net effect is a cancellation of pumping currents in the power supply. The phase

of the audio signals needs to be corrected by connecting one of the speakers in the opposite polarity as the

other channel.

Theoretical Efficiency Of A TA3020 Amplifier

The efficiency, , of an amplifier is:

= POUT/PIN

The power dissipation of a TA3020 amplifier is primarily determined by the on resistance, RON, of the output

transistors used, and the switching losses of these transistors, PSW. For a TA3020 amplifier, PIN (per channel)

is approximated by:

PIN = PDRIVER + PSW + POUT ((RS + RON + RCOIL + RL)/RL)2

where: PDRIVER = Power dissipated in the TA3020 = 1.6W/channel

PSW = 2 x (0.01) x Qg (Qg is the gate charge of M, in nano-coulombs)

RCOIL = Resistance of the output filter inductor (typically around 50m)

For a 125W RMS per channel, 8 load amplifier using STW34NB20 MOSFETs, and an RS of 50m,

PIN = PDRIVER + PSW + POUT ((RS + RON + RCOIL + RL)/RL)2

= 1.6 + 2 x (0.01) x (95) + 125 x ((0.025 + 0.11 + 0.05 + 8)/8)2 = 1.6 + 1.9 + 130.8

= 134.3W

In the above calculation the RDS (ON) of 0.065 was multiplied by a factor of 1.7 to obtain RON in order to account

for some temperature rise of the MOSFETs. (RDS (ON) typically increases by a factor of 1.7 for a typical MOSFET

as temperature increases from 25C to 170C.)

So, = POUT/PIN = 125/134.3 = 93%

Performance Measurements of a TA3020 Amplifier

Tripath amplifiers operate by modulating the input signal with a high-frequency switching pattern. This signal is

sent through a low-pass filter (external to the TA3020) that demodulates it to recover an amplified version of the

audio input. The frequency of the switching pattern is spread spectrum and typically varies between 200kHz

and 1.5MHz, which is well above the 20Hz 22kHz audio band. The pattern itself does not alter or distort the

audio input signal but it does introduce some inaudible noise components.

23 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

The measurements of certain performance parameters, particularly those that have anything to do with noise,

like THD+N, are significantly affected by the design of the low-pass filter used on the output of the TA3020 and

also the bandwidth setting of the measurement instrument used. Unless the filter has a very sharp roll-off just

past the audio band or the bandwidth of the measurement instrument ends there, some of the inaudible noise

components introduced by the Tripath amplifier switching pattern will get integrated into the measurement,

degrading it.

Tripath amplifiers do not require large multi-pole filters to achieve excellent performance in listening tests, usually a more

critical factor than performance measurements. Though using a multi-pole filter may remove high-frequency noise and

improve THD+N type measurements (when they are made with wide-bandwidth measuring equipment), these same filters

can increase distortion due to inductor non-linearity. Multi-pole filters require relatively large inductors, and inductor non-

linearity increases with inductor value.

Package Information

48-pin DIP

24 TA3020 MC/ Rev. 2.0/11.01

Tr i path Technol ogy, I nc. - Techni cal I nfor m ati on

PRELIMINARY This product is still in development. Tripath Technology Inc. reserves the right to make any

changes without further notice to improve reliability, function or design.

This data sheet contains the design specifications for a product in development. Specifications may change in any

manner without notice. Tripath and Digital Power Processing are trademarks of Tripath Technology Inc. Other

trademarks referenced in this document are owned by their respective companies.

Tripath Technology Inc. reserves the right to make changes without further notice to any products herein to improve

reliability, function or design. Tripath does not assume any liability arising out of the application or use of any

product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of

others.

TRIPATHS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN CONSENT OF THE PRESIDENT OF TRIPATH

TECHNOLOGY INC.

As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with

instructions for use provided in this labeling, can be reasonably expected to result in significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be

reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Contact Information

TRIPATH TECHNOLOGY, INC

2560 Orchard Parkway, San Jose, CA 95131

408.750.3000 - P

408.750.3001 - F

For more Sales Information, please visit us @ www.tripath.com/cont_s.htm

For more Technical Information, please visit us @ www.tripath.com/data.htm

25 TA3020 MC/ Rev. 2.0/11.01

Vous aimerez peut-être aussi

- TDA2500 Technical Data SheetDocument29 pagesTDA2500 Technical Data SheetNanang BaliPas encore d'évaluation

- TA2020-020 Stereo 20W (4 Using Digital Power Processing (DPP™) TechnologyDocument13 pagesTA2020-020 Stereo 20W (4 Using Digital Power Processing (DPP™) TechnologyReinaldo OrtizPas encore d'évaluation

- TA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyDocument18 pagesTA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyvetchboyPas encore d'évaluation

- TC2001Document15 pagesTC2001api-3736768Pas encore d'évaluation

- TC2000 Stereo Class-T™ Audio Controller Using Digital Power Processing (DPP™) TechnologyDocument9 pagesTC2000 Stereo Class-T™ Audio Controller Using Digital Power Processing (DPP™) TechnologyNanang BaliPas encore d'évaluation

- Ta2021 100Document24 pagesTa2021 100purejavascriptPas encore d'évaluation

- 3159-QFP64E: SANYO Electric Co.,Ltd. Semiconductor Bussiness HeadquartersDocument21 pages3159-QFP64E: SANYO Electric Co.,Ltd. Semiconductor Bussiness HeadquartersVeronicaGonzalezPas encore d'évaluation

- Model: UHFTV-200D-19 TV Pallet Amplifier ModuleDocument2 pagesModel: UHFTV-200D-19 TV Pallet Amplifier ModulejosePas encore d'évaluation

- 1.25Gb 20klm 1490T-1310R SM (Standard Code)Document6 pages1.25Gb 20klm 1490T-1310R SM (Standard Code)Sean SerinPas encore d'évaluation

- MF-2500DS-T12-18x/19x/20x/21x MF-2500DS-R13-18x MF-2500DS-R14-19x/20x/21xDocument9 pagesMF-2500DS-T12-18x/19x/20x/21x MF-2500DS-R13-18x MF-2500DS-R14-19x/20x/21xGabriel RacovskyPas encore d'évaluation

- 1.UPS2000-G Series (6-20kVA) Datasheet 06 - (20180207)Document2 pages1.UPS2000-G Series (6-20kVA) Datasheet 06 - (20180207)cirta4ever IBN BadisPas encore d'évaluation

- UP4 Din BrochureDocument2 pagesUP4 Din BrochuresenthilrsenthilPas encore d'évaluation

- TDA25410 If Amplifier With Demodulator and AfcDocument8 pagesTDA25410 If Amplifier With Demodulator and Afcspam0000Pas encore d'évaluation

- STK4221 AF Power Amplifier (Split Power Supply) (80W + 80W Min, THD 0.4%)Document6 pagesSTK4221 AF Power Amplifier (Split Power Supply) (80W + 80W Min, THD 0.4%)Vitorio LogoPas encore d'évaluation

- Model: UHFTV-400D-20 TV Pallet Amplifier ModuleDocument2 pagesModel: UHFTV-400D-20 TV Pallet Amplifier ModuleHernán Robert Ruelas GaldosPas encore d'évaluation

- MSB Digital Multi Function Meter Hobut M850Document2 pagesMSB Digital Multi Function Meter Hobut M850stranfirPas encore d'évaluation

- Z109REG2: High Performance Universal ConverterDocument2 pagesZ109REG2: High Performance Universal ConvertersanthoshkumarPas encore d'évaluation

- Huong Dan REC DPR2700Document16 pagesHuong Dan REC DPR2700Chim ConPas encore d'évaluation

- BCI88108LDocument3 pagesBCI88108LMartin SilisquePas encore d'évaluation

- TCS7191B: General Description FeaturesDocument14 pagesTCS7191B: General Description FeaturesJesus SanchezPas encore d'évaluation

- Philips Xh3 HP l1502 l1523 Compaq Fp5315Document13 pagesPhilips Xh3 HP l1502 l1523 Compaq Fp5315Malfo10Pas encore d'évaluation

- Ta 0104 ADocument18 pagesTa 0104 AJump DownPas encore d'évaluation

- PAFM1000W144 Rev4.2Document5 pagesPAFM1000W144 Rev4.2Juan Enrique Castillo CanoPas encore d'évaluation

- Lighting Lighting: EB-Certalume For PLT/C LampsDocument2 pagesLighting Lighting: EB-Certalume For PLT/C LampssnowwooPas encore d'évaluation

- AFT05MP075NDocument21 pagesAFT05MP075NTeyfik koyuncuPas encore d'évaluation

- Iraudamp 17Document13 pagesIraudamp 17Carlos AlvarezPas encore d'évaluation

- LV1116N/NV: Electronic Volume ControlDocument18 pagesLV1116N/NV: Electronic Volume Controlgun gun saepulPas encore d'évaluation

- Ic Audio La4285 Ic Audio La4285Document3 pagesIc Audio La4285 Ic Audio La4285Freddy PerezPas encore d'évaluation

- 3W Monaural Power Amplifier: Audio Output For TV ApplicationDocument3 pages3W Monaural Power Amplifier: Audio Output For TV ApplicationRobertoPas encore d'évaluation

- TP03AL220S03LSW 2W 85-265VAC Input 3.3VDC OutputDocument3 pagesTP03AL220S03LSW 2W 85-265VAC Input 3.3VDC OutputtoppowerPas encore d'évaluation

- PAFM80W Rev4.2Document4 pagesPAFM80W Rev4.2Juan Enrique Castillo CanoPas encore d'évaluation

- BD9486FDocument37 pagesBD9486F94430s19684Pas encore d'évaluation

- DPC-0000210 V8Document12 pagesDPC-0000210 V8achapPas encore d'évaluation

- 4015 Extended Specifications V1 2Document31 pages4015 Extended Specifications V1 2SHAHID KHAN CHANNARPas encore d'évaluation

- PAFM150W Rev4.0Document3 pagesPAFM150W Rev4.0Juan Enrique Castillo CanoPas encore d'évaluation

- PAFM800W Rev4.2Document5 pagesPAFM800W Rev4.2Juan Enrique Castillo CanoPas encore d'évaluation

- TND1 Single-Phase Automatic AC Voltage Regulator TNS1 Three-Phase Automatic AC Voltage RegulatorDocument3 pagesTND1 Single-Phase Automatic AC Voltage Regulator TNS1 Three-Phase Automatic AC Voltage RegulatorJohan García CentenoPas encore d'évaluation

- 300Mw at 3.3V Supply Audio Power Amplifier With Standby Mode Active HighDocument19 pages300Mw at 3.3V Supply Audio Power Amplifier With Standby Mode Active HighPanagiotis PanagosPas encore d'évaluation

- AH101Document7 pagesAH101Edi PurwantoPas encore d'évaluation

- TA2020Document13 pagesTA2020Irimia Mihai AdrianPas encore d'évaluation

- Schneider Electric - Altivar-212 - ATV212HD22N4Document15 pagesSchneider Electric - Altivar-212 - ATV212HD22N4sofianignitePas encore d'évaluation

- Inverter Type No. 104PWBR1Document10 pagesInverter Type No. 104PWBR1Daniel Chacon MatúPas encore d'évaluation

- Dual Operational Amplifier: Features DescriptionDocument6 pagesDual Operational Amplifier: Features DescriptionAmin MahfudiPas encore d'évaluation

- Datasheet Tda 7376bDocument9 pagesDatasheet Tda 7376bstefanithaPas encore d'évaluation

- ETC ATW2815D-MSTRDocument9 pagesETC ATW2815D-MSTRBaCresPas encore d'évaluation

- Cxa3834m SonyDocument29 pagesCxa3834m Sonygerson evandro hanauerPas encore d'évaluation

- FM62429 Serial Data Control Dual Electronic Volume: SpecificationDocument10 pagesFM62429 Serial Data Control Dual Electronic Volume: Specificationfabio_sgPas encore d'évaluation

- SM0665 Service Manual: BZ-1 CP-AW2519NDocument128 pagesSM0665 Service Manual: BZ-1 CP-AW2519NVinicio SangalliPas encore d'évaluation

- CC Ain Om Ain AinDocument5 pagesCC Ain Om Ain AinAlfonso BasilePas encore d'évaluation

- 300W Broadcast FM Amplifier ModuleDocument4 pages300W Broadcast FM Amplifier ModuleJuan Enrique Castillo CanoPas encore d'évaluation

- MRF1K50HDocument22 pagesMRF1K50HISMAEL ALVEZPas encore d'évaluation

- Modular Inverter Datasheet Media TSI 48Vdc - 230vac - 1.5kVA EN v1.3Document2 pagesModular Inverter Datasheet Media TSI 48Vdc - 230vac - 1.5kVA EN v1.3Charmer JiaPas encore d'évaluation

- Constant Current Led DriverDocument27 pagesConstant Current Led DriverJubin JainPas encore d'évaluation

- Empower RF Amplifier 1117Document3 pagesEmpower RF Amplifier 1117DaniPas encore d'évaluation

- EL816Document15 pagesEL816Walcir FerreiraPas encore d'évaluation

- CXA3834MDocument29 pagesCXA3834MGerardo ReyesPas encore d'évaluation

- American ESS Split-Phase Inverter: Product FeaturesDocument2 pagesAmerican ESS Split-Phase Inverter: Product FeaturesEngjoo Kho Jr.Pas encore d'évaluation

- PAFM1000WEX Rev4.1Document4 pagesPAFM1000WEX Rev4.1Juan Enrique Castillo CanoPas encore d'évaluation

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2D'EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Pas encore d'évaluation

- Lenze 8200XE Instruction ManualDocument90 pagesLenze 8200XE Instruction ManualDawid MleczkoPas encore d'évaluation

- MonkeyBoard DAB DAB FM Digital Radio Development Board Pro Mit SlideShowDocument3 pagesMonkeyBoard DAB DAB FM Digital Radio Development Board Pro Mit SlideShowDawid MleczkoPas encore d'évaluation

- Eb TK2050Document14 pagesEb TK2050Dawid MleczkoPas encore d'évaluation

- TA2024 Mods Draft STAGE1Document7 pagesTA2024 Mods Draft STAGE1Dawid MleczkoPas encore d'évaluation

- TA2024 Mods Draft STAGE2Document5 pagesTA2024 Mods Draft STAGE2Dawid MleczkoPas encore d'évaluation

- Ta2022 PDFDocument31 pagesTa2022 PDFDawid MleczkoPas encore d'évaluation

- ZAPI AC-2 ManualDocument72 pagesZAPI AC-2 ManualDawid MleczkoPas encore d'évaluation

- AmplifierDocument1 pageAmplifierDawid MleczkoPas encore d'évaluation

- 41150Document14 pages41150zayerirezaPas encore d'évaluation

- 2nd Year Short Question Answers From Within ChaptersDocument40 pages2nd Year Short Question Answers From Within ChaptersZain ZuhabPas encore d'évaluation

- Master Data - Rab 2021 Teknika Kapal Penangkap Ikan: NO Nama Alat Merk TypeDocument78 pagesMaster Data - Rab 2021 Teknika Kapal Penangkap Ikan: NO Nama Alat Merk TypebisriPas encore d'évaluation

- AEE Applied Electricity and Electronics Lab Manual (Revised 2018)Document146 pagesAEE Applied Electricity and Electronics Lab Manual (Revised 2018)hassan100% (1)

- Doble F6150 Protection Test Instrument: Knowledge Is PowerDocument69 pagesDoble F6150 Protection Test Instrument: Knowledge Is PowerChhimi WangchukPas encore d'évaluation

- United States Patent (19) : 11) Patent Number: 4,864,547 (45) Date of Patent: Sep. 5, 1989Document18 pagesUnited States Patent (19) : 11) Patent Number: 4,864,547 (45) Date of Patent: Sep. 5, 1989mohasPas encore d'évaluation

- Bidirectional Visitor CounterDocument35 pagesBidirectional Visitor CounterParthi_8971% (7)

- LS12机芯服务手册概要Document73 pagesLS12机芯服务手册概要Jorge Tom Simpson CruzPas encore d'évaluation

- Smartpack Monitoring and Control Unit PDFDocument20 pagesSmartpack Monitoring and Control Unit PDFSohaib Omer SalihPas encore d'évaluation

- Converter Based On Energy Injection Control For AC-AC, AC-DC, DC-DC, DC-ACDocument5 pagesConverter Based On Energy Injection Control For AC-AC, AC-DC, DC-DC, DC-ACbima bagusPas encore d'évaluation

- Eecim02 Course MaterialDocument42 pagesEecim02 Course Materialsmahesh_1980Pas encore d'évaluation

- Pulse Motor Free Energy Generator For Electric Car Charging SystemDocument5 pagesPulse Motor Free Energy Generator For Electric Car Charging Systemرشيد بن صغيرPas encore d'évaluation

- 54.5V/30A Power Cabinet: VPRS-430Document3 pages54.5V/30A Power Cabinet: VPRS-430Tuan MinhPas encore d'évaluation

- GGT-30 Geophysical Transmitter Maintenance and Repair ManualDocument46 pagesGGT-30 Geophysical Transmitter Maintenance and Repair ManualHenry AlvaxPas encore d'évaluation

- Resonant ConversionDocument27 pagesResonant ConversionAruna ChandranPas encore d'évaluation

- Access Power Solutions Installation Guide: (SM45 Controlled)Document102 pagesAccess Power Solutions Installation Guide: (SM45 Controlled)Elvis Eliud HernándezPas encore d'évaluation