Académique Documents

Professionnel Documents

Culture Documents

Lecturenotes Chapter6

Transféré par

vasu_ks438Description originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Lecturenotes Chapter6

Transféré par

vasu_ks438Droits d'auteur :

Formats disponibles

1

COEN 312 DIGITAL SYSTEMS DESIGN - LECTURE NOTES

Concordia University

Chapter 6: Registers and Counters

NOTE: For more examples and detailed description of the material in the lecture

notes, please refer to the main textbook:

Digital Design 3rd Edition, By Morris Mano, Publisher Prentice Hall, 3rd Edition

All examples used in the lecture notes are from the above reference.

Up-Down Binary Counters

- The state table of the four-bit up counter with T flip-flops is given below.

Present State Next State Flip-Flop Inputs

No. Q3 Q2 Q1 Q0 Q3 Q2 Q1 Q0 T3 T2 T1 T0

0 0 0 0 0 0 0 0 1 0 0 0 1

1 0 0 0 1 0 0 1 0 0 0 1 1

2 0 0 1 0 0 0 1 1 0 0 0 1

3 0 0 1 1 0 1 0 0 0 1 1 1

4 0 1 0 0 0 1 0 1 0 0 0 1

5 0 1 0 1 0 1 1 0 0 0 1 1

6 0 1 1 0 0 1 1 1 0 0 0 1

7 0 1 1 1 1 0 0 0 1 1 1 1

8 1 0 0 0 1 0 0 1 0 0 0 1

9 1 0 0 1 1 0 1 0 0 0 1 1

10 1 0 1 0 1 0 1 1 0 0 0 1

11 1 0 1 1 1 1 0 0 0 1 1 1

12 1 1 0 0 1 1 0 1 0 0 0 1

13 1 1 0 1 1 1 1 0 0 0 1 1

14 1 1 1 0 1 1 1 1 0 0 0 1

15 1 1 1 1 0 0 0 0 1 1 1 1

- This table shows that a bit changes when all of its less significant bits are equal to

one (this is what one intuitively expects in an up counter).

- Similarly, one can find the state table of a down counter, where a bit changes

when all of its less significant bits are equal to zero.

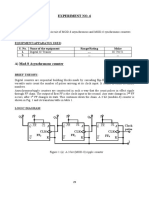

- One can design an up-down counter with an up and down control inputs, as

shown in the following figure.

Lecture Notes Prepared by Amir G. Aghdam

Up 2

A0

Down T

C

A1

T

C

A2

T

C

A3

T

C

CLK

- It can be easily verified that when the external input “Up” is equal to 1, then no

matter what the other external input, i.e. “Down” is, the circuit will operate as an

up-counter.

- When the external input “Down” is equal to 1 and the external input “Up” is equal

to zero, then the circuit operates as a down-counter.

- If both external inputs “Up” and “Down” are equal to zero, then the output of the

flip-flops remain unchanged.

- A binary counter with parallel load is shown in the following figure.

Lecture Notes Prepared by Amir G. Aghdam

Count

3

Load

A0

J

I0

C

K

I1 A1

J

C

K

I2 A2

J

C

K

I3 A3

J

C

K

Clear

CLK

Carry-output

Lecture Notes Prepared by Amir G. Aghdam

4

- When the external input “Load” is equal to 1, then no matter what “Count” is, the

input lines I0, I1, I2 and I3 will appear in the output of the flip-flops A0, A1, A2 and

A3, respectively.

- When, on the other hand, “Count” is equal to 1 and “Load” is equal to zero, then

the circuit will operate as an up-counter.

- When both external inputs “Load” and “Count” are equal to zero, then the flip-

flop outputs remain unchanged.

BCD Counter

- A BCD up counter is a digital system that counts from 0 to 9 as a decimal digit,

and returns back to 0 to repeat the counting.

- A BCD counter can be built in a way similar to the binary counter.

- The state table can be obtained as shown below.

Present State Next State Output Flip-Flop Inputs

No. Q8 Q4 Q2 Q1 Q8 Q4 Q2 Q1 y T8 T4 T2 T1

0 0 0 0 0 0 0 0 1 0 0 0 0 1

1 0 0 0 1 0 0 1 0 0 0 0 1 1

2 0 0 1 0 0 0 1 1 0 0 0 0 1

3 0 0 1 1 0 1 0 0 0 0 1 1 1

4 0 1 0 0 0 1 0 1 0 0 0 0 1

5 0 1 0 1 0 1 1 0 0 0 0 1 1

6 0 1 1 0 0 1 1 1 0 0 0 0 1

7 0 1 1 1 1 0 0 0 0 1 1 1 1

8 1 0 0 0 1 0 0 1 0 0 0 0 1

9 1 0 0 1 0 0 0 0 1 1 0 0 1

- The output is, in fact, a carry out, which indicates that the numbers 0 to 9 have

been counted once and a new set of BCD codes are being counted.

Counters with unused States

- A sequential circuit with m states, where 2 n −1 < m < 2 n , will require n flip-flops,

and as a result, the circuit will have 2 n − m unused states.

- For example, a counter with a prespecified sequence 000-001-010-100-101-110-

000 has two unused states 011 and 111, as shown in the following state table.

Lecture Notes Prepared by Amir G. Aghdam

5

Present State Next State Flip-Flop Inputs

A B C A B C JA KA JB KB JC KC

0 0 0 0 0 1 0 x 0 x 1 x

0 0 1 0 1 0 0 x 1 x x 1

0 1 0 1 0 0 1 x x 1 0 x

1 0 0 1 0 1 x 0 0 x 1 x

1 0 1 1 1 0 x 0 1 x x 1

1 1 0 0 0 0 x 1 x 1 0 x

- To find the simplified flip-flop input expressions using K-map, the terms

corresponding to the unused states 011 and 111 are considered don’t-care

conditions.

- For instance, the K-map corresponding to JA is as follows.

B’ B

BC 00 01 11 10

A

A’ 0 0 0 x 1

A 1 x x x x

C’ C C’

- The simplified Boolean expressions for the flip-flop inputs are as follows:

JA = B KA = B

JB = C KB = 1

J C = B' KC = 1

- This leads to the following logic diagram for this system:

Lecture Notes Prepared by Amir G. Aghdam

6

J A

C

K

J B

C

K

J C

C

1 K

CLK

- From the logic circuit, one can find out what happens if the circuit starts from an

unused state.

- This can be easily figured out from the state diagram which is obtained below.

111

000

001 110

010 101

100

011

Ring Counter

Lecture Notes Prepared by Amir G. Aghdam

7

- A ring counter is a register with circular shift, where only one flip-flop output is

equal to one, and all other ones are zero.

- A ring counter can be used to generate the timing signal for a circuit, where, for

example, only one component of the system should get a set input and all other

ones should get a zero input.

- An example of a 4-bit ring counter is given below.

Shift right T0 T1 T2 T3

- A typical timing diagram of the above counter is as follows:

CLK

T0

T1

T2

T3

- A ring counter with 2 n bits (or 2 n timing signals) can be implemented using a n-

bit binary counter and a n-to- 2 n -line decoder.

- For example, the above ring counter can be implemented as follows:

T0 T1 T2 T3

2x4

Decoder

Count Enable 2-bit Counter

Lecture Notes Prepared by Amir G. Aghdam

8

- The following circuit is a 4-bit ring counter with a Start line.

Q0 Q1 Q2 Q3

Start

D D D D

C C C C

CLK

- When the Start line is equal to one, the left-most flip-flop is set and all other flip-

flops are reset, as required for a ring counter.

Asynchronous Counter or Ripple Counter

- Example: A three-bit ripple up-counter with T flip-flops is given below.

1 T T T

CLK C C C

A0 A1 A2

Least significant bit Most significant bit

- A0 toggles once after each clock edge.

- The counting sequence is 0-1-2-3-4-5-6-7-0-…, as shown below:

A2 A1 A0

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Lecture Notes Prepared by Amir G. Aghdam

9

- The timing diagram of the ripple counter given above, is as follows:

CLK

A0

A1

A2

T4

- As it can be seen from the above diagram, in reality because of the propagation

delay, the counting will have some transition problem for a short period of time

after the clock edge. For instance, right after T4, we will have 011-010-000-100

(instead of 000-100).

- One can also use a D flip-flop to build a ripple counter, by connecting the input of

each flip-flop to the Q’ of the same flip-flop.

- A three bit ripple down-counter with T flip-flops is given below.

1 T T T

CLK C C C

A0 A1 A2

Least significant bit Most significant bit

BCD Ripple Counter

0000 0001 0010 0011 0100

1001 1000 0111 0110 0101

Lecture Notes Prepared by Amir G. Aghdam

10

- It can be easily verified that:

- Q1 changes after each clock cycle.

- Q2 complements each time Q1 changes from 1 to 0 while Q8 is 0.

- Q2 remains at 0 while Q8 is 1.

- Q4 complements each time Q2 changes from 1 to 0.

- Q8 remains at 0 while Q2 or Q4 is 0.

- When Q2 and Q4 both become equal to 1, then Q8 complements as soon as Q1

changes from 1 to 0.

- Q8 changes to 0 next time that Q1 changes from 1 to 0.

Reference:

[1] Digital Design 3rd Edition, By Morris Mano, Publisher Prentice Hall, 3rd Edition.

Lecture Notes Prepared by Amir G. Aghdam

Vous aimerez peut-être aussi

- ECE 120 Worksheet 5: From Problem Statement To Digital CircuitDocument4 pagesECE 120 Worksheet 5: From Problem Statement To Digital CircuitAnatasyaOktavianiHandriatiTata100% (1)

- Design of MOD6 Synchronous CounterDocument7 pagesDesign of MOD6 Synchronous CounterFaizur Rahman100% (1)

- Digital Lab Report 3Document8 pagesDigital Lab Report 3علي عليPas encore d'évaluation

- Baby Incubator Alarm Circuit Copper TaskDocument4 pagesBaby Incubator Alarm Circuit Copper TaskDanelle Geamala50% (2)

- Cost Estimating Manual for Pipelines and Marine Structures: New Printing 1999D'EverandCost Estimating Manual for Pipelines and Marine Structures: New Printing 1999Évaluation : 5 sur 5 étoiles5/5 (2)

- Shackle Marking InformationDocument7 pagesShackle Marking Informationmalborn100% (1)

- How To Read An ODBC Trace FileDocument13 pagesHow To Read An ODBC Trace FileganeshharidasPas encore d'évaluation

- 4 Bit CounterDocument4 pages4 Bit CounterArun Kumar K MPas encore d'évaluation

- Vdocuments - MX - Cascading Asynchronous Counters Svbit Svbitecwordpresscom 3 Cascading AsynchronousDocument17 pagesVdocuments - MX - Cascading Asynchronous Counters Svbit Svbitecwordpresscom 3 Cascading AsynchronousRajashekarBalyaPas encore d'évaluation

- Lecture 2Document24 pagesLecture 2sanjoni.jainPas encore d'évaluation

- Counters: Dr. M.Aarthy Assistant Professor Senior School of Electronics Engineering Vellore Institute of TechnologyDocument21 pagesCounters: Dr. M.Aarthy Assistant Professor Senior School of Electronics Engineering Vellore Institute of TechnologyRahul ChahalPas encore d'évaluation

- ECE213: Digital Electronics: UNIT-5 Sequential Logic Circuit ApplicationsDocument12 pagesECE213: Digital Electronics: UNIT-5 Sequential Logic Circuit ApplicationsAharsh SinghPas encore d'évaluation

- Ipple Counters R: Class Notes CLASS 14-2&3Document4 pagesIpple Counters R: Class Notes CLASS 14-2&3salPas encore d'évaluation

- QUAN-Computer System Architecture-DescriptiveDocument66 pagesQUAN-Computer System Architecture-DescriptiveDebanjan PatraPas encore d'évaluation

- Digital Circuits - CountersDocument6 pagesDigital Circuits - CountersB.Prashant JhaPas encore d'évaluation

- Attachment 1Document2 pagesAttachment 1successfanacademyPas encore d'évaluation

- ENS2456 Solutions 4Document9 pagesENS2456 Solutions 4omairakhtar12345Pas encore d'évaluation

- Design of Counters: Welcome To The Course-Digital System Design Code-BECE102LDocument14 pagesDesign of Counters: Welcome To The Course-Digital System Design Code-BECE102LwhytujayPas encore d'évaluation

- MODULE 4 - Flip Flop & RegistersDocument27 pagesMODULE 4 - Flip Flop & RegistersChaitanya J S ReddyPas encore d'évaluation

- CH 6 PDFDocument40 pagesCH 6 PDFnananguibPas encore d'évaluation

- CarabuelaDocument1 pageCarabuelaRubén MackayPas encore d'évaluation

- Pertemuan 12 Counter Asinkron 2015Document27 pagesPertemuan 12 Counter Asinkron 2015Khalif GaffarezkaPas encore d'évaluation

- Lecture 9: Encoders and Decoders Dr. Shama NoreenDocument59 pagesLecture 9: Encoders and Decoders Dr. Shama NoreenHaseeb ArifPas encore d'évaluation

- Lecture9 RegistersDocument16 pagesLecture9 RegistersDao Anh HaoPas encore d'évaluation

- Taller Chapter 3 Sistemas DigitalesDocument4 pagesTaller Chapter 3 Sistemas DigitalesCristian PuentesPas encore d'évaluation

- Digital Electronics - Tutorial #1Document3 pagesDigital Electronics - Tutorial #1Dishawn NationPas encore d'évaluation

- 17 Timing PDFDocument4 pages17 Timing PDFControl System Engineering LabPas encore d'évaluation

- Working With Combinational LogicDocument62 pagesWorking With Combinational Logic박대민Pas encore d'évaluation

- CSCI350-S22-Assignment 4Document1 pageCSCI350-S22-Assignment 4Atharva TemkarPas encore d'évaluation

- 1.3.1 Logic GatesDocument14 pages1.3.1 Logic Gatessaad nasirPas encore d'évaluation

- Digital Circuits - Application of Shift RegistersDocument4 pagesDigital Circuits - Application of Shift RegistersB.Prashant JhaPas encore d'évaluation

- Experiment 11 Asynchronous CountersDocument10 pagesExperiment 11 Asynchronous CountersMd. Arif Hasan MasumPas encore d'évaluation

- Final Report: Simulation of Digital CircuitsDocument20 pagesFinal Report: Simulation of Digital CircuitsPhạm NamPas encore d'évaluation

- PROBLEM SET 10 SolutionsDocument34 pagesPROBLEM SET 10 Solutionsnandini katariaPas encore d'évaluation

- Lab 02 - Gates - CircuitsDocument20 pagesLab 02 - Gates - CircuitsJohnPas encore d'évaluation

- IIT Convolution CodesDocument11 pagesIIT Convolution CodesHarshaPas encore d'évaluation

- Counter SlidesDocument10 pagesCounter Slidessanjeevani rawatPas encore d'évaluation

- Finite State Machines: by Mike ChenDocument25 pagesFinite State Machines: by Mike ChenKulwant NagiPas encore d'évaluation

- Counter IDocument23 pagesCounter IAMIT KUMAR SINGHPas encore d'évaluation

- CounterDocument33 pagesCounterAMIT KUMAR SINGHPas encore d'évaluation

- Logic Gate Design: 3 Inputs and 2 Output SystemsDocument9 pagesLogic Gate Design: 3 Inputs and 2 Output SystemsAditya ParmarPas encore d'évaluation

- Overall Order of Irreversible Reactions From The Half-Life TDocument15 pagesOverall Order of Irreversible Reactions From The Half-Life Talice AnnabellePas encore d'évaluation

- Counters RegistersDocument28 pagesCounters RegistersBaePas encore d'évaluation

- Preludio CarulliDocument1 pagePreludio CarulliMikaPas encore d'évaluation

- Assignment 2Document8 pagesAssignment 2DrunkmilitiaPas encore d'évaluation

- CounterDocument9 pagesCounterrmangaiPas encore d'évaluation

- LCD Mod3Ass TUMALIUANDocument6 pagesLCD Mod3Ass TUMALIUANmaxpein100% (1)

- Sum of Products: CS232 Lecture Notes Circuits Fall 2020Document5 pagesSum of Products: CS232 Lecture Notes Circuits Fall 2020Abel YifatPas encore d'évaluation

- Aziz PDFDocument4 pagesAziz PDFdanyalhamzahPas encore d'évaluation

- Experiment 7Document3 pagesExperiment 7AAAAALLENNPas encore d'évaluation

- Tarea 2 Hardware 2Document6 pagesTarea 2 Hardware 2a01663882Pas encore d'évaluation

- Switching Circuits & Logic DesignDocument13 pagesSwitching Circuits & Logic DesignDr Ravi Kumar A.VPas encore d'évaluation

- DC-AC Inverter 10KWDocument125 pagesDC-AC Inverter 10KWnishan80% (5)

- Digital Logic DesignDocument28 pagesDigital Logic DesignAri BaderPas encore d'évaluation

- Name: Izaan Ahmed Khan STD ID: FA19-BSCS-0049 COURSE: DLD Theory Assignment # 03Document10 pagesName: Izaan Ahmed Khan STD ID: FA19-BSCS-0049 COURSE: DLD Theory Assignment # 03Izaan Ahmed KhanPas encore d'évaluation

- IT-2 Space Switching UnitDocument2 pagesIT-2 Space Switching UnitИринаPas encore d'évaluation

- SP Am1 en AUMADocument1 pageSP Am1 en AUMATamas KubolaPas encore d'évaluation

- STONA 2014 Exhibitiors ListDocument56 pagesSTONA 2014 Exhibitiors Listvasu_ks438Pas encore d'évaluation

- A Collection of Nursery RhymesDocument9 pagesA Collection of Nursery Rhymesfiore-2627Pas encore d'évaluation

- Chanakya The GreatDocument21 pagesChanakya The Greatvasu_ks438Pas encore d'évaluation

- List of Sanctioned Cases Under IIPP (96th GENERAL SLC) Held On 01/03/2013 Pavala VaddiDocument14 pagesList of Sanctioned Cases Under IIPP (96th GENERAL SLC) Held On 01/03/2013 Pavala Vaddivasu_ks438Pas encore d'évaluation

- Case Study Solution - Network of QueuesDocument26 pagesCase Study Solution - Network of Queuesvasu_ks438Pas encore d'évaluation

- SQL1Document13 pagesSQL1Devalla Bhaskar GaneshPas encore d'évaluation

- S ParametersDocument29 pagesS ParameterseloisePas encore d'évaluation

- Processing Sequence When Posting An EventDocument5 pagesProcessing Sequence When Posting An EventSrinivas ManchiPas encore d'évaluation

- Automatic Fruit Image Recognition System Based On Shape and Color FeaturesDocument2 pagesAutomatic Fruit Image Recognition System Based On Shape and Color FeaturesakshayPas encore d'évaluation

- SMS SRH-2D SedimentTransportDocument19 pagesSMS SRH-2D SedimentTransportthendyPas encore d'évaluation

- Electrosurgical Text HandboockDocument94 pagesElectrosurgical Text HandboockThéu Castro100% (1)

- Viscosity Measurements On Oligoesters From Terephthalic Acid and GlycoDocument7 pagesViscosity Measurements On Oligoesters From Terephthalic Acid and GlycoMaria RincondePas encore d'évaluation

- Digital Control SystemDocument34 pagesDigital Control SystemLaxman Koirala100% (3)

- Chapter 11Document53 pagesChapter 11Vijendhar ReddyPas encore d'évaluation

- Code Division DuplexingDocument19 pagesCode Division DuplexingNitin SakpalPas encore d'évaluation

- Calculation Sheet Boiler Control BuildingDocument35 pagesCalculation Sheet Boiler Control BuildingKhamal Rachmanda AdamPas encore d'évaluation

- Devlopment and Analysis of Natural Banana Fiber CompositeDocument3 pagesDevlopment and Analysis of Natural Banana Fiber CompositeEditor IJRITCCPas encore d'évaluation

- Thermal Analysis and Compensation of A Double Column Machining CentreDocument9 pagesThermal Analysis and Compensation of A Double Column Machining CentreShamanth CPas encore d'évaluation

- Test A: Two-Dimensional Motion and VectorsDocument9 pagesTest A: Two-Dimensional Motion and VectorsAref DahabrahPas encore d'évaluation

- TH 2100Document67 pagesTH 2100KI TechnologiesPas encore d'évaluation

- Tutorial - How To Use The Poser Format ExporterDocument7 pagesTutorial - How To Use The Poser Format ExporterMimhypopbummilha SwuPas encore d'évaluation

- Part 1Document120 pagesPart 1Raju Halder0% (1)

- Lec.5 (Prameters of OHTL Pt.2)Document10 pagesLec.5 (Prameters of OHTL Pt.2)AbdullahPas encore d'évaluation

- 3questions Measurements and UncertaintyDocument2 pages3questions Measurements and UncertaintyLeanne DerigePas encore d'évaluation

- Summative Test in Grade 10 Science PDF FreeDocument2 pagesSummative Test in Grade 10 Science PDF FreeMalyn ReyesPas encore d'évaluation

- Abbott 2021 ApJL 915 L5Document24 pagesAbbott 2021 ApJL 915 L5Manju SanthakumariPas encore d'évaluation

- Structure Lab Manual FullDocument318 pagesStructure Lab Manual FullRodrigo Requelme BorjaPas encore d'évaluation

- Energy Audit Report by CPRIDocument247 pagesEnergy Audit Report by CPRImag_ktps20021520100% (2)

- Instruction For Lab Practice: 5. No Cancellation of Booked Slot Is Allowed This TimeDocument12 pagesInstruction For Lab Practice: 5. No Cancellation of Booked Slot Is Allowed This Timebalaji817150Pas encore d'évaluation

- Measurement of Earthing Systems: Central Networks Earthing Manual Section E4Document45 pagesMeasurement of Earthing Systems: Central Networks Earthing Manual Section E4ahmed_k7117Pas encore d'évaluation

- Unit 10 Lesson 3 Activity Guide - Unreasonable TimeDocument2 pagesUnit 10 Lesson 3 Activity Guide - Unreasonable Timetrivediom427Pas encore d'évaluation

- Vogue 201602 Japan PDFDocument254 pagesVogue 201602 Japan PDFJack Douglas YooPas encore d'évaluation

- Astm A106-2002Document13 pagesAstm A106-2002henryPas encore d'évaluation