Académique Documents

Professionnel Documents

Culture Documents

Tle 4729

Transféré par

Abbode HoraniDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Tle 4729

Transféré par

Abbode HoraniDroits d'auteur :

Formats disponibles

2-Phase Stepper-Motor Driver TLE 4729 G

Bipolar-IC

Overview

Features

• 2 × 0.7 amp. full bridge outputs

• Integrated driver, control logic and current control

(chopper)

• Very low current consumption in inhibit mode

• Fast free-wheeling diodes P-DSO-24-3

• Max. supply voltage 45 V

• Output stages are free of crossover current

• Offset-phase turn-ON of output stages

• All outputs short-circuit proof

• Error-flag for overload, open load, over-temperature

• SMD package P-DSO-24-3

Type Ordering Code Package

TLE 4729 G Q67006-A9312 P-DSO-24-3

Description

TLE 4729 G is a bipolar, monolithic IC for driving bipolar stepper motors, DC motors and

other inductive loads that operate by constant current. It is fully pin and function

compatible except the current programing is inverse to the TLE 4728 G with an additional

inhibit feature. The control logic and power output stages for two bipolar windings are

integrated on a single chip which permits switched current control of motors with 0.7 A

per phase at operating voltages up to 16 V.

The direction and value of current are programmable for each phase via separate control

inputs. In the case of low at all four current program inputs the device is switched in

inhibit mode automatically. A common oscillator generates the timing for the current

control and turn-on with phase offset of the two output stages. The two output stages in

full-bridge configuration include fast integrated freewheeling diodes and are free of

crossover current. The device can be driven directly by a microprocessor in several

modes by programming phase direction and current control of each bridge

independently.

With the two error outputs the TLE 4729 G signals malfunction of the device. Setting the

control inputs high resets the error flag and by reactivating the bridges one by one the

location of the error can be found.

Data Sheet 1 1999-06-24

TLE 4729 G

TLE 4729 G

Ι 10 1 24 Ι 20

Ι 11 2 23 Ι 21

Phase 1 3 22 Phase 2

OSC 4 21 Error 1

GND 5 20 GND

GND 6 19 GND

GND 7 18 GND

GND 8 17 GND

Q11 9 16 Q21

R1 10 15 R2

+V S 11 14 Error 2

Q12 12 13 Q22

AEP02195

Figure 1 Pin Configuration (top view)

Data Sheet 2 1999-06-24

TLE 4729 G

Pin Definitions and Functions

Pin No. Function

1, 2, 23, 24 Digital control inputs IX0, IX1 for the magnitude of the current of the

particular phase.

Iset = 450 mA with Rsense = 1 Ω

IX1 IX0 Phase Current Example of

Motor Status

L L 0 No current 1)

L H 0.155 × Iset Hold

H L Iset Normal mode

H H 1.55 × Iset Accelerate

1)

“No current” in both bridges inhibits the circuit and current

consumption will sink below 50 µA (inhibit-mode)

3 Input phase 1; controls the current through phase winding 1. On

H-potential the phase current flows from Q11 to Q12, on L-potential in

the reverse direction.

5 ... 8, Ground; all pins are connected at leadframe internally.

17 ... 20

4 Oscillator; works at approx. 25 kHz if this pin is wired to ground across

2.2 nF.

10 Resistor R1 for sensing the current in phase 1.

9, 12 Push-pull outputs Q11, Q12 for phase 1 with integrated free-wheeling

diodes.

11 Supply voltage; block to ground, as close as possible to the IC, with a

stable electrolytic capacitor of at least 47 µF in parallel with a ceramic

capacitor of 100 nF.

14 Error 2 output; signals with “low” the errors: short circuit to ground of

one or more outputs or over-temperature.

13, 16 Push-pull outputs Q22, Q21 for phase 2 with integrated free-wheeling

diodes.

15 Resistor R2 for sensing the current in phase 2.

Data Sheet 3 1999-06-24

TLE 4729 G

Pin Definitions and Functions (cont’d)

Pin No. Function

21 Error 1 output; signals with “low” the errors: open load or short circuit

to + VS of one or more outputs or short circuit of the load or over-

temperature.

22 Input phase 2; controls the current flow through phase winding 2. On

H-potential the phase current flows from Q21 to Q22, on L-potential in

the reverse direction.

+V S

OSC

Oscillator

C OSC Q11

T11 T12

D11 D12

Ι 10

Function

Ι 11 Logic T13 T14

Q12

Phase 1 D13 D14

Phase 1

Error 1

R1

R sense

Error-Flag

Error 2 TLE 4729 G

Generation

+V S

Inhibit

Q21

T21 T22

D21 D22

Ι 20

Function

Ι 21 Logic T23 T24

Q22

Phase 2 D23 D24

Phase 2

R2

GND R sense

AEB02196

Figure 2 Block Diagram

Data Sheet 4 1999-06-24

TLE 4729 G

Absolute Maximum Ratings

Tj = – 40 to 150 °C

Parameter Symbol Limit Values Unit Remarks

min. max.

Supply voltage VS – 0.3 45 V –

Error outputs VErr – 0.3 45 V –

IErr – 3 mA –

Output current IQ –1 1 A –

Ground current IGND –2 – A –

Logic inputs VIXX – 15 15 V IXX; Phase 1, 2

Oscillator voltage VOSC – 0.3 6 V –

R1, R2 input voltage VRX – 0.3 5 V –

Junction temperature Tj – 125 °C –

Tj – 150 °C max. 10,000 h

Storage temperature Tstg – 50 125 °C –

Thermal resistances

Junction-ambient Rth ja – 75 K/W –

Junction-ambient Rth ja – 50 K/W –

(soldered on a 35 µm

thick 20 cm2 PC board

copper area)

Junction-case Rth jc – 15 K/W Measured on

pin 5

Note: Stresses above those listed here may cause permanent damage to the

device. Exposure to absolute maximum rating conditions for extended

periods may affect device reliability.

Operating Range

Supply voltage VS 5 16 V –

Case temperature TC – 40 110 °C Measured on

pin 5; Pdiss = 2 W

Output current IQ – 800 800 mA –

Logic inputs VIXX –5 6 V IXX; Phase 1, 2

Error outputs VErr – 25 V –

IErr 0 1 mA –

Note: In the operating range, the functions given in the circuit description are fulfilled.

Data Sheet 5 1999-06-24

TLE 4729 G

Characteristics

VS = 6 to 16 V; Tj = – 40 to 130 °C

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Current Consumption

From + VS IS – – 50 µA IXX = L; VS = 12;

Tj ≤ 85 °C

From + VS IS 20 30 50 mA IQ1, 2 = 0 A

Oscillator

Output charging current IOSC 90 120 135 µA –

Charging threshold VOSCL 0.8 1.3 1.9 V –

Discharging threshold VOSCH 1.7 2.3 2.9 V –

Frequency fOSC 18 24 30 kHz COSC = 2.2 nF

Phase Current (VS = 9 … 16 V)

Mode “no current” IQ – 0 – mA IX0 = L; IX1 = L

Voltage threshold of current

Comparator at Rsense in

mode: Vch 40 70 100 mV IX0 = H; IX1 = L

Hold Vcs 410 450 510 mV IX0 = L; IX1 = H

Setpoint Vca 630 700 800 mV IX0 = H; IX1 = H

Accelerate

Logic Inputs (Phase X)

Threshold VI 1.2 1.7 2.2 V –

Hysteresis VIHy – 200 – mV –

L-input current IIL – 10 –1 1 µA VI = 1.2 V

L-input current IIL – 100 – 20 –5 µA VI = 0 V

H-input current IIH –1 0 10 µA VI = 5 V

Data Sheet 6 1999-06-24

TLE 4729 G

Characteristics (cont’d)

VS = 6 to 16 V; Tj = – 40 to 130 °C

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Logic Inputs (IX1; IX0)

Threshold VI 0.8 1.7 2.2 V –

Hysteresis VIHy – 200 – mV –

L-input current IIL – 100 – 5 µA VI = 0 V

H-input current IIH 5 20 50 µA VI = 5 V

Error Outputs

Saturation voltage VErrSat 50 200 500 mV IErr = 1 mA

Leakage current IErrL – – 10 µA VErr = 25 V

Thermal Protection

Shutdown Tjsd 140 150 160 °C IQ1, 2 = 0 A

Prealarm Tjpa 120 130 140 °C VErr = L

Delta ∆Tj 10 20 30 K ∆Tj = Tjsd – Tjpa

Hysteresis shutdown Tjsdhy – 20 – K –

Hysteresis prealarm Tjpahy – 20 – K –

Power Outputs

Diode Transistor Sink Pair

(D13, T13; D14, T14; D23, T23; D24, T24)

Saturation voltage VsatI 0.1 0.3 0.5 V IQ = – 0.45 A

Saturation voltage VsatI 0.2 0.5 0.8 V IQ = – 0.7 A

Reverse current IRI 500 1000 1500 µA VS = VQ = 40 V

Forward voltage VFI 0.6 0.9 1.2 V IQ = 0.45 A

Forward voltage VFI 0.7 1 1.3 V IQ = 0.7 A

Data Sheet 7 1999-06-24

TLE 4729 G

Characteristics (cont’d)

VS = 6 to 16 V; Tj = – 40 to 130 °C

Parameter Symbol Limit Values Unit Test Condition

min. typ. max.

Diode Transistor Source Pair

(T11, D11; T12, D12; T21, D21; T22, D22)

Saturation voltage VsatuC 0.6 1 1.2 V IQ = 0.45 A;

Saturation voltage VsatuD 0.1 0.3 0.6 V charge

IQ = 0.45 A;

Saturation voltage VsatuC 0.7 1.2 1.5 V discharge

Saturation voltage VsatuD 0.2 0.5 0.8 V IQ = 0.7 A; charge

IQ = 0.7 A;

Reverse current IRu 400 800 1200 µA discharge

Forward voltage VFu 0.7 1 1.3 V VS = 40 V, VQ = 0

Forward voltage VFu 0.8 1.1 1.4 V V

Diode leakage current ISL 0 3 10 mA IQ = – 0.45 A

IQ = – 0.7 A

IF = – 0.7 A

Error Output Timing

Time Phase X to IXX tPI – 5 20 µs

Time IXX to Phase X tIP – 12 100 µs

Delay Phase X to Error 2 tPEsc – 45 100 µs

Delay Phase X to Error 1 tPEol – 15 50 µs

Delay IXX to Error 2 tIEsc – 30 80 µs

Reset delay after Phase X tRP – 3 10 µs

Reset delay after IXX tRI – 1 5 µs

Note: The listed characteristics are ensured over the operating range of the integrated

circuit. Typical characteristics specify mean values expected over the production

spread. If not otherwise specified, typical characteristics apply at TA = 25 °C and

the given supply voltage.

For details see next four pages.

These parameters are not 100% tested in production, but guaranteed by design.

Data Sheet 8 1999-06-24

TLE 4729 G

Diagrams

Timing between IXX and Phase X to prevent setting the error flag

Operating conditions:

+ VS = 14 V, Tj = 25 °C, Ierr = 1 mA, load = 3.3 mH, 1 Ω

a) If tPI < typ. 5 µs, an error “open load” will be set.

Ι XX

Phase X

t PI

AET02197

Figure 3

b) If tIP < typ. 12 µs, an error “open load” will be set.

Ι XX

Phase X

t IP

AET02198

Figure 4

Data Sheet 9 1999-06-24

TLE 4729 G

This time strongly depends on + VS and inductivity of the load, see diagram below.

AED02199

30

µs

t IP

25

VS= 6 V

20

15

10

9V

12 V

5

16 V

0

0 10 20 30 40 mH 60

L

Figure 5 Time tIP versus Load Inductivity

Propagation Delay of the Error Flag

Operating conditions:

+ VS = 14 V, Tj = 25 °C, Ierr = 1 mA, load = 3.3 mH, 1 Ω

a) IXX = H, error condition: short circuit to GND.

Phase X

Error 2

t PEsc

AED02200

typ. tPEsc: 45 µs

Figure 6

Data Sheet 10 1999-06-24

TLE 4729 G

b) IXX = H, error condition: open load (equivalent: short circuit to + VS).

Phase X

Error 1

t PEol

AET02201

typ. tPEol: 15 µs

Figure 7

c) Phase X = H or L, const.; error condition: short circuit to GND.

Ι XX

Error 2

t IEsc

AET02202

typ. tIEsc: 30 µs

tIEsc is also measured under the condition: begin of short circuit to GND

till error flag set.

Figure 8

Data Sheet 11 1999-06-24

TLE 4729 G

d) IXX = H, reset of error flag when error condition is not true.

Phase x

Error X

t RP

AET02203

typ. tRP: 3 µs

Figure 9

e) Phase X = H or L, const.; reset of error flag when error condition is not true.

Ι XX

Error X

t RI

AET02204

typ. tRI: 1 µs

Figure 10

Data Sheet 12 1999-06-24

TLE 4729 G

Quiescent Current IS versus Supply Voltage Quiesc. Current IS versus Junct. Temp. Tj;

VS; bridges not chopping; Tj = 25 °C bridges not chopping, VS = 14 V

AED02205 AED02206

60 60

Ι QX =

mA mA Ι QX = 0.70 A

ΙS 0.70 A ΙS

50 50

0.45 A

0.45 A

40 40

0.07 A

0.07 A

30 30

20 20

10 10

0 0

5 10 15 V 20 -50 0 50 100 C 150

VS Tj

Oscillator Frequency fOsc versus Output Current IQX versus

Junction Temperature Tj Junction Temperature Tj

AED02207 AED02208

30 800

mA

700

kHz Ι QX Ι X1 = H, Ι X0 = H

f Osc

600

25

500

VS = 14 V 400 Ι X1 = H, Ι X0 = L

C OSC = 2.2 nF

300

20

200 V S = 14 V

R X = 1Ω

100

15 0

-50 0 50 100 C 150 -50 0 50 100 C 150

Tj Tj

Data Sheet 13 1999-06-24

TLE 4729 G

Output Saturation Voltages Vsat Forward Current IF of Free-Wheeling Diodes

versus Output Current IQ versus Forward Voltages VF

AED02209 AED02210

2.0 1.0

V sat

V S = 14 V ΙF A

V T j = 25 ˚C

T j = 25 C V Fl V Fu

0.8

1.5

0.6

V satuC

1.0

0.4

V satl

0.5 V satuD

0.2

0 0

0 0.2 0.4 0.6 A 0.8 0 0.5 1.0 V 1.5

ΙQ VF

Typical Power Dissipation Ptot versus Permissible Power Dissipation Ptot versus

Output Current IQ (non stepping) Case Temp. TC (measured at pin 5)

AED02211 AED02212

4 16

P tot P tot

L phase x = 10 mH

W W

R phase x = 2 Ω

3 C OSC = 2.2 nF 12

TC = 25 C

both phases active 10

2 8

T jmax =

V S = 14 V

6 150 C

120 C

1 4

0 0

0 0.2 0.4 0.6 A 0.8 -25 0 25 75 125 C 175

ΙQ TC

Data Sheet 14 1999-06-24

TLE 4729 G

Input Characteristics of IXX, Phase X Output Leakage Current

AED02213 AED02214

40 1.2

µA

20 Ι xx ΙR

mA

i Ι xx

0 0.8

Phase X V S = 40 V

-20

0.4

-40 V S = 16 V

Tj =

-60 40 C 0

25 C

-80 150 C

-0.4

-100

-120 -0.8

-6 -4 -2 0 2 4 V 6 0 10 20 30 V 40

V Ι xx VQ

Quiescent Current IS versus Supply Voltage

VS; inhibit mode; Tj = 25 °C

AED02215

250

µA

ΙS

200

150

100

50

0

0 5 10 15 V 20

VS

Data Sheet 15 1999-06-24

TLE 4729 G

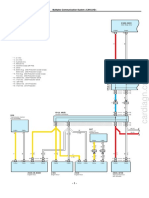

+12V

100 nF 100 µ F

11

1 VS

Ι 10

2

Ι 11 9

3 Q11

Phase 1 12

21 Q12

Error 1

Microcontroller 14 TLE 4729 G 16

Error 2 Q21

24 13 M

Ι 20 Q22

23 Stepper

Ι 21

22 Motor

Phase 2

OSC GND

4 15 10 5,6,7,8,

R2 R1 17,18,19,20

22 nF

1Ω 1Ω

AES02216

Figure 11 Application Circuit

VS

100 µF 100 nF

ΙS

+V S V satu V Fu

Ι XX, Phase X

ΙΙ Ι Rl

TLE 4729 G Output

ΙQ Ι Ru

Error X

VΙ Ι Err

V satl

Osc GND R sense V Fl

V Err

Ι OSC Ι SL Ι GND Ι Rsense

V OSC

2.2 nF VC 1Ω

AES02217

Figure 12 Test Circuit

Data Sheet 16 1999-06-24

TLE 4729 G

full step operation

accelerate mode normal mode

H

Ι 10

L

t

H

Ι 11

L

t

H

Phase 1

L

t

i acc

i set

Ι Q1

t

- i set

- i acc

i acc

i set

Ι Q2

t

- i set

- i acc

H

Phase 2

L

t

H

Ι 20

L

t

H

Ι 21

L

t

AED02218

Figure 13 Full Step Operation

Data Sheet 17 1999-06-24

TLE 4729 G

half step operation

accelerate mode normal mode

H

Ι 10

L

t

H

Ι 11

L

t

H

Phase 1

L

t

i acc

i set

Ι Q1

t

- i set

- i acc

i acc

i set

Ι Q2

t

- i set

- i acc

H

Phase 2

L

t

H

Ι 20

L

t

H

Ι 21

L

t

AED02219

Figure 14 Half Step Operation

Data Sheet 18 1999-06-24

TLE 4729 G

V Osc

V Osc H

V Osc L

t

Ι Rsense 1

0

t

Ι Rsense 2

0

t

V Q12

+ VS

V FU

V satl

V ca

0 t

V Q11 V satu D V satu C

+ VS

V Q22

+ VS

0

V Q21 t

+ VS

Ι Q1

i acc

Ι Q2

t

i acc

t

Operating conditions:

VS = 14 V Phase x = H

L phase x = 10 mH Ι XX =H

R phase x = 4 Ω AED02220

Figure 15 Current Control in Chop-Mode

Data Sheet 19 1999-06-24

TLE 4729 G

V Osc

2.3 V

1.3 V Oscillator

High Imped.

0V

Phase change-over t

Phase H

L

t

Ι Rsense 1

0

t

V Q11

+VS

High

Impedance

t

V Q12

+VS

High

Impedance

Ι set

Ι Phase 1 fast current

decay

T1 slow current decay t

Operating conditions: - Ι set

VS = 14 V Ι 11 = L for t < T 1

L phase 1 = 1 mH Ι 11 = H for t > T 1 slow current decay

R phase 1 = 4 Ω Ι 10 = Ι 2X = L AED02221

Figure 16 Phase Reversal and Inhibit

Data Sheet 20 1999-06-24

TLE 4729 G

Calculation of Power Dissipation

The total power dissipation Ptot is made up of

saturation losses Psat (transistor saturation voltage and diode forward

voltages),

quiescent losses Pq (quiescent current times supply voltage) and

switching losses Ps (turn-ON / turn-OFF operations).

The following equations give the power dissipation for chopper operation without phase

reversal.

This is the worst case, because full current flows for the entire time and switching losses

occur in addition.

Ptot = 2 × Psat + Pq + 2 × Ps

where

Psat ≅ IN {VsatI × d + VFu (1 – d) + VsatuC × d + VsatuD (1 – d)}

Pq = Iq × VS

V i D × t DON ( i D + i R ) × t ON I N

P q ≅ -----S- --------------------

- + ---------------------------------- + ---- ( t DOFF + t OFF )

T 2 4 2

IN = nominal current (mean value)

Iq = quiescent current

iD = reverse current during turn-on delay

iR = peak reverse current

tp = conducting time of chopper transistor

tON = turn-ON time

tOFF = turn-OFF time

tDON = turn-ON delay

tDOFF = turn-OFF delay

T = cycle duration

d = duty cycle tp / T

Vsatl = saturation voltage of sink transistor (TX3, TX4)

VsatuC = saturation voltage of source transistor (TX1, TX2) during charge cycle

VsatuD = saturation voltage of source transistor (TX1, TX2) during discharge cycle

VFu = forward voltage of free-wheeling diode (DX1, DX2)

VS = supply voltage

Data Sheet 21 1999-06-24

TLE 4729 G

+V S

Tx2

Tx1 Dx1 Dx2

Tx4

Tx3 Dx3 Dx4

VC

R sense

AET02222

Figure 17

Turn-ON Turn-OFF

Voltage and

iR ΙN

Current on iD

Chopper V S + V Fu

Transistor

V S + V Fu

V satl

t

t D ON t ON t D OFF t OFF

tP

AET02223

Figure 18 Voltage and Current on Chopper Transistor

Data Sheet 22 1999-06-24

TLE 4729 G

Application Hints

The TLE 4729 G is intended to drive both phases of a stepper motor. Special care has

been taken to provide high efficiency, robustness and to minimize external components.

Power Supply

The TLE 4729 G will work with supply voltages ranging from 5 V to 16 V at pin VS. Surges

exceeding 16 V at V S wont harm the circuit up to 45 V, but whole function is not

guaranteed. As soon as the voltage drops below approximately 16 V the TLE 4729 G

works promptly again.

As the circuit operates with chopper regulation of the current, interference generation

problems can arise in some applications. Therefore the power supply should be

decoupled by a 0.1 µF ceramic capacitor located near the package. Unstabilized

supplies may even afford higher capacities.

Inhibit Mode

In the case of low at all four current program inputs IXX the device will switch into inhibit

condition; the current consumption is reduced to very low values.

When starting operation again, i.e. putting at least one IXX to high potential, the Error 1

output signals an open load error if the corresponding phase input is high. The error is

reset by first recirculation in chop mode.

Current Sensing

The current in the windings of the stepper motor is sensed by the voltage drop across

Rsense. Depending on the selected current internal comparators will turn off the sink

transistor as soon as the voltage drop reaches certain thresholds (typical 0 V, 0.07 V,

0.45 V and 0.7 V). These thresholds are not affected by variations of VS. Consequently

instabilized supplies will not affect the performance of the regulation. For precise current

level it must be considered, that internal bounding wire (typ. 60 mΩ) is a part of Rsense.

Due to chopper control fast current rises (up to 10 A/µs) will occur at the sensing

resistors. To prevent malfunction of the current sensing mechanism Rsense should be

pure ohmic. The resistors should be wired to GND as directly as possible. Capacitive

loads such as long cables (with high wire to wire capacity) to the motor should be

avoided for the same reason.

Synchronizing Several Choppers

In some applications synchrone chopping of several stepper motor drivers may be

desirable to reduce acoustic interference. This can be done by forcing the oscillator of

the TLE 4729 G by a pulse generator overdriving the oscillator loading currents

(approximately ± 120 µA). In these applications low level should be between 0 V and

0.8 V while high level should between 3 V and 5 V.

Data Sheet 23 1999-06-24

TLE 4729 G

Application Hints (cont’d)

Optimizing Noise Immunity

Unused inputs should always be wired to proper voltage levels in order to obtain highest

possible noise immunity.

To prevent crossconduction of the output stages the TLE 4729 G uses a special break

before make timing of the power transistors. This timing circuit can be triggered by short

glitches (some hundred nanoseconds) at the phase inputs causing the output stage to

become high resistive during some microseconds. This will lead to a fast current decay

during that time. To achieve maximum current accuracy such glitches at the phase

inputs should be avoided by proper control signals.

To lower EMI a ceramic capacitor of max. 3 nF is advisable from each output to GND.

Thermal Shut Down

To protect the circuit against thermal destruction, thermal shut down has been

implemented.

Error Monitoring

The error outputs signal corresponding to the logic table the errors described below.

Logic Table

Kind of Error Error Output

Error 1 Error 2

a) No error H H

b) Short circuit to GND H L

c) Open load 1) L H

d) b) and c) simultaneously H L

e) Temperature prealarm L L

1)

Also possible: short circuit to + VS or short circuit of the load.

Over-Temperature is implemented as pre-alarm; it appears approximately 20 K before

thermal shut down. To detect an open load, the recirculation of the inductive load is

watched. If there is no recirculation after a phase change-over, an internal error flipflop

is set. Because in most kinds of short circuits there won’t flow any current through the

motor, there will be no recirculation after a phase change-over, and the error flipflop for

open load will be set, too. Additionally an open load error is signaled after a phase

change-over during hold mode.

Data Sheet 24 1999-06-24

TLE 4729 G

Only in the case of a short circuit to GND, the most probably kind of a short circuit in

automotive applications, the malfunction is signaled dominant (see d) in logic table) by a

separate error flag. Simultaneously the output current is disabled after 30 µs to prevent

disturbances.

A phase change-over or putting both current control inputs of the affected bridge on low

potential resets the error flipflop. Being a separate flipflop for every bridge, the error can

be located in easy way.

Data Sheet 25 1999-06-24

TLE 4729 G

Package Outlines

P-DSO-24-3

(Plastic Dual Small Outline Package)

0.35 x 45˚

2.65 max

2.45 -0.2

7.6 -0.2 1)

0.2 -0.1

+0.09

x

8˚ ma

0.23

1.27 0.4 +0.8

0.35 +0.15 2) 0.1 10.3 ±0.3

0.2 24x

24 13

1 12

15.6 -0.4 1)

Index Marking

1) Does not include plastic or metal protrusions of 0.15 max rer side

2) Does not include dambar protrusion of 0.05 max per side GPS05144

Sorts of Packing

Package outlines for tubes, trays etc. are contained in our

Data Book “Package Information”.

SMD = Surface Mounted Device Dimensions in mm

Data Sheet 26 1999-06-24

Vous aimerez peut-être aussi

- E19 (B), E20 (C) : Multiplex Communication SystemDocument14 pagesE19 (B), E20 (C) : Multiplex Communication SystemAbbode HoraniPas encore d'évaluation

- 2015+Toyota+Tundra+Repair+Manual N7 PDFDocument9 pages2015+Toyota+Tundra+Repair+Manual N7 PDFAbbode HoraniPas encore d'évaluation

- Ignition Systems - 2JZ-GTEDocument13 pagesIgnition Systems - 2JZ-GTEAbbode HoraniPas encore d'évaluation

- Ignition SystemDocument16 pagesIgnition SystemAbbode HoraniPas encore d'évaluation

- Charging (5vz-Fe)Document15 pagesCharging (5vz-Fe)Abbode HoraniPas encore d'évaluation

- Service SpecificationsDocument93 pagesService SpecificationsAbbode Horani100% (2)

- Brake PDFDocument60 pagesBrake PDFAbbode HoraniPas encore d'évaluation

- Starting (5vz-Fe)Document18 pagesStarting (5vz-Fe)Abbode HoraniPas encore d'évaluation

- 34 Rear SuspensionDocument5 pages34 Rear SuspensionAbbode HoraniPas encore d'évaluation

- Starting (2uz-Fe)Document20 pagesStarting (2uz-Fe)Abbode HoraniPas encore d'évaluation

- Service SpecificationsDocument93 pagesService SpecificationsAbbode HoraniPas encore d'évaluation

- Emission Control (2uz-Fe)Document15 pagesEmission Control (2uz-Fe)Abbode HoraniPas encore d'évaluation

- ClutchDocument21 pagesClutchAbbode HoraniPas encore d'évaluation

- Transfer (VF2BM)Document2 pagesTransfer (VF2BM)Abbode HoraniPas encore d'évaluation

- CLUTCHDocument21 pagesCLUTCHAbbode HoraniPas encore d'évaluation

- Pwde9502-D Carisma 99 Chassis 22Document5 pagesPwde9502-D Carisma 99 Chassis 22Abbode HoraniPas encore d'évaluation

- Charging (5vz-Fe)Document15 pagesCharging (5vz-Fe)Abbode HoraniPas encore d'évaluation

- 13e Diesel Fuel PDFDocument15 pages13e Diesel Fuel PDFAbbode HoraniPas encore d'évaluation

- MMC 380 Workshop Manual 2005Document8 pagesMMC 380 Workshop Manual 2005Abbode HoraniPas encore d'évaluation

- Jamnagar Mahanagar Seva Sadan Mukhya Mantri Gruh Yojna - Ews - Applicants ListDocument8 pagesJamnagar Mahanagar Seva Sadan Mukhya Mantri Gruh Yojna - Ews - Applicants ListAbbode HoraniPas encore d'évaluation

- 13f Fuel SupplyDocument9 pages13f Fuel Supplyhenry_zambranoPas encore d'évaluation

- GR00000300 52 PDFDocument2 pagesGR00000300 52 PDFAbbode HoraniPas encore d'évaluation

- Hilux 2KD PDFDocument10 pagesHilux 2KD PDFHugo PacoPas encore d'évaluation

- Chery Maintenance Manual For Oriental SonDocument13 pagesChery Maintenance Manual For Oriental SonAbbode HoraniPas encore d'évaluation

- Accelerator Control System: SectionDocument4 pagesAccelerator Control System: SectionAbbode HoraniPas encore d'évaluation

- Auto Cruise Control System: SectionDocument2 pagesAuto Cruise Control System: SectionAbbode HoraniPas encore d'évaluation

- SSP - 358 - Hot-Film Air-Mass Meter HFM 6Document20 pagesSSP - 358 - Hot-Film Air-Mass Meter HFM 6dromakiPas encore d'évaluation

- Immokiller 1.1 Software For Immobilizer: PDF Created With Pdffactory Pro Trial VersionDocument5 pagesImmokiller 1.1 Software For Immobilizer: PDF Created With Pdffactory Pro Trial VersionAbbode HoraniPas encore d'évaluation

- Aw80 40leDocument3 pagesAw80 40leAbbode HoraniPas encore d'évaluation

- 6 Speed Sleeve ReplacementDocument3 pages6 Speed Sleeve ReplacementJamil ElbannaPas encore d'évaluation

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- (Counter) Paper - 1 - 7967 - 163 PDFDocument57 pages(Counter) Paper - 1 - 7967 - 163 PDFmaprofPas encore d'évaluation

- 8-Bit Serial-Input/Serial or Parallel-Output Shift Register With Latched 3-State OutputsDocument11 pages8-Bit Serial-Input/Serial or Parallel-Output Shift Register With Latched 3-State OutputsLưu TinhPas encore d'évaluation

- P3T32 en M G006 IEC Web PDFDocument416 pagesP3T32 en M G006 IEC Web PDFChristian Bravo De GuzmanPas encore d'évaluation

- Question Bank Chapter 6 and Chapter 7Document5 pagesQuestion Bank Chapter 6 and Chapter 7noonePas encore d'évaluation

- Lab Manual FOR Computer Organization LabDocument13 pagesLab Manual FOR Computer Organization Labhifzan786Pas encore d'évaluation

- ECE380 Digital Logic: Synchronous Sequential Circuits: Implementations Using D-Type, T-Type and JK-type Flip-FlopsDocument9 pagesECE380 Digital Logic: Synchronous Sequential Circuits: Implementations Using D-Type, T-Type and JK-type Flip-FlopsMoHsin KhPas encore d'évaluation

- Ee6502 Microprocessors and MicrocontrollersDocument97 pagesEe6502 Microprocessors and MicrocontrollersAnbalagan Guru0% (1)

- Pa3 Libguide Ide Ug PDFDocument193 pagesPa3 Libguide Ide Ug PDFsriharshaPas encore d'évaluation

- Us 14 Oh Reverse Engineering Flash Memory For Fun and Benefit WP PDFDocument35 pagesUs 14 Oh Reverse Engineering Flash Memory For Fun and Benefit WP PDFFrancisco AlvesPas encore d'évaluation

- 1986FujitsuMemoriesDatabook 894963362Document1 176 pages1986FujitsuMemoriesDatabook 894963362กิจรุ่งเรือง โพจันPas encore d'évaluation

- Exploringdigitallogic With Logisim-Evolution: GeorgeselfDocument265 pagesExploringdigitallogic With Logisim-Evolution: GeorgeselfsaraPas encore d'évaluation

- Connect. 611U To The CPUDocument68 pagesConnect. 611U To The CPUVladimirAgeevPas encore d'évaluation

- M62429P/FP: Serial Data Control Dual Electronic VolumeDocument6 pagesM62429P/FP: Serial Data Control Dual Electronic VolumeStefanoViganóPas encore d'évaluation

- 4.222 S.y.b.sc - Physics Sem III IVDocument24 pages4.222 S.y.b.sc - Physics Sem III IVChandan GuptaPas encore d'évaluation

- DSE4520 MKII User Manual PDFDocument41 pagesDSE4520 MKII User Manual PDFDonovan van der Sandt100% (2)

- TMS 1000 Series Data Manual Dec76Document46 pagesTMS 1000 Series Data Manual Dec76Juan EstebanPas encore d'évaluation

- CH - 1Document155 pagesCH - 1Abdela Aman MtechPas encore d'évaluation

- Counters 1Document40 pagesCounters 1A10-14Rajat KumarPas encore d'évaluation

- Course: Electronic Engineering UEC001: Topic: Sequential CircuitsDocument35 pagesCourse: Electronic Engineering UEC001: Topic: Sequential Circuitsgoku dukePas encore d'évaluation

- Pseudo-Noise SequencesDocument10 pagesPseudo-Noise SequencesNgọc ToảnPas encore d'évaluation

- Cpe 308 Lab 10Document8 pagesCpe 308 Lab 10Victor DanielPas encore d'évaluation

- Control Display Modules: 3-LDSM, 3-24x Series, 3-12xx Series, 3-6/3S1xxx SeriesDocument4 pagesControl Display Modules: 3-LDSM, 3-24x Series, 3-12xx Series, 3-6/3S1xxx Seriesluis valdezPas encore d'évaluation

- KL 310Document4 pagesKL 310khaled07200Pas encore d'évaluation

- Very Good Notes-Up2Document304 pagesVery Good Notes-Up2Abhay SortePas encore d'évaluation

- Motorola SeminarsandApplicationBooksCMOSDataManualVolume2 SpecialFunctionsOCRDocument423 pagesMotorola SeminarsandApplicationBooksCMOSDataManualVolume2 SpecialFunctionsOCRFLAVIO100% (3)

- Combinational Circuits: ALU: AND OR ADD SUB SLT Zero (A B)Document16 pagesCombinational Circuits: ALU: AND OR ADD SUB SLT Zero (A B)anbanePas encore d'évaluation

- B.Tech EC Syllabus 3rd YearDocument35 pagesB.Tech EC Syllabus 3rd Yearpcjoshi02Pas encore d'évaluation

- Lab7 - Behavioral Modeling and Timing ConstraintsDocument6 pagesLab7 - Behavioral Modeling and Timing Constraintswert1a2Pas encore d'évaluation

- Analog and Digital Lab: Course OutcomesDocument12 pagesAnalog and Digital Lab: Course OutcomesHanduPas encore d'évaluation

- Study Plan EE-221 Digital Logic DesignDocument5 pagesStudy Plan EE-221 Digital Logic Designnauman yasinPas encore d'évaluation