Académique Documents

Professionnel Documents

Culture Documents

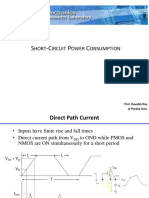

Ulti Upply Oltage: Prof. Kaushik Roy at Purdue Univ

Transféré par

Dr. Sampatrao L PinjareTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Ulti Upply Oltage: Prof. Kaushik Roy at Purdue Univ

Transféré par

Dr. Sampatrao L PinjareDroits d'auteur :

Formats disponibles

MULTI-SUPPLY VOLTAGE

Prof. Kaushik Roy

@ Purdue Univ.

Multi-Supply Voltage: Basic Idea

•Use higher supply in the critical sections of logic

•Lower supply voltage in the non-critical sections

•Might need level converters to communicate between

different voltage levels

•Major improvement in dynamic power due to lower

supply voltage blocks

Prof. Kaushik Roy

@ Purdue Univ.

Example: Multi-Voltage Scheduling

Clock

0

1 A1 A4 A1 M4 A1

Bottlenecks for single 2 A2 A2 A2

A3 A3 A3

Vdd, VT, Clock 3

4

Non-Uniform Clock Number of

Path Length Period Control Steps

source Clock Resources

Cycle (1+,2*)

y(n-1) x(n)

Schedule to exploit -a1

[1]

-a2

y(n-2)

b0

0

1

*

4V

*

3V

slack 2

*

3 4V

+

4 4V

+

y(n)

5 4V

sink

Source: Intel [-max latency] max latency=5

Prof. Kaushik Roy

@ Purdue Univ.

Multi-Voltage IC Design Issues

high VDD high VDD

Level Conversions

OUT OUT

low VDD

IN

DC-DC Efficiency

• need efficiency of at least

to break even VHI2

2

Layout: VLO

• separate power and ground routing

• substrate contacts between voltage regions

Source: Intel

Prof. Kaushik Roy

@ Purdue Univ.

Multi-Voltage Results

• Summary of results:

– up to 50% energy savings 1 vs. 2 voltages

– less than 15% additional savings 2 vs. 3

– area penalties vary from 0 up to 170%

Source: Intel

Prof. Kaushik Roy

@ Purdue Univ.

Vous aimerez peut-être aussi

- Linux Kernel and Device DriversDocument492 pagesLinux Kernel and Device DriversshankarnarendraPas encore d'évaluation

- Rinnai Service ManualDocument112 pagesRinnai Service Manualrlynch33100% (1)

- GE T2100 Treadmill Service Manual Rev A.Document152 pagesGE T2100 Treadmill Service Manual Rev A.Marckus Brody0% (1)

- Computer Workstation Ergonomics Self Assessment ChecklistDocument3 pagesComputer Workstation Ergonomics Self Assessment ChecklistPrashanth Vijender100% (2)

- Introduction To Analog Design: Dr. S. L. PinjareDocument65 pagesIntroduction To Analog Design: Dr. S. L. PinjareDr. Sampatrao L Pinjare100% (1)

- Analog Layout UTLDocument3 pagesAnalog Layout UTLDr. Sampatrao L PinjarePas encore d'évaluation

- Closing The Gap Between Asic Custom Tools and TechniquesDocument431 pagesClosing The Gap Between Asic Custom Tools and TechniquesAnonymous ZaO7fL4t100% (3)

- Overview of MEMSDocument152 pagesOverview of MEMSDr. Sampatrao L PinjarePas encore d'évaluation

- ECEN 325 Lab 3: Operational Amplifiers - Part IDocument4 pagesECEN 325 Lab 3: Operational Amplifiers - Part ISam AlbaPas encore d'évaluation

- EE201 CHP 3.1 W4L2 UpDocument14 pagesEE201 CHP 3.1 W4L2 Upzain khuramPas encore d'évaluation

- DC Circuits: Fundamentals of Electric CircuitsDocument33 pagesDC Circuits: Fundamentals of Electric CircuitsHoàng HoàngAnhPas encore d'évaluation

- ch4 (20231004)Document33 pagesch4 (20231004)jane8773Pas encore d'évaluation

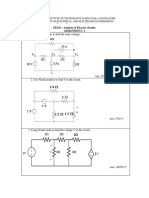

- COURSE TITLE: Electrical Circuits Design I Lab COURSE CODE: 182.6Document1 pageCOURSE TITLE: Electrical Circuits Design I Lab COURSE CODE: 182.6jubayerrislamPas encore d'évaluation

- PR No.2 Superposition TheoremDocument4 pagesPR No.2 Superposition Theorembadgujar_bandhuPas encore d'évaluation

- Part 2 Resistive Circuit Luoguomin Unit1 6pscDocument8 pagesPart 2 Resistive Circuit Luoguomin Unit1 6pscTamim SikderPas encore d'évaluation

- FALLSEM2022-23 EEE1024 ETH VL2022230107633 Reference Material I 07-10-2022 Module 1 L3 Node Voltage Analysis Mesh Current AnalysisDocument11 pagesFALLSEM2022-23 EEE1024 ETH VL2022230107633 Reference Material I 07-10-2022 Module 1 L3 Node Voltage Analysis Mesh Current AnalysisKaushik VijayakumarPas encore d'évaluation

- EEE1001 Basic Electrical and Electronics Engineering: Node Voltage Analysis, Mesh Current AnalysisDocument11 pagesEEE1001 Basic Electrical and Electronics Engineering: Node Voltage Analysis, Mesh Current AnalysisISHAAAAAAAAAAANPas encore d'évaluation

- Principle of Equivalence, Series and Parallel Connections, Thevenin Equivalent CircuitDocument37 pagesPrinciple of Equivalence, Series and Parallel Connections, Thevenin Equivalent CircuitNo OnePas encore d'évaluation

- Jawaharlal Nehru Engineering College: Laboratory ManualDocument28 pagesJawaharlal Nehru Engineering College: Laboratory ManualsanjbishtPas encore d'évaluation

- 112 SyllabusDocument10 pages112 Syllabusluoaier1016Pas encore d'évaluation

- ECE333 Renewable Energy Systems 2015 Lect3Document31 pagesECE333 Renewable Energy Systems 2015 Lect3rdelgranadoPas encore d'évaluation

- Chapter 2Document20 pagesChapter 2badrilaminPas encore d'évaluation

- Activity 4: Mesh Analysis, Nodal Analysis and Superposition TheoremDocument23 pagesActivity 4: Mesh Analysis, Nodal Analysis and Superposition Theoremjian cool dudePas encore d'évaluation

- Conclusion Circuits LabDocument22 pagesConclusion Circuits Laber denice catamoraPas encore d'évaluation

- Slides of Lecture3Document29 pagesSlides of Lecture3rudra patraPas encore d'évaluation

- Indian Institute of Technology BombayDocument2 pagesIndian Institute of Technology BombayArman KhanPas encore d'évaluation

- Diodes Lesson 6# PDFDocument40 pagesDiodes Lesson 6# PDFMohsin ElgondiPas encore d'évaluation

- Non LinearDocument11 pagesNon LinearvineethrajuPas encore d'évaluation

- ESC201 Assignment 1Document3 pagesESC201 Assignment 1garud2221Pas encore d'évaluation

- TLC 27 L 4Document44 pagesTLC 27 L 4Hendra KosasihPas encore d'évaluation

- TLC27L4, TLC27L4A, TLC27L4B, TLC27L4Y, TLC27L9 Lincmos Precision Quad Operational AmplifiersDocument43 pagesTLC27L4, TLC27L4A, TLC27L4B, TLC27L4Y, TLC27L9 Lincmos Precision Quad Operational AmplifiersMedo AntikaPas encore d'évaluation

- Lap 9Document3 pagesLap 9ABPas encore d'évaluation

- Pessli1238 PDFDocument66 pagesPessli1238 PDFiswadihrPas encore d'évaluation

- R.M.K. Engineering College: Subject Code/ Name 20EC0241/ Principles of Electronics Engineering LabDocument50 pagesR.M.K. Engineering College: Subject Code/ Name 20EC0241/ Principles of Electronics Engineering Lab2044- M.S.SANGAVIPas encore d'évaluation

- Panasonic th-32gs490dx Chassis 7n21t SMDocument35 pagesPanasonic th-32gs490dx Chassis 7n21t SMlejojoel321Pas encore d'évaluation

- C&S 2 - Series Circuits, Parallel Circuits and Series-Parallel Circuits Ganjil 1920Document5 pagesC&S 2 - Series Circuits, Parallel Circuits and Series-Parallel Circuits Ganjil 1920Ambleh AmblehPas encore d'évaluation

- EE101 Assignment 2Document2 pagesEE101 Assignment 2Sumukha ShettyPas encore d'évaluation

- Physics 2 Exp. 04 Even 2324Document7 pagesPhysics 2 Exp. 04 Even 2324RidwanPas encore d'évaluation

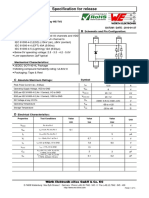

- Specification For Release: TVS Diode Array WE-TVS SOT143-4LDocument5 pagesSpecification For Release: TVS Diode Array WE-TVS SOT143-4LkapakdoonPas encore d'évaluation

- Circuit Theorems: Sjtu 1Document40 pagesCircuit Theorems: Sjtu 1Janine TuradoPas encore d'évaluation

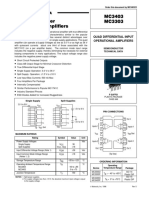

- Quad Differential Input Operational Amplifiers: Semiconductor Technical DataDocument8 pagesQuad Differential Input Operational Amplifiers: Semiconductor Technical DataVictor HemzPas encore d'évaluation

- DC Circuits: Fundamentals of Electric CircuitsDocument34 pagesDC Circuits: Fundamentals of Electric CircuitsHoàng HoàngAnhPas encore d'évaluation

- Short-Circuit-Protected High-Side SwitchingDocument1 pageShort-Circuit-Protected High-Side SwitchingThomas BORNEYPas encore d'évaluation

- Basic Electrical Engineering Tutorial 2Document5 pagesBasic Electrical Engineering Tutorial 2RajPas encore d'évaluation

- cd00004588 Macromodels User Manual For Standard Linear Products StmicroelectronicsDocument10 pagescd00004588 Macromodels User Manual For Standard Linear Products StmicroelectronicsshhmmmPas encore d'évaluation

- EPE423a Exper4Document9 pagesEPE423a Exper4Mohab ZationPas encore d'évaluation

- Chapter 2 Pen207 Lecture 6Document14 pagesChapter 2 Pen207 Lecture 6skrabeftolPas encore d'évaluation

- Cs1153 Electron Devices and Circuits LabDocument60 pagesCs1153 Electron Devices and Circuits LabDinesh KumarPas encore d'évaluation

- ZXDU68 W301 (V5.0R06M04) DC Power System User GuideDocument7 pagesZXDU68 W301 (V5.0R06M04) DC Power System User GuideSebastian Davila MontesPas encore d'évaluation

- Edc Lab Report 5Document5 pagesEdc Lab Report 5aneesPas encore d'évaluation

- EE201 CHP 3.2 W5L1 UpDocument15 pagesEE201 CHP 3.2 W5L1 Upzain khuramPas encore d'évaluation

- Lecture 3 Buck ConverterDocument13 pagesLecture 3 Buck ConverterGabriel Verdesoto YepezPas encore d'évaluation

- LM358S D PDFDocument10 pagesLM358S D PDFDevenshPas encore d'évaluation

- D2822N ShaoxingSilicoreTechnologyDocument5 pagesD2822N ShaoxingSilicoreTechnologyandrebuhlerPas encore d'évaluation

- LM324S, LM2902S Single Supply Quad Operational Amplifiers: PDIP 14 N Suffix CASE 646Document8 pagesLM324S, LM2902S Single Supply Quad Operational Amplifiers: PDIP 14 N Suffix CASE 646wijakesumaPas encore d'évaluation

- ECE 3144 Lecture 8: Dr. Rose Q. Hu Electrical and Computer Engineering Department Mississippi State UniversityDocument10 pagesECE 3144 Lecture 8: Dr. Rose Q. Hu Electrical and Computer Engineering Department Mississippi State UniversityGopakumar G NairPas encore d'évaluation

- Analog Electronics GATE IES PSU Study Materials PDFDocument17 pagesAnalog Electronics GATE IES PSU Study Materials PDFDharmveer SinghPas encore d'évaluation

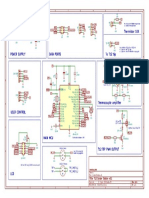

- Thermistor 10K: Tip+ Tip-Tip - Check - 1 Tip - Check - 2Document1 pageThermistor 10K: Tip+ Tip-Tip - Check - 1 Tip - Check - 2darioPas encore d'évaluation

- 2-Kirchhoff''s Current Law - Node Voltage Analysis-20!08!2023Document15 pages2-Kirchhoff''s Current Law - Node Voltage Analysis-20!08!2023Saisharan M 22BEC0603Pas encore d'évaluation

- Electrical EngineeringDocument3 pagesElectrical Engineeringmasud.firstPas encore d'évaluation

- Islamic University of Technology (Iut) : Course: Name of The ExperimentDocument2 pagesIslamic University of Technology (Iut) : Course: Name of The ExperimentshiamPas encore d'évaluation

- Quiz - SAR ADC Input TypesDocument12 pagesQuiz - SAR ADC Input TypesPintuabcPas encore d'évaluation

- Purpose: Lab 1 Diode CharacteristicsDocument7 pagesPurpose: Lab 1 Diode CharacteristicsshahidPas encore d'évaluation

- srv25 4Document9 pagessrv25 4Aditya SrivatsavPas encore d'évaluation

- Abstraet-A General Expression For An N-Port Network ReciprocityDocument3 pagesAbstraet-A General Expression For An N-Port Network ReciprocityChristopher OrtegaPas encore d'évaluation

- Ejercicios Cap05Document8 pagesEjercicios Cap05Miguel LiceagaPas encore d'évaluation

- SodapdfDocument18 pagesSodapdfby767ronPas encore d'évaluation

- Actorization AND Pproximation: Prof. Kaushik Roy at Purdue UnivDocument7 pagesActorization AND Pproximation: Prof. Kaushik Roy at Purdue UnivDr. Sampatrao L PinjarePas encore d'évaluation

- A DSP: L - P, U E P, & E R: Pplication TO OW Ower Nequal Rror Rotection Rror EsiliencyDocument11 pagesA DSP: L - P, U E P, & E R: Pplication TO OW Ower Nequal Rror Rotection Rror EsiliencyDr. Sampatrao L PinjarePas encore d'évaluation

- Approximate Full Adder CellsDocument11 pagesApproximate Full Adder CellsDr. Sampatrao L PinjarePas encore d'évaluation

- Canonical Signed Digits (CSD)Document5 pagesCanonical Signed Digits (CSD)Dr. Sampatrao L PinjarePas encore d'évaluation

- A - C L P - Application Domain: Multi-Media Systems, Recognition, Mining, SynthesisDocument4 pagesA - C L P - Application Domain: Multi-Media Systems, Recognition, Mining, SynthesisDr. Sampatrao L PinjarePas encore d'évaluation

- Lock Ating: Prof. Kaushik Roy at Purdue UnivDocument8 pagesLock Ating: Prof. Kaushik Roy at Purdue UnivDr. Sampatrao L PinjarePas encore d'évaluation

- R D R C C R: Educing THE Ynamic Ange OF Omputation AND Omplexity EductionDocument6 pagesR D R C C R: Educing THE Ynamic Ange OF Omputation AND Omplexity EductionDr. Sampatrao L PinjarePas encore d'évaluation

- A Bit-Serial Adder Using Partially Reversible LogicDocument9 pagesA Bit-Serial Adder Using Partially Reversible LogicDr. Sampatrao L PinjarePas encore d'évaluation

- Ariable Upply Oltage: Prof. Kaushik Roy at Purdue UnivDocument7 pagesAriable Upply Oltage: Prof. Kaushik Roy at Purdue UnivDr. Sampatrao L PinjarePas encore d'évaluation

- L - P Vlsi S P: L C D: OW Ower Ignal Rocessing OW Omplexity EsignDocument8 pagesL - P Vlsi S P: L C D: OW Ower Ignal Rocessing OW Omplexity EsignDr. Sampatrao L PinjarePas encore d'évaluation

- Ogic Tyle: Prof. Kaushik Roy at Purdue UnivDocument10 pagesOgic Tyle: Prof. Kaushik Roy at Purdue UnivDr. Sampatrao L PinjarePas encore d'évaluation

- S - C P C: Hort Ircuit Ower OnsumptionDocument7 pagesS - C P C: Hort Ircuit Ower OnsumptionDr. Sampatrao L PinjarePas encore d'évaluation

- E - C RCC: B I E R: Nergy Onsumption IN Ircuits A Rief Ntroduction TO Nergy EcoveryDocument8 pagesE - C RCC: B I E R: Nergy Onsumption IN Ircuits A Rief Ntroduction TO Nergy EcoveryDr. Sampatrao L PinjarePas encore d'évaluation

- Estimation of Average Number of Transitions: Source: IntelDocument2 pagesEstimation of Average Number of Transitions: Source: IntelDr. Sampatrao L PinjarePas encore d'évaluation

- MicrothrusterDocument1 pageMicrothrusterDr. Sampatrao L PinjarePas encore d'évaluation

- VLSI Implementation of Artificial Neural NetworkDocument26 pagesVLSI Implementation of Artificial Neural NetworkDr. Sampatrao L PinjarePas encore d'évaluation

- Design of CMOS Low Dropout Voltage RegulatorDocument32 pagesDesign of CMOS Low Dropout Voltage RegulatorDr. Sampatrao L PinjarePas encore d'évaluation

- Icp-Oes Plasma Quant Pq9000Document16 pagesIcp-Oes Plasma Quant Pq9000Mari Sherlin Salisi-ChuaPas encore d'évaluation

- DGT Quick Setup 07.03 13.03 ENDocument1 pageDGT Quick Setup 07.03 13.03 ENseabellPas encore d'évaluation

- Stabila 196-2 Elettronica ENDocument22 pagesStabila 196-2 Elettronica ENJohn WalesPas encore d'évaluation

- M-550 Power Service Manual: Model No: 3399 Drawring No: Customer: Model No: M-550 Power Rev, DateDocument65 pagesM-550 Power Service Manual: Model No: 3399 Drawring No: Customer: Model No: M-550 Power Rev, Datealbinopu2liuPas encore d'évaluation

- DIAL's RequirementsDocument57 pagesDIAL's RequirementsShaikh Saeed AlamPas encore d'évaluation

- DVR5104EDocument4 pagesDVR5104ETTB VisionPas encore d'évaluation

- DP LAN Others 13115 DriversDocument2 284 pagesDP LAN Others 13115 DriversSyed AliPas encore d'évaluation

- Tuncuk Et Al., 2012 PDFDocument10 pagesTuncuk Et Al., 2012 PDFlaguna028Pas encore d'évaluation

- DPP - (5) 11th (P) IOC (E) - Ans PDFDocument2 pagesDPP - (5) 11th (P) IOC (E) - Ans PDFRishabh GuptaPas encore d'évaluation

- 63230-500-282A1 PM8 Install GuideDocument8 pages63230-500-282A1 PM8 Install GuideJohan M. CcoriPas encore d'évaluation

- DSR Electrical 2012Document60 pagesDSR Electrical 2012vijay_raina31140% (1)

- ClimateMaster Troubleshooting Info Revised 10-04-11Document5 pagesClimateMaster Troubleshooting Info Revised 10-04-11Daniel VeraPas encore d'évaluation

- Calibration of Linear Displacement Sensor Systems Used To Measure MicromotionDocument4 pagesCalibration of Linear Displacement Sensor Systems Used To Measure MicromotionAhmad Zubair RasulyPas encore d'évaluation

- Programación de Control de Temperatura OMRON, Modelo E5CC-E5ECDocument336 pagesProgramación de Control de Temperatura OMRON, Modelo E5CC-E5ECReinaldo Cordero100% (1)

- Zeeman EffectDocument5 pagesZeeman Effectjsebas635Pas encore d'évaluation

- Prac. Summer 2014Document19 pagesPrac. Summer 2014Praful KakdePas encore d'évaluation

- FDAS Technical Data SheetsDocument6 pagesFDAS Technical Data SheetsPhel FloresPas encore d'évaluation

- 6EP14362BA10 Datasheet enDocument4 pages6EP14362BA10 Datasheet enTio SPas encore d'évaluation

- Panasonic SA-AK960 Mini ComboDocument121 pagesPanasonic SA-AK960 Mini Comboppstone100% (3)

- Leggett (2008) - Realism and The Physical WorldDocument6 pagesLeggett (2008) - Realism and The Physical WorldsajadonscribdPas encore d'évaluation

- Pizzato - Elettrica FS2996D024 F3 Datasheet PDFDocument35 pagesPizzato - Elettrica FS2996D024 F3 Datasheet PDFEwerton SoaresPas encore d'évaluation

- EE100 User Manual V 1.1Document21 pagesEE100 User Manual V 1.1PujiyonoPas encore d'évaluation

- Craftsman 98023 40V 12V Lithium-Ion Cordless ChainsawDocument6 pagesCraftsman 98023 40V 12V Lithium-Ion Cordless ChainsawJoe ZhaoPas encore d'évaluation

- PC2000-8 Spec SheetDocument20 pagesPC2000-8 Spec SheetNeeraj ChauhanPas encore d'évaluation

- Toshiba e Studio163 203 165 205 Printer Brochure PDFDocument2 pagesToshiba e Studio163 203 165 205 Printer Brochure PDFMohamed ZayedPas encore d'évaluation