Académique Documents

Professionnel Documents

Culture Documents

Guia de Elec. III Lab #1

Transféré par

mohamedTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Guia de Elec. III Lab #1

Transféré par

mohamedDroits d'auteur :

Formats disponibles

PRACTICAS DEL LABORATORIO

DE ELECTRONICA III

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

LABORATORIO DE ELECTRÓNICA III

PRÁCTICA Nº 1

“AMPLIFICADOR MULTIETAPA CON ETAPA DE POTENCIA”

OBJETIVOS GENERAL:

1. Diseñar un amplificador multietapa

OBJETIVOS ESPECÍFICO:

1. Implementar y evaluar un amplificador multietapa

2. Acoplar un amplificador de potencia en la salida del multietapa.

ANÁLISIS PRELIMINAR:

Estudiar los siguientes temas:

Características de un Amplificador Inversor y no Inversor.

Circuito Multietapa

Diseño de un Circuito Amplificador Discreto Multietapa

Modelamiento y características de Amplificadores de Potencia.

PLANIFICACIÓN:

EQUIPO NECESARIO

Computador con últimas especificaciones

Herramienta de simulación ORCAD PSPICE 10.3

1 Protoboard

1 Fuente de voltaje Regulada (0-32V / 0-3A)

1 Generador de señal con su respectiva punta de prueba (0-10 Mhz)

1 Osciloscopio con sus respectivas puntas de prueba (0-200Mhz)

1 Multímetro Digital (500V / 10 A /10 Mhz )

Pinzas, Pelacables, cables.

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

COMPONENTES NECESARIOS

Resistencias de ¼ Watt

Capacitores a 50 V

Transistores BJT

ECUACIONES BÁSICAS

EXPRESION MATEMATICA

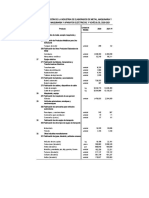

Etapa Rin Rout Av Ai

EC Rb//rπ ≈ rπ RC//ro -gm(ro//Rb//RL) - gmRin ≈ -βo

_ βo + (RC//RL) _ βo(Rb+Rib) ≈ -βo

EC-RE Rb//[rπ + (1+βo)Re] RC rπ + (1+βo)Re Rb i

rπ + (Rb//Rg) (1+βo)REM ≈ 1 (1+βo)(Rb+Rib)

CC Rb//[rπ + (1+βo)REM] 1+βo rπ + (1+βo)REM k Rb

rπ ≈ 1 βo ≈ α

BC 1+βo gm Rc gm(RC//RL) 1+βo gm

GV =AV Rin i

(Rg+Rin)

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

AMPLIFICADOR MULTI-ETAPA

PROCEDIMIENTO

Para la construcción de un circuito amplificador, que genere una ganancia superior a 100,

implica la necesidad de construcción más de una etapa; un solo amplificador de abundante

ganancia es inestable, Motivo suficiente para haber tomado dicha decisión.

Un método muy común es la construcción varias etapas en cascada; dos etapas inversoras

encargadas de generar la ganancia deseada, una tercera etapa con la finalidad de obtener

una impedancia pequeña a la salida y una etapa de potencia clase AB, este etapa es un

compromiso entre la eficacia de los amplificadores clase B y la eliminación de la distorsión

de cruce de los diseños en clase A. En este trabajo se detallan los cálculos hechos para el

diseño que se representa como sigue en la figura 1:

Diagramas de Bloques

Figura 1.

1. DISEÑO DEL AMPLIFICADOR MULTIETAPA:

Las características que fueron especificadas para el multietapa son:

Señal de entrada: Vin = 24 mv

Ganancia total de tensión: Av > 100

Impedancia de entrada: Zin > 10 KΩ

Resistencia de carga: RL = 100 Ω

Rango de frecuencia : 20 Hz a 30 kHz

Tensión sinusoidal de salida: Vop = 2.4 Vp

Acople capacitivo

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

Diseño de la etapa 3:

Las características para esta etapa son las siguientes:

Ganancia de la etapa: Av ≅ 1

Voltaje base-emisor : VBE = 0.7v

Beta del dispositivo: ß = 250

Fuente DC dual: VCC ± 12v

La tercera etapa debe proporcinar una impedancia de salida baja, su ganancia no es

importante porque es el trabajo de las dos etapas que la anteceden. El esquemático de esta

etapa se puede apreciar en la figura 2:

Etapa 3 Colector Común

Figura 2

Se adopta que por máxima transferencia de potencia:

𝑹𝟏𝟏 = 𝑹𝑳 = 𝟏𝟎𝟎Ω

Teniendo muy en cuenta la consideración de que se debe estar centrado en la recta AC, que

tiende precisamente a centrar el punto de operación:

𝟐𝑽𝑪𝑪

𝑰𝒄𝒒 = 𝑹𝒂𝒄 = 𝑹𝟏𝟏//𝑹𝑳 𝑹𝒅𝒄 = 𝑹𝟏𝟏 𝑰𝒄𝒒 ≅ 𝟏𝟔𝟎𝒎𝑨

𝑹𝒂𝒄 + 𝑹𝒅𝒄

El diseño continúa con el cálculo de la resistencia de base RB, la cual posteriormente nos

permitirá calcular el valor de R9 y R10. RB es el resultante del paralelo entre R1 y R2.

𝑹𝑩 = 𝟏𝟎%(𝜷 + 𝟏)𝑹𝑬 𝑹𝑩 = 𝟐. 𝟓𝒌Ω

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

Estamos en capacidad de hallar el VBB o sea la caída de tensión sobre R2. La hallamos así:

𝑹𝒃

𝑽𝑩𝑩 = ( + 𝑹𝒆) 𝑰𝒄𝒒 + 𝑽𝑩𝑬 + 𝑽𝑬𝑬

𝜷+𝟏

𝑽𝑩𝑩 = 𝟔. 𝟐𝟗𝒗

Finalmente hallamos los valores de R9 y R10 de la siguiente manera:

𝟐𝑽𝑪𝑪

𝑹𝟏𝟎 = ∗ 𝑹𝑩 𝑹𝟏𝟎 ≅ 𝟗. 𝟓 𝒌Ω

𝑽𝑩𝑩

𝑹𝑩

𝑹𝟗 = 𝑹𝟗 ≅ 𝟑. 𝟒 𝒌Ω

𝑽𝑩𝑩

𝟏 − 𝟐𝑽𝑪𝑪

Para el cálculo de la ganancia de tensión y de la impedancia de entrada, se realiza el modelo

del circuito:

Pequeña Señal de la Etapa 3

Figura 5

Para la ganancia de tensión:

𝑽𝒐 (𝟏 + 𝜷). 𝑹𝟏𝟏. 𝑰𝒃

𝑨𝒗𝟑 = 𝑨𝒗𝟑 =

𝑽𝒔 [𝜷𝒓𝒆 + (𝟏 + 𝜷). 𝑹𝟏𝟏]. 𝑰𝒃

𝑨𝒗𝟑 ≅ 𝟏

Para la impedancia de entrada:

𝒁𝒊𝒏𝟑 = (𝑹𝟗//𝑹𝟏𝟎)//[𝜷𝒓𝒆 + (𝟏 + 𝜷). 𝑹𝟏𝟏]

𝑽𝒕

𝒓𝒆′ = 𝒁𝒊𝒏𝟑 ≅ 𝟐. 𝟑 𝒌Ω

𝑰𝒄𝒒

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

Diseño de la etapa 2:

Las características para esta etapa son las siguientes:

Ganancia de la etapa: Av = 12

Voltaje base-emisor : VBE = 0.7v

Beta del dispositivo: ß = 250

Fuente DC: VCC = 12v

El esquemático de esta etapa se puede apreciar en la figura 4:

Etapa 2 Emisor Comun

Figura 4

Por máxima transferencia de potencia:

𝑹𝟕 = 𝑹𝑳 𝑹𝑳 = 𝒁𝒊𝒏𝟑 𝑹𝟕 = 𝟐. 𝟑 𝒌Ω

Se procede a trabajar con la ecuación de la Av de esta etapa, para ello se dibuja el modelo

de pequeña señal:

Pequeña Señal de la Etapa 2

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

Figura 5

𝑽𝒔

∗ 𝑽𝒔 = 𝑰𝒃. 𝜷𝒓𝒆 + 𝑰𝒃(𝜷 + 𝟏)𝑹𝟖 𝑰𝒃 =

𝜷𝒓𝒆 + (𝜷 + 𝟏)𝑹𝟖

∗ 𝑽𝒐 = −𝜷𝑰𝒃. 𝑹𝟕//𝒁𝒊𝒏𝟑

𝜷. 𝑹𝟕//𝒁𝒊𝒏𝟑

𝑨𝒗 = − 𝑨𝒗 = −𝟏𝟐

𝑽𝒕

𝜷 𝑰𝒄 + (𝜷 + 𝟏)𝑹𝟖

En la ecuación se definen dos incógnitas: Ic y R8.

Partiendo de la figura 4:

𝑽𝑪𝑪 − 𝑽𝑪𝑬𝒔𝒂𝒕

𝑽𝑪𝑪 − 𝑰𝒄𝑹𝟕 − 𝑽𝑪𝑬𝒔𝒂𝒕 − 𝑰𝒆𝑹𝟖 = 𝟎 𝑰𝒄 = 𝑽𝑪𝑬𝒔𝒂𝒕 = 𝟎. 𝟐𝒗

𝑹𝟕 + 𝑹𝟖

También se definen dos incógnitas: Ic y R8. Pero remplazando Ic en la ecuación de la

ganancia y despejando los valores conocidos:

𝑹𝟖 ≅ 𝟗𝟎 Ω

Para el valor de Ic, se opta por:

𝑽𝑪𝑪

𝑰𝒄𝒒 = 𝑹𝒂𝒄 = 𝑹𝟕//𝒁𝒊𝒏𝟑 + 𝑹𝟖 𝑹𝒅𝒄 = 𝑹𝟕 + 𝑹𝟖

𝑹𝒂𝒄 + 𝑹𝒅𝒄

𝑰𝒄𝒒 ≅ 𝟑. 𝟑 𝒎𝑨

Partiendo nuevamente de la figura 4:

𝑽𝑩𝑬 + 𝑰𝒄. 𝑹𝟖

∗ 𝑰𝒑. 𝑹𝟔 = 𝑽𝑩𝑬 + 𝑰𝒄. 𝑹𝟖 𝑹𝟔 =

𝑰𝒑

𝑰𝒄

𝑰𝒑 ≥ 𝟏𝟎𝑰𝒃 = 𝟏𝟎 𝑰𝒑 ≥ 𝟏𝟑𝟔 µ𝑨 𝑹𝟔 ≅ 𝟕. 𝟒 𝒌Ω

𝜷

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

𝑽𝒄𝒄 − 𝑰𝒑. 𝑹𝟔

∗ 𝑽𝒄𝒄 = 𝑰𝒑(𝑹𝟓 + 𝑹𝟔) 𝑹𝟓 = 𝑹𝟓 ≅ 𝟖𝟏 𝒌Ω

𝑰𝒑

Para la impedancia de entrada:

𝒁𝒊𝒏𝟐 = (𝑹𝟓//𝑹𝟔)//[𝜷𝒓𝒆 + (𝟏 + 𝜷). 𝑹𝟖]

𝒁𝒊𝒏𝟐 ≅ 𝟓. 𝟑𝟐 𝒌Ω

Diseño de la etapa 1:

Las características para esta etapa son las siguientes:

Ganancia de la etapa: Av = 12

Voltaje base-emisor : VBE = 0.7v

Beta del dispositivo: ß = 250

Fuente DC: VCC = 12v

El esquemático de esta etapa se puede apreciar en la figura 6:

Etapa 1 Emisor Comun

Figura 6

Por máxima transferencia de potencia:

𝑹𝟑 = 𝑹𝑳 𝑹𝑳 = 𝒁𝒊𝒏𝟐 𝑹𝟑 = 𝟓. 𝟑𝟐𝒌Ω

Se procede a trabajar con la ecuación de la Av de esta etapa, para ello se dibuja el modelo

de pequeña señal:

Pequeña Señal de la Etapa 1

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

Figura 7

𝑽𝒔

∗ 𝑽𝒔 = 𝑰𝒃. 𝜷𝒓𝒆 + 𝑰𝒃(𝜷 + 𝟏)𝑹𝟒 𝑰𝒃 =

𝜷𝒓𝒆 + (𝜷 + 𝟏)𝑹𝟒

∗ 𝑽𝒐 = −𝜷𝑰𝒃. 𝑹𝟑//𝒁𝒊𝒏𝟐

𝜷. 𝑹𝟑//𝒁𝒊𝒏𝟐

𝑨𝒗 = − 𝑨𝒗 = −𝟗

𝑽𝒕

𝜷 𝑰𝒄 + (𝜷 + 𝟏)𝑹𝟒

En la ecuación se definen dos incógnitas: Ic y R4.

Partiendo de la figura 6:

𝑽𝑪𝑪 − 𝑽𝑪𝑬𝒔𝒂𝒕

𝑽𝑪𝑪 − 𝑰𝒄𝑹𝟑 − 𝑽𝑪𝑬𝒔𝒂𝒕 − 𝑰𝒆𝑹𝟒 = 𝟎 𝑰𝒄 = 𝑽𝑪𝑬𝒔𝒂𝒕 = 𝟎. 𝟐𝒗

𝑹𝟑 + 𝑹𝟒

También se definen dos incógnitas: Ic y R4. Pero remplazando Ic en la ecuación de la

ganancia y despejando los valores conocidos:

𝑹𝟒 ≅ 𝟐𝟖𝟕 Ω

Para el valor de Ic, se opta por:

𝑽𝑪𝑪

𝑰𝒄𝒒 = 𝑹𝒂𝒄 = 𝑹𝟑//𝒁𝒊𝒏𝟐 + 𝑹𝟒 𝑹𝒅𝒄 = 𝑹𝟑 + 𝑹𝟒

𝑹𝒂𝒄 + 𝑹𝒅𝒄

𝑰𝒄𝒒 ≅ 𝟏. 𝟑𝟗𝟔 𝒎𝑨

Partiendo nuevamente de la figura 4:

𝑽𝑩𝑬 + 𝑰𝒄. 𝑹𝟒

∗ 𝑰𝒑. 𝑹𝟐 = 𝑽𝑩𝑬 + 𝑰𝒄. 𝑹𝟒 𝑹𝟐 =

𝑰𝒑

𝑰𝒄

𝑰𝒑 ≥ 𝟏𝟎𝑰𝒃 = 𝟏𝟎 𝑰𝒑 ≥ 𝟓𝟓. 𝟖𝟓 µ𝑨 𝑹𝟐 ≅ 𝟏𝟗. 𝟕𝟎𝒌Ω

𝜷

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

𝑽𝒄𝒄 − 𝑰𝒑. 𝑹𝟐

∗ 𝑽𝒄𝒄 = 𝑰𝒑(𝑹𝟏 + 𝑹𝟐) 𝑹𝟏 = 𝑹𝟏 ≅ 𝟐𝟏𝟒. 𝟖 𝒌Ω

𝑰𝒑

Para la impedancia de entrada:

𝒁𝒊𝒏𝟏 = (𝑹𝟏//𝑹𝟐)//[𝜷𝒓𝒆 + (𝟏 + 𝜷). 𝑹𝟒]

𝒁𝒊𝒏𝟏 ≅ 𝟏𝟒. 𝟓 𝒌Ω

Capacitores de acople:

En el cálculo de cada condensador debe tenerse en cuenta los siguientes aspectos:

Al condensador que ve la menor impedancia se le asigna la frecuencia baja

especificada. En caso de este diseño, C2 ve la menor impedancia, por lo tanto:

𝟏

𝑪𝟐 ≥ 𝑠𝑒 𝑎𝑑𝑜𝑝𝑡𝑎; 𝑪𝒔 = 𝟑. 𝟓 µ𝐟

𝟐𝝅. 𝒁𝒊𝒏𝟑. 𝒇𝒎𝒊𝒏

Al siguiente que ve una impedancia baja, se le asigna la frecuencia, pero una década

abajo. Para el caso de este diseño, se le asigna a C1 una frecuencia de 2Hz. Su

calculo es como sigue:

𝟏

𝑪𝟏 ≥ 𝑠𝑒 𝑎𝑑𝑜𝑝𝑡𝑎; 𝑪𝒔 = 𝟏𝟓 µ𝐟

𝒇𝒎𝒊𝒏

𝟐𝝅. 𝒁𝒊𝒏𝟐. 𝟏𝟎

Al capacitor que falta por calcular se le asigna la frecuencia baja pero 2 décadas

abajo, es decir que fL =0.2Hz:

𝟏

𝑪𝒔 ≥ 𝑠𝑒 𝑎𝑑𝑜𝑝𝑡𝑎; 𝑪𝒔 = 𝟓𝟓 µ𝐟

𝒇𝒎𝒊𝒏

𝟐𝝅. 𝒁𝒊𝒏𝟏. 𝟏𝟎𝟎

{_

Con esto concluye el diseño de preamplificador.

Circuito Total

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

Figura 8

SIMULACIÓN CON ORCAD PSPICE

OBTENCION DEL VOLTAJE DE SALIDA

1. Se crea el nuevo Proyecto:

New / Project

Analog or Mixed A/D / OK

Create Pspice Project / OK

2. Se implementa el circuito de la Figura.

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

3. Se elige un nuevo perfil de simulación

New simulation profile / Create

4. Editar los parámetros de simulación

Analysis type: Time Domain (Transient)

Options: General settings

Run to Time: 200µs

Start saving data after: 0.1µs

Transient options

Maximum step size: 1µs

Output File Options

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

5. Ubicamos un marcador de voltaje, Voltage Marker, en el emisor del transistor.

6. Corremos el circuito con Pspice / Run

Voltaje de salida

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

OBTENCION DE LA GANANCIA

1. Pspice / Edit simulation Setting

2. Editar los parámetros de simulación

Analysis type: AC Sweep/Settings.

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

AC Sweep Type: Logarithmic.

Start Frequency: 0.1

End Frequency: 10G

Points/Decade: 100

Output File Options

3. Pspice / Run

Ganancia del Multietapa

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

“IMPLEMENTACION DE LA ETAPA AMPLIFICADORA”

Se opta por el acoplamiento de una etapa amplificadora de potencia clase AB, como ya se

ha dicho anteriormente, el esquemático de esta etapa se puede apreciar en la figura 7:

Etapa de potencia Clase AB

Figura 9

Circuito Multietapa con Amplificador de Potencia Clase AB

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

Voltaje de salida

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

Ganancia Total

EJECUCIÓN:

1. Diseñe un amplificador multi-etapa discreto con las siguientes características:

a) Ganancia de voltaje mayor o igual a 300 ± 5%. (Medido a 20 kHz).

b) Manejo de señal a la salida: 15 V pico a pico. (Medido a 20 kHz).

c) Resistencia de entrada mayor o igual 150KΩ.

d) Resistencia de salida igual a 20Ω.

e) Punto terminal de -3dB de baja frecuencia menor o igual a 40Hz (fL≤40Hz).

f) Punto terminal de -3dB de alta frecuencia mayor o igual 50Khz (fh≥50KHz).

g) Respuesta en la banda de paso máximamente plana.

h) El amplificador debe estar compensado con respecto a variaciones de

temperatura.

i) Fuentes de alimentación de ± 12v. (máximo)

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

2. Elabore, siga y desarrolle, la simulación que demuestre que se cumplen con cada uno de

las especificaciones anteriores. Deberá entregarse un archivo para cada uno de los ítems

anteriores (Las simulaciones solo se aceptan en ORCAD).

3. Realice un proyecto de diseño que incluya:

a) Incluya los cálculos realizados para cumplir los parámetros del punto No 1

b) Tabla con los valores esperados para los parámetros exigidos.

c) Circuito diseñado con valores de voltajes y corrientes de polarización.

d) Procedimiento para medir las características solicitadas en el punto N° 1.

e) Hojas de especificaciones de los dispositivos semiconductores utilizados,

justificando su escogencia.

PROFUNDIZACIÓN:

El circuito de la figura 1. Corresponde a una casada de amplificadores BJT de tres etapas,

acopladas en cd, fabricados a partir de dispositivos discretos.

a. Analice el circuito multietapa que se presenta y determine la excursión máxima para el

voltaje de salida.

b. Estime los valores de polarización, la ganancia aproximada en pequeña señal, además

de la ROUT y RIN.

Figura 1. Amplificador en cascada

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

CONCLUSIONES:

ING. JOSE ALEJO RANGEL ROLÓN

josealejor@ufps.edu.co

Vous aimerez peut-être aussi

- Curso de Tierra Cessna CaravanDocument185 pagesCurso de Tierra Cessna Caravanivargasv100% (7)

- Catalogo Ekoline PDF OkDocument186 pagesCatalogo Ekoline PDF OkJonathan HerreraPas encore d'évaluation

- Samsung Curso Inverter QDocument3 pagesSamsung Curso Inverter QFrederman RodasPas encore d'évaluation

- Manual Johansson 6605Document24 pagesManual Johansson 6605Javier Ruiz Perea100% (1)

- Manual Cheetah XI (Traducción)Document158 pagesManual Cheetah XI (Traducción)Jose Antonio Mio83% (6)

- Inspeccion BarredoraDocument13 pagesInspeccion Barredoraalexis pozo contrerasPas encore d'évaluation

- Desarme y Ensamble de Una Bomba Centrifuga en VoladizoDocument10 pagesDesarme y Ensamble de Una Bomba Centrifuga en VoladizoChristian daniel ParsonsPas encore d'évaluation

- Lab3 Ie S12018 PDFDocument15 pagesLab3 Ie S12018 PDFmohamedPas encore d'évaluation

- Lab1 Ie S12018Document20 pagesLab1 Ie S12018mohamedPas encore d'évaluation

- Lab2 Ie S12018 PDFDocument3 pagesLab2 Ie S12018 PDFmohamedPas encore d'évaluation

- Laboratorio 1 PDFDocument20 pagesLaboratorio 1 PDFmohamedPas encore d'évaluation

- Lab5 Ie S12018 PDFDocument4 pagesLab5 Ie S12018 PDFmohamedPas encore d'évaluation

- Lab4 PDFDocument4 pagesLab4 PDFmohamedPas encore d'évaluation

- Lab1 IEDocument13 pagesLab1 IEmohamedPas encore d'évaluation

- TABLA DE SENSORES Grupo C-01 PDFDocument14 pagesTABLA DE SENSORES Grupo C-01 PDFmohamedPas encore d'évaluation

- Paper Lab 3 IE PDFDocument5 pagesPaper Lab 3 IE PDFmohamedPas encore d'évaluation

- Taller1 IE 2018 PDFDocument4 pagesTaller1 IE 2018 PDFmohamedPas encore d'évaluation

- ResueltosDocument10 pagesResueltosChavi Almeida100% (1)

- Tiendas Virtuales y Chequeo de Lab PDFDocument2 pagesTiendas Virtuales y Chequeo de Lab PDFmohamedPas encore d'évaluation

- Thermocouple ExampleDocument3 pagesThermocouple ExampleelprofesorpanPas encore d'évaluation

- Valvulas SB1 Info TecDocument2 pagesValvulas SB1 Info TecJulian TagliariniPas encore d'évaluation

- Despiece 0445020056Document3 pagesDespiece 0445020056Andy Anderson Limachi PeraltaPas encore d'évaluation

- Check List VerDocument39 pagesCheck List VerJavier LorenzoPas encore d'évaluation

- Dupline Charla UniversidadDocument46 pagesDupline Charla UniversidadSope Urrutia100% (1)

- Informe PericialDocument25 pagesInforme PericialdanteyanayacoPas encore d'évaluation

- ACT3 MPA 3arDocument10 pagesACT3 MPA 3arAnghel FariasPas encore d'évaluation

- Monografía ElectronicaDocument29 pagesMonografía ElectronicaFrank ArandaPas encore d'évaluation

- Cestek 1Document16 pagesCestek 1Rodolfo CardenasPas encore d'évaluation

- 16.12 Producción de La Industria de Elaborados de Metal, Maquinaria Y Equipo, Maquinaria Y Aparatos Eléctricos, Y Vehículos, 2020-2021Document2 pages16.12 Producción de La Industria de Elaborados de Metal, Maquinaria Y Equipo, Maquinaria Y Aparatos Eléctricos, Y Vehículos, 2020-2021Sharon NatividadPas encore d'évaluation

- 3 ES-PT-103-FV - Escaleras Dielétricas Extensión 3C PDFDocument1 page3 ES-PT-103-FV - Escaleras Dielétricas Extensión 3C PDFJhon Jairo ValenciaPas encore d'évaluation

- Manual Reconectador Schneider PDFDocument109 pagesManual Reconectador Schneider PDFEnrique TorrezPas encore d'évaluation

- Regulador Leroy SomerDocument16 pagesRegulador Leroy SomerCarlos ZugastiPas encore d'évaluation

- Regulador de Potencia Por Triac (INFORME) ALBERTO N.Document17 pagesRegulador de Potencia Por Triac (INFORME) ALBERTO N.albertoPas encore d'évaluation

- SWAN QUAD - En.esDocument2 pagesSWAN QUAD - En.esisrael peñaPas encore d'évaluation

- Artículos de Mecánica PopularDocument10 pagesArtículos de Mecánica PopularLobsang Rampa100% (1)

- CO-EST-P117-SSOMA-008 Uso de Herramientas Man. y Eqp. Rot. de Poder VR.01Document19 pagesCO-EST-P117-SSOMA-008 Uso de Herramientas Man. y Eqp. Rot. de Poder VR.01Luis A. Castillo PerezPas encore d'évaluation

- Transcord SRL Volvo: Repuestos Y Servicios N/P Frecuencia (Horas) Fecha Motor KM X X X X XDocument1 pageTranscord SRL Volvo: Repuestos Y Servicios N/P Frecuencia (Horas) Fecha Motor KM X X X X XKEVIN ALEXIS HINOSTROZA CARDENASPas encore d'évaluation

- Sistemas OperativosDocument33 pagesSistemas OperativosD.H. ValdemarPas encore d'évaluation

- Informe 08 AnalógicaDocument8 pagesInforme 08 AnalógicaEfrain Ismael Rolando JaramilloPas encore d'évaluation

- Tecnología 09 Guía 3 Placa BaseDocument7 pagesTecnología 09 Guía 3 Placa BaseSEBASTIAN VALDES VALEROPas encore d'évaluation

- Control Tarjeta JMG - ENG 1.1 Titan 1800Document26 pagesControl Tarjeta JMG - ENG 1.1 Titan 1800daniel100% (1)

- Accesorios DusterDocument35 pagesAccesorios Dustereduardo jose oyola cortesPas encore d'évaluation

- Practica No. 13 Avance y Retroceso Por Final de Carrera TemporizadoDocument5 pagesPractica No. 13 Avance y Retroceso Por Final de Carrera TemporizadoJanet FrutiksPas encore d'évaluation