Académique Documents

Professionnel Documents

Culture Documents

s3051 PDF

Transféré par

Robert VojakTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

s3051 PDF

Transféré par

Robert VojakDroits d'auteur :

Formats disponibles

®

DEVICE

SPECIFICATION

2.5 GBPS LIMITING AMPLIFIER S3051

2.5 GBPS LIMITING AMPLIFIER S3051

FEATURES GENERAL DESCRIPTION

• 2 GHz Bandwidth The S3051 limiting amplifier with its high gain and wide

• 32dB Gain bandwidth is ideal for use as a post amplifier in fiber

• Single +5V Power Supply optic receivers with data rates up to 2.5 Gbps. The

amplifier's gain is 32dB, and differential signals as

• Fully Differential Architecture

small as 12 mVp-p, can be amplified to 900 mVp-p.

• 16 pin Glass-Metal Package Figure 1 shows a typical system application.

APPLICATIONS

• SONET OC-48

• Fiber Optic Data Links

• High-Speed FM Limiting Amplifier

Figure 1. System Block Diagram

CBYP

V+REF

VCC

CIN

OUT+ DIN+ DOUT+

S3051

INPUT CIN

OUT– DIN- DOUT–

CBYP

V–REF

July 14, 1999 / Revision B 1

S3051 2.5 GBPS LIMITING AMPLIFIER

DETAILED DESCRIPTION

The S3051 is an integrated limiting amplifier in- The referred wideband input noise (160 µVrms) al-

tended for high-frequency fiber-optic applications. lows for a less than 1E-9 Bit Error Rate for inputs

The circuit connects to typical transimpedance am- down to 2 mVp-p.

plifiers found within a fiber-optic link. The linear

The S3051 is designed to allow adjustment of the

signal output from a transimpedance amplifier can

DC offset between the DIN+ and DIN– inputs. V+REF

contain significant amounts of noise, and may vary

can be used as a reference from which the required

in amplitude over time. The S3051 limiting amplifier

offset can be subtracted to set the DC bias level at

quantizes the signal, and outputs a voltage limited

DIN–. Similarly, V–REF can be used to set the DC

waveform over a 38 dB input dynamic range.

bias level at DIN+. (See Application Information).

At low signal levels, below 12 mVp-p, the circuit be-

If no adjustment is made to the input DC bias level,

haves as a linear amplifier. At higher levels the

two resistors can be connected in a negative feed-

device becomes a limiting amplifier.

back configuration in order to cancel any DC offset

at the input. This will minimize the pulse width distor-

tion. (See separate S3051 Limiting Amplifier

Application document.)

Figure 2. Functional Block Diagram

NC VCC(OB) GND(OB) GND(OB)

8 7 6 5

110pF

4

5kΩ GND(OB)

9 50Ω

V–REF

5kΩ

3

10 DOUT–

DIN–

11 GS1 GS2 OB

DIN+ 2

DOUT+

5kΩ

12 50Ω

V+REF

5kΩ 1

GND(OB)

110pF

13 14 15 16

VCC= +5V VCC(GS1,GS2) VCC(GS1,SS2) GND(GS1,GS2) GND(GS1,GS2)

NC ..... No Connect

2 July 14, 1999 / Revision B

2.5 GBPS LIMITING AMPLIFIER S3051

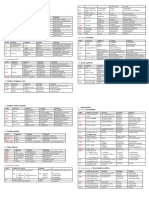

Table 1. S3051 Pin Assignment and Descriptions

Pin Name Level I/ O Pin # Description

DOUT+ Analog O 2 Positive data output.

DOUT– Analog O 3 Negative data output.

V–REF DC O 9 Data Negative reference. Requires up-close external bypassing

with a capacitor 0.047µF, or greater, matching the input coupling

capacitor. (See Figure 7.)

DIN– Analog I 10 Negative data input.

DIN+ Analog I 11 Positive data input.

V+REF DC O 12 Data Positive reference. Requires up-close external bypassing

with a capacitor 0.047µF, or greater, matching the input coupling

capacitor. (See Figure 7.)

VCC +5V S 7, 13, 14 Positive supply.

GND OV S 1, 4, 5, 6, Negative supply.

15, 16

NC 8 No connect.

July 14, 1999 / Revision B 3

S3051 2.5 GBPS LIMITING AMPLIFIER

Figure 3. S3051 16-Pin Glass-Metal Package

Thermal Management

Device Max Power Θja

S3051 750 mW 60˚ C/W

4 July 14, 1999 / Revision B

2.5 GBPS LIMITING AMPLIFIER S3051

Figure 4. S3051 Pinout (Top View)

GND

GND

VCC

VCC

16

15

14

13

GND 1 12 V+REF

S3051

DOUT+ 2 11 DIN+

TOP VIEW

DOUT– 3 16 Lead Flat Pack 10 DIN-

GND 4 9 V–REF

5

8

GND

GND

VCC

NC

July 14, 1999 / Revision B 5

S3051 2.5 GBPS LIMITING AMPLIFIER

Table 2. Recommended Operating Conditions

Parameter Min Typ Max Units

Ambient Temperature Under Bias –40 +85 ˚C

Junction Temperature Under Bias –10 +130 ˚C

Voltage on VCC with respect to GND 4.75 5.0 5.25 V

Table 3. Absolute Maximum Ratings

Parameter Min Typ Max Units

Storage Temperature Range –55 +175 ˚C

Processing Temperature +400 ˚C

Power Supply VCC with respect to GND 6. 0 V

Input Voltage (DIN+, DIN–) 6.0 V

VCC

DOUT+, DOUT– (with 50Ω load) 2.5 V

+0.3

ESD Sensitivity 1 Under 500 V

1. Human body model.

6 July 14, 1999 / Revision B

2.5 GBPS LIMITING AMPLIFIER S3051

Table 4. AC Electrical Characteristics

(VCC = 5V ± 5%, TA = –40˚C to +85˚C)

Parameters Description Min Typ Max Units Conditions

Peak-to-peak,

VID = Voltage Range

12 1000 mVp-p differential

(VIN+)-(VIN–) (Over which output is limited)

(See Figure 5.)

AD Differential Gain 32 48 dB VID = 8mVp-p

Differential Input Noise Input referred noise =

160 µV

RMS output noise/low

VN

frequency gain,

3.58 nV/√H z

7 kHz–2 GHz

Input is 2.488 Gbps

223-1 PRBS, VID =

PWD Pulse Width Distortion 0.1 UI

12mVp-p and

1000mVp-p note 1

tR, tF Output Edge Speed (20%–80%) 100 165 ps VID = 12mVp-p

Peak-to-peak,

VOD = differential, 50Ω line

Differential Output Voltage Swing 550 900 mVpp

(VOUT+)-(VOUT–) termination.

(See Figure 6.)

BWH Upper Small-Signal Bandwidth 1.6 2 GHz

Input coupling and

BWL Low Frequency Cut-off 2 kHz bypassing as in

Figure 7.

200 kHz–2 GHz, 50Ω

S11 Input Reflection Coefficient –15 dB

line termination.

200 kHz–2 GHz, 50Ω

S12 Isolation –45 dB

line termination.

200 kHz–2 GHz, 50Ω

S22 Output Reflection Coefficent –15 dB

line termination.

Note 1. Input offset calibrated out at VID = 15mV.

July 14, 1999 / Revision B 7

S3051 2.5 GBPS LIMITING AMPLIFIER

Table 5. DC Electrical Characteristics

(VCC = 5V ± 5%, TA = –40˚C to +85˚C)

Parameters Description Min Typ Max Units Comments

ICC Power Supply Current 75 100 mA

VDIN Input Bias Voltage VCC/2 V

Miximum Input (DIN+, DIN–) Offset VDIN

VOFFSET mV

Adjust ±300

VCC VCC

VOL Output LOW Voltage V

–0.95 –0.5

VCC

VOH Output HIGH Voltage VCC V

–0.5

Figure 5. Input Voltage

VIN+

5mV Min

500mV Max

VIN–

VID = [VIN+] - [VIN–]

10mV Min

0 1000mV Max

Figure 6. Output Voltage

VOUT+

300mV

Min

VOUT–

VOD = [VOUT+] - [VOUT–]

600mV

0 Min

8 July 14, 1999 / Revision B

2.5 GBPS LIMITING AMPLIFIER S3051

APPLICATIONS INFORMATION

Connecting to the Input of S3051

The equivalent input circuit of S3051 is shown in Figure 7. Both DC biasing and 50 Ohm input line termination

have been implemented internally.

Figure 7. S3051 Equivalent Input Circuit

VCC VCC

110pF

0.047 µF 5Ω V–REF

5 kΩ 5 kΩ

9

50Ω

0.047 µF DIN-

VIN–

10

0.047 µF DIN+

VIN+

11

5 kΩ 5 kΩ

50Ω

0.047 µF 5Ω V–REF

12

110pF

July 14, 1999 / Revision B 9

S3051 2.5 GBPS LIMITING AMPLIFIER

Connecting to the Output of S3051

The output of the S3051 does not require any external termination.

Figure 8. Output Termination

5V +5V

Zo=50Ω VCC–0.4V

DOUT+ 2 19

0.1µF

100Ω

DOUT- 3 18

Zo=50Ω 0.1µF VCC–0.4V

S3051 S3050

Adjusting Input DC Offset

The DC bias level at DIN– and DIN+ can be adjusted by inserting a Difference Amplifier function, as

shown in Figures 9 and 10.

Figure 9. Adjusting the DC Bias Level at DIN–

C BYP

V +REF

V IN+ DIN+ DOUT+

+

DIN- DOUT-

V OFFSET -

C BYP

V -REF

Figure 10. Adjusting the DC Bias Level at DIN+

C BYP

V +REF

+

DIN+ DOUT+

V OFFSET -

V IN- DIN- DOUT-

C BYP

V -REF

10 July 14, 1999 / Revision B

2.5 GBPS LIMITING AMPLIFIER S3051

Typical Operating Characteristics

Figure 11. Vcc Supply Current vs. Temperature

Figure 12. Frequency Response

July 14, 1999 / Revision B 11

S3051 2.5 GBPS LIMITING AMPLIFIER

Figure 13. Eye Pattern @VID = 12mV

Figure 14. Eye Pattern @VID = 1000mV

12 July 14, 1999 / Revision B

2.5 GBPS LIMITING AMPLIFIER S3051

Figure 15. Input Voltage vs. Output Voltage

July 14, 1999 / Revision B 13

S3051 2.5 GBPS LIMITING AMPLIFIER

Ordering Information

PREFIX DEVICE PACKAGE

S – Integrated Circuit 3051 A – 16 Lead Flat Pack

X XXXX X

Prefix Device Package

O 900

IS

1

D

CE

RT

E

IFI

Applied Micro Circuits Corporation • 6290 Sequence Dr., San Diego, CA 92121

Phone: (858) 450-9333 • (800) 755-2622 • Fax: (858) 450-9885

http://www.amcc.com

AMCC reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and

advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied

on is current.

AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey

any license under its patent rights nor the rights of others.

AMCC reserves the right to ship devices of higher grade in place of those of lower grade.

AMCC SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR

USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

AMCC is a registered trademark of Applied Micro Circuits Corporation.

Copyright ® 1999 Applied Micro Circuits Corporation

14 July 14, 1999 / Revision B

Vous aimerez peut-être aussi

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- Service Manual: Meat Mincer HR2725/00 HR2724/00Document2 pagesService Manual: Meat Mincer HR2725/00 HR2724/00Robert Vojak100% (1)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Philips 190tw8fb-00 PDFDocument90 pagesPhilips 190tw8fb-00 PDFsttecnico50% (2)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- TX-P42S20E TX-P42S20ES TX-P42S20L TX-PF42S20 TX-PR42S20: Plasma TelevisionDocument118 pagesTX-P42S20E TX-P42S20ES TX-P42S20L TX-PF42S20 TX-PR42S20: Plasma TelevisionRobert VojakPas encore d'évaluation

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (890)

- AK53 Service ManualDocument62 pagesAK53 Service Manualb6481136Pas encore d'évaluation

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- S 3051Document14 pagesS 3051Robert VojakPas encore d'évaluation

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- 32PHT4201 12Document80 pages32PHT4201 12georgedragosPas encore d'évaluation

- FA5695 FujiDocument21 pagesFA5695 FujiRobert VojakPas encore d'évaluation

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- LG 42LH50 LCD (EEFL-Ballast) TV Training ManualDocument77 pagesLG 42LH50 LCD (EEFL-Ballast) TV Training Manualdann222100% (1)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Tpn14.1e La 312278519598 141107Document253 pagesTpn14.1e La 312278519598 141107Robert VojakPas encore d'évaluation

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Pc817 DatasheetDocument5 pagesPc817 DatasheetprincebahariPas encore d'évaluation

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Sony Hcd-gx45 Rg440 Ver-1.2Document78 pagesSony Hcd-gx45 Rg440 Ver-1.2Mario GalvezPas encore d'évaluation

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- LG 42pj350 Training Manual (ET)Document132 pagesLG 42pj350 Training Manual (ET)RomelyGery Martinez89% (9)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- Service: LCD-TVDocument70 pagesService: LCD-TVRobert VojakPas encore d'évaluation

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- Laser Step by Step TutorialDocument11 pagesLaser Step by Step TutorialRobert VojakPas encore d'évaluation

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- Laser Step by Step TutorialDocument11 pagesLaser Step by Step TutorialRobert VojakPas encore d'évaluation

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Philips hts3020Document45 pagesPhilips hts3020Robert VojakPas encore d'évaluation

- Pioneer DV 300 KDocument69 pagesPioneer DV 300 KsvnnvsPas encore d'évaluation

- Data Warehousing: Modern Database ManagementDocument49 pagesData Warehousing: Modern Database ManagementNgọc TrâmPas encore d'évaluation

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- XS Power Batteries D Series InstructionsDocument2 pagesXS Power Batteries D Series InstructionsAutopiezas PanaPas encore d'évaluation

- Serial Port InterfacingDocument5 pagesSerial Port Interfacingyampire100% (1)

- Algebra Translating Algebraic Phrases 001Document2 pagesAlgebra Translating Algebraic Phrases 001crazyomnislash25% (4)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- 3BSE079234 - en 800xa 6.0 ReleasedDocument7 pages3BSE079234 - en 800xa 6.0 ReleasedFormat_CPas encore d'évaluation

- Home Automation Iot Bca Up (2ND SEMINAR PPT) RTDocument30 pagesHome Automation Iot Bca Up (2ND SEMINAR PPT) RTTejaswiniPas encore d'évaluation

- Design of Shaft Straightening MachineDocument58 pagesDesign of Shaft Straightening MachineChiragPhadkePas encore d'évaluation

- MITRES 6 002S08 Chapter2Document87 pagesMITRES 6 002S08 Chapter2shalvinPas encore d'évaluation

- ASTM D 1510 - 02 Carbon Black-Iodine Adsorption NumberDocument7 pagesASTM D 1510 - 02 Carbon Black-Iodine Adsorption Numberalin2005100% (1)

- DSD - Assignment 1 2018Document3 pagesDSD - Assignment 1 2018Naveen KumarPas encore d'évaluation

- HFM Currency CubeDocument2 pagesHFM Currency CubeSudhakar kPas encore d'évaluation

- MAINTAIN COOLANT LEVELDocument6 pagesMAINTAIN COOLANT LEVELAgustin BerriosPas encore d'évaluation

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- GenEd Mathematics LLL PDFDocument32 pagesGenEd Mathematics LLL PDFArmely NiedoPas encore d'évaluation

- Velocity profiles and incompressible flow field equationsDocument2 pagesVelocity profiles and incompressible flow field equationsAbdul ArifPas encore d'évaluation

- AMD OverDrive Utility 4.3.1.0698 Release NotesDocument1 pageAMD OverDrive Utility 4.3.1.0698 Release Notesbayu_gendeng666Pas encore d'évaluation

- PDF Solution Manual For Gas Turbine Theory 6th Edition Saravanamuttoo Rogers CompressDocument7 pagesPDF Solution Manual For Gas Turbine Theory 6th Edition Saravanamuttoo Rogers CompressErickson Brayner MarBerPas encore d'évaluation

- Proper Fluid Selection Maintenance For Heat Transfer TNTCFLUIDS PDFDocument12 pagesProper Fluid Selection Maintenance For Heat Transfer TNTCFLUIDS PDFAnonymous bHh1L1Pas encore d'évaluation

- QAF10A200S TheTimkenCompany 2DSalesDrawing 03 06 2023Document1 pageQAF10A200S TheTimkenCompany 2DSalesDrawing 03 06 2023LeroyPas encore d'évaluation

- Unit-3 BioinformaticsDocument15 pagesUnit-3 Bioinformaticsp vmuraliPas encore d'évaluation

- Singer Basic Tote Bag: Shopping ListDocument5 pagesSinger Basic Tote Bag: Shopping ListsacralPas encore d'évaluation

- Unit 3: Databases & SQL: Developed By: Ms. Nita Arora Kulachi Hansraj Model School Ashok ViharDocument18 pagesUnit 3: Databases & SQL: Developed By: Ms. Nita Arora Kulachi Hansraj Model School Ashok ViharAthira SomanPas encore d'évaluation

- Jaguar Land Rover Configuration Lifecycle Management WebDocument4 pagesJaguar Land Rover Configuration Lifecycle Management WebStar Nair Rock0% (1)

- Excel 2007 Lesson 7 QuizDocument5 pagesExcel 2007 Lesson 7 Quizdeep72Pas encore d'évaluation

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- DasibiOzoneMonitorManual 1008Document183 pagesDasibiOzoneMonitorManual 1008api-26966403100% (2)

- 4495 10088 1 PBDocument7 pages4495 10088 1 PBGeorgius Kent DiantoroPas encore d'évaluation

- ENGG1330 2N Computer Programming I (20-21 Semester 2) Assignment 1Document5 pagesENGG1330 2N Computer Programming I (20-21 Semester 2) Assignment 1Fizza JafferyPas encore d'évaluation

- PDS OperatorStationDocument7 pagesPDS OperatorStationMisael Castillo CamachoPas encore d'évaluation

- Affixation (Landscape)Document4 pagesAffixation (Landscape)difafalahudinPas encore d'évaluation

- Curtis CatalogDocument9 pagesCurtis CatalogtharngalPas encore d'évaluation

- AutoCAD Mechanical 2015 Overview Brochure - A4Document4 pagesAutoCAD Mechanical 2015 Overview Brochure - A4Raul ReynosoPas encore d'évaluation