Académique Documents

Professionnel Documents

Culture Documents

Spyglass-Cdc: Industry Most Comprehensive, Practical, and Powerful CDC Solution

Transféré par

RamakrishnaRao SoogooriTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Spyglass-Cdc: Industry Most Comprehensive, Practical, and Powerful CDC Solution

Transféré par

RamakrishnaRao SoogooriDroits d'auteur :

Formats disponibles

THINK

SpyGlass-CDC

Industry Most Comprehensive, Practical, THINK

and Powerful CDC Solution

Among the many verification challenges confronting system-on-chip (SoC) designers these days, clock

domain crossings (CDCs) rank near the top in difficulty. Todays SoCs have dozens or sometimes

even hundreds of clock domains, many of them difficult to verify using conventional simulation or

static timing analysis (STA). For these bugs to be detected in simulation, it requires long simulation

runs and a chance encounter and STA does not check for asynchronous clock domains. As a

consequence, CDCs have become a leading cause of design errors. Such errors can add significant

time and expense to the design-and-debug cycle, and may even find their way into silicon, necessitating

costly re-spins.

The Problem

The success of static CDC verification tools is synchronization mechanisms. Both can be difficult

determined by two critical measures--the time or impossible to accurately verify using simulation.

taken to signoff and the completeness of CDC And conventional static CDC analysis tools do

verification. Conventional CDC analysis tools too little and too much at the same time,

fall short in both areas. They generate large simultaneously overlooking real design errors

amounts of noise (false violations)--extending the and over-reporting large numbers of false

verification cycle--and provide poor coverage of violations. As a result the user is forced into an

complex CDC synchronization schemes. endless bug-hunting process, which often

discourages the designer and leaves real bugs

Two particularly troublesome CDC-related issues undetected.

involve FIFO- and handshake-based

The Atrenta Solution SpyGlass-CDC

Supports widest variety of synchronizers and Works without the manual effort to supplement

produces the least amount of false violations CDC testing with simulation vectors and writing

assertions

Automatically recognizes and formally verifies

complex handshake and FIFO synchronization Integrates with Atrenta SpyGlass capabilities

schemes targeted for RTL like constraints, constraints and

DFT

Formally verifies data stability

> Easy to ramp up and begin productive use

Automatically recognizes and formally verifies within half a day, even for non-experts

gray-code logic in re-convergent signals

> A structured methodology enables quick

adoption by engineers and constraints

optimized designs

SpyGlass-CDC Methodology

Provides easy-to-use and a comprehensive method Walks users through a series of recommended

for solving CDC problems at RTL to avoid costly steps to analyze CDC problems at block and

silicon re-spins chip level - the steps include design setup, setup

checks, design-unit integration chip level CDC

Provides methodology documentation and rule- verification, report review and CDC verification

sets as part of the product software installation sign-off

User-guided CDC sub-methodology flow results

in fewer but meaningful violations, thus saving

time for the RTL designer

The Atrenta Difference

SpyGlass-CDC

Separating True From False Violations The SpyGlass-CDC solution also formally verifies

to see if the following conditions can be violated

In order to isolate real clock domain crossing (Fig 2).

issues, it is necessary to detect various

Fig 2: Functional Checks for Handshake

synchronization schemes--not just basic two-flop

or multi-flop synchronizers, but more complex Handshake1 check

mechanisms, such as handshakes and FIFO- REQ

based schemes. Once detected, these DATA

synchronizers need to be verified as working

Violation: Data changing while request is active

correctly.

Handshake2 check

Both detection and verification have their own REQ

set of challenges, but when done properly, one ACK

N cycle window

can confidently claim correctness of these clock Violation: ACK does not become active within N cycles

domain crossings. This knowledge can be used after REQ (default N=5 cycles)

to filter out false violations, which typically result

when a tool fails to recognize properly

synchronized crossings and instead reports them Verifying FIFO Synchronizers

as unsynchronized. Many tools lack the ability

to detect and functionally verify handshake FIFOs are commonly used to transfer data

structures. Given that it is now commonplace to generated by a source to a destination where

find up to 80 percent of CDCs controlled by the source and destination are clocked at different

handshakes in large design modules, false or variable rates. Very often the source and

violations can be numbering in the hundreds. destination reside in different clock domains, in

These false violations make designers give up which case an asynchronous FIFO is needed.

on CDC verification with conventional tools in

the market. Similar problems arise with FIFO Asynchronous FIFOs involve multiple clock domain

synchronizers as well. crossings for empty and full flag calculation as

well as data read to the destination domain. In

Verifying Handshake Synchronizers a FIFO, these crossings are not always

synchronized using traditional synchronization

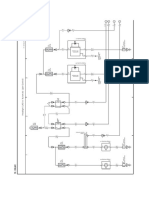

Fig 1 shows a typical handshake synchronization methods. Again, other CDC tools are unable to

scheme. Traditional CDC tools that look only for recognize such FIFO scheme (Fig 3), and will

a double-flop synchronizer will report these report these crossings as unsynchronized, resulting

crossings as unsynchronized, resulting in a large in a large number of false violations.

number of false violations.

Fig 3: Typical FIFO Synchronization Scheme

Other CDC tools report these

Fig1: Typical Handshake Sychronization Scheme as CDC violations

clk_A clk_A

Other CDC tools DATA BUS DATA BUS

write _en read _en

clk_A report these as clk_B

CDC violations clk_A Write Read clk_B

write_ read_ FSM

Domain FSM addr Domain

addr

clk_A DATA BUS

clk_B FIFO memory array

EN EN Empty

Domain Domain Full

REQ

compar- synchronize synchronize compar-

Sender Receiver ator read_addr write_addr ator

Handshake clk_B Handshake

clk_A FSM ACK FSM clk_B

Binary Gray to

clk_A to Gray Binary

The SpyGlass-CDC solution automatically The SpyGlass-CDC solution not only automatically

identifies such handshake schemes, and can thus identifies the above FIFO scheme but also

eliminate a large number of false violations. performs formal checking for data stability (on

However, the crossing cannot be considered safe double-flop synchronizers), and re-convergence

until its functionality is proven to be correct. signals (from the gray encoder).

Atrenta Inc. is the leading provider of Early Design Closure solutions to radically © Copyright 2008

improve design efficiency throughout the IC design flow. Customers benefit from Atrenta Inc. All rights

Atrenta tools & methodologies to capture design intent, explore implementation reserved. Atrenta, the

Atrenta logo, SpyGlass,

CONTACT: alternatives, validate RTL and optimize designs early, before expensive and time 1Team, and Early

1.408.453.3333 consuming detailed implementation. With over 140 customers, including the Design Closure are

moreinfo@atrenta.com worlds top 10 semiconductor companies, Atrenta provides the most comprehensive registered trademarks of

www.atrenta.com solution in the industry for Early Design Closure. Atrenta, Right from the Start! Atrenta Inc. All others

are the property of their

respective holders.

Atrenta Inc. 2077 Gateway Place, Suite 300, San Jose, CA 95110, USA Tel 408-453-3333 Fax 408-453-3322

Vous aimerez peut-être aussi

- SpyGlass CDCDocument2 pagesSpyGlass CDCyuga_aranPas encore d'évaluation

- Spyglass CDCDocument2 pagesSpyglass CDCRahul SharmaPas encore d'évaluation

- Critical Clock-Domain-Crossing Bugs: Steve Edn080320Ms4271 Figure 1 Steve Edn080320Ms4271 Figure 2Document4 pagesCritical Clock-Domain-Crossing Bugs: Steve Edn080320Ms4271 Figure 1 Steve Edn080320Ms4271 Figure 2Prabakaran EllaiyappanPas encore d'évaluation

- Study and Analysis of RTL Verification Tool IEEE ConferenceDocument7 pagesStudy and Analysis of RTL Verification Tool IEEE ConferenceZC LPas encore d'évaluation

- Bitcoin CaseStudy UserGuide GoldenUPF v1.1 PDFDocument30 pagesBitcoin CaseStudy UserGuide GoldenUPF v1.1 PDFashokPas encore d'évaluation

- Top Down AsicDocument17 pagesTop Down AsicKrishna M ViswanathPas encore d'évaluation

- Meridian CDC.A TrainingDocument114 pagesMeridian CDC.A Trainingvinodkumar kPas encore d'évaluation

- Lin TingDocument87 pagesLin TingVeeresh TangadgiPas encore d'évaluation

- Nvme Pcie SSD M.2 ManualDocument56 pagesNvme Pcie SSD M.2 ManualDummy BearPas encore d'évaluation

- VC SpyGlass CDC Quick Start GuideDocument28 pagesVC SpyGlass CDC Quick Start Guideworkat60474Pas encore d'évaluation

- Lab 6 Introduction To VerilogDocument7 pagesLab 6 Introduction To Verilogmmorsy1981Pas encore d'évaluation

- Verification TutorialDocument14 pagesVerification TutorialAdemar Gregoruti JuniorPas encore d'évaluation

- VCMDocument522 pagesVCMSai Kumar NallagangulaPas encore d'évaluation

- HDL Code Analysis For ASICs in Mobile SystemsDocument87 pagesHDL Code Analysis For ASICs in Mobile SystemsTuan NamPas encore d'évaluation

- Cadence Uv M Debug SlidesDocument34 pagesCadence Uv M Debug SlidesBharathwajan ParthasarathyPas encore d'évaluation

- Clock Domain Crossing Issues &Document35 pagesClock Domain Crossing Issues &Nishanth Gowda100% (1)

- 1.FPGA Design Flow Processes PropertiesDocument5 pages1.FPGA Design Flow Processes Propertiesmachnik1486624Pas encore d'évaluation

- Systemverilog For Design and Verification: Engineer Explorer SeriesDocument486 pagesSystemverilog For Design and Verification: Engineer Explorer Seriesvinay100% (1)

- VLSI Physical Design AutomationDocument18 pagesVLSI Physical Design Automationjeevan_raoPas encore d'évaluation

- SoC Design - A ReviewDocument131 pagesSoC Design - A ReviewSambhav VermanPas encore d'évaluation

- Synopsys Formality WorkshopDocument293 pagesSynopsys Formality WorkshopBasem HeshamPas encore d'évaluation

- Io MultiplexingDocument19 pagesIo Multiplexingsubramanyam62Pas encore d'évaluation

- Study of VLSI Design Methodologies and Limitations Using CAD Tools For CMOS Technology PresentationDocument26 pagesStudy of VLSI Design Methodologies and Limitations Using CAD Tools For CMOS Technology PresentationRoshdy AbdelRassoulPas encore d'évaluation

- Open File 2Document68 pagesOpen File 2AbhiPanchalPas encore d'évaluation

- Pulsed Latch Timing Analysis: Product Version: Tempus 15.1 October, 2015Document21 pagesPulsed Latch Timing Analysis: Product Version: Tempus 15.1 October, 2015Anshita AgarwalPas encore d'évaluation

- OpenSTA TutorialDocument57 pagesOpenSTA TutorialAbhinav VarakanthamPas encore d'évaluation

- ASIC經典總結Document134 pagesASIC經典總結Mark Ting-Min LinPas encore d'évaluation

- Guidelines For Design Synthesis Using Synopsys Design Compiler Design SynthesisDocument13 pagesGuidelines For Design Synthesis Using Synopsys Design Compiler Design Synthesisnishad_86Pas encore d'évaluation

- Clock Domain Crossing (CDC) : Erik Seligman CS 510, Lecture 17, March 2009Document39 pagesClock Domain Crossing (CDC) : Erik Seligman CS 510, Lecture 17, March 2009Rohan PeterPas encore d'évaluation

- Ece5745 Tut2 DCDocument15 pagesEce5745 Tut2 DCMisbahPas encore d'évaluation

- Lint Usage RulesDocument9 pagesLint Usage RulespnrgoudPas encore d'évaluation

- Ece5950 Tut4 Vcs GLDocument5 pagesEce5950 Tut4 Vcs GLVijay Kumar NPas encore d'évaluation

- Testing of VLSI CircuitsDocument9 pagesTesting of VLSI CircuitsjeyapriyaPas encore d'évaluation

- Synchronous ResetDocument1 pageSynchronous ResetAneesh RaveendranPas encore d'évaluation

- Vlsi 161217161739 PDFDocument29 pagesVlsi 161217161739 PDFkondalarao79Pas encore d'évaluation

- Ccs Timing WPDocument15 pagesCcs Timing WPSeshareddy KatamPas encore d'évaluation

- Wipro System On ChipDocument11 pagesWipro System On Chipprodip7Pas encore d'évaluation

- PD Design 1Document43 pagesPD Design 1Kanhaiya MishraPas encore d'évaluation

- Setup and Hold Time - Static Timing Analysis (STA) Basic (Part 3a) - VLSI ConceptsDocument3 pagesSetup and Hold Time - Static Timing Analysis (STA) Basic (Part 3a) - VLSI ConceptsRakesh KumarPas encore d'évaluation

- Different File FormatsDocument10 pagesDifferent File FormatsSunny GuptaPas encore d'évaluation

- A. Download Atrenta 5.x Release FileDocument12 pagesA. Download Atrenta 5.x Release File783520101Pas encore d'évaluation

- User GuideDocument592 pagesUser Guidebvnagesha17488Pas encore d'évaluation

- Lint SPQDocument3 pagesLint SPQAnil KumarPas encore d'évaluation

- Pre Final Sem Project ReportDocument79 pagesPre Final Sem Project Reportapi-301719207Pas encore d'évaluation

- BS PDFDocument31 pagesBS PDFRohith RajPas encore d'évaluation

- Amba 3 Axi Protocol Checker: User GuideDocument58 pagesAmba 3 Axi Protocol Checker: User GuidepriyajeejoPas encore d'évaluation

- Simulation in SimvisionDocument2 pagesSimulation in SimvisionIliyasMohammedPas encore d'évaluation

- Getting Started Lab With Spyglass 450Document47 pagesGetting Started Lab With Spyglass 450Никита Борсяков100% (1)

- File FormatDocument61 pagesFile FormatPRINCE KUMAR MAHATOPas encore d'évaluation

- Cadence SimDocument34 pagesCadence Simsanjayr_nittPas encore d'évaluation

- Cadence TutorialDocument24 pagesCadence TutorialVENKIPas encore d'évaluation

- Lab2 Synopsys DCDocument12 pagesLab2 Synopsys DCkrunalPas encore d'évaluation

- Synthesis QuestionsDocument4 pagesSynthesis QuestionsSupraja VedulaPas encore d'évaluation

- SDCrules PDFDocument163 pagesSDCrules PDFarunpandiyanPas encore d'évaluation

- NC Sim To Innovus FlowDocument52 pagesNC Sim To Innovus FlowSanthoshReddyPas encore d'évaluation

- DDR4 SdramDocument189 pagesDDR4 SdramRamakrishnaRao SoogooriPas encore d'évaluation

- Full Flow Clock Domain Crossing - From Source To Si: March 2016Document13 pagesFull Flow Clock Domain Crossing - From Source To Si: March 2016RamakrishnaRao SoogooriPas encore d'évaluation

- C-17 Painting Cost Break Up1Document4 371 pagesC-17 Painting Cost Break Up1RamakrishnaRao SoogooriPas encore d'évaluation

- 1 Clock Domain CrossingDocument35 pages1 Clock Domain CrossingRamakrishnaRao SoogooriPas encore d'évaluation

- Full Flow Clock Domain Crossing - From Source To Si: March 2016Document13 pagesFull Flow Clock Domain Crossing - From Source To Si: March 2016RamakrishnaRao SoogooriPas encore d'évaluation

- IntroDocument17 pagesIntroRamakrishnaRao SoogooriPas encore d'évaluation

- Migrating To Onsemi Network & CliosoftDocument29 pagesMigrating To Onsemi Network & CliosoftRamakrishnaRao SoogooriPas encore d'évaluation

- Floorplan Assignment Name - Sap IdDocument1 pageFloorplan Assignment Name - Sap IdRamakrishnaRao SoogooriPas encore d'évaluation

- 5-01-2019 Physical DesignDocument3 pages5-01-2019 Physical DesignRamakrishnaRao SoogooriPas encore d'évaluation

- Emp Name: Floorplan Assignment: On On On Off On On OnDocument4 pagesEmp Name: Floorplan Assignment: On On On Off On On OnRamakrishnaRao SoogooriPas encore d'évaluation

- All ScriptsDocument4 pagesAll ScriptsRamakrishnaRao SoogooriPas encore d'évaluation

- Physics Lab Experiment 6Document6 pagesPhysics Lab Experiment 6Peter Sam CoPas encore d'évaluation

- NSX Battle Card - FinalDocument2 pagesNSX Battle Card - FinalElias Bezulle100% (1)

- DPM Engineering WorksDocument34 pagesDPM Engineering WorksAkash SinghPas encore d'évaluation

- Reference Jica-Chodai Scouring Manual in ThailandDocument175 pagesReference Jica-Chodai Scouring Manual in ThailandSeptinurriandianiPas encore d'évaluation

- iQ-WEBX 6 2 3 Installation Guide INT EN - 001RDocument51 pagesiQ-WEBX 6 2 3 Installation Guide INT EN - 001RDoug KolkowPas encore d'évaluation

- Overall EWD Vehicle Exterior Rear Fog LightDocument10 pagesOverall EWD Vehicle Exterior Rear Fog Lightgabrielzinho43Pas encore d'évaluation

- KinematicsDocument33 pagesKinematicsErik MagnoPas encore d'évaluation

- IT Dashboard Dec2013Document870 pagesIT Dashboard Dec2013Dolly SinghPas encore d'évaluation

- Aset WTP HarapanDocument7 pagesAset WTP HarapanReinhard SimbolonPas encore d'évaluation

- Cooling Coil SizingDocument4 pagesCooling Coil SizingRanu JanuarPas encore d'évaluation

- Analysis of Open-Channel Flow Transitions Using Specific Energy DiagramDocument13 pagesAnalysis of Open-Channel Flow Transitions Using Specific Energy DiagramRandy ViolaPas encore d'évaluation

- Mathalino: E N W S G S V V V V V W W W D Γ Γ Γ Γ Γ Γ Γ Γ Ll Pl Li Pi GiDocument8 pagesMathalino: E N W S G S V V V V V W W W D Γ Γ Γ Γ Γ Γ Γ Γ Ll Pl Li Pi GiLovely Joy ArdanielPas encore d'évaluation

- Is 13935 2009 PDFDocument33 pagesIs 13935 2009 PDFManojKumawatRjPas encore d'évaluation

- Doka Large Formwork User ManualDocument21 pagesDoka Large Formwork User ManualNasir AryaniPas encore d'évaluation

- Congratulations On The Purchase of Your New Antari Z Series Fog MachineDocument20 pagesCongratulations On The Purchase of Your New Antari Z Series Fog MachineWalter SeidlPas encore d'évaluation

- (Task Specific Risk Assessment) : No Name Signature Position Date N Name Signature Position DateDocument5 pages(Task Specific Risk Assessment) : No Name Signature Position Date N Name Signature Position DateRavi Shankar TurlapatiPas encore d'évaluation

- Basic NetworkingDocument21 pagesBasic NetworkingMina Ilagan RazonPas encore d'évaluation

- Concrete Making MaterialsDocument55 pagesConcrete Making Materialsjaffna100% (1)

- Microsoft PowerPoint - ASEP - NSCP 2015 Chapter6 - WOODDocument75 pagesMicrosoft PowerPoint - ASEP - NSCP 2015 Chapter6 - WOODRay Ramilo67% (9)

- Lorentz Ps4000 Manual enDocument9 pagesLorentz Ps4000 Manual encorazto100% (1)

- d1 - Evaluation - Justify Content Designs and Formats - FinalDocument5 pagesd1 - Evaluation - Justify Content Designs and Formats - Finalapi-466034593Pas encore d'évaluation

- Megger DET14 DET24 An en V 01Document16 pagesMegger DET14 DET24 An en V 01costelchelariuPas encore d'évaluation

- APU TA Training Manual (JUNE 2013)Document57 pagesAPU TA Training Manual (JUNE 2013)zhuhangPas encore d'évaluation

- 02 04 16 BPZ Transclinic 16i 4 Sprachen PRINTDocument144 pages02 04 16 BPZ Transclinic 16i 4 Sprachen PRINTjuanPas encore d'évaluation

- Tugs - Developments For PDFDocument28 pagesTugs - Developments For PDFP Venkata SureshPas encore d'évaluation

- SI Failure of Bremi Ignition Coils E36 - 7, E39, E46, E53Document2 pagesSI Failure of Bremi Ignition Coils E36 - 7, E39, E46, E53strexxPas encore d'évaluation

- TCSP10403R0Document30 pagesTCSP10403R0BADRI VENKATESHPas encore d'évaluation

- Dyeing Machines: By: Ambika Udaikumar Ankita Singh Dhara Parmar Monali Wani Sonal MarwahDocument15 pagesDyeing Machines: By: Ambika Udaikumar Ankita Singh Dhara Parmar Monali Wani Sonal MarwahMohammed Atiqul Hoque ChowdhuryPas encore d'évaluation

- C-Zone SDN BHD: Price List Effective 10 AUG 2019Document2 pagesC-Zone SDN BHD: Price List Effective 10 AUG 2019Cikgu AlPas encore d'évaluation

- Jovan Marjanovic Theory of Gravity MachinesDocument10 pagesJovan Marjanovic Theory of Gravity MachinesWilhelm HartmanPas encore d'évaluation