Académique Documents

Professionnel Documents

Culture Documents

7.1 Arquitectura Harvard PDF

Transféré par

LeandroTombettaTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

7.1 Arquitectura Harvard PDF

Transféré par

LeandroTombettaDroits d'auteur :

Formats disponibles

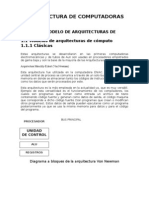

En la arquitectura von Neumann, la CPU se conecta con una memoria única, donde coexisten datos e

instrucciones, a través de un mismo sistema de buses. Esto tiene 2 desventajas:

El tamaño de los datos e instrucciones está fijado por el ancho del bus que comunica la memoria con

la CPU. Así, con un bus de 8 bits, se tendrán que manejar datos e instrucciones de una o más unidades

de 8 bits (bytes) de longitud. Si quisiéramos acceder a una instrucción o dato de más de un byte de

longitud, tendríamos que realizar más de un acceso a la memoria.

El procesador es más lento en su respuesta, ya que no puede buscar en memoria una nueva

instrucción mientras no finalicen las transferencias de datos de la instrucción anterior, lo cual

impide superponer ambos tiempos de acceso. Osea, la CPU puede estar bien leyendo una instrucción

o leyendo/escribiendo datos desde/hacia la memoria pero ambos procesos no pueden ocurrir al

mismo tiempo, ya que las instrucciones y datos usan el mismo sistema de buses.

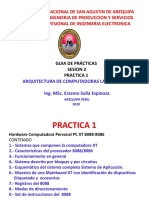

En la arquitectura Harvard, la memoria de instrucciones y la memoria de datos son independientes y cada

una dispone de su propio sistema de buses para el acceso. Este aislamiento y diferenciación tiene las

siguientes ventajas:

Al tener buses separados y de diferente tamaño, la longitud de los datos y las instrucciones puede

ser distinta, al igual que el tamaño de cada memoria, debido a la diferencia de tamaño de los buses

de direcciones. Entonces, al no estar relacionados el tamaño de uno y otro, las instrucciones pueden

optimizarse para ocupar una sola posición de memoria de programa, evitando acceder más veces a

la memoria y logrando así mayor velocidad y menor longitud de programa.

Se puede acceder en forma simultánea e independiente a la memoria de datos y a la memoria de

instrucciones, por lo que podemos completar la ejecución de una instrucción (memoria de datos), y

al mismo tiempo leer la siguiente instrucción a ejecutar (memoria de programa), logrando mayor

velocidad.

A su vez, esta organización favorece a la segmentación o “pipeline”, que aprovecha la separación de las

memorias de la arquitectura Harvard, pudiendo ejecutar una instrucción (lo que implica acceder a la

memoria de datos) mientras se busca la siguiente (en la memoria de programa). Esto permite solapar

ambas fases, permitiendo que cada instrucción se ejecute de manera efectiva en un ciclo (excepto por las de

salto que tardan dos), aumentando así el número de instrucciones ejecutadas simultáneamente en un

determinado periodo de tiempo. Si bien la duración de cada una no se reduce, si se reduce la duración del

conjunto de ellas. Esto último es a su vez, una característica importante de los procesadores RISC (una

instrucción por ciclo), por lo que dichos procesadores hacen uso de arquitectura Harvard. Por ejemplo, los

PIC16C84 que usamos en la práctica usan esta organización.

Vous aimerez peut-être aussi

- Mapa Conceptual de Arquitectura de Moldelo de Von Neumann.Document1 pageMapa Conceptual de Arquitectura de Moldelo de Von Neumann.yuridia100% (3)

- Administración de sistemas operativosD'EverandAdministración de sistemas operativosÉvaluation : 3.5 sur 5 étoiles3.5/5 (8)

- UF0852 - Instalación y actualización de sistemas operativosD'EverandUF0852 - Instalación y actualización de sistemas operativosÉvaluation : 5 sur 5 étoiles5/5 (1)

- Tema 4 ActividadesDocument4 pagesTema 4 ActividadesOscar Panez LizargaPas encore d'évaluation

- Manual Configuracion TxD-V1Document16 pagesManual Configuracion TxD-V1Rubén Alberto Rodríguez PachanoPas encore d'évaluation

- Arquitecturas de ComputadorasDocument6 pagesArquitecturas de ComputadorasIrving ChávezPas encore d'évaluation

- Arquitectura Von Neumann y Arquitectura HarvardDocument3 pagesArquitectura Von Neumann y Arquitectura HarvardMerari Davalos PerezPas encore d'évaluation

- Arquitectura Harvard y Von Neumann PDFDocument2 pagesArquitectura Harvard y Von Neumann PDFLuis AlbertoPas encore d'évaluation

- Arquitectura Harvard y Von NeumannDocument2 pagesArquitectura Harvard y Von NeumannEFRAIN SANDOVALPas encore d'évaluation

- Arquitectura Harvard Ventajas y DesventajasDocument2 pagesArquitectura Harvard Ventajas y DesventajasOsbaldo Taurino GQ100% (1)

- PipelinesDocument8 pagesPipelinesAndre FernándezPas encore d'évaluation

- Arquitectura HarvardDocument5 pagesArquitectura HarvardFernanda NathalyPas encore d'évaluation

- Trabajo2 RedesDocument3 pagesTrabajo2 RedesIvan CazorlaPas encore d'évaluation

- Arquitectura Von Neumann y Arquitectura Harvard UltimaDocument5 pagesArquitectura Von Neumann y Arquitectura Harvard UltimaDuivan Andree Mata JaureguiPas encore d'évaluation

- Arquitectura de ComputadorasDocument8 pagesArquitectura de ComputadorasSorel TorresPas encore d'évaluation

- Arquitectura HarvardDocument4 pagesArquitectura HarvardMaria Ruiz LinoPas encore d'évaluation

- Arquitectura HarvardDocument7 pagesArquitectura HarvardLuisPas encore d'évaluation

- Montaje y Mantenimiento 1º EjerciciosDocument3 pagesMontaje y Mantenimiento 1º EjerciciosChristian46RMPas encore d'évaluation

- Mapa Ensayo 2conclusiones DimasBustosDocument3 pagesMapa Ensayo 2conclusiones DimasBustosDIMAS EDUARDO BUSTOS SOSAPas encore d'évaluation

- Taller MicroprocesadoresDocument5 pagesTaller MicroprocesadoresDanielPas encore d'évaluation

- Arquitectura Von Neumann y Arquitectura HarvardDocument3 pagesArquitectura Von Neumann y Arquitectura HarvardCesarBeltran100% (1)

- Comparacion Arquitectura de Von Neuman y HarvadDocument1 pageComparacion Arquitectura de Von Neuman y HarvadSebastian Medina BernalPas encore d'évaluation

- Arquitectura HarvardDocument1 pageArquitectura HarvardEsauRojasPas encore d'évaluation

- Arquitectura HarvardDocument2 pagesArquitectura HarvardJonathan Fernando Amaguaña SimbañaPas encore d'évaluation

- MultiprocesadorDocument19 pagesMultiprocesadorCHINO JIMENEZPas encore d'évaluation

- BDD Shared MemoryDocument4 pagesBDD Shared MemoryJesus MedinaPas encore d'évaluation

- Arquitectura HarvardDocument4 pagesArquitectura HarvardAndrea Alejandra Hernández RodríguezPas encore d'évaluation

- Gonzalez Ibarra Reporte ArquitecturaDocument11 pagesGonzalez Ibarra Reporte ArquitecturaCarolina GonzalezPas encore d'évaluation

- Multiprocesamiento ParaleloDocument9 pagesMultiprocesamiento ParaleloElmerCuencaBalabarca0% (1)

- Arquitectura Von Neumann y Arquitectura HarvardDocument3 pagesArquitectura Von Neumann y Arquitectura HarvardJuan RuizPas encore d'évaluation

- Tipos de Memoria y Arquitectura de Von Neuman Vs HarvardDocument10 pagesTipos de Memoria y Arquitectura de Von Neuman Vs Harvardviviam pal,maPas encore d'évaluation

- 53 Unidad6 Coherencia de CacheDocument12 pages53 Unidad6 Coherencia de CacheDoracelia Gazga LovePas encore d'évaluation

- Arquitecturas de MicrocontroladoresDocument19 pagesArquitecturas de MicrocontroladoresStephenakd13Pas encore d'évaluation

- Arquitectura HarvardDocument2 pagesArquitectura Harvardyoanderson fernandezPas encore d'évaluation

- Estructura de MicroprocesadoresDocument5 pagesEstructura de MicroprocesadoresEve PeciPas encore d'évaluation

- Unidad2 Arroyo 8cm1Document20 pagesUnidad2 Arroyo 8cm1Daniel VargasPas encore d'évaluation

- Arquitecturas Von Neumann & HarvardDocument1 pageArquitecturas Von Neumann & HarvardCarlos Alberto HernándezPas encore d'évaluation

- Arquitectura HarvardDocument11 pagesArquitectura Harvardsergio damianPas encore d'évaluation

- Arquitectura HarvardDocument12 pagesArquitectura HarvardAndreaFabiolaParedesGomez0% (1)

- Ensayodescriptivo de La Arquitectura de Von Neumann y Harvard - DeisymorenoDocument4 pagesEnsayodescriptivo de La Arquitectura de Von Neumann y Harvard - Deisymorenodeisy morenoPas encore d'évaluation

- Arquitecturas ClásicasDocument11 pagesArquitecturas ClásicasGiovani ArellanoPas encore d'évaluation

- Arquitectura de Von NeumanDocument5 pagesArquitectura de Von NeumanCarlosFernandoAgudeloMendozaPas encore d'évaluation

- Arquitectura ComputadoraDocument4 pagesArquitectura ComputadoraEthiel Morales CPas encore d'évaluation

- Memoria Compartida Distribuida PDFDocument22 pagesMemoria Compartida Distribuida PDFMarcos Julián GaliciaPas encore d'évaluation

- Ventajas y Desventajas de Arquitecturas Harvard y Von NeumannDocument5 pagesVentajas y Desventajas de Arquitecturas Harvard y Von NeumannRobe UtreraPas encore d'évaluation

- MPP y SMPDocument5 pagesMPP y SMPEfra26100% (1)

- Jerarquia de Buses MultiplesDocument7 pagesJerarquia de Buses MultiplesSergio RamirezPas encore d'évaluation

- El ComputadorDocument4 pagesEl ComputadorEloy José BanquetPas encore d'évaluation

- Grupo 7 Arquitectura Del SMPDocument4 pagesGrupo 7 Arquitectura Del SMPtoxic_gabriel1207Pas encore d'évaluation

- Arquitectura de ComputadorasDocument53 pagesArquitectura de Computadorastilsma100% (3)

- Arquitectura Von Neumann y HarvardDocument7 pagesArquitectura Von Neumann y HarvardBrian JaramilloPas encore d'évaluation

- 1.2-Modelo de Arquitectura de ComponentesDocument5 pages1.2-Modelo de Arquitectura de ComponentesALDAIR MACEO FERNANDEZPas encore d'évaluation

- El Diseño Del Nivel de MicroarquitecturaDocument10 pagesEl Diseño Del Nivel de MicroarquitecturaManuel InciartePas encore d'évaluation

- Arquitectura HarvardDocument9 pagesArquitectura HarvardCarlos Manuel Limaylla HuaynatesPas encore d'évaluation

- Actividad 3.1 Arquitecturas Von Neumman y HarvardDocument4 pagesActividad 3.1 Arquitecturas Von Neumman y HarvarddiegoPas encore d'évaluation

- Arquitectura de Las ComputadorasDocument5 pagesArquitectura de Las ComputadorasHermes MejíaPas encore d'évaluation

- Arquitectura de HarvardDocument2 pagesArquitectura de HarvardJulio David Godoy OrtízPas encore d'évaluation

- Sesion2 Practica1 SDocument11 pagesSesion2 Practica1 SJano Jesus AlexPas encore d'évaluation

- UF1468 - Almacenamiento de la información e introducción a SGBDD'EverandUF1468 - Almacenamiento de la información e introducción a SGBDPas encore d'évaluation

- UF1275 - Selección, instalación, configuración y administración de los servidores de transferencia de archivosD'EverandUF1275 - Selección, instalación, configuración y administración de los servidores de transferencia de archivosPas encore d'évaluation

- Cinematica 3Document16 pagesCinematica 3alff21100% (1)

- Trabajo Practico N°1 Estadística DescriptivaDocument21 pagesTrabajo Practico N°1 Estadística DescriptivaLeandroTombettaPas encore d'évaluation

- Introduccion A SQL PDFDocument7 pagesIntroduccion A SQL PDFLeandroTombettaPas encore d'évaluation

- Tiro OblicuoDocument17 pagesTiro Oblicuohar548100% (2)

- Introduccion A SQL PDFDocument7 pagesIntroduccion A SQL PDFLeandroTombettaPas encore d'évaluation

- Algunas Aplicaciones de Campos Escalares PDFDocument8 pagesAlgunas Aplicaciones de Campos Escalares PDFLeandroTombettaPas encore d'évaluation

- Clase Unidad 1 TP 1Document2 pagesClase Unidad 1 TP 1LeandroTombettaPas encore d'évaluation

- Teoría de Análisis 2Document13 pagesTeoría de Análisis 2LeandroTombettaPas encore d'évaluation

- 1 Normalizacion 19Document47 pages1 Normalizacion 19LeandroTombettaPas encore d'évaluation

- Ley de Responsabilidad Social EmpresarialDocument11 pagesLey de Responsabilidad Social EmpresarialTiara Brasesco MurgaPas encore d'évaluation

- Plano TangenteDocument6 pagesPlano TangenteLeandroTombettaPas encore d'évaluation

- Ejer GLADDocument3 pagesEjer GLADLeandroTombettaPas encore d'évaluation

- Smalltalk Sintaxis Parte IDocument27 pagesSmalltalk Sintaxis Parte ILeandroTombettaPas encore d'évaluation

- Construcción de Una Máquina ReducidaDocument1 pageConstrucción de Una Máquina ReducidaLeandroTombettaPas encore d'évaluation

- Aceptor de Estados Finitos de Transiciones Lambda-ClausuraDocument1 pageAceptor de Estados Finitos de Transiciones Lambda-ClausuraLeandroTombettaPas encore d'évaluation

- Unidad 2 PDFDocument51 pagesUnidad 2 PDFLeandroTombettaPas encore d'évaluation

- SSL2 2014Document40 pagesSSL2 2014Jokerwin09Pas encore d'évaluation

- Solucionario Fisica Vol 1 Alonso Finn PDFDocument21 pagesSolucionario Fisica Vol 1 Alonso Finn PDFLeandroTombettaPas encore d'évaluation

- SSL3 2014 PDFDocument43 pagesSSL3 2014 PDFLeandroTombettaPas encore d'évaluation

- UT XII-Propiedades de Los So Lidos PDFDocument20 pagesUT XII-Propiedades de Los So Lidos PDFLeandroTombettaPas encore d'évaluation

- SSL1 2014 PDFDocument22 pagesSSL1 2014 PDFLeandroTombettaPas encore d'évaluation

- Urrutia - Calculo DiferencialDocument7 pagesUrrutia - Calculo DiferencialLeandroTombettaPas encore d'évaluation

- Fisica JuevesDocument6 pagesFisica JuevesLeandroTombetta100% (1)

- Vector EsDocument15 pagesVector EsLeandroTombetta100% (1)

- Fisica MiercolesDocument6 pagesFisica MiercolesLeandroTombettaPas encore d'évaluation

- Fisica JuevesDocument6 pagesFisica JuevesLeandroTombetta100% (1)

- Mesas de Examenes - Diciembre 2018 - 2Document5 pagesMesas de Examenes - Diciembre 2018 - 2LeandroTombettaPas encore d'évaluation

- Fisica JuevesDocument6 pagesFisica JuevesLeandroTombetta100% (1)

- Fisica MartesDocument9 pagesFisica MartesLeandroTombettaPas encore d'évaluation

- Produccion Organica, Biologica, EcologicaDocument7 pagesProduccion Organica, Biologica, EcologicaLeandroTombettaPas encore d'évaluation

- Mapa Conceptual Tipos de Harware Jorge BernalDocument1 pageMapa Conceptual Tipos de Harware Jorge BernalJorge BernalPas encore d'évaluation

- Lista de Precios 2017Document13 pagesLista de Precios 2017Wendy RodriguezPas encore d'évaluation

- IT Essentials PC Hardware and Software Version 4Document575 pagesIT Essentials PC Hardware and Software Version 4Jesus Romero MirandaPas encore d'évaluation

- Manual de Uso ElectroNika 2009: El Software para El Técnico Reparador y para Los Electrónicos Desde 1995Document43 pagesManual de Uso ElectroNika 2009: El Software para El Técnico Reparador y para Los Electrónicos Desde 1995D.A.S. Electrónica100% (7)

- Cómo Elegir Un Buén PICDocument2 pagesCómo Elegir Un Buén PICDavid LidueñasPas encore d'évaluation

- Compu SR RaulDocument1 pageCompu SR RaulHAROLD JULIO CALDERÓN COAGUILAPas encore d'évaluation

- 5 - Taller Funciones - .Si y .Si - ConjuntoDocument12 pages5 - Taller Funciones - .Si y .Si - ConjuntoLuz NavarretePas encore d'évaluation

- SmartPPD EspDocument15 pagesSmartPPD EspAlan ChavezPas encore d'évaluation

- Autocad LentoDocument5 pagesAutocad Lentoalbert huamani huancaPas encore d'évaluation

- Gestión de ArchivosDocument5 pagesGestión de ArchivosMMMPas encore d'évaluation

- Especificaciones SP 04FHBDocument3 pagesEspecificaciones SP 04FHBAlbertoRamirezHaroPas encore d'évaluation

- Ricoh MP C2504 FolletoDocument4 pagesRicoh MP C2504 FolletoInnovar CopiadorasPas encore d'évaluation

- WNC Router CPE WNC 4G FDD WLD71-T4 White MoDocument1 pageWNC Router CPE WNC 4G FDD WLD71-T4 White MoJorge Ahumada MayoristaPas encore d'évaluation

- Preguntas de La Arquitectura Del ComputadorDocument4 pagesPreguntas de La Arquitectura Del ComputadorYordan Esteban SILVA GOMEZPas encore d'évaluation

- Caso de Estudio HardwareDocument3 pagesCaso de Estudio HardwareLuciano ErisonPas encore d'évaluation

- Módulos SPI e I2CDocument23 pagesMódulos SPI e I2CClaudia LunaPas encore d'évaluation

- Ricoh Aficio CL3500NDocument3 pagesRicoh Aficio CL3500NjomibadiPas encore d'évaluation

- Guía de Inicio Rápido 8.32 NVR GeovisionDocument2 pagesGuía de Inicio Rápido 8.32 NVR GeovisionLuis GarHerPas encore d'évaluation

- Actividad Evaluativa Eje 2 - Ergonomia Ocupacional - Claudia RojasDocument18 pagesActividad Evaluativa Eje 2 - Ergonomia Ocupacional - Claudia Rojasinesita38Pas encore d'évaluation

- Victoria 4Document8 pagesVictoria 4tom25_04Pas encore d'évaluation

- MP c307spf RicohDocument4 pagesMP c307spf RicohJosis OnPas encore d'évaluation

- (2013) CD 4942Document179 pages(2013) CD 4942Marcos Olivares DiazPas encore d'évaluation

- Dimensiones de La CalidadDocument4 pagesDimensiones de La CalidadFernando OEPas encore d'évaluation

- Album Sistemas OperativosDocument11 pagesAlbum Sistemas OperativosEduardo Castillo100% (2)

- Actividad 1 Módulo 2 (Operaciones Basicas de Oficinas)Document7 pagesActividad 1 Módulo 2 (Operaciones Basicas de Oficinas)Liz doania Perez santanaPas encore d'évaluation

- xxxCursoDBA10g1 Parte1Document109 pagesxxxCursoDBA10g1 Parte1Marco GarciaPas encore d'évaluation

- Cotizacion Uface800 Plus 00020221021cDocument2 pagesCotizacion Uface800 Plus 00020221021cIvan FelicesPas encore d'évaluation

- La Evolución Del Celular en El Paso Del TiempoDocument4 pagesLa Evolución Del Celular en El Paso Del TiempoAlfredo VegaPas encore d'évaluation