Académique Documents

Professionnel Documents

Culture Documents

IOP communication with CPU and I/O devices

Transféré par

Reader_scribd0 évaluation0% ont trouvé ce document utile (0 vote)

27 vues4 pagesAn Input-Output Processor (IOP) may be classified as a processor with direct memory access. In this configuration, the computer system can be divided into a memory unit and one or more processors. Each IOP takes care of input and output tasks, relieving The CPU from the housekeeping chores involved in I / O transfers.

Description originale:

Titre original

4.7

Copyright

© Attribution Non-Commercial (BY-NC)

Formats disponibles

PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentAn Input-Output Processor (IOP) may be classified as a processor with direct memory access. In this configuration, the computer system can be divided into a memory unit and one or more processors. Each IOP takes care of input and output tasks, relieving The CPU from the housekeeping chores involved in I / O transfers.

Droits d'auteur :

Attribution Non-Commercial (BY-NC)

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

27 vues4 pagesIOP communication with CPU and I/O devices

Transféré par

Reader_scribdAn Input-Output Processor (IOP) may be classified as a processor with direct memory access. In this configuration, the computer system can be divided into a memory unit and one or more processors. Each IOP takes care of input and output tasks, relieving The CPU from the housekeeping chores involved in I / O transfers.

Droits d'auteur :

Attribution Non-Commercial (BY-NC)

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 4

4.

7 Input-Output Processor (IOP)

Instead of having each interface communicate

with the CPU, a computer may incorporate one or

more external processors and assign them the task of

communicating directly with all I/O devices. An

input-output processor (IOP) may be classified as a

processor with direct memory access capability that

communicates with I/O devices. In this

configuration, the computer system can be divided

into a memory unit, and a number of processors

comprised of the CPU and one or more IOPs. Each

IOP takes care of input and output tasks, relieving

the CPU from the housekeeping chores involved in

I/O transfers. A processor that communicates with

remote terminals over telephone and other

communication media in a serial fashion is called a

data communication processor (DCP).

The IOP is similar to a CPU except that it is

designed to handle the details of I/O processing,

Unlike the DMA controller that must be set up

entirely by the CPU, the IOP can fetch and execute

its own instructions. IOP instructions are specifically

designed to facilitate I/O transfers. In addition, the

IOP can perform other processing asks, such as

arithmetic, logic, branching, and code translation.

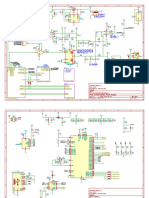

The block diagram of a computer with two

processors is shown in Fig. 4-19. The memory unit

occupies a central position and can communicate

with each processor by means of direct memory

access. The CPU is responsible for processing data

needed in the solution of computation tasks. The IOP

provides a path for transfer of data between various

peripheral devices and the memory unit. The CPU is

usually assigned the task of initiating the I/O

program. From then on the IOP operates

independent of the CPU and continues to transfer

data from external devices and memory.

The data formats of peripheral devices differ from

memory and CPU data formats. The IOP must

structure data words from many different sources.

For example, it may be necessary to take four bytes

from an input device and pack them into one 32-bit

word before the transfer to memory. Data are

gathered in the IOP at the device rate and bit

capacity while the CPU is executing its own

program. After the input data are assembled into a

memory word, they are transferred from IOP directly

into memory by "stealing" one memory cycle from

the CPU. Similarly, an output word transferred from

memory to the IOP is directed from the IOP to the

output device at the device rate and bit capacity.

Figure 4-19 Block Diagram of a Computer with

I/O Processor

The communication between the IOP and the

devices attached to it is similar to the program

control method of transfer. Communication with the

memory is similar to the direct memory access

method. The way by which the CPU and IOP

communicate depends on the level of sophistication

included in the system. In very-large-scale

computers, each processor is independent of all

others and anyone processor can initiate an

operation. In most computer systems, the CPU is the

master while the IOP is a slave processor. The CPU

is assigned the task of initiating all operations, but

I/O instructions are executed in the IOP. CPU

instructions provide operations to start an I/O

transfer and also to test I/O status conditions needed

for making decisions on various I/O activities. The

IOP, in turn, typically asks for CPU attention by

means of an interrupt. It also responds to CPU

requests by placing a status word in a prescribed

location in memory to be examined later by a CPU

program. When an I/O operation is desired, the CPU

informs the IOP where to find the I/O program and

then leaves the transfer details to the IOP.

Instructions that are read from memory by an IOP

are sometimes called commands, to distinguish them

from instructions that are read by the CPU.

Otherwise, an instruction and a command have

similar functions. Commands are prepared by

experienced programmers and are stored in memory.

The command words constitute the program for the

IOP. The CPU informs the 10P where to find the

commands in memory when it is time to execute the

I/O program.

4.7.1 CPU-IOP Communication

The communication between CPU and IOP may

take different forms, depending on the particular

computer considered. In most cases the memory unit

acts as a message center where each processor leaves

information for the other. To appreciate the

operation of a typical IOP, we will illustrate by a

specific example the method by which the CPU and

IOP communicate. This is a simplified example that

omits many operating details in order to provide an

overview of basic concepts. The sequence of

operations may be carried out as shown in the flow

chart of Fig. 4-20. The CPU sends an instruction to

test the IOP path. The IOP responds by inserting a

status word in memory for the CPU to check. The

bits of the status word indicate the condition of the

IOP and I/O device, such as IOP overload condition,

device busy with another transfer, or device ready

for I/O transfer. The CPU refers to the status word in

memory to decide what to do next. If all is in order,

the CPU sends the instruction to start I/O transfer.

The memory address received with this instruction

tells the IOP where to find its program.

The CPU can now continue with another program

while the IOP is busy with the I/O program. Both

programs refer to memory by means of DMA

transfer. When the IOP terminates the execution of

its program, it sends an interrupt request to the CPU.

The CPU responds to the interrupt by issuing an

instruction to read the status from the IOP. The IOP

responds by placing the contents of its status report

into a specified memory location. The status word

indicates whether the transfer has been completed or

if any errors occurred during the transfer. From

inspection of the bits in the status word, the CPU

determines if the I/O operation was completed

satisfactorily without errors.

The IOP takes care of all data transfers between

several I/O units and the memory while the CPU is

processing another program. The IOP and CPU are

competing for the 1.lSe of memory, so the number of

devices that can be in operation is limited by the

access rune of the memory. It is not possible-to

saturate the memory by I/O devices in most systems,

as the speed of most devices is much slower than the

CPU. However, some very fast units, such as

magnetic disks, can use an appreciable number of

the available memory cycles. In that case, the speed

of the CPU may deteriorate because it will often

have to wait for the IOP to conduct memory

transfers.

Vous aimerez peut-être aussi

- Coa 2.3Document5 pagesCoa 2.3Raman Ray 105Pas encore d'évaluation

- Input-Output Interface FundamentalsDocument23 pagesInput-Output Interface FundamentalsyashPas encore d'évaluation

- Asynchronous Data Transfer ModesDocument5 pagesAsynchronous Data Transfer ModesAshwani KumarPas encore d'évaluation

- How I/O devices transfer data to and from computersDocument11 pagesHow I/O devices transfer data to and from computersNora MuhammadPas encore d'évaluation

- DMA and IOP Modes of Data TransferDocument8 pagesDMA and IOP Modes of Data TransferGagandeep SinghPas encore d'évaluation

- A Timely Question.: Pre-EmptivelyDocument18 pagesA Timely Question.: Pre-EmptivelyAnonymous enHaphbPas encore d'évaluation

- Ignou Solution Guide 2018-19Document34 pagesIgnou Solution Guide 2018-19Shivangi MaheshwariPas encore d'évaluation

- Module VDocument41 pagesModule VAryan JainPas encore d'évaluation

- In Put Out Put OrganizationDocument45 pagesIn Put Out Put OrganizationdevibalaPas encore d'évaluation

- Io OrganizationDocument20 pagesIo Organizationbijan shresthaPas encore d'évaluation

- Title of The PresentationDocument14 pagesTitle of The PresentationBivekMazumderPas encore d'évaluation

- Input Output Organization: IO Interface Modes of Transfer Interrupt Direct Memory Access Introduction To IO ProcessorDocument41 pagesInput Output Organization: IO Interface Modes of Transfer Interrupt Direct Memory Access Introduction To IO ProcessorPRADEEP JPas encore d'évaluation

- Different Modes of Data TransferDocument2 pagesDifferent Modes of Data TransferRekha Al85% (13)

- Io ModulesDocument28 pagesIo ModulesAbdukadir AbdullahPas encore d'évaluation

- A Timely Question.: Pre-EmptivelyDocument21 pagesA Timely Question.: Pre-EmptivelyRamesh RajaPas encore d'évaluation

- Lecture1 2 3Document40 pagesLecture1 2 3Prince AliPas encore d'évaluation

- Input/Output Organization and Modes of Data TransferDocument18 pagesInput/Output Organization and Modes of Data TransferVibhash Kumar GabelPas encore d'évaluation

- Comparing DMA, I/O Processor, Polling and InterruptsDocument3 pagesComparing DMA, I/O Processor, Polling and InterruptsCharles BurgosPas encore d'évaluation

- Input-Output Modules: Detection Mechanism. Functions of I/O ModuleDocument8 pagesInput-Output Modules: Detection Mechanism. Functions of I/O ModuleSubash GautamPas encore d'évaluation

- Input Output OrganizationDocument13 pagesInput Output OrganizationAsma ShaikPas encore d'évaluation

- Operations and AddressingDocument6 pagesOperations and AddressingNguyễn KhanhPas encore d'évaluation

- Dpco Unit 5 Part 4Document9 pagesDpco Unit 5 Part 4AparnaPas encore d'évaluation

- CPU I/O Programming Input and OutputDocument8 pagesCPU I/O Programming Input and OutputVijayaraghavan VPas encore d'évaluation

- Computer Organization-Chapter 9Document9 pagesComputer Organization-Chapter 9Bipin MasalPas encore d'évaluation

- Research Activity 2Document5 pagesResearch Activity 2Jastine AnnePas encore d'évaluation

- CO UNIT IVDocument5 pagesCO UNIT IVMohd Ismail GourPas encore d'évaluation

- Systems Programming Techniques for I/O OperationsDocument8 pagesSystems Programming Techniques for I/O OperationsareebaPas encore d'évaluation

- COA UNIT 4 NotesDocument20 pagesCOA UNIT 4 NotesShubham AggarwalPas encore d'évaluation

- UNIT - 5 - 1st PartDocument22 pagesUNIT - 5 - 1st PartR BHARATH VARDHAN REDDYPas encore d'évaluation

- Chapter 4 - SGDocument4 pagesChapter 4 - SGGabriel TomagosPas encore d'évaluation

- Input Output ModuleDocument3 pagesInput Output ModuleJerome 高自立 KoPas encore d'évaluation

- I/O Organizations and PeripheralsDocument30 pagesI/O Organizations and PeripheralsSumit GuptaPas encore d'évaluation

- Lecture 5 - CPU DesignDocument20 pagesLecture 5 - CPU Designnoberth nikombolwePas encore d'évaluation

- OS - Chapter - 6 - Input Output ManagementDocument21 pagesOS - Chapter - 6 - Input Output Managementabelcreed1994Pas encore d'évaluation

- Input Output HardwareDocument6 pagesInput Output Hardwaremmmoneyyyy2Pas encore d'évaluation

- Component of A Digital ComputerDocument15 pagesComponent of A Digital Computerreginaamondi133Pas encore d'évaluation

- Unit 5 - Operating SystemDocument11 pagesUnit 5 - Operating SystemVEDANSH PARGAIEN CO20366Pas encore d'évaluation

- Chapter 1 Computer FundamentalDocument8 pagesChapter 1 Computer FundamentalSeema SehdevPas encore d'évaluation

- University of Engineering and Technology Peshawar: Assignment 4Document5 pagesUniversity of Engineering and Technology Peshawar: Assignment 4Maaz MarwatPas encore d'évaluation

- I-O FuctionDocument5 pagesI-O FuctionDương PhạmPas encore d'évaluation

- 06 - Stallings CH7 Input OutputDocument62 pages06 - Stallings CH7 Input Outputnalhajri038Pas encore d'évaluation

- Module 1 of Computer OrganizationDocument27 pagesModule 1 of Computer OrganizationNimmymolManuelPas encore d'évaluation

- Assignment OnDocument27 pagesAssignment OnTerrigbade TaiwoPas encore d'évaluation

- Computer Architecture: Lecture 6Document25 pagesComputer Architecture: Lecture 6Mohsin AliPas encore d'évaluation

- COA Seminar ReportDocument8 pagesCOA Seminar ReportVijay SankarPas encore d'évaluation

- Input Output Processing (8086)Document31 pagesInput Output Processing (8086)Tech_MX50% (4)

- Computer Organization and Architecture Lecture NotesDocument125 pagesComputer Organization and Architecture Lecture NotesokPas encore d'évaluation

- IO SystemDocument32 pagesIO Systemnanekaraditya06Pas encore d'évaluation

- Assignment No. 2: Computer Organization and Assembly LanguageDocument4 pagesAssignment No. 2: Computer Organization and Assembly LanguageSarmad JavedPas encore d'évaluation

- Computer Architecture Quick NotesDocument2 pagesComputer Architecture Quick NotesAgrippa MungaziPas encore d'évaluation

- Computer Assgnment For Grade 6aDocument14 pagesComputer Assgnment For Grade 6aDebela TesfayePas encore d'évaluation

- Lec 3 - Top View of SystemDocument11 pagesLec 3 - Top View of SystemKimani MaithyaPas encore d'évaluation

- Coa Unit-1Document21 pagesCoa Unit-1singhshiva8082Pas encore d'évaluation

- L20 InterruptDocument18 pagesL20 InterruptRaghavendrachari KPas encore d'évaluation

- Microprocessors and Micro Controllers: 2 Mark Questions With AnswersDocument26 pagesMicroprocessors and Micro Controllers: 2 Mark Questions With AnswersrameshsophidarlaPas encore d'évaluation

- Io Device ManagementDocument56 pagesIo Device Managementbibek gautamPas encore d'évaluation

- Computer Harware 2nd YearDocument12 pagesComputer Harware 2nd Yearrajendhar VarmaPas encore d'évaluation

- Peripheral Devices and I/O InterfacesDocument50 pagesPeripheral Devices and I/O Interfaceskarvind08Pas encore d'évaluation

- Transport Layer: Unit - IVDocument19 pagesTransport Layer: Unit - IVHarishmaPas encore d'évaluation

- Signal Flow GraphDocument48 pagesSignal Flow GraphsufyanPas encore d'évaluation

- Final Year Project TopicsDocument112 pagesFinal Year Project TopicsJyothi BurlaPas encore d'évaluation

- Dir x1560 Datasheet Eu enDocument2 pagesDir x1560 Datasheet Eu enMilosPas encore d'évaluation

- Igad Policy Youth 2022 - Document 1aDocument112 pagesIgad Policy Youth 2022 - Document 1aRICHARD BONYOPas encore d'évaluation

- Reliance Jio Internship Report on Employee MotivationDocument51 pagesReliance Jio Internship Report on Employee MotivationSahas ShettyPas encore d'évaluation

- Literature Review of Online Registration SystemDocument8 pagesLiterature Review of Online Registration Systemzepewib1k0w3100% (1)

- Presentation of Dairy Management SystemDocument35 pagesPresentation of Dairy Management SystemEnola Syawla100% (1)

- System ConceptsDocument4 pagesSystem Conceptsjai232100% (6)

- History of LinuxDocument5 pagesHistory of LinuxBaskarran VijayakumarPas encore d'évaluation

- LogDocument57 pagesLogEva AriantiPas encore d'évaluation

- ZXSM-2500E Specification SummaryDocument65 pagesZXSM-2500E Specification SummarysarfrazatiqPas encore d'évaluation

- BNB List 3742Document443 pagesBNB List 3742Walter MatsudaPas encore d'évaluation

- Saas Solutions On Aws FinalDocument26 pagesSaas Solutions On Aws Finalfawares1Pas encore d'évaluation

- Model Cards For Model ReportingDocument10 pagesModel Cards For Model Reportingoscar Julian Perdomo CharryPas encore d'évaluation

- Amber Krieg ResumeDocument1 pageAmber Krieg Resumeapi-376941376Pas encore d'évaluation

- Jabra Android SDK Developers GuideDocument12 pagesJabra Android SDK Developers GuideEmilio AlejandroPas encore d'évaluation

- UntitledDocument36 pagesUntitledisaac gonzalezPas encore d'évaluation

- 11 - Chapter 5Document22 pages11 - Chapter 5Parth MundhwaPas encore d'évaluation

- Rancang Bangun Sistem Informasi Penjualan Toko Kelontong Winda SlemanDocument16 pagesRancang Bangun Sistem Informasi Penjualan Toko Kelontong Winda Slemanpetty riantiPas encore d'évaluation

- Advanced SAS Interview Questions You'll Most Likely Be AskedDocument27 pagesAdvanced SAS Interview Questions You'll Most Likely Be AskedVibrant PublishersPas encore d'évaluation

- Commercial Building Maintenance and External Cleaning CompanyDocument8 pagesCommercial Building Maintenance and External Cleaning Companybisankhe2Pas encore d'évaluation

- Ups MotherboardDocument5 pagesUps MotherboardMustapha El MaouzouniPas encore d'évaluation

- Addons Mozilla Org en US Firefox Addon Save As PDF Utm SourcDocument5 pagesAddons Mozilla Org en US Firefox Addon Save As PDF Utm SourcThanga PandiPas encore d'évaluation

- Scripting Language - WikipediaDocument9 pagesScripting Language - WikipediaGilbertPas encore d'évaluation

- Teach Yourself Logic 2020 - Peter SmithDocument99 pagesTeach Yourself Logic 2020 - Peter SmithPaolo Pagliaro100% (1)

- Computers & Geosciences Volume 37 Issue 2 2011 [Doi 10.1016%2Fj.cageo.2010.06.008] Faisal Shahzad; Richard Gloaguen -- TecDEM- A MATLAB Based Toolbox for Tectonic Geomorphology, Part 1- Drainage Network Preprocessing AnDocument11 pagesComputers & Geosciences Volume 37 Issue 2 2011 [Doi 10.1016%2Fj.cageo.2010.06.008] Faisal Shahzad; Richard Gloaguen -- TecDEM- A MATLAB Based Toolbox for Tectonic Geomorphology, Part 1- Drainage Network Preprocessing AnCristina CristeaPas encore d'évaluation

- 3 Months Look Ahead PlanDocument6 pages3 Months Look Ahead PlananjnaPas encore d'évaluation

- Contoh CVDocument2 pagesContoh CVBetty Pasaribu100% (1)

- Surge Protector Vs UPS Vs Power StripDocument4 pagesSurge Protector Vs UPS Vs Power StripTransformerOptimusPas encore d'évaluation

- Chip War: The Quest to Dominate the World's Most Critical TechnologyD'EverandChip War: The Quest to Dominate the World's Most Critical TechnologyÉvaluation : 4.5 sur 5 étoiles4.5/5 (227)

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002D'EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Évaluation : 5 sur 5 étoiles5/5 (1)

- Chip War: The Fight for the World's Most Critical TechnologyD'EverandChip War: The Fight for the World's Most Critical TechnologyÉvaluation : 4.5 sur 5 étoiles4.5/5 (82)

- 8051 Microcontroller: An Applications Based IntroductionD'Everand8051 Microcontroller: An Applications Based IntroductionÉvaluation : 5 sur 5 étoiles5/5 (6)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102D'EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Évaluation : 5 sur 5 étoiles5/5 (2)

- Amazon Web Services (AWS) Interview Questions and AnswersD'EverandAmazon Web Services (AWS) Interview Questions and AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (3)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XD'EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XÉvaluation : 3 sur 5 étoiles3/5 (2)

- Model-based System and Architecture Engineering with the Arcadia MethodD'EverandModel-based System and Architecture Engineering with the Arcadia MethodPas encore d'évaluation

- Dancing with Qubits: How quantum computing works and how it can change the worldD'EverandDancing with Qubits: How quantum computing works and how it can change the worldÉvaluation : 5 sur 5 étoiles5/5 (1)

- Creative Selection: Inside Apple's Design Process During the Golden Age of Steve JobsD'EverandCreative Selection: Inside Apple's Design Process During the Golden Age of Steve JobsÉvaluation : 4.5 sur 5 étoiles4.5/5 (49)

- 2018 (40+) Best Free Apps for Kindle Fire Tablets: +Simple Step-by-Step Guide For New Kindle Fire UsersD'Everand2018 (40+) Best Free Apps for Kindle Fire Tablets: +Simple Step-by-Step Guide For New Kindle Fire UsersPas encore d'évaluation

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxD'EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxPas encore d'évaluation

- From Cell Phones to VOIP: The Evolution of Communication Technology - Technology Books | Children's Reference & NonfictionD'EverandFrom Cell Phones to VOIP: The Evolution of Communication Technology - Technology Books | Children's Reference & NonfictionPas encore d'évaluation

- Electronic Dreams: How 1980s Britain Learned to Love the ComputerD'EverandElectronic Dreams: How 1980s Britain Learned to Love the ComputerÉvaluation : 5 sur 5 étoiles5/5 (1)

- Cancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionD'EverandCancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionÉvaluation : 5 sur 5 étoiles5/5 (2)

- The No Bull$#!£ Guide to Building Your Own PC: No Bull GuidesD'EverandThe No Bull$#!£ Guide to Building Your Own PC: No Bull GuidesPas encore d'évaluation

![Computers & Geosciences Volume 37 Issue 2 2011 [Doi 10.1016%2Fj.cageo.2010.06.008] Faisal Shahzad; Richard Gloaguen -- TecDEM- A MATLAB Based Toolbox for Tectonic Geomorphology, Part 1- Drainage Network Preprocessing An](https://imgv2-2-f.scribdassets.com/img/document/283133569/149x198/8e251c988e/1443552163?v=1)