Académique Documents

Professionnel Documents

Culture Documents

Ec6404 Linear Integrated Circuits Nov Dec 2017 Reg 2013

Transféré par

Mohanaprakash Ece0 évaluation0% ont trouvé ce document utile (0 vote)

40 vues3 pagesEc6404 Linear Integrated Circuits Nov Dec 2017

Copyright

© © All Rights Reserved

Formats disponibles

PDF ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentEc6404 Linear Integrated Circuits Nov Dec 2017

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

40 vues3 pagesEc6404 Linear Integrated Circuits Nov Dec 2017 Reg 2013

Transféré par

Mohanaprakash EceEc6404 Linear Integrated Circuits Nov Dec 2017

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 3

jv A

B..vo[AlU

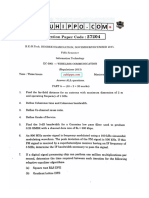

| BE/B-Tech, DEGREE EXAMINATION, NOVEMBER/DECEMBER 2017

i Fourth Semester

Electronics and Communication Engineering

f EC 6404 — LINEAR INTEGRATED CIRCUITS

(Common to Medical Electronics/Robotics and Automation Engineering)

f (Regulations 2013)

ime : Three Hours Maximum : 100 Marks

Answer ALL questions

PART-A (10x2=20 Marks)

. Draw the de transfer characteristics of a BJT differential amplifier and define

differential mode input voltages.

. The power supply rejection of an op-amp is 80dB for a 1V change in supply voltage.

Calculate the change in offset voltage.

3. State the limitations of an ideal integrator.

How will you realize a peak detector using a precision rectifier ?

cays

i, Mention the need of pre-distortion circuits in Gilbert analog multiplier and how is

the configuration of Gilbert multiplier done with pre-distortion circuits.

|. Define capture-range and lock-range of PLL.

+ How is the classification of A/D converters carried out based on their operational

features ?

+ Find the number of resistors required for an 8-bit weighted resistor D/A converter.

Consider the smallest resistance is R and obtain those resistance values.

+ Define current transfer ratio of an opto-coupler.

| Draw a fixed voltage regulator circuit and state its operations.

‘Yeauhippo.com yy

rr

2

50440

(5*13=66 M,

11.

12.

13.

14,

PART -B

a) i) With a help of a block diagram, explain the various stages present in an

operational amplifier.

ii) Draw the transfer chara A

the linear and non-linear operation.

on

ting amplifier circuits of an op-amp i

he expressions for the closed-loop

cteristics of an operational amplifier and explain

b) i) Draw the inverting and non-inve'

closed-loop configuration. Obtain t

gain in these circuits.

ii) Perform the AC analysis of the operational amplifier 741.

nal amplifier, integrator is

i) For performing differentiation in an operatior

preferred to differentiator — Explain.

ii) What is an instrumentation amplifier ? Draw a system whose gain is

controlled by a variable resistance.

(OR)

b) i) Design a clipper circuit for a clipping level of +0.61V, given an input sir

wave signal of 0.5V peak. Assume the gain of the amplifier is 12 and it

has an input resistance of 1k-ohm connected.

ii) Design a second order Butterworth low-pass filter having upper cut-off

frequency of 2.5 kHz.

a)

a) i) Write notes on basic analog multiplication techniques.

ii) Explain the operation of a variable transconductance multiplier circuit.

Derive the expression for its output voltage.

on

b) Derive the expression for free running frequency of voltage controlled

ii) Explain the process of FSK demodulation using PLL. How is ili

P 5 the stabilit

the frequency obtained in a PLL by the use of voltage controlled -scilai

a) i) Explain in detail on the operational feat it weil i

eee atures of 4-bit weighted resistor

ii) Differentiate betwe

coment ‘een current mode and voltage mode R-2R ladder D/A

(OR)

“8: 50440

b) i) With a neat block diagram, explain the operation of successive approximation

type A/D converter in detail. 6)

ii) An 8-bit A/D converter accepts an input voltage signal of range 0 to 9V.

What is the minimum value of the input voltage required for generating a

change of 1 least significant bit ? Specify the digital output for an input

voltage of 4 V. What input voltage will generate all 1s at the A/D converter

? (8)

oe ‘

. a) i) With neat diagram, explain the operation of an astable and monostable

multivibrators. (3)

ii) Draw the functional diagram and connection diagram of a low voltage

regulator and explain. (6)

(OR)

») i) Draw the block diagram of a typical IC audio power amplifier and briefly

explain their salient features. ©

ii) Design a frequency to voltage converter using IC VFC 32 for a full scale

output of 8 V for a full scale input frequency of 80 kHz with a maximum

cman e

PART-C (1*15=15 Marks)

8) i) Design a differentiator to produce an output of 4 V when the input changes

by 2 V in 60 micro seconds. 6

ii) A PLL has a free running frequency of 400 kHz and the band-width of the

Jow pass filter is 8 kHz. Will the loop tend to acquire lock for an input signal

of 550 kHz ? Explain, In this case, assume that the phase detector

produces sum and difference frequency components. (10)

(OR)

>) i) Design a square wave generator using 555 timer for a frequency of 120 Hz

and 60% duty cycle, Assume C= 0.2 uF. M

ii) For a 4-bit R-2R ladder D/A converter assume that the full scale voltage is

12 V. Calculate the step change in output voltage on input varying from

1001 to 1111. ®

Vous aimerez peut-être aussi

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- List of Software Companies in IndiaDocument158 pagesList of Software Companies in IndiaSurya HarishPas encore d'évaluation

- CN 4th Unit MCQ 160Document30 pagesCN 4th Unit MCQ 160Mohanaprakash EcePas encore d'évaluation

- CN 5th Unit MCQ 173Document25 pagesCN 5th Unit MCQ 173Mohanaprakash EcePas encore d'évaluation

- Ap7301 Emi&Emc NotesDocument126 pagesAp7301 Emi&Emc NotesMohanaprakash EcePas encore d'évaluation

- CN 3rd Unit MCQ 130Document19 pagesCN 3rd Unit MCQ 130Mohanaprakash Ece100% (1)

- CN MCQ All Units 74Document16 pagesCN MCQ All Units 74Mohanaprakash EcePas encore d'évaluation

- Ec 6001 Apr May 2018Document2 pagesEc 6001 Apr May 2018Mohanaprakash EcePas encore d'évaluation

- Ec6801 Wireless Communication Reg 2013 Nov Dec 2015Document4 pagesEc6801 Wireless Communication Reg 2013 Nov Dec 2015Mohanaprakash EcePas encore d'évaluation

- EC6801Document2 pagesEC6801Mohanaprakash EcePas encore d'évaluation

- TCP/IP Protocol Suite and Networking Fundamentals QuizDocument39 pagesTCP/IP Protocol Suite and Networking Fundamentals QuizMohanaprakash EcePas encore d'évaluation

- IP Fundamentals Quiz: Key Concepts on IP Addressing, ICMP, Fragmentation & MoreDocument28 pagesIP Fundamentals Quiz: Key Concepts on IP Addressing, ICMP, Fragmentation & MoreMohanaprakash EcePas encore d'évaluation

- MPMC Ec8691 Lab ManualDocument107 pagesMPMC Ec8691 Lab ManualMohanaprakash Ece71% (7)

- WCDocument1 pageWCJ.Gowri ShankarPas encore d'évaluation

- WCDocument1 pageWCJ.Gowri ShankarPas encore d'évaluation

- Digital Manual FOR II CSEDocument49 pagesDigital Manual FOR II CSEMohanaprakash EcePas encore d'évaluation

- NewsletterDocument2 pagesNewsletterMohanaprakash EcePas encore d'évaluation

- Aph 2018-19Document258 pagesAph 2018-19mailabhikeshPas encore d'évaluation

- Final - Approval Process Handbook 2017-18Document274 pagesFinal - Approval Process Handbook 2017-18Mohanaprakash EcePas encore d'évaluation

- Digital Manual FOR II CSEDocument49 pagesDigital Manual FOR II CSEMohanaprakash EcePas encore d'évaluation

- Readmission Transfer Later Entry InstructionsDocument1 pageReadmission Transfer Later Entry InstructionsMohanaprakash EcePas encore d'évaluation

- Gradient Magnitude Similarity DeviationDocument12 pagesGradient Magnitude Similarity DeviationMohanaprakash EcePas encore d'évaluation

- Computer Architecture Two Mark QuestionsDocument9 pagesComputer Architecture Two Mark QuestionsMohanaprakash EcePas encore d'évaluation

- Gradian Magnitude Similarity DeviationDocument4 pagesGradian Magnitude Similarity DeviationMohanaprakash EcePas encore d'évaluation

- Stationary and WSS Processes DefinedDocument1 pageStationary and WSS Processes DefinedMohanaprakash EcePas encore d'évaluation

- Gradient Magnitude Similarity DeviationDocument12 pagesGradient Magnitude Similarity DeviationMohanaprakash EcePas encore d'évaluation

- EVS 2marks - 2012 EditionDocument20 pagesEVS 2marks - 2012 EditionMohanaprakash EcePas encore d'évaluation

- QP Esd Lab IiDocument1 pageQP Esd Lab IiMohanaprakash EcePas encore d'évaluation

- 07/03/15 1 BiodiversityDocument10 pages07/03/15 1 BiodiversityMohanaprakash EcePas encore d'évaluation

- Esd Lab Record - 14122014Document100 pagesEsd Lab Record - 14122014Mohanaprakash EcePas encore d'évaluation