Académique Documents

Professionnel Documents

Culture Documents

Informe Logica Combinacional

Transféré par

Felipe Guevara0 évaluation0% ont trouvé ce document utile (0 vote)

11 vues2 pagesinforme-logica-combinacional

Titre original

informe-logica-combinacional

Copyright

© © All Rights Reserved

Formats disponibles

PDF, TXT ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentinforme-logica-combinacional

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

11 vues2 pagesInforme Logica Combinacional

Transféré par

Felipe Guevarainforme-logica-combinacional

Droits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF, TXT ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 2

Informe Lógica Combinacional y Conceptos Básicos FPGA y Verilog

Juan Felipe Guevara Rodrı́guez, Hair Sebastián López Criollo, Brajhan Andrés Urián Flórez

I. E NTRADAS IV. I NTERRUPTORES

El dispositivo tiene 5 entradas, A y B que son de 3 bits, La fpga tiene disponibles 8 interruptores, y la disposición

Cin que siempre se mantendrá en cero y Selec0 y Selec1 fue la siguiente:

que son de 1 bit. 1) Los 3 bits de la entrada A son SW0, SW1 y SW2.

Donde cada interruptor corresponde a los pesos, es

decir SW0 es 20 , SW1 es 21 y SW2 es 22

II. M ÓDULOS

2) Los 3 bits de la entrada B son SW3, SW4 y SW5.

1) El comparador, tiene como función comparar los dos Funcionan igual que en la entrada A, explicada ante-

valores ingresados, luego muestra solamente el valor riormente.

mayor en la pantalla, su salida es de 6 bits. 3) Select0 y Select1 son SW6 y SW7 respectivamente.

2) Módulo de paridad, su función es determinar si el Estos últimos dos, son los que seleccionan el módulo,

valor, o los valores ingresados tienen una cantidad par cuando están en la posición 0, está seleccionado el módulo

o impar de unos, la pantalla muestra un 1 si tiene un de sumador, cuando están los dos en la posición 1, está

número impar de unos y un 0 si tiene un número par seleccionado el módulo de paridad, cuando SW6 está en 0 y

de unos. Por ejemplo, al ingresar el número 4, que en SW7 en 1, se selecciona el módulo del restador y por último,

binario serı́a 0100, en la pantalla saldrı́a un uno. cuando SW6 está en 1 y SW7 en 0 se selecciona el modulo

3) El sumador(msum), tiene un bloque en su interior de comparación.

llamado sumc, que es quien se encarga de hacer la

V. F UNCIONAMIENTO DEL 7 SEGMENTOS

operación de suma de 1 bit. Y el módulo msum repite

este proceso 3 veces. La señal que sale del Mux tiene 6 bits, ası́ que para que

4) El restador(mrest), su función es realizar la operación el display de 7 segmentos pueda funcionar correctamente, es

de resta entre los valores ingresados. Los bloques necesario el uso de un decodificador que convierta la señal

rest 1 representan la estructura condicional: en caso de salida en 8 bits, para una mejor explicación se tomará

de que el quinto bit de rest (salida del restador) sea una lı́nea de código.

1, (lo que indica que hay un número negativo) los bit (Sal==6’b000001) ? 8’b11111001://+ La parte de la

1, 2 y 3 toman los valores de la salida del bloque izquierda de la lı́nea de código, muestra seis números en

magnitud, los demás bit de rest 1 corresponden a los código binario, los seis bits que serán convertidos en ocho

bit de rest. Si el quinto bit de rest es 0, los bit de bits. Donde los primeros cuatro bits, de derecha a izquierda,

rest 1 son iguales a los bit de rest. Ası́ pues la salida son la magnitud del número que dio como resultado de la

del bloque mag (que es magnitud) sólo se usa cuando operación. El quinto bit indica si el número es negativo o

el número es negativo, ya que calcula su valor absoluto, no, cosa que puede ser posible por la resta, si es negativo se

sin embargo en caso de que su entrada sea positiva, la indica con un 1, de lo contrario va un 0. El último bit, es el

salida no corresponderá a la magnitud verdadera por que se encarga de la igualdad.

lo que es necesario realizar el condicional mencionado Ahora bien, la parte de la derecha indica la disposición de

anteriormente. los led’s en el 7 segmentos, que trabaja con lógica negativa,

se encienden con un0, y permanecen apagados con un 1.

Los 7 bits de derecha a izquierda encienden los led’s. El

III. C ONEXIONES

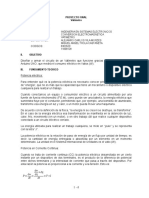

7 segmentos tiene una letra para cada segmento como se

Las entradas A y B se conectan a los 4 módulos, com- muestra en la siguiente figura.

parador, msum, mrest y paridad. El Cin en cambio sólo va a

2 de los módulos, msum y mrest. Mientras que las entradas

restantes, Selec0 y Selec1 se conectan directo a cada bloque

del Mux, al igual que cada módulo, estos van a los bloques

que tiene el multiplexor en su interior, que en total son 4.

Como las salidas de los módulos son de 6 bits, la salida del

Mux es también de 6 bits, por eso esta salida se conecta al Fig. 1. Configuración 7 segmentos

dec, que luego de procesarla genera una salida de 8 bits para

que el 7segmentos pueda interpretar la señal y encender los Por lo tanto en el ejemplo que se presentó, sólo estarán

led’s requeridos. encendidos los segmentos que pertenecen a las letras b y c,

formando un 1. Y el último bit, es el encargado de encender

al punto, cuando se trata de un número negativo.

Vous aimerez peut-être aussi

- Estacion MeteorologicaDocument2 pagesEstacion MeteorologicaFelipe GuevaraPas encore d'évaluation

- Aplicacion MotorDC PDFDocument25 pagesAplicacion MotorDC PDFFelipe GuevaraPas encore d'évaluation

- Proyecto Clase MagistralDocument5 pagesProyecto Clase MagistralFelipe GuevaraPas encore d'évaluation

- Aplicacion MotorDCDocument7 pagesAplicacion MotorDCFelipe GuevaraPas encore d'évaluation

- Caract. InstrumentaciónDocument2 pagesCaract. InstrumentaciónFelipe GuevaraPas encore d'évaluation

- Cuántica MayoDocument1 pageCuántica MayoFelipe GuevaraPas encore d'évaluation

- CPTYPTDocument1 pageCPTYPTFelipe GuevaraPas encore d'évaluation

- Taller Final Señales 2Document18 pagesTaller Final Señales 2Felipe GuevaraPas encore d'évaluation

- Cuántica MayoDocument1 pageCuántica MayoFelipe GuevaraPas encore d'évaluation

- Trabajo CuánticaDocument2 pagesTrabajo CuánticaFelipe GuevaraPas encore d'évaluation

- Ensayo Fresas SalvajesDocument11 pagesEnsayo Fresas SalvajesFelipe GuevaraPas encore d'évaluation

- Biblia de Los Trucos para Windows E InternetDocument180 pagesBiblia de Los Trucos para Windows E Internetmagatscribd100% (74)

- Manual GoyaDocument43 pagesManual GoyaSeteBoadoPedrido100% (2)

- Manual Destilador Purelab Option ElgaDocument46 pagesManual Destilador Purelab Option ElgamaraperezlindoPas encore d'évaluation

- Definiciones y Parametros de CircuitosDocument31 pagesDefiniciones y Parametros de Circuitosluialarcon2175% (4)

- Apu - Instalaciones ElectricasDocument188 pagesApu - Instalaciones ElectricasArquidark73% (11)

- Practica 1 Circuitos Electricos y ElectronicosDocument10 pagesPractica 1 Circuitos Electricos y ElectronicosJúnior Jose Solano RKS100% (1)

- Practica 6 Ley de KirchoffDocument5 pagesPractica 6 Ley de KirchoffLuis Jaime PerezPas encore d'évaluation

- Segunda Parcial Arquitectura de Computadoras.Document23 pagesSegunda Parcial Arquitectura de Computadoras.alexisllamasPas encore d'évaluation

- M2 - Trabajo Práctico #2Document5 pagesM2 - Trabajo Práctico #2Pancho FuentesPas encore d'évaluation

- Informe de Laboratorio de Voltaje 20211196116Document3 pagesInforme de Laboratorio de Voltaje 20211196116ANA MARIA POLANIA MONTILLA0% (1)

- Practica 24Document3 pagesPractica 24RuloEduardoPas encore d'évaluation

- Práctica 2 Circuitos PDFDocument19 pagesPráctica 2 Circuitos PDFBryan0% (1)

- Preinforme Practica 3 Electronica DigitalDocument9 pagesPreinforme Practica 3 Electronica DigitalRobbin Roman100% (1)

- 2 CarsaDocument2 pages2 CarsaSamuel BustillosPas encore d'évaluation

- FUENTE DE 9v A 5 VDocument24 pagesFUENTE DE 9v A 5 VcristianvarPas encore d'évaluation

- Parte 2 Solo LaboratoriosDocument23 pagesParte 2 Solo LaboratoriosCarlos MendoPas encore d'évaluation

- Instalaciones Eléctricas PresentaciónDocument44 pagesInstalaciones Eléctricas PresentaciónJennifer HernandezPas encore d'évaluation

- Ejercicios Alterna IIIDocument3 pagesEjercicios Alterna IIIDavid Palanca MartínezPas encore d'évaluation

- Reglas Del JuegoDocument3 pagesReglas Del JuegoRamses VegaPas encore d'évaluation

- Guia Primeros Pasos Con Un SSDDocument37 pagesGuia Primeros Pasos Con Un SSDRainoxPas encore d'évaluation

- Teoria ImagenesDocument15 pagesTeoria ImagenesDennis BurgasiPas encore d'évaluation

- f1.g8.Pp Formato Listado General Confirmacion Metrologica e Inspeccion de Operacion de Los Equipos de Medicion v3Document1 pagef1.g8.Pp Formato Listado General Confirmacion Metrologica e Inspeccion de Operacion de Los Equipos de Medicion v3Diana GutierrezPas encore d'évaluation

- Potenciometro y PH MetroDocument9 pagesPotenciometro y PH MetroSara RsPas encore d'évaluation

- 2128-1 Condiciones No NormalizadasDocument10 pages2128-1 Condiciones No NormalizadasOmar Reinoso TigrePas encore d'évaluation

- E1 Plus 1Document2 pagesE1 Plus 1daroltecPas encore d'évaluation

- Sistema IT MDocument36 pagesSistema IT Momar100% (2)

- Inversor de Voltaje de 150 Watts Con 555 y MOSFETsDocument2 pagesInversor de Voltaje de 150 Watts Con 555 y MOSFETstelmarocioPas encore d'évaluation

- Maquinas Electricas Capitulo 7Document13 pagesMaquinas Electricas Capitulo 7JuandeDiosPas encore d'évaluation

- Laboratorio Virtual CapacitoresDocument8 pagesLaboratorio Virtual CapacitoresJulySepulvedaArroyavePas encore d'évaluation

- Sistema de Control MecatronicaDocument9 pagesSistema de Control MecatronicaMaria Enedina ContrerasPas encore d'évaluation

- Vatimetro Con ArduinoDocument6 pagesVatimetro Con ArduinomiguelPas encore d'évaluation