Académique Documents

Professionnel Documents

Culture Documents

CTS experiments comparison

Transféré par

manojkumarDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

CTS experiments comparison

Transféré par

manojkumarDroits d'auteur :

Formats disponibles

CTS activities Experiment 1 Experiment 2

Drive strengths 2,4,8 All

Cells BUFF BUFF

NBUFFX2_RVT,

Inputs NBUFFX2_RVT, NBUFFX4_RVT,

Clock cell names NBUFFX4_RVT, NBUFFX8_RVT,

NBUFFX8_RVT NBUFFX16_RVT,

NBUFFX32_RVT

Total number of clock cells 0+586+344 0+586+344

Insertion Delay (Longest path delay) 4.5113 4.5113

Max Global skew (Max ID - Min ID) 2.0858 2.0858

Clock Tree power (report_power) 2.23E+03 2.22E+03

Congestion Vertical utilization 9.21% 9.13%

(report_congestio

Outputs n) Horizontal utilization 12.28% 12.16%

Timing Setup violations 17 16

(clock_opt) Hold violations 143 144

inst Count 7083 7116

Buf/Inv Count 1844 1874

No.of Levels 281(1+216+64) 281(1+216+64)

Experiment 3 Experiment 4 Experiment 5 Experiment 6

2,4,8 All 2,4,8 All

INV INV BUFF & INV BUFF & INV

NBUFFX2_RVT,

NBUFFX4_RVT,

NBUFFX8_RVT,

INVX0_RVT, NBUFFX2_RVT, NBUFFX16_RVT,

INVX1_RVT, NBUFFX4_RVT, NBUFFX32_RVT,

INVX2_RVT, INVX2_RVT, NBUFFX8_RVT, INVX0_RVT,

INVX4_RVT, INVX4_RVT, INVX2_RVT, INVX1_RVT,

INVX8_RVT INVX8_RVT, INVX4_RVT, INVX2_RVT,

INVX16_RVT, INVX8_RVT INVX4_RVT,

INVX32_RVT INVX8_RVT,

INVX16_RVT,

INVX32_RVT

0+586+344 0+586+344 0+586+344 0+586+344

4.5124 4.5113 4.5112 4.511

2.0866 2.0858 2.0857 2.0858

2.22E+03 2.23E+03 2.22E+03 2.22E+03

9.44% 9.37% 9.17% 9.21%

12.86% 12.49% 12.23% 12.30%

16 17 17 16

143 143 143 144

7612 7682 7072 7054

2391 2458 1845 1820

281(1+216+64) 281(1+216+64) 281(1+216+64) 281(1+216+64)

Vous aimerez peut-être aussi

- HEF4538BDocument14 pagesHEF4538BAlireza RahimiPas encore d'évaluation

- General Description: Dual Retriggerable Precision Monostable MultivibratorDocument17 pagesGeneral Description: Dual Retriggerable Precision Monostable Multivibratorsajad hejaziPas encore d'évaluation

- Mop of Setup Ret in Sran 18sp - v1Document13 pagesMop of Setup Ret in Sran 18sp - v1RizkiPas encore d'évaluation

- 052-Tech Note - Proc, Tranducer Diagnostic Test (4.7 SW)Document3 pages052-Tech Note - Proc, Tranducer Diagnostic Test (4.7 SW)Saad ElhemediPas encore d'évaluation

- 74HC4538 74HCT4538: 1. General DescriptionDocument24 pages74HC4538 74HCT4538: 1. General DescriptionremikhaledPas encore d'évaluation

- Operating Values and Measurements for the Dyna Ross CompressorDocument1 pageOperating Values and Measurements for the Dyna Ross Compressorantonio martosPas encore d'évaluation

- Switch Chip Features GuideDocument21 pagesSwitch Chip Features GuideRuben ChengPas encore d'évaluation

- Adobe Scan Nov 06, 2023Document9 pagesAdobe Scan Nov 06, 2023kiransuhas62Pas encore d'évaluation

- 20BEE074 MD Rashid Analog Electronics Lab Experiment-6Document7 pages20BEE074 MD Rashid Analog Electronics Lab Experiment-6Thor OdinsonPas encore d'évaluation

- MANUAL DATA SHEET XENAX® Xvi48V8Document101 pagesMANUAL DATA SHEET XENAX® Xvi48V8Aldin BeganovicPas encore d'évaluation

- Daily Progress Welding Joint Report Wharf Boat Landing Upper StructureDocument2 pagesDaily Progress Welding Joint Report Wharf Boat Landing Upper StructureAditya Hadi SPas encore d'évaluation

- Nama: Irfan Efrizal NIM: 17501241032: RegressionDocument3 pagesNama: Irfan Efrizal NIM: 17501241032: RegressionedwinPas encore d'évaluation

- TM - Mini VRF ODU BDocument123 pagesTM - Mini VRF ODU BDelpoPas encore d'évaluation

- REN Isl81401-01a DST 20210528Document47 pagesREN Isl81401-01a DST 20210528Quoc phan congPas encore d'évaluation

- Proclim ATOM VRF Multi 2020 - CompressedDocument114 pagesProclim ATOM VRF Multi 2020 - CompressedBabi Dou100% (1)

- Kenwood TS-530SP Instructions ManualDocument38 pagesKenwood TS-530SP Instructions ManualYayok S. AnggoroPas encore d'évaluation

- Ve Pioneer pl-516 ServiceDocument29 pagesVe Pioneer pl-516 ServiceJulien AlfieriPas encore d'évaluation

- 3 26 doneDocument3 pages3 26 donesthanarayan407Pas encore d'évaluation

- 3 26Document2 pages3 26sthanarayan407Pas encore d'évaluation

- Korg DW-8000 Service ManualDocument47 pagesKorg DW-8000 Service ManualMatthew DavidsonPas encore d'évaluation

- ST2106 & ST2107Document66 pagesST2106 & ST2107kingarpit240% (1)

- Switch Lab: Etherchannel Negotiation Protocols: Pagp: ObjectiveDocument3 pagesSwitch Lab: Etherchannel Negotiation Protocols: Pagp: ObjectiveDaniel HailePas encore d'évaluation

- ST24LC21B, ST24LW21 ST24FC21, ST24FC21B, ST24FW21: 1 Kbit (x8) Dual Mode Serial EEPROM For Vesa Plug & PlayDocument22 pagesST24LC21B, ST24LW21 ST24FC21, ST24FC21B, ST24FW21: 1 Kbit (x8) Dual Mode Serial EEPROM For Vesa Plug & Playdayne81sPas encore d'évaluation

- Anomaly DetectionDocument13 pagesAnomaly DetectionkarlbifuPas encore d'évaluation

- Assignment 3 SolutionDocument2 pagesAssignment 3 SolutionshwetapooranibalasubramanianPas encore d'évaluation

- 74HC2G14 74HCT2G14: 1. General DescriptionDocument21 pages74HC2G14 74HCT2G14: 1. General DescriptionNicolas PeresPas encore d'évaluation

- Hp71 Ids HardwareDocument184 pagesHp71 Ids HardwareMarcos NavarroPas encore d'évaluation

- ECD Entire SemDocument76 pagesECD Entire SemAniruddhPas encore d'évaluation

- FALLSEM2021-22 CSE2006 ETH VL2021220104060 Reference Material II 23-11-2021 8087 Arch ProgramDocument51 pagesFALLSEM2021-22 CSE2006 ETH VL2021220104060 Reference Material II 23-11-2021 8087 Arch ProgramAakash kumar shahPas encore d'évaluation

- Acco4093 - 2nd Evals - SummaryDocument2 pagesAcco4093 - 2nd Evals - SummaryMaryTherese VillanuevaPas encore d'évaluation

- Quintel Product Datasheet QS4658-3 (700-2400 4ft 65deg) FEB 2017 (Rev 3.2)Document2 pagesQuintel Product Datasheet QS4658-3 (700-2400 4ft 65deg) FEB 2017 (Rev 3.2)gggPas encore d'évaluation

- Ear T Hquakeengi Neer I NG: I .Nscp2015Sei Smi Canalysi S (Stati Cforceprocedure)Document2 pagesEar T Hquakeengi Neer I NG: I .Nscp2015Sei Smi Canalysi S (Stati Cforceprocedure)matthew cometaPas encore d'évaluation

- RET Configuration HuaweiDocument209 pagesRET Configuration HuaweiAhmad Zulfian TojibPas encore d'évaluation

- PIC16f690 program for pulse displayDocument5 pagesPIC16f690 program for pulse displayandres zegarraPas encore d'évaluation

- Data Transfers, Addressing, and ArithmeticDocument23 pagesData Transfers, Addressing, and ArithmeticbsudheertecPas encore d'évaluation

- Megger SMRT Differential Relay Settings HelpDocument15 pagesMegger SMRT Differential Relay Settings Helpmuhammad awaisPas encore d'évaluation

- Lab4 and P - MergedDocument8 pagesLab4 and P - MergedAnonymousPas encore d'évaluation

- UTERUSDocument6 pagesUTERUSsneha ravichandranPas encore d'évaluation

- Attribute - Study - Report NP Chart FormatDocument1 pageAttribute - Study - Report NP Chart FormatM.saravananPas encore d'évaluation

- Standard Indication Instrument Indication (Bar) Average Pressure Electrical X1 X2 X3 X4 X5 (Bar) (Ma)Document20 pagesStandard Indication Instrument Indication (Bar) Average Pressure Electrical X1 X2 X3 X4 X5 (Bar) (Ma)Anwar hidayatPas encore d'évaluation

- Netflow Analysis CiscoDocument20 pagesNetflow Analysis Ciscohola amigoPas encore d'évaluation

- DSP LAB MergedDocument48 pagesDSP LAB Mergednoorullah syedPas encore d'évaluation

- 74LVC1GX04: 1. General DescriptionDocument18 pages74LVC1GX04: 1. General DescriptionAmirPas encore d'évaluation

- Fa CSC508Document14 pagesFa CSC508Muhammad IsfahanPas encore d'évaluation

- ST - Anne'S: Multiple Choice Questions UNIT-2 (50X1 50 Marks)Document6 pagesST - Anne'S: Multiple Choice Questions UNIT-2 (50X1 50 Marks)St. Anne's CET (EEE Department)Pas encore d'évaluation

- Manual Invec2Document254 pagesManual Invec2Sergio Sevilla Cruz57% (7)

- Low Noise Operational Amplifiers: DatasheetDocument43 pagesLow Noise Operational Amplifiers: DatasheetMisael GonzalezPas encore d'évaluation

- Factor Analysis: NotesDocument8 pagesFactor Analysis: NotesMitram 2022Pas encore d'évaluation

- 24AA128/24LC128/24FC128: 128K I C Serial EEPROMDocument44 pages24AA128/24LC128/24FC128: 128K I C Serial EEPROMJosemar M. FerreiraPas encore d'évaluation

- OpenECU-CCS FaultListDocument18 pagesOpenECU-CCS FaultListsaranakom cheecharoenPas encore d'évaluation

- KA CARE Timetable - Eng OnlyDocument7 pagesKA CARE Timetable - Eng OnlymmcdonaldPas encore d'évaluation

- Anomalies in Heavy Flavor Jets at CDF: G.Apollinari-FermilabDocument33 pagesAnomalies in Heavy Flavor Jets at CDF: G.Apollinari-Fermilabas d-fPas encore d'évaluation

- DGIF ControlsDocument16 pagesDGIF ControlskuchowPas encore d'évaluation

- Jumper Setting & Connector List - v1.1Document12 pagesJumper Setting & Connector List - v1.1DeniMestiWidiantoPas encore d'évaluation

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsD'EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsÉvaluation : 1 sur 5 étoiles1/5 (1)

- MoP - Management SWITCH & UAT SDC v0.1Document58 pagesMoP - Management SWITCH & UAT SDC v0.1Samuel ChristianPas encore d'évaluation

- Data SheetDocument58 pagesData SheetCruzmary AriasPas encore d'évaluation

- 4G - MAPA - GA - Deviation Summary - 20201207Document22 pages4G - MAPA - GA - Deviation Summary - 20201207Nino BongoyPas encore d'évaluation

- Hold Fix M (1) .TCL SubmititDocument6 pagesHold Fix M (1) .TCL SubmititmanojkumarPas encore d'évaluation

- CrosstalkDocument85 pagesCrosstalkSreyas MohanPas encore d'évaluation

- tc3 Tutorial GCA FINALDocument42 pagestc3 Tutorial GCA FINALmanojkumarPas encore d'évaluation

- Icc2 Useful CommandsDocument4 pagesIcc2 Useful Commandssudhakar kandi83% (6)

- An ECO Approach at Silicon-Freeze Stage: Victor Soh Realtek Singapore Pte LTDDocument20 pagesAn ECO Approach at Silicon-Freeze Stage: Victor Soh Realtek Singapore Pte LTDmanojkumarPas encore d'évaluation

- Broadband Cumulative Unbilled Usage - 08572-295710 PDFDocument1 pageBroadband Cumulative Unbilled Usage - 08572-295710 PDFmanojkumarPas encore d'évaluation

- Explore Your Design With These Useful Single-Line Dbget Scripts in InnovusDocument7 pagesExplore Your Design With These Useful Single-Line Dbget Scripts in InnovusmanojkumarPas encore d'évaluation

- 4.fixing Hold Time Violations by Inserting Delay at The Data Path EndpointDocument3 pages4.fixing Hold Time Violations by Inserting Delay at The Data Path EndpointmanojkumarPas encore d'évaluation

- 5.script To Report The Filler Cells in A DesignDocument2 pages5.script To Report The Filler Cells in A DesignmanojkumarPas encore d'évaluation

- How CRPR Handles Dynamically Switched Related ClocksDocument4 pagesHow CRPR Handles Dynamically Switched Related ClocksmanojkumarPas encore d'évaluation

- Book 1Document3 pagesBook 1manojkumarPas encore d'évaluation

- BookUpto12ticketsinamonthbylinkingAadhaar PDFDocument10 pagesBookUpto12ticketsinamonthbylinkingAadhaar PDFnagaraju chariPas encore d'évaluation

- LP Sign OffDocument11 pagesLP Sign OffmanojkumarPas encore d'évaluation

- 4 Hybris Install PDFDocument6 pages4 Hybris Install PDFmanojkumarPas encore d'évaluation

- Calculating Toggle Rate in PrimeTime PX & Power CompilerDocument3 pagesCalculating Toggle Rate in PrimeTime PX & Power CompilermanojkumarPas encore d'évaluation

- Clock Concurrent Optimization: Paul Cunningham, Marc Swinnen, Steev Wilcox Electronic Design Processes April 10, 2009Document25 pagesClock Concurrent Optimization: Paul Cunningham, Marc Swinnen, Steev Wilcox Electronic Design Processes April 10, 2009manojkumar100% (1)

- Double-Patterning ConceptsDocument2 pagesDouble-Patterning ConceptsmanojkumarPas encore d'évaluation

- Multi Level Physical Hierarchy FloorplanningDocument8 pagesMulti Level Physical Hierarchy FloorplanninghardeepPas encore d'évaluation

- Innovus Foundation Flows Guide May2018Document7 pagesInnovus Foundation Flows Guide May2018manojkumarPas encore d'évaluation

- Mentorpaper 73527Document9 pagesMentorpaper 73527manojkumarPas encore d'évaluation

- IR-Induced Clock Jitter Extraction and Improvement: Kenny Chen & James SuDocument6 pagesIR-Induced Clock Jitter Extraction and Improvement: Kenny Chen & James SumanojkumarPas encore d'évaluation

- Case Study of Complex Full Chip Low Power Implementation in 16nm NodeDocument32 pagesCase Study of Complex Full Chip Low Power Implementation in 16nm NodemanojkumarPas encore d'évaluation

- ClockPulseGen 09 09 08Document9 pagesClockPulseGen 09 09 08manojkumarPas encore d'évaluation

- Creating Power-Switch Arrays and RingsDocument7 pagesCreating Power-Switch Arrays and RingsmanojkumarPas encore d'évaluation

- Understanding The UPF Power Domain and Domain Boundary - Mentor GraphicsDocument15 pagesUnderstanding The UPF Power Domain and Domain Boundary - Mentor GraphicsmanojkumarPas encore d'évaluation

- Advantages of Replacement To A Chip Varistor and Selection PointsDocument16 pagesAdvantages of Replacement To A Chip Varistor and Selection PointsmanojkumarPas encore d'évaluation

- Duet Embedded Memories and Logic Libraries For TSMC 28HP: HighlightsDocument5 pagesDuet Embedded Memories and Logic Libraries For TSMC 28HP: HighlightsmanojkumarPas encore d'évaluation

- Title Description: (/S/) Cases (/S/Case-List) Stars (/S/Star-List) Articles (/S/Knowledge) Help (/S/Help-Info)Document2 pagesTitle Description: (/S/) Cases (/S/Case-List) Stars (/S/Star-List) Articles (/S/Knowledge) Help (/S/Help-Info)manojkumarPas encore d'évaluation

- Manoj - Qualcomm Interview QuestionsDocument1 pageManoj - Qualcomm Interview Questionsmanojkumar100% (1)

- Automatically Adding Spare Cells: IC Compiler II Implementation User Guide, Version R-2020.09 ECO FlowDocument2 pagesAutomatically Adding Spare Cells: IC Compiler II Implementation User Guide, Version R-2020.09 ECO FlowmanojkumarPas encore d'évaluation

- Individual Moving Range (I-MR) Charts ExplainedDocument18 pagesIndividual Moving Range (I-MR) Charts ExplainedRam Ramanathan0% (1)

- Manufacturing Processes (ME361) Lecture 13: Instructor: Shantanu BhattacharyaDocument28 pagesManufacturing Processes (ME361) Lecture 13: Instructor: Shantanu BhattacharyaSahil SundaPas encore d'évaluation

- AsdfgDocument2 pagesAsdfgTejendra PachhaiPas encore d'évaluation

- Advanced Scan I21no2Document29 pagesAdvanced Scan I21no2Jaiber SosaPas encore d'évaluation

- Final System DocumentationDocument31 pagesFinal System DocumentationEunice AquinoPas encore d'évaluation

- Tutorial Sim MechanicsDocument840 pagesTutorial Sim MechanicsHernan Gonzalez100% (4)

- CH 11 & CH 12 John R. Schermerhorn - Management-Wiley (2020)Document16 pagesCH 11 & CH 12 John R. Schermerhorn - Management-Wiley (2020)Muhammad Fariz IbrahimPas encore d'évaluation

- Saes H 201Document9 pagesSaes H 201heartbreakkid132Pas encore d'évaluation

- Design of Hydraulic Structures Seepage TheoryDocument13 pagesDesign of Hydraulic Structures Seepage TheorySuleman FaisalPas encore d'évaluation

- The Truth of Extinction: 7.1 Nietzsche's FableDocument2 pagesThe Truth of Extinction: 7.1 Nietzsche's FableGraciela Barón GuiñazúPas encore d'évaluation

- Crafting and Executing StrategyDocument33 pagesCrafting and Executing Strategyamoore2505Pas encore d'évaluation

- 2VAA001695 en S Control NTCS04 Controller Station Termination UnitDocument43 pages2VAA001695 en S Control NTCS04 Controller Station Termination UnitanbarasanPas encore d'évaluation

- DANA 6800-1 Parts ManualDocument4 pagesDANA 6800-1 Parts ManualDude manPas encore d'évaluation

- Adverb Affirmation Negation LessonDocument4 pagesAdverb Affirmation Negation LessonMire-chan Bacon100% (1)

- Confirmation Form: Pillar Regional Conference (NCR)Document1 pageConfirmation Form: Pillar Regional Conference (NCR)Llano Multi-Purpose CooperativePas encore d'évaluation

- Republic of The Philippines Iba, Zambales: President Ramon Magsaysay State UniversityDocument3 pagesRepublic of The Philippines Iba, Zambales: President Ramon Magsaysay State UniversityErika Joy EscobarPas encore d'évaluation

- MST 2 ReviewerDocument4 pagesMST 2 ReviewerAizha NarioPas encore d'évaluation

- Design and Simulation of Programmable AC-DC Converter Using Pulse Width Modulation (PWM) Techniques in MATLABDocument5 pagesDesign and Simulation of Programmable AC-DC Converter Using Pulse Width Modulation (PWM) Techniques in MATLABJeannot MpianaPas encore d'évaluation

- Non-Destructive Examination & Standard CF Acceptance For - Forgsd - Pipe Work Stub PiecesDocument2 pagesNon-Destructive Examination & Standard CF Acceptance For - Forgsd - Pipe Work Stub PiecesveeramalaiPas encore d'évaluation

- Guimaras State CollegeDocument5 pagesGuimaras State CollegeBabarianCocBermejoPas encore d'évaluation

- 16SEE - Schedule of PapersDocument36 pages16SEE - Schedule of PapersPiyush Jain0% (1)

- HRM Assignment Final - Case StudyDocument7 pagesHRM Assignment Final - Case StudyPulkit_Bansal_2818100% (3)

- Ninja's Guide To OnenoteDocument13 pagesNinja's Guide To Onenotesunil100% (1)

- Operation 490BDocument60 pagesOperation 490BYe Min Htike100% (1)

- CTM Catalogue 2015-2016Document100 pagesCTM Catalogue 2015-2016Anonymous dXcoknUPas encore d'évaluation

- 7 C's of Business LetterDocument3 pages7 C's of Business LetterGladys Forte100% (2)

- Mindfulness With Collegiate Gymnasts - Effects On Flow, Stress and Overall Mindfulness LevelsNicholas P. Cherupa,, Zeljka VidicDocument13 pagesMindfulness With Collegiate Gymnasts - Effects On Flow, Stress and Overall Mindfulness LevelsNicholas P. Cherupa,, Zeljka VidicGABRIELPas encore d'évaluation

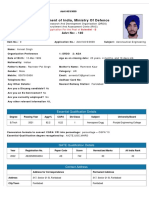

- DrdoDocument2 pagesDrdoAvneet SinghPas encore d'évaluation

- Silicon ManufacturingDocument132 pagesSilicon ManufacturingAndrea SottocornolaPas encore d'évaluation

- Proejcr ManduaDocument552 pagesProejcr ManduaDanny NguyenPas encore d'évaluation