Académique Documents

Professionnel Documents

Culture Documents

Clase IB - 05 Circuitos MSI - All

Transféré par

DanDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Clase IB - 05 Circuitos MSI - All

Transféré par

DanDroits d'auteur :

Formats disponibles

Universsidad Politécnica Sallesiana Campus Surr

1

SISTEEMAS DIGITALESS

Capítuloo 5

CIRCUIITOS MSII (1): Mu

ultiplexorees y demu

ultiplexorres

5.1.Introd

ducción

Los circutioos MSI son loos que están constituidos por

p un númerro de puertas lógicas compprendidos entrre 12 y 100.

En este capíítulo veremos una serie dee circuitos com mbinaciones que se utilizan mucho en electrónica digital

d y que

son la base para la creación de diseñoos más compleejos. Aunque se pueden diiseñar a partirr de puertas lóógicas, estos

circuitos se pueden

p tratar como

c “componnentes”, asignnándoles un sím

mbolo, o utilizzando una cierrta nomenclatura.

Los circuitoss que veremos son los siguieentes:

M

Multiplexores y demultiplexxores

Coodificadores y decodificadoores

Coomparadores

Lo más importante es comprender paara qué sirven n, cómo funciionan y que bitsb de entrad da y salida uttilizan. Estos

circuitos los podríamos diiseñar perfectaamente nosotrros, puesto quue se trata de circuitos

c combbinacionales y por tanto

podemos apliicar todo lo apprendido en ell capítulo

5.2. Multip

plexores

5.2.1.Concep

ptos

Un Multipleexor es un ciircuito combiinacional al que entran vaarios canales de datos, y ssólo uno de ellos, e el que

hallamos seleeccionado, es el que aparecce por la salid da. Es decir, que

q es un circcuito que nos ppermite SELE ECCIONAR

que datos passan a través dee dicho compoonente.

Vamos a verr un ejemplo NO electróniico. Imaginem mos que hay dos tuberías (canales de ddatos) por el que circulan

distintos fluiddos (datos). Una

U transportaa agua para reggar y la otra agua

a potable. Estas

E tuberías llegan a una granja, en la

cual hay unaa única manguuera por la quee va a salir ell agua (bien potable o bien para regar), ssegún lo que seleccione

s el

granjero posicionando la llave de pasoo en una u ottra posición. En la figura anterior se m muestra un essquema. Las

posiciones soon la 0 para el agua potable y 1 para el aggua de regar.

Moviendo laa llave de paaso, el granjeero puede selleccionar si lo l que quieree que salga ppor la manguuera es agua

potable, paraa dar de beberr al ganado, o agua para reegar los cultivvos. Según cóm

mo se posicione esta llave de

d paso, en la

posición 0 ó en la 1, selecccionamos una tubería u ottra. Pero ¿por qué sólo doss tuberías?. Poorque es un ejjemplo. A la

granja podríaan llegar 4 tubeerías.

En este casoo el granjero tendría

t una llaave de paso

con 4 posicioones, como see muestra en la figura 5.2.

Esta llave se podría poner en 4 posicionnes distintas

para dar pasoo a la tubería 0, 1, 2 ó 3. Obsérvese que

sólo pasa unaa de las tuberrías en cada momento,

m ¡y

sólo una!. Haasta que el graanjero no vuellva a cambiar la

llave de pasoo no se seleccioonará otra tubería.

Con este ejem

mplo es muy fácil

f entender la idea de

multiplexor.. Es como unaa llave de pasoo, que sólo

Reaalizado por : Ing Carlos Pillajo A.

Universsidad Politécnica Sallesiana Campus Surr

2

SISTEEMAS DIGITALESS

conecta uno de

d los canales de datos de entrada

e con el canal de datoss de salida.

Ahora en vezz de en tuberíaas, podemos pensar

p en canaales de datos, y tener un esquuema como ell que se muesstra en la figuura

5.3, en la quue hay 4 canales de datos, y sólo uno de ellos es seleeccionado porr el multiplexoor para llegar a la salida . En

E

u multiplexorr tenemos dos tipos de entraadas:

general, en un

En

ntradas de daatos: (Las tubeerías en el ejem

mplo).

En

ntrada de seleección: Indica cuál de las enntradas se ha seleccionado

s (

(posición de laa llave de pasoo).

5.2.2. Multiplexorees y bits

Hemos vistoo cómo a un multiplexor

m l llegan núm

le meros por disttintas entradaas y según el nnúmero que le l llegue por

la entrada de selección,, lo manda por p la salida o no. ¡¡Núm meros!! Recorrdemos que loos circuitos digitales

d sólo

trabajan con números.

Pero estos núúmeros, vimos que siempre vendrán

v expreesados en binaario y por tantoo se podrán exxpresar mediannte bits.

¿Cuantos bitss? Depende dee lo grande quue sean los núúmeros con loss que se quieree trabajar.

En el interiorr de los micropprocesadores es muy normaal encontrar multiplexores

m d 8 bits, que ttienen varias entradas

de e de daatos

de 8 bits. Peero se puede trabajar

t con multiplexores

m q tengan 4 bits por cadaa entrada, o inncluso 2, o inccluso 1bit. Enn la

que

figura 5.4 se muestran doss multiplexores que tienen 4 entradas de datos.

d Por elloo la entrada dee selección tiene dos bits (para

poder selecciionar entre loss cuatro canalees posibles). Sin e uno las entrradas de datoss son de 2 bits y en el otro de

S embargo, en d 1

bit.

Mirando el número

n de saalidas, podemoos conocer el tamaño de lo os canales de entrada.

q el de la izqquierda tiene 2 bits de salida, por tanto suus canales de

Así en los doos multiplexorres de la figuraa 5.4, vemos que

entrada son de

d 2 bits. El dee la derecha tieene 1 bit de saalida, por tantoo los canales de

d 1 bit.

Los multiplexxores en lo quue principalmeente nos centraaremos son loos que tienen canales

c de 1 biit. A partir de ellos

podremos coonstruir multipplexores mayoores, bien con un mayor núm mero de canales de entrada o bien con unn mayor númerro

de bits por caada canal.

Reaalizado por : Ing Carlos Pillajo A.

Universidad Politécnica Salesiana Campus Sur

3

SISTEMAS DIGITALES

5.2.3. Multiplexores de 1 bit y sus expresiones booleanas

Llamaremos así a los multiplexores que tienen canales de entrada de 1 bit, y por tanto sólo tienen un bit de salida.

Estudiaremos estos multiplexores, comenzando por el más simple de todos, el que sólo tienen una entrada de selección.

Multiplexores con una entrada de selección

El multiplexor más simple es el que sólo tiene una entrada de selección, S, que

permite seleccionar entre dos entradas de datos, según que S=0 ó S=1. Su aspecto es el

siguiente:

¿Cómo podemos expresar la función de salida F, usando el Algebra de Boole?.

Existe una manera muy sencilla y que ya conocemos: hacer la tabla de verdad y obtener la función más simplificada.

Construyamos la tabla de verdad. Lo primero que nos preguntamos es, ¿Cuantas entradas tengo en este circuito?. En

total hay tres entradas. Dos son de datos I1, I0 y una es de selección S. La tabla de verdad tendrá en total 23=8 filas. Para

construir esta tabla de verdad sólo hay que entender el funcionamiento del multiplexor e ir caso por caso rellenando la

tabla. Por ejemplo, ¿qué ocurre si S=1, I1=0 y I0=1?. Aplicamos la definición de multiplexor. Puesto que S=0, se está

seleccionando la entrada de datos 0, es decir, la entrada I0. Por tanto, lo que entre por la entrada I1 será ignorado por el

multiplexor. Si la entrada seleccionada es la I0, la salida tendrá su mismo valor. Y puesto que I0=1, entonces F=1. Si

hacemos lo mismo para todos los casos, tendremos la siguiente tabla de verdad:

La tabla se ha dividido en dos bloques, uno en el que S=0 y otro en el que S=1. En el primer

bloque, se selecciona I0 que aparecerá en la salida. Se ha puesto en negrita todos los valores de

I0 para que se vea que son los mismos que hay a la salida. En el bloque inferior, lo que se

selecciona es I1 y es lo que se obtiene por la salida.

Apliquemos el método de Karnaugh para obtener la expresión más simplificada de F. El

diagrama que se obtiene es el siguiente: (Se aconseja al lector que lo haga por su propia cuenta,

sin mirar los apuntes, así le sirve además para practicar :-)

Obtenemos la siguiente expresión: F= /S*I0 + S*I1

Y si ahora observamos lo que la ecuación nos dice, veremos que tiene mucho sentido:

“Si S=0, F = I0 y si S=1, F = I1”

¡¡Es justo la definición de un multiplexor!! La salida toma el valor de una de las entradas, según el valor que tome

la entrada de selección.

En realidad, el multiplexor lo podríamos haber descrito de una manera más sencilla, y podríamos haber obtenido la

ecuación de otra forma. Veamos cómo.

La función F que describe el comportamiento de un multiplexor con una única entrada de selección,

la podemos describir mediante la siguiente tabla:

que lo que nos viene a decir es lo mismo que su ecuación: cuando S=0, por la salida del

multiplexor aparece el valor I0y cuando S=1, aparece el valor I1. Estamos considerando las variables I0 e I1 como

parámetros y NO como variables de entrada del circuito y por tanto estamos considerando como si la función F sólo

dependiese de la variable S, es decir, tenemos la función F(S). ¿Cómo podemos obtener la ecuación del multiplexor

a partir de esta tabla?:

aplicando el teorema de expansión, obtenemos los siguiente: F(S) = S*F(1) + /S*F(0)

y F(1) es la salida del multiplexor cuando S=1, es decir, que F(1) = I1 y F(0) es la salida cuando S=0, F(0)=I0. La

ecuación del multiplexor es la siguiente: F(S) = S*I1 + /S*I0

¡¡Que es la misma ecuación que habíamos obtenido por Karnaugh!!

No se asuste el lector por los desarrollos teóricos. Lo importante es comprender cómo funcionan este tipo de

m ultiplexores y cuál es la ecuación que los describe, independientemente de cómo la hallamos obtenido. Aquí, hemos

obtenido la ecuación por dos métodos diferentes. Veremos que con los multiplexores de dos entradas de selección sólo lo

podremos hacer por el segundo método.

Realizado por : Ing Carlos Pillajo A.

Universsidad Politécnica Sallesiana Campus Surr

4

SISTEEMAS DIGITALESS

Multiplexorees con dos en ntradas de seleección.

El siguiente multiplexor en

e complejidaad es el que teenga 2 entrad das de

selección, poor lo que se podrá seleccioonar hasta 4 entradas

e posiibles.

Habrá por tannto 4 entradaas de datos. El

E circuito es como

c el siguieente:

Hay 4 entraddas de datos y 2 entradas de d selección, en total 6 enttradas.

Ahora hacemmos lo mismo que antes, construimos la tablat de verdaad y

aplicamos Kaarnaugh... perro.... ¿6 variabbles?

¡¡Hay que h bla que tengaa 26= 64 filass!! ¡¡Y luego aplicar

hacer una tab

Karnaugh a una funciónn de 6 variablles!!!

Vemos que esste método, auunque fácil, reqquire muchas operaciones.

o ¡¡Es un métodoo ideal para quue lo haga un ordenador!!.

o

Nosotros obttendremos sus ecuaciones dee otra manera diferente.

Vamos a desccribir este mulltiplexor mediiante la siguiennte tabla:

que lo que nos

n está expressando es que lal salida del multiplexor

m valldrá I0,I1,I2 o I3 según el vaalor

que tomen laas variables dee entrada S1 y S0. Estamos considerandoo que la funcióón F sólo deppende

de estas dos variables: F(S

S1,S0) y que I0,I1,I2 e I3 soon parámetros,, es decir, valoores constantees que

pueden valer ’0’ ó ’1’.

Si aplicamos el teorema ded expansión a la función F(S1,S0), desarrrollándola poor S1 , obtenem mos lo siguiennte:

F(S1,S0) = S1*F(1,S0)

S + /S1*F(0,S0)

/

¿Cuando valee F(0,0)?, es decir,

d ¿cuál es la salida del multiplexor

m cuuando S0 = 0 y S1=0 ?. Por la definición de

d multiplexorr,

la salida será lo que venga por

p el canal 0,, que es I0. Dee la misma mannera obtenemoos que F(0,1)=

=I1, F(1,0)=I22, F(1,1)=I3

Sustituyendoo estos valoress en la ecuacióón anterior y reordenándola

r un poco tenemos la expressión final parra un

multiplexor de dos entrad das de selecciión:

F= S1´S0´I0 + S1´S0 I1 + S1 S0´ I2 + S1

S S0 I3 (5.2)

Olvidémonoss ahora de cóm mo hemos obbtenido esa eccuación. Lo im mportante es entenderla

e y saber utilizarlaa. Vamos a

comprobar sii efectivamentte esta ecuacióón describe ell funcionamiennto de un mulltiplexor de 2 eentradas de seelección y 4

entradas de datos.

d

Si S1=0 y S0=0,

S sabemoss por el compoortamiento de un

u multiplexoor que se selecccionará la entrrada para quee aparezca porr la

salida. Vamos a comprobarrlo. En la ecuaación del multiiplexor sustituuimos S1 por 0 y S0 por 1. O

Obtenemos: I00

Se deja comoo ejercicio el quue se comprueebe la ecuaciónn para el resto de

d valores de las

l entradas dee selección.

Multiplexor con cualquieer número de entradas de selección

Si ahora teneemos un multtiplexor con 3 entradas de selección, quee me permitirrá seleccionar entre 8 entraddas de datos,

q lo describee es la generallización de la ecuación 5.2. En total habrá 8 sumandoss y en cada unno de ellos se

la ecuación que

encontrarán las

l variables S2,S1

S y S0 adeemás de los coorrespondientees parámetros I0,I1,I2,……., I7

Y lo mismo podemos

p haceer para cualquuier multiplexoor con un núm

mero de entradas de seleccióón mayor, lo quue ocurre que la

ecuación tenddrá muchos más

m términos.

Reaalizado por : Ing Carlos Pillajo A.

Universidad Polittécnica Salesianaa 1

SISTEEMAS DIGITALESS

5.3. D

Demultiplexo

ores

5.3.1. Conceptos

El concepto de demultipleexor es similarr al de multiplexor, viendo las entradas de

d datos comoo salidas y la salida como

entradas. En un multiplexxor hay variass entradas de datos, y sólo una de ellas se saca por eel canal de saalida. En los

demultiplexoores hay un únnico canal de entrada

e que se saca por una de las múltiplles salidas (y ssólo por una!!!).

Si utilizamoss el símil de la granja y laas tuberías, poodemos imagiinar el siguiennte escenario. Supongamos que ahora a

la granja le llega una única tubería conn agua, pero en el interiorr de la granja hay varias m mangueras, caada una para

limpiar una zona

z del estabblo o dar de beber

b a los annimales de esaa zona. Cómoo sólo hay un granjero, sóloo podrá usar

una de las mangueras

m cadaa vez (el granjjero no podrá usar a la vez dos

d mangueras, porque estáán en sitios differentes!!).

Para seleccioonar qué mangguera quiere usar en cada momento, haay una llave de d paso, de maanera que si laa sitúa en unaa

posición, el agua

a que viene por la entradda saldrá por la manguera 0,

0 mientras quue si la sitúa enn la otra posiciión, el agua

saldrá por la manguera 1 (vver figura 5.5))

De la mismaa manera que en los multipplexores puedee haber variass entradas, en los demultipllexores puede haber varias

salidas. Por ejemplo

e en la figura

f 5.6 se muestra

m el mismo sistema dee tuberías de la

l granja, peroo ahora hay 4 mangueras,

para llegar a 4 zonas disttintas de la granja.

g Ahora el granjero teendrá que posiicionar la llavve de paso en una de las 4

posiciones poosibles, para que

q el agua sallga por la mannguera seleccioonada.

Ya comprenddemos cómo fuuncionan los demultiplexore

d es. Si lo aplicaamos al mundoo de la electrónnica, en vez de

d tuberías

tendremos caanales de datoos. Habrá un único canal de

d entrada, poor el que llegaarán números,, que saldrán sólo por uno

de los canalees de salida, el que tengam

mos seleccionaado, como se muestra

m en la figura 5.7.

En general enn un demultiplexor tendrem

mos:

Una entradaa de datos

Una entradaa de selección

n: que indica a cuál de las saalidas se mandda la entrada

Varios canalles de datos de

d salida. Sóloo estará activo el que se haya seleccionadoo.

Reaalizado Por : Ing. Carlos Pillajo A

Universidad Polittécnica Salesianaa 2

SISTEEMAS DIGITALESS

5.3.2. Juntando mu

ultiplexores y demultiplex

xores

Vamos a verr una aplicacióón típica de los

l multiplexoores y los dem multiplexores.. Imaginemos que tenemos 4 sistemas,

que los llam

maremos a,b,c y d, y que neecesitan enviaar informaciónn a otros 4 disspositivos A,B B,C y D. La coomunicación

es uno a uno, es decir, el sistema a sólo envía informaación al sistem

ma A, el b al B,

B el c al C y eel d al D.

¿Qué alternattivas hay paraa que se produuzca este envíoo de datos? Unna posibilidadd es obvia, y ess la que se muuestra en la

figura 5.10. Directamente

D s tiran cabless para estableccer los canales de comunicacción.

se

Pero esta no es la única sollución. Puede ser que podam mos tirar los 4 cables, porquue sean muy caaros o porque sólo haya un

único cable que

q comuniquee ambas parte, y será necesaario llevar porr ese cable toddas las comunicaciones.

s muestra en la figura 5.9. Vemos que loos sismteas a, b, c y d se coonectan a un m

La solución se multiplexor. Un

U circuito de

control, coneectado a las enntradas de seleección de estee multiplexor, se- lecciona periódicamennte los diferenttes sistemas,

enviando porr la salida el caanal corresponndiente. Podemmos ver que a la salida del multiplexor

m see encuentra la información

enviada por los

l 4 siste- maas. Se dice quee esta informaación está mulltiplexada en el tiempo. All final de esta línea hay un

demultiplexoor que realiza la función invversa. Un circcuito de controol selecciona periódicamennte

por qué saliddas debe salir la

l informaciónn que llega porr la entrada.

Lo que hemoos conseguidoo es que toda la informacióón enviada poor un sistema, llega a su hoomólogo en ell extremo

anterior, peroo sólo hemos utilizado

u un únnico canal de datos.

d

5.3.3. Demultiplex xores y bits

Un demultipllexor, como cuualquier otro circuito

c digitaal trabaja sólo con números. Pero estos núúmeros vendrán expresadoss

en binario, por

p lo que los canales de datosd de entraada y salida, y la entrada de d selección vvendrán expreesados en

binario y tenndrán un númeero determinaddo de bits.

Una vez máss nos hacemoos la preguntaa, ¿Cuantos biits?. Depende. Depende de la aplicaciónn que estemos diseñando o

con la que estemos trabajanndo. En la figuura 5.10 se muuestran dos dem multiplexores de 4 canales,, por lo que teendrán 2 bits

para la entradda de seleccióón. El de la izqquierda tiene canales

c de 2 biits y el de la derecha

d de 1 biit.

Los multipleexores que vammos a estudiaar son lo que tienen canalees de 1 bit. A partir

p de elloss podremos co

onstruir

multiplexorees con un mayyor número dee bits por canaal.

Reaalizado Por : Ing. Carlos Pillajo A

Universidad Politécnica Salesiana 3

SISTEMAS DIGITALES

5.3.4. Demultiplexores de 1 bit y sus expresiones booleanas

Demultiplexor de una entrada de selección

El demultiplexor más simple es el que tiene una entrada de selección, una entrada de datos y dos salidas. Según el valor de

la entrada de selección, la entrada de datos se sacará por la salida O0 o por la O1:

Nos hacemos la misma pregunta que en el caso de los multiplexsores: ¿Cómo podemos

expresar las funciones de salida usando el Algebra de Boole?. Podemos escribir la

tabla de verdad y obtener las expresiones más simplificadas. Para tener la tabla

aplicamos la definición de demultiplexor y vamos comprobando caso por caso qué

valores aparecen en las salidas. Por ejemplo, si S=1 e I=1, se estará seleccionando la

salida O=1, y por ella saldrá el valor de I, que es 1. La salida O0 no estará seleccionada y tendrá el valor 0.

Para obtener las expresiones de O0 y O1 no hace falta aplicar Karnaugh puesto que cada

salida sólo toma el valor ’1’ para un caso y ’0’ para todos los restantes. Desarrollando por la

primera forma canónica:

O1 = S * I ; O0 = /S* I

Y podemos comprobar que si hemos seleccionado la salida 0 (S=0), entonces O0 = I y O1=0, y si hemos seleccionado la

salida 1 (S=1), O0 = 0 y O1=1 .

De la misma manera que hicimos con los multiplexores, podemos considerar que las funciones O0 y O1 sólo dependen

de la entrada de Selección (S), tomando la entrada I como un parámetro. Así podemos describir este demultiplexor

mediante la siguiente tabla:

Esta descripción será la que empleemos, ya que es más compacta.

Demultiplexor de dos entradas de selección

Este demultiplexor tiene dos entradas de selección y cuatro salidas:

La tabla de verdad “abreviada” la podemos expresar así:

La entrada I se saca por la salida indicada en las entradas de selección. Las ecuaciones de las funciones de salida son:

O0 = /S1 /S0 I ; O1= /S1 S0 I ; O2 = S1 /S0 I ; O3 = S1 S0 I

Si analizamos la ecuación de O0 lo que nos dice es lo siguiente: “ O0= 1 sólo cuando S1=0 y S0=0”. Para el resto de

valores que pueden tomar las entradas de selección S1 y S0, O0, siempre será 0.

Demultiplexor con cualquier número de entradas de selección

Realizado Por : Ing. Carlos Pillajo A

Universidad Polittécnica Salesianaa 4

SISTEEMAS DIGITALESS

Para demultipplexores con mayor

m númeroo de entradas de

d selección, laas ecuaciones serán similarees. Por ejempllo, en el caso de

d

un demultiplexor que tengaa tres entradass de selecciónn: S2,S1 y S0 , y que por tantto tendrá 8 sallidas, la ecuacción para la

salida O5 serrá: O5 = S2 /S1/ S0 I

O será: O0 = /S2 /S1 /S0 I

y la ecuaciónn de la salida O0

Se deja comoo ejercicio al lector el que obbtenga el restoo de ecuacionees de salida.

5.4. M

Multiplexore es con entradaa de validacióón (ENABLE E)

Los multiplexores, y en geeneral la mayooría de circuittos MSI, disponen de una entrada

e adiciional, llamadaa entrada de

validación (een inglés Enaable). Esta enttrada funcionaa como un inteerruptor de enncendido/apaggado para el circuito

c MSI.

Si la entradda de validaciión está activvada, el circu uito funcionaará normalm mente. Pero sii esta está desactivada, el

circuito sacará el valor ’0’ por todas suss salidas, indeependientemennte de lo que llegue

l por sus entradas. Se dice

d que está

deshabilitadoo (no está en funcionamiento

fu o).

Las entradas de validación se les suele llaamar E (del innglés Enable) y pueden ser de dos tipos: acctivas a nivel alto

a ó activas a

nivel bajo.

5.4.1. Entrada de validación

v acctiva a nivel alto

a

Si esta entradda se encuentrra a ’1’ (E=1) el multiplexoor funciona norrmalmente (esstá

conectado). Si

S se encuenrtaa a ’0’ (E=0) entonces

e su sallida será ’0’ (eestará

desconectadoo). A continuación se muesttra un multipleexor de 4 entraadas de datos,, 2

entradas de selección

s y una entrada de vali-

v dación acctiva a nivel altto:

Sóloo en los casos en los que E=1, el multiplexxor se comportta

com

mo tal. Cuandoo E=0, la salidaa Z siempre esstá a ’0’. Estaa

tabla de verdad se suele escribbir de una mannera más

abreeviada de la siiguiente maneera:

Con las ’x’ de

d la primera fila

f se indica que cuando E=0,

E independiientemente dee los valores qque tengan las entradas S1 y

S0 la salida siempre

s tendráá el valor ’0’.

¿Y cual seríaa la nueva ecuuación de este multiplexor? La misma que antes pero ahora

a multiplicada por E:

Z= (/S1

( /S0 I0 + /S1

/ S0 I1 + S1 /S0 I2 + S1 S0 I3) E

Si E=0, entonnces Z=0. El multiplexor

m esstá deshabilitaado.

5.4.2. Entrada de validación

v acctiva a nivel bajo

b

Otros fabricaamentes de circcuitos integraddos utilizan una

entrada de validación

v actiiva a nivel bajjo, que es justtamente

la inversa de la enterior. Se suele denotarr mediante /E. Cuando

la entrada E está

e a ’0’ el multiplexor

m funnciona normallmente,

y cuando estáá a ’1’ está deesconectado. En E la siguientee figura

se muestran dos multiplexxores de 4 enttradas, dos enntradas

de selección y una entradaa de validaciónn activa a niveel bajo.

Ambos multiiplexores son iguales,

i pero se

s han utilizaddo

notaciones diistintas. En el de

d la izquuierda se utilizza /E y en el dee la derecha E pero

p con un

pequeño círculo en la entraada:

La tabla de verdad

v es la sigguiente:

Reaalizado Por : Ing. Carlos Pillajo A

Universidad Polittécnica Salesianaa 5

SISTEEMAS DIGITALESS

Y la nueva eccuación es:

Z = (/S1 /S0 I0 + /S1 S0 I1 + S1 /S0 I2 + S1 S0 I3) /E

Cuando E=1,, /E=0 y entonnces Z=0, con lo que el multtiplexor se enccuentra deshaabilitado.

5.5. E

Extensión de multiplexorees

La idea es poder conseguir tener multiplexores

m más grandees a partir de otros máás pequeños. Y esto es

necesario porque en nuesttros diseños podemos

p neceesitar unos muultiplexores grrandes, sin em

mbargo en el mercado

m nos

encontramos con multiplexores menorees. Tenemos que q saber cóm mo construir loos multiplexoores que necessitamos para

nuestra aplicación a partirr de los multipplexores que encontramos enn el mercado.

La extensiónn puede ser biien aumentan ndo el númerro de entradaas, bien aumeentando el nú

úmero de bitss por cada

canal de dattos o bien ambbos a la vez.

5.5.1. Aumento dell número de entradas

La solución es

e conectarloss en cascada. Lo mejor es verlo

v con un

ejemplo. Imaaginemos que necesitamos una

u multiplexoor de 8 canales,

pero sólo dispponemos de varios

v de 2 cannales:

La solución ese conectarloss en cascada. Primero coloccamos una

columna de 4 multiplexorees de dos entraadas, para tenner en total 8

entradas. Toddas las entradaas de seleccióón de esta prim

mera columna

se unen. Por comodidad enn el dibujo, estto se representta mediante unna

línea verticall que une la saalida S de un multiplexor

m conn el de abajo.

A continuaciión colocamoss una segundaa columna de 2 multiplexores

de 2 entraddas, también con sus enttradas de sellección unidaas.

Fiinalmente collocamos una última colum

mna con un

únnico multiplexxor de 2 entraddas.

Colocados de esta manera, coonseguimos tenner un

multiplexor

m de 8 entradas y trres entradas dee selección. Laa

únnica consideraación que hay que tener en cuenta

c es que la

enntrada de seleccción de los m

multiplexores ded la primera

coolumna tiene peso

p 0, la seguunda peso 1 y la última pesoo

2::

¡¡Vamos a compprobarlo!! (Sieempre que se hace un diseño

Reaalizado Por : Ing. Carlos Pillajo A

Universidad Politécnica Salesiana 6

SISTEMAS DIGITALES

hay que comprobar si es correcto).

Vamos a comprobar qué ocurre si seleccionamos el canal 6. Introducimos en binario el número 6 por las entradas de

selección: S2=1, S1=1 y S0=0. Por la entrada S de los multiplexores de la primera columna se introduce un ’0’, por lo que

estos multiplexores sacan por sus salidas lo que hay en sus entradas I1,I0,I2,I4 e I6. Por la entrada de selección de los

multiplexores de la segunda columna se introduce un ’1’ por lo que están seleccionando su canal I1. A la salida de estos

multiplexores se tendrá: I2 e I6. Finalmente, el multiplexor de la última columna está seleccionando su entrada I1, por lo

que la salida final es I6(Recordar la idea de multiplexor como una llave de paso que conecta tuberías de agua):

Ejemplo:

Construir un multiplexor de 16 entradas usando multiplexores de 4.

Los conectamos en cascada, para lo cual necesitamos una primera

columna de 4 multiplexores de 4 entradas, con entradasde todos ellos

unidos, así como las . En la segunda fila hay un único multiplexor

de 4 entradas:

Realizado Por : Ing. Carlos Pillajo A

Universidad Politécnica Salesiana 7

SISTEMAS DIGITALES

5.5.2. Aumento del número de bits por canal

Para conseguir esto hay que conectarlos en paralelo. Imaginemos

que tenemos queremos construir un multiplexor de dos canales de

entrada, cada uno de ellos de 2 bits, y para ello disponemos de

multiplexores de 2 canales de un bit:

Utilizaremos dos multiplexores de lo que tenemos, uno por cada bit

que tengamos en el

nuevo canal de salida. Como los canales en el nuevo multiplexor

son de 2 bits, necesitaremos 2 multiplexores de canales de 1 bit. Uno

de estos multiplexores será al que vayan los bits de menos peso de

los canales de entrada y el otro los de mayor peso. Las entradas de selección de ambos

están unidas:

Si con en este nuevo multiplexor hacemos S=0, las salidas serán Z0 = A0 y Z1 = A1. Y si hacemos S=1, entonces

obtenemos Z0 = B0 y Z1 = B1 . ¡¡Es lo que andábamos buscando!!. Por la salida obtenemos bien el número que viene por el

canal 0 ( A1 A0 ) ó bien el número que viene por el canal 1 (B1 B0).

Ejemplo:

Construir un muliplexor de 4 canales de 4 bits, usando

multiplexores de 4 entradas de 1 bit.

Ahora necesitaremos 4 multiplexores de los que tenemos, a cada uno de

los cuales les llegan los bits del mismo peso de los diferentes canales.

Por el primer multiplexor entran los bits de menor peso (A0,B0,C0 y

D0) y por el último los de mayor ( A3,B3,C3 y D3). En el dibujo no se

muestran todas las conexiones para no complicarlo:

Realizado Por : Ing. Carlos Pillajo A

Universidad Polittécnica Salesianaa 8

SISTEEMAS DIGITALESS

5.6. I

Implementac ión de funcioones con MX’’s

Utilizando multiplexores

m e posible impllementar funcciones booleannas. En generaal, cualquier fu

es función de n variables se

puede implemmentar utilizaando un mulltiplexor de n--1 entradas ded selección.

Por ejemplo, dada la funcióón: F = /x y z + x /y + /x /y

/ /z

que tiene 3 variables,

v se puuede implemeentar utilizandoo un multiplexxor de 2 entraadas de control,

como el mosttrado a continnuación:

Existen dos maneras

m de haccerlo. Una es emplear

e el algebra de boole y la ecuación de este tipo

de multiplexoores. Por lo general este méétodo es más complicado. La

L otra es utillizar un métoddo

basado en la tabla de verdaad.

5.6.1. Método basa

ado en el Alg

gebra de Boolle

La ecuación de un multipleexor de 2 entraadas de controol y 4 entradass es la siguientte:

O = /S1 /S0 I0 + /S1 S0 I1 + S1 S /S0 I2 + S11 S0 I3

La ecuación de la funciónn que queremoos implementaar la podemoss expresar de la siguiente fo

forma:

F = /x /y /z + /x y z + x /y 1 + x y 0

¡¡Que es muuy parecida a Z!!. Si igualaamos términoos, obtenemos que por las entradas del mmultiplexor haay que

introducir:

I0 = /z ; I1 = z ; I2 = 1 ; I3 = 0 ; S0 = y ; S1 = x

La función see implementa así:

Vamos a commprobarlo. Parra ello sustituiimos en la ecuación del

multiplexor los

l valores quue estamos intrroduciendo poor las entradas:

O= /S1 /S0 I0 + /S1 S0 I1 + S1 /S0 I2 + S1 S0 I3 = /x /y I0 + /x y I1 + x /y I2 + x y I3

= /x /y z + /x y z + x /y 0 + x y 1

= /x /y z + /x y z + x y = F

5.6.2. Método basa

ado en la tabla de verdad

Este método se basa en loo mismo, peroo se usan las tablas de verddad en vez dee utilizar las eecuaciones dell multiplexor,

por ello es más

m sencillo e intuitivo. Adem

más tiene otra ventaja: es unn método meccánico, siemprre se hace iguual sea cual seea

la función (A

Aunque como se verá en loos ejercicios allgunas funcionnes se pueden implementar dde manera máás fácil si

utilizamos la entrada de vaalidación).

Vamos a realizar este ejem

mplo con la funnción anterior. Seguimos loss siguientes paasos:

1. Connstruimos la taabla de verdad de la función F a implemenntar.

2. Diviidimos la tablla en tantos grupos

g como canales de enntrada halla. En este caso

hay 4 entraddas, por lo quue hacemos 4 grupos. Las variables de mayor peso se s introducen

directamente por las entraddas de seleccióón S1 y S0 :

Las variables

v X e Y son las que ses han introduucido por las entradas

e de

seleccción ( S1 = x, S0 = y). Vemoos que hay 4 grupos

g de filass. El primer

grupoo se corresponnde con la entrrada I0, el siguuiente por la I1, el siguientee por la I2 y el último por la

I3.

3. El valor

v a introduucir por las enntradas I0,I1,I22, e I3 lo obtennemos miranddo las columnaas de

la derrecha (la colum

mna de Z y de O).

En el primer grupoo, cuando Z=00, O=1 y cuanndo Z=1, O=00, por tanto . Esa será

Reaalizado Por : Ing. Carlos Pillajo A

Universidad Polittécnica Salesianaa 9

SISTEEMAS DIGITALESS

la salida cuanndo se selecciione el canal 0,

0 por tanto poor su entrada habrá

h que intrroducir lo mism

mo: I0 = /z .

Ahora nos fijjamos en el siguiente grupoo, correspondieente a I1. En este

e caso, cuanndo Z=0, O=00 y cuando Z=

=1, O=1, por loo

que deducimos que O = I1 = z

Vamos a por el tercer grupoo. Si Z=0, O=0 y si Z=0, tam mbién O=0. Inndependientem

mente del valoor de Z, la salidda vale 0: I2=00.

Y para el últiimo grupo ocuurre que si Z=00, O=1, y si Z=1,

Z O=1. Dedducimos que I33=1

Si ahora haceemos la conexxiones obtenem

mos el mismo circuito que en

e el caso anteerior.

Ejemplo:

Implementaar la función F = A B + /A B /C + A /B /C

/ + A /B /C utilizando

u un

n multiplexor,

r, sin entrada de validación

n.

Utilizaremos el método baasado en las tablas de verddad. Lo que queremos

q impplementar es uun circuito quue tiene 3

entradas y unna salida. Com

mo tienen 3 variables

v de entrada,

e en geeneral necesitaaremos un mulltiplexor de 2 entradas de

control:

Ahora vamos siiguiente los paasos del

A

m

método. Primerro construimoss la tabla de

veerdad a partir F:

F

Laas entradas A y B las conecctamos

diirectamente a S1 y S0 respeectivamente.

Fiijándonos en las

l columnas de d C y F,

deeducimos las siguientes

s connexiones:

I0 = C ; I1= /C ; I2= /C ; I3= 1

El circuito finnal es el siguieente:

5.6.3. Implementación de funciones con mu

ultiplexores con

c entrada de

d validación

n

Para implem

mentar funcionnes también see puede usar la entrada de validación. En

E este caso nno todas las funciones

fu se

pueden implementar con este

e tipo de multiplexores.

m La entrada de

d validación la

l usamos commo si fuese unaa entrada más.

Ejemplo .- Implementar

I l siguiente fu

la unción utilizaando un multip

plexor F = A /B C + A B C

Primero utiliizaremos un multiplexor

m sinn entrada de validación,

v utiilizando el meetodo de las

tablas de verddad. Como la función

f tiene 3 variables, neecesitamos un multiplexor de

d 2 entradas

de control.

La tabla de verdad

v de esta función es:

Reaalizado Por : Ing. Carlos Pillajo A

Universidad Polittécnica Salesianaa 10

SISTEEMAS DIGITALESS

Las entradas A y B se coonectan directaamente a las entradas S1 y S0. Los valoores

que se introdducen por las entradas

e son: I0

I = 0, I1 = 0 , I2=I3=C. El circuito es el

siguiente:

¿Se podría immplementar essta función coon un multipleexor con entrada de validaciión?.

Si nos fijamoos en la funcióón F vemos quue podemos saacar factor com

mún en A:

F = A /B C + A B C = A (/B

( /C + B C)

¡¡ Y esa es laa ecuación de un multiplexoor de una entraada de controll y una entrada de validacióón!!. Si A=0, entonces F=0, y

si A=1, se com mporta como un multiplexoo. Por tanto intrroducimos A directamente por la entradaa de validaciónn y para el resto

necesitamos un multiplexoor de 1 entradaa de selecciónn. Y como la ecuación es tann sencilla, no hhace falta ni siquiera

s hacer el

método de laas tablas de verrdad, fijándonnos en su ecuacción es suficieente.

La ecuación de un multipleexor con una entrada

e de seleección es: F = /S I0 + S I1

Si introducim

mos B por S, /C

C por I0 y C por

p I1 ya lo tennemos:

5.7. R

Resumen

En este capítulo

c hemmos visto los l multipleexores y loos

demultiplexoores, constituuidos internam mente por puertas

p lógicaas.

Los multipleexores nos peermiten seleccionar entre uno de varioos

canales de entrada

e (tuberrías) para saccarlo por la salida.

s Por ello

disponen de unas entradaas de datos (por ( donde enntra el “agua””),

unas entraddas de seleccióón (Llaves dee paso) y un canal

c de salid

da. Estos canaales de datos ppueden ser dee varios bits,

sin embargo,, en este capíttulo nos he- mos

m centrado en los multipllexores que tienen canales de datos de 1 bits, puesto

que a partir de ellos poddemos construuir multiplexoores con canaales de datoss de mayor cantidad de biit, así como

multiplexores que tienen mayor

m cantidadd de canales de entrada.

También hemmos visto los demultiplexor

d res, que realizzan la funciónn inversa. Un canal

c de entradda (tubería) see puede

conectar a unna de las diferrentes salidas,, según el valoor introducidoo por las entraddas de seleccióón (llaves de paso).

p

Los multipleexores puedenn tener opcionnalmente unaa entrada de validación, que puede seer activa a nivvel alto o a

nivel bajo y actúa como una

u especie ded interruptor que permite que el multipllexor funcionee o no. Si estáá activada, el

multiplexor funciona

f malmente. Si la entrada de validación esstá desactivadaa, por la salidda del multipleexor siempre

norm

hay un ’0’.

Por último heemos visto quue con un multtiplexor tambiién se pueden implementarr funciones lóógicas, y es ottra alternativa

que tenemos además de lass puertas lógiccas. Metiante el método de las tablas dee verdad, poddemos saber fáácilmente quéé

variables hayy que conectarr a las entradaas del multipleexor.

Reaalizado Por : Ing. Carlos Pillajo A

Universidad Politécnica Salesiana Electrónica Digital

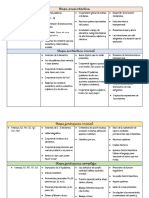

CIRCUITOS LÓGICOS MSI

Los sistemas digitales obtienen datos e información codificada en bianario la cual

continuamente se utiliza para diferentes operaciones; entre estas:

• Decodificación y codificación

• Multiplexión

• Demultiplexión

• Comparación

• Conversión de código

• Asignación del bus de datos.

Estas operaciones se han facilitado gracias a que existe a disponibilidad numerosos

Circuitos Integrados que realizan tales funciones y son denominados MSI (Integración

a Mediana Escala).

Vamos ha estudiar muchos tipos de dispositivos MSI, para cada uno, iniciaremos con un análisis sobre un

principio básico de operación y luego introduciremos Circuitos Integrados Específicos.

DECODIFICACORES

El decodificador es un circuito lógico que acepta un conjunto de entradas, representa un

numero binario y sólo activa la salida que corresponde a ese número de entrada.

En otras palabras, Un circuito decodificador analiza sus entradas, determina qué número

binario está presente allí y

activa la salida que

corresponde a ese número; el

resto de las salidas

permanecen inactivas.

En algunos decodificadores

no se utilizan todos los 2N

códigos posibles de entrada,

sino solo algunos cuantos. Ej.

Un decodificador BCD a

decimal tiene un código de

entrada de 4 bits y 10 líneas de salida que corresponden a los diez códigos BCD

En la figura anterior se muestra la

circuitería de un decodificador de tres

entradas y 23 = 8 salidas, en este circuito

se usan todas las compuertas AND, y por

lo tanto las salidas son activas en ALTO.

Este decodificador se puede denominar

de varias maneras:

• Decodificador de 3 a 8 líneas,

porque tiene 3 líneas de entrada y

8 líneas de salida.

• Decodificador binario a octal ó

convetidor binario a octal.

• Decodificador de 1 a 8, porque

sólo 1 de las 8 salidas se activa a

la vez.

By: MSc Carlos Pillajo 1

Universidad Politécnica Salesiana Electrónica Digital

Entradas ENABLE

Algunos decodificadores tiene una o más entradas de ENABLE que se emplean para

controlar la operación del decodificador. Ej.- si se

tiene una línea en común de ENABLE conectada a

una cuarta entrada de cada compuerta. Con esta

línea mantenida en ALTO, el decodificador

funcionará normalmente y el código de entrada

A,B,C determinará que salida es ALTA. Sin

embargo, con la ENABLE mantenida en BAJO,

todas las salidas se forzarán al estado BAJO sin

importar los niveles en las entradas A,B,C. Así ,

el decodificador se habilitará sólo si la ENABLE

es ALTA.

En el siguiente diagrama podemos ver un

decodificador 74ALS138. EN donde primero

obserbe que sus salidas son activas en BAJO, otra señal es el etiquetado de las salidas

como /O7, /Oe6, /O5, etc. La barra sobrepuesta significa que se trata de salidas activas

en BAJO.

El código de entrada se aplica a A2,A1 yA0, donde A2 es el

MSB, las entradas /E1,/E2, y E3 son entradas de ENABLE

separadas que se combinan en la compuerta AND, para

habilitar las salidas y que respondan a la combinación de

entrada A2,A1 y A0, la salida de la compuerta AND debe

ser ALTA. Lo anterior ocurrirá sólo cuando /E1=E2=0 y

E3=1. Si una o más de las entradas de ENABLE está en su

estado inactivo, la salida AND será BAJA, lo que forzará a

todas las salidas del decodificador a su estado inactivo en

ALTO, sin importar el código de entrada. Esto se resume en

la siguiente

tabla de

verdad.

Recuerde que X representa la condición

“no importa”.

Ej: Indique los estados de las salidas del

74LS138 para cada uno de los siguientes

conjuntos de entradas.

a.- E3 = /E2 = 1 ; /E1= 0, A2=A1=A0=0 Sol.= Todas Salidas en ALTO

b.- E3 = 1; /E2 = /E1= 0, A2= 0 A1=A0=1 Sol.= O3 en bajo.

Decodificador de BCD a decimal.- en el siguiente diagrama se presenta un

decodificador de BCD a decimal 7442 ó 74LS42. Cada

salida pasa a BAJO sólo cuando se aplica una entrada BCD

correspondiente. Ej.- /O5 pasará a bajo sólo cuando las

entradas DCBA = 1001 , etc. Para combinaciones de entrada

que son inválidas para BCD, ninguna de las salidas se

activará. A este decodificador se lo denomina también

decodificador de 4 a 10 ó decodificador 1 a 10, note que este

no tiene la entrada ENABLE.

Decodificador-exitador BCD a Decimal.- el TTL 7445 es un decodificador-excitador de

BCD a decimal. El término exitador se agrega a su descripción porque este CI tiene

By: MSc Carlos Pillajo 2

Universidad Politécnica Salesiana Electrónica Digital

salidas de colector abierto que pueden operar con límites de corriente y voltaje mayores

que una salida TTL normal. Las salidas del 7445 pueden sumir hasta 80mA en el estado

BAJO y pueden ascender hasta 30V en el estado ALTO. Esto las hace adecuadas para

manejar de manera directa cargas de LEDs o lámparas o motores de CD.

APLICACIONES.

Los decodificadores se emplean cuando una salida o un grupo de éstas se deban activar

sólo cuando ocurra una combinación específica de niveles de entrada. Estos niveles de

entrada a menudo los proporcionan las salidas de un contador o de un registro. Cuando

las entradas del decodificador provienen de un contador o de un registro. Cuando las

entradas del decodificador provienen de un contador que se está pulsando de manera

continua, las salidas del decodificador se activan en forma secuencial y se pueden

emplear como señales de sincronización para encender o apagar dispositivos en

tiempos específicos.

Los decodificadores son también usados en los microprocesadores para convertir

instrucciones binarias en señales de tiempo, para controlar máquinas en procesos

industriales o implementar circuitos lógicos avanzados. El decodificador convierte

números binarios en sus equivalentes Octales (base 8), decimales (base 10) y

Hexadecimales (base 16).

DECODIFICADORES-EXCITADORES DE BCD A 7 SEGMENTOS

La mayoria del equipo digital tiene algún medio para desplegar visualmente la

información de manera que la entienda fácilmente el usuario u operador. Esta

información consiste en datos numéricos, pero también puede ser

alfanumérica. Uno de los métodos más comunes para desplegar

digitos numéricos se emplea una configuración de 7 segmentos

para formar los caracteres 0 al 9 y a veces caracteres hexadecimales

A-F. En una configuración común se emplean diodos emisores de

luz LED para cada segmento. Si se controla la corriente a través de

cada LED algunos segmentos se iluminaran y otros permanecerán

oscuros, de modo que se generará el patrón de carácter deseado.

El decodificador-excitador de BCD a 7 segmentos se usa para tomar una entrada BCD

de cuatro bits y proporcionar las salidas que pasarán corriente a través de los segmentos

apropiados para desplegar visualmente el dígito decimal.

En la siguiente figura se muestra un decodificador-excitador de BCD a 7 segmentos

TTL (7446 ó 7447) usado para excitar una lectura LED de 7 segmentos. Cada segmento

consta de uno ó mas

LEDs. Todos los ánodos

de los LEDs están

conectados a

Vcc(+5Vdc). Los

cátodos de los LEDs

están conectados

mediante resistencias

limitadoras de corriente

a las salidas correctas

del decodificador-

excitador, el cual tiene

By: MSc Carlos Pillajo 3

Universidad Politécnica Salesiana Electrónica Digital

salidas activas en BAJO que son transistores de exitación de colector abierto, los cuales

pueden sumir una gran cantidad de corriente. Esto se debe a que las lecturas de los LED

quizá requieran 10 a40 mA por segmento dependiendo de su tipo y tamaño.

Los decodificadores-excitadores de 7 segmentos, como el 7446/7447, son excepciones a

la regla debido a que los circuitos de decodificación sólo activarán una salida por cada

combinación de entradas. Más bien, activan un patrón único de salidas para cada

combinación de entradas.

Visualizadoes LED de ánodo común Vs. Cátodo común

Los Displays usado en la figura anterior es del tipo ánodo común porque los ánodos de

todos los segmentos están conectados a Vcc. En otro tipo de displays de 7 segmentos se

usa una configuración de cátodo común en la cual los cátodos de todos los segmentos

están unidos y conectados a tierra. Este tipo de display se lo debe utilizar con un

decodificador de BCD a 7 segmentos con salidas activas en ALTO (7448 ) que apliquen

un voltaje ALTO a los ánodos de los segmentos a activar.

Ej.- Cada segmento de un Display de 7 segmentos tiene una capacidad nominal para

operar a 10mA a 2.7V para una brillantez normal. Calcule el valor de la resistencia

limitante de corriente necesaria para producir aproximadamente 10 mA por segmento.

Rs= 2.3V / 10mA = 230 ohms , por lo tanto Rs= 220 ohms

CODIFICADORES

La mayoría de los decodificadores aceptan un código de entrada y producen un ALTO

(o un BAJO) en una y sólo en una línea de salida. En otras palabras un decodificador

identifica, reconoce o detecta un código en particular. Lo opuesto de este proceso de

decodificación se le llama codificación y se lleva a cabo mediante un circuito lógico

llamado codificador.

Un codificador tiene un número

de líneas de entrada, de las cuales

sólo una se activa en un tiempo

determinado y produce un código

de salida de N bits, dependiendo

de cuál entrada se active.

Ya vimos un decodificador de

binario a octal (decodificador de 3

a 8 lineas) acepta un código de entrada de tres bits

y activa una de ocho lineas de salida

correspondiente a ese código

Un codificador de octal a binario (codificador de

8 a 3 líneas) realiza la función opuesta; acepta 8

líneas de entrada y produce un código de salida de

tres bits correspondiente a la entrada activada.

Del grafico se puede verificar que un BAJO en

cualquier entrada individual producirá el código

binario de salida correspondiente a esa entrada.

By: MSc Carlos Pillajo 4

Universidad Politécnica Salesiana Electrónica Digital

Ej. /A3 (mientras todas las entradas son ALTAS) producirá O2=0, O1=1, y O0 = 1 que

es el código binario para el 3

Codificado de Prioridad .- una desventaja del circuito codificador simple anterior

cuando se activa más de una entrada a la vez. Una versión modificada de este circuito,

llamado codificador de prioridad, incluye la lógica necesaria para asegurar que cuando

dos o más entradas se activen, el código de salida corresponderá a la entrada que tiene

asociada el mayor de los números. Ej. Cuando /A3 y /A5 sean BAJAS el código de

salida será 101 (5).

Codificador de prioridad de decimal a BCD 74147

En la figura se tiene el símbolo para el

74147, que funciona como codificador de

prioridad de decimal a BCD. Tiene 9

entradas activas en BAJO las cuales

representan los números 1 al 9 y produce el

código BCD inverso correspondiente a la

entrada activada con el número mayor.

Codificador Interruptor.- Como se

indica en la siguiente figura se puede

utilizar un 74147 como codificador

interruptor. Los 10 interruptores podrían

ser los interruptores del teclado de una

calculadora, representando los dígitos del 0 al 9 Normalmente los interruptores son del

tipo abierto normal, de modo que todas las entradas del codificador normalmente son

ALTAS y la salida BCD

es 0000 (note los

inversores). Cuando se

presiona la tecla de un

dígito el circuito

producirá el código BCD

para ese dígito. Como el

74LS147 es un

codificador de prioridad,

la opresión simultánea de

teclas producirá el código

BCD de la tecla con el

número mayor.

By: MSc Carlos Pillajo 5

Universidad Politécnica Salesiana Electrónica Digital

Ejercicios a realizar.

1.- En la figura se muestra cómo cuatro decodificadores 74LS138 y un INVERSOR se

pueden configurar para que funcionen como un decodificador de 1 a 32. Los

decodificadores están etiquetados Z1 a Z4 para su fácil referencia y las ocho entradas

de cada uno se combinan en 32 salidas. Las salidas Z1 son /O0 a /O7 , y asi

sucesivamente y las salidas de Z4 son /O24 a /O31 Un código de entrada de 5 bits

A4A3A2A1A0 sólo activará una de las 32 salidas, para cada uno de los 32 códigos

posibles.

a. Que salida se activará para A4A3A2A1A0 = 01101

b. Que intervalo de códigos de entrada activará el chip Z4

2.- Se puede activar más de una salida del decodificador al mismo tiempo?

3.- Cual es la función de la entrada ENABLE de un decodificador?

4.- Cuales segmentos del display de ánodo común se iluminarán para una entrada del

decodificador-excitador de 1001?

5.- Cada segmento de un Display de 7 segmentos tiene una capacidad nominal para

operar a 12mA a 2.5V para una brillantez normal. Calcule el valor de la resistencia

limitante de corriente necesaria para producir aproximadamente 12 mA por segmento.

By: MSc Carlos Pillajo 6

Universidad Politécnica Salesiana Electrónica Digital

6.- Determine las salidas del codificador mostrado en la siguiente figura cuando /A3 y

/A5 están simultáneamente en BAJO.

By: MSc Carlos Pillajo 7

Universidad Politécnica Salesiana Electrónica Digital

MULTIPLEXORES

Un estéreo de los que tenemos en casa quizá tenga un interruptor para seleccionar

música entre una de 4 fuentes: un casete de cinta, un disco compacto CD, un

sintonizador de radio o una entrada auxiliar de auido o vídeo. El interruptor selecciona

una de las señales electrónicas de estas cuatro fuentes y la envía al amplificador de

potencia y de allí a las bocinas. En términos simples, esto es lo que hace un multiplexor

MUX selecciona una de varias señales de entrada y la envía a la salida.

Un multiplexor digital o selector de datos

es un circuito lógico que acepta varias

entradas de datos digitales y selecciona

una de ellas en cualquier instante para

enviarla a la salida. El enrutamiento de la

entrada de datos deseada hacia la salida se

controla mediante entradas de SELECT.

En la figura anterior se muestra el diagrama

funcional de un multiplexor digital general.

El multiplexor actúa como un interruptor de

posiciones múltiples controlado digitalmente,

donde el código digital aplicado a las

entradas de SELECT controla que entradas

de datos se cambiarán a la salida.

Dicho de otra manera un multiplexor

selecciona 1 de N fuentes de datos de entrada

y transmite los datos seleccionador a un solo

canal de salida. A esto se le llama multiplexaje.

Multiplexor básico de dos entradas.

En la siguiente figura se muestra la

circuitería lógica de un multiplexor de

dos entradas, con entradas de datos I0

e I1 y una entrada SELECT, S. El

nivel lógico aplicado a la entrada S

determina que compuerta AND se

habilita, de modo que su entrada de

datos pase por la compuerta OR hacia

la salida Z. Considerando esto de otro

modo, la expresión booleana para la

salida es: Z = Io*/S + I1*S

Multiplexor de cuatro entradas

La misma idea básica se puede usar para formar el

multplexor de cuatro entradas que se muestra en

la siguiente figura. En este caso hay cuatro

entradas que se transmiten selectivamente a la

salida, de acuerdo a las cuatro combinaciones

posibles de las entradas de SELECT S1So

S1 So Salida

0 0 z = Io 1 0 z = I2

0 1 z = I1 1 1 z = I3

By: MSc Carlos Pillajo 1

Universidad Politécnica Salesiana Electrónica Digital

Multiplexor de ocho entradas

En la siguiente figura se muestra el diagrama lógico

del multiplexor de 8 entradas 74LS151 este

multiplexor tiene una ENABLE –E y proporciona

las salidas normal e invertida. Cuando /E=0, las

entradas de SELECT S2S1So escogerán una

entrada de datos de (Io a I7) para el paso hacia la

salida Z.

Mux cuádruple de dos entradas 74LS157

Este es un circuito integrado multiplexor muy útil que contiene cuatro multiplexores de

dos entradas, como el que se indica en la siguiente figura. Note la forma en que se

etiquetan las entradas y salidas de datos. Recuerde

que todas las salidas se deshabilitarán (BAJAS)

cuando /E = 1.

Es útil considerar a este multiplexor como si fuera

un multiplexor simple de dos entradas, pero en el

cual cada entrada tiene cuatro líneas y la salida

también cuatro líneas.

APLICACIONES DE LOS MULTIPLEXORES

Los circuitos multiplexores tiene numerosas y variadas aplicaciones en sistemas

digitales de todos tipos. Entre éstas, la SELECT de datos, enrutamiento de datos,

secuencia de operaciones, conversión de paralelo a serial, generación de forma de ondas

y generación de funciones lógicas.

Enrutamiento de datos.- los multiplexores pueden enlutar datos desde una de varias

fuentes a un destino. EN una

aplicación común se usan

multiplexores 74LS157 para

seleccionar y visualizar el

contenido de cualquiera de los

contadores BCD, usando un solo

conjunto de decodificadores-

excitadores y Displays como se

muestra en la figura.

El objetivo de la técnica de

multiplexaje, como la que

empleamos aquí, es compartir el

tiempo de los decodificadores-

excitadores y circuitos de

visualización entre dos

contadores, en vez de tener un

conjunto separado de

decodificadores excitadores y

visualizadores para cada

contador.

By: MSc Carlos Pillajo 2

Universidad Politécnica Salesiana Electrónica Digital

Conversión de paralelo a serial .- Muchos sistemas digitales procesan datos binarios

en forma paralela (todos los bits a la vez) porque es más rápido.

Sin embargo, cuando los datos se transmiten a

distancias relativamente grandes, la

configuración en paralelo es indeseable porque

requiere un gran número de líneas de

transmisión. Por este motivo, los datos binarios o

la información que está en forma paralela con

frecuencia se convierten a forma serial antes de

ser transmitidos a un destino remoto. Un método

para llevar a cabo esta conversión de paralela a

serial, consiste en usar un multiplexor.

Secuencia de Operaciones.- Se utiliza los

multiplexores como parte de un secuenciador de

control que pasa por etapas, cada una lleva a

cabo alguna parte del proceso físico que está

siendo controlado.

Generación de Funciones Lógicas .- Los

multiplexores se pueden usar para implementar

funciones lógicas de manera directa a partir de

una tabla de verdad, sin que se necesite la

simplificación. Cuando un multiplexor se usa

para este fin, las entradas SELECT se emplean

como variables lógicas y cada entrada de datos

se conecta de manera permanente en ALTO o

BAJO, según sea necesario para satisfacer la

tabla de verdad.

DEMULTIPLEXORES

(DISTRIBUIDORES DE DATOS)

Un multiplexor toma varias entradas y

transmite una de ellas a la salida.

Un demultiplexor (DEMUX) realiza la

operación inversa: toma una sola

entrada y la distribuye sobre varias

salidas.

En la figura se muestra el diagrama

funcional de un demultiplexor digital. El

código de entrada SELECT determina a

qué salida se transmitirá la entrada de

DATOS. En otras palabras, el

By: MSc Carlos Pillajo 3

Universidad Politécnica Salesiana Electrónica Digital

demultiplexor toma una fuente de datos de entrada y la distribuye de manera selectiva a

1 de N canales de salida, igual que un interruptor de posiciones múltiples.

Demultiplexor de 1 línea a 8 líneas.

En la siguiente figura se muestra el diagrama

lógico de un demultiplexor que distribuye una

línea de entrada a ocho líneas de salida. El

circuito demultiplexor es muy similar al circuito

decodificador de 3 líneas a 8 líneas, como se

indicó muchos decodificadores de CI tienen una

entrada de ENABLE, que es una entrada

adicional agregada a las compuertas del

decodificador. Por lo tanto, este tipo de chip

decodificador se puede usar como un

demultiplexor, con las entradas de código

binario que sirven como las entradas SELECT y la entrada de ENABLE funge como la

entrada de datos I. Por esta razón, los fabricantes de CI a menudo llaman este tipo de

dispositivos decodificador-demultiplexor y se puede emplear para desempeñar una u

otra función.

Demultiplexor de Reloj.- El principio de multiplexaje tiene muchas aplicaciones. En

la siguiente figura se muestra el

demultiplexor 74LS138 que es usado

como demultiplexor de reloj. Bajo el

control de las líneas de SELECT, la señal

de reloj se encamina al destino deseado

COMPARADORES DE MAGNITUD

Otro miembro útil de la categoría de MSI de

CI es el comparador de magnitud. Es un

circuito lógico combinacional que compara

dos cantidades binarias de entrada y genera

salidas para indicar cuál tiene la magnitud

mayor.

En la siguiente figura se muestra el símbolo

lógico del comparador de magnitud 74LS85

El 74LS85 compara dos números binarios

de cuatro bits sin signo. Uno de ellos es

A3A2A1A0, el cual se denomina palabra A; el otro es B3B2B1B0 y se llama palabra B

En este caso A y B representan cantidades numéricas.

By: MSc Carlos Pillajo 4

Universidad Politécnica Salesiana Electrónica Digital

El 74LS85 tiene tres salidas activas en ALTO. La salida O a b será ALTO cuando la

magnitud de la palabra A sea mayor que la magnitud de la palabra B. La salida O a=b

será ALTA cuando las palabras A y B sean identicas.

Las entradas en cascada proporcionan un medio

para ampliar la operación de comparación a más de

cuatro bits , conectando en cascada dos o más

comparadores de cuatro bits.

Cuando se realiza una comparación de cuatro bits

las entradas en cascada se debe conecta como se

indica. Para que el comparador produzca las salidas

correctas.

Cuando se van a conectar dos comparadores en

cascada, las salidas del comparador de orden inferior se conectan a las entradas

correspondientes del de orden superior como se indica en la figura, donde el

comparador a la izquierda compara los cuatro bits de orden inferior de las dos palabras

de ocho bits A7A6A5A4A3A2A1A0 Y B7B6B5B4B3B2B1B0 Sus salidas se

alimentan a las entradas en cascada del comparador de la derecha, que compara los bits

del orden superior. Las salidas del comparador de orden superior son las salidas finales

que indican el resultado de la comparación de ocho bits.

By: MSc Carlos Pillajo 5

Universidad Politécnica Salesiana Electrónica Digital

Ejercicios a realizar.

1.- En la figura se utilizan dos 74LS151 un

Inversor y una compuerta OR analice el circuito

si

Que entrada será seleccionada a la salida si

a) S3S2S1S0 = 01101 X = ____

b) S3S2S1S0 = 10010 X = ____

2.- Determine las condiciones de entrada que se

requieren en cada salida Z para adoptar el nivel

lógico de su entrada Io correspondiente. En el

mux 74LS157

3.- Un cierto multiplexor puede conectar una de

32 entradas de datos a sus salida. ¿Cuántas entradas diferentes tiene este MUX, dibuje

su diagrama.

4.- Implemente la función lógica Z= /A/BC + AB/C + A/BC utilice el MUX 74LLS151,

escriba la tabla para la función.

5.- Determine que salida se activará y en que estado estará para la operación de la

configuración de comparación de ocho bits para los siguientes casos:

a.- A7A6A5A4A3A2A1A0 = 10101111 ; B7B6B5B4B3B2B1B0 = 10110001 _____

b.- A7A6A5A4A3A2A1A0 = 10101111 ; B7B6B5B4B3B2B1B0 = 10101001 ______

By: MSc Carlos Pillajo 6

Vous aimerez peut-être aussi

- Laboratorio #3 - Rectificacion de Onda Completa y FiltradoDocument23 pagesLaboratorio #3 - Rectificacion de Onda Completa y Filtradodaniel rochaPas encore d'évaluation

- Brazo Robot Con ArduinoDocument3 pagesBrazo Robot Con ArduinoHenry Chiclla HuamanPas encore d'évaluation

- S01. Diodo Semiconductor PDFDocument73 pagesS01. Diodo Semiconductor PDFLa puta K te parioPas encore d'évaluation

- Informe 2 Repaso Teorema de MorganDocument5 pagesInforme 2 Repaso Teorema de MorganGüerrëröYöylëPas encore d'évaluation

- Multiplex DemultiplexorDocument13 pagesMultiplex DemultiplexorSamn EddyPas encore d'évaluation

- Laboratorio 7 - Circuitos Aritméticos RestadoresDocument9 pagesLaboratorio 7 - Circuitos Aritméticos RestadoresIan MelgarejoPas encore d'évaluation

- Circuitos Digitales 1 Informe 3Document39 pagesCircuitos Digitales 1 Informe 3Rasec MundoPas encore d'évaluation

- Practica 3Document12 pagesPractica 3fr0zt3rPas encore d'évaluation

- 26 - 2circuitos PAL, PLA, GAL - ARDUINODocument44 pages26 - 2circuitos PAL, PLA, GAL - ARDUINOJeison ManobandaPas encore d'évaluation

- Circuito de Polarización FETDocument6 pagesCircuito de Polarización FETCristian BalcarcePas encore d'évaluation

- Puente de Win Informe CalculosDocument6 pagesPuente de Win Informe CalculosDaniel CevallosPas encore d'évaluation

- Proyecto MoctezumaDocument16 pagesProyecto Moctezumadavid chavarriaPas encore d'évaluation

- 6 Circuitos Combinacionales P ImprimirDocument36 pages6 Circuitos Combinacionales P ImprimirFabian AcostaPas encore d'évaluation

- TransistoresDocument17 pagesTransistoresErwin Alfonso Balcazar MoraledaPas encore d'évaluation

- Practica Calificada de Circuitos Digitales 01-02TDocument1 pagePractica Calificada de Circuitos Digitales 01-02TXavier PalaciosPas encore d'évaluation

- Previo 6 - MultiplexoresDocument8 pagesPrevio 6 - MultiplexoresAnoniuox Maz NaahPas encore d'évaluation

- Practica # 3 Electrónica Digital IDocument8 pagesPractica # 3 Electrónica Digital ImilindrosoPas encore d'évaluation

- Guia - ADC0808Document6 pagesGuia - ADC0808Eduardo Mayorga EspejoPas encore d'évaluation

- Protocolo de Enrutamiento RIP GNS3Document6 pagesProtocolo de Enrutamiento RIP GNS3Juan IngaPas encore d'évaluation

- Ejercicios Lógica CombinacionalDocument1 pageEjercicios Lógica CombinacionalBecker Orlando Perez FIallosPas encore d'évaluation

- Transmisor Inalambrico de Audio y VideoDocument9 pagesTransmisor Inalambrico de Audio y VideoHuevo Frito Doble YemaPas encore d'évaluation

- Informe Final Laboratorio N - 3Document18 pagesInforme Final Laboratorio N - 3Michael Alexander0% (1)

- 7 Dispositivos Integrados PDFDocument105 pages7 Dispositivos Integrados PDFcchristt2584Pas encore d'évaluation

- Rectificadores Trifasicos y Multifasicos de Onda Completa, InformeDocument6 pagesRectificadores Trifasicos y Multifasicos de Onda Completa, InformeVíctor •Pas encore d'évaluation

- Ejercicios ConvolucionDocument4 pagesEjercicios Convolucionogidoc0% (1)

- Diseño Del Amplificador Con BJT 2N3904Document4 pagesDiseño Del Amplificador Con BJT 2N3904Omar ChirinosPas encore d'évaluation

- CMOSDocument21 pagesCMOSJonathanDavidPas encore d'évaluation

- Tarea 1Document16 pagesTarea 1Mauricio Glez.Pas encore d'évaluation

- Capitulo9 CircuitosLogicosDocument13 pagesCapitulo9 CircuitosLogicosRonald Requejo SamamePas encore d'évaluation

- Ejercicios de Puertas LogicasDocument2 pagesEjercicios de Puertas LogicasJhonny Choez Burgos100% (1)

- Practica 2Document4 pagesPractica 2servando graterolPas encore d'évaluation

- 1 - 16F873-BDocument48 pages1 - 16F873-BJuan Martin Alderete GobbatoPas encore d'évaluation

- 04 - Circuitos Rectificadores y FiltroDocument11 pages04 - Circuitos Rectificadores y Filtrodiego181802Pas encore d'évaluation

- Algebra de Boole Simplificación de FuncionesDocument7 pagesAlgebra de Boole Simplificación de FuncionesMadelaine Caro CocaPas encore d'évaluation

- LABORATORIO 4 Filtros ActivosDocument10 pagesLABORATORIO 4 Filtros ActivosChristopher PalaciosPas encore d'évaluation

- TRANSISTORDocument14 pagesTRANSISTOROliver Herrera AcebedoPas encore d'évaluation

- Unidad 3 Campos Escalares y VectorialesDocument37 pagesUnidad 3 Campos Escalares y VectorialespabloPas encore d'évaluation

- Polarización en DC de Los Transistores JFETDocument5 pagesPolarización en DC de Los Transistores JFETJuan sebastian Chacón VegaPas encore d'évaluation

- Consulta, Factor de Rizado y FiltrosDocument3 pagesConsulta, Factor de Rizado y FiltrosPaty SalazarPas encore d'évaluation

- Adaptacion de ImpedanciasDocument5 pagesAdaptacion de ImpedanciasjuansantospalaciosPas encore d'évaluation

- Capitulo 6. Sistemas Secuenciales PDFDocument24 pagesCapitulo 6. Sistemas Secuenciales PDFEfra IbacetaPas encore d'évaluation

- Experimentos de Circuitos Recortadores y Sujetadores Con DiodosDocument17 pagesExperimentos de Circuitos Recortadores y Sujetadores Con DiodosGovanna LunaPas encore d'évaluation

- Cuestionario Previo 7 Diseño Digital FI UNAMDocument3 pagesCuestionario Previo 7 Diseño Digital FI UNAMPandaPas encore d'évaluation

- Laboratorio N01 Control Digital PDFDocument11 pagesLaboratorio N01 Control Digital PDFjorgePas encore d'évaluation

- Practica 3 - Lab Electronica IIIDocument5 pagesPractica 3 - Lab Electronica IIIBrayan RodriguezPas encore d'évaluation

- Informe 6Document2 pagesInforme 6Dario OroscoPas encore d'évaluation

- Transformada Discreta de Fourier Ejercicios PDFDocument4 pagesTransformada Discreta de Fourier Ejercicios PDFandres felipe sandoval porrasPas encore d'évaluation

- Unidad 1 - Familias Logicas de ICDocument15 pagesUnidad 1 - Familias Logicas de ICCarlos OrtegaPas encore d'évaluation

- Unidad 2Document21 pagesUnidad 2c.j. rodriquezPas encore d'évaluation

- Labort Sistemas DigitalesDocument25 pagesLabort Sistemas DigitalesJuan FieePas encore d'évaluation

- Practica 3 Hector MartinezDocument21 pagesPractica 3 Hector MartinezHéctor J. MartínezPas encore d'évaluation

- Andy Ramirez Parte III InteresanteDocument25 pagesAndy Ramirez Parte III InteresanteGERARDO CABRERAPas encore d'évaluation

- Lab 4 - ADC-DAC-2018 - 2Document3 pagesLab 4 - ADC-DAC-2018 - 2fieeg4Pas encore d'évaluation

- Laboratorio 5 Arduino Motor DC Robótica UPNDocument8 pagesLaboratorio 5 Arduino Motor DC Robótica UPNPrimus 2018Pas encore d'évaluation

- Interfazado General Del Computador (Sistema Mínimo)Document21 pagesInterfazado General Del Computador (Sistema Mínimo)Luis PerezPas encore d'évaluation

- Cuestionario Previo 4 Diseño Digital FI UNAMDocument10 pagesCuestionario Previo 4 Diseño Digital FI UNAMPandaPas encore d'évaluation

- Circuitos CombinacionalesDocument38 pagesCircuitos CombinacionalesJesus Francisco Diaz Alvarado0% (1)

- MonografiaDocument11 pagesMonografiayinoPas encore d'évaluation

- Combinacionales y Secuenciales PDFDocument45 pagesCombinacionales y Secuenciales PDFFranciscoGuadalupeContrerasBarcenasPas encore d'évaluation

- Rock - EncuestaDocument7 pagesRock - EncuestaByrön UscaPas encore d'évaluation

- Historia de La Teoría CríticaDocument2 pagesHistoria de La Teoría CríticaHoracioPas encore d'évaluation

- Dionisio de HalicarnasoDocument3 pagesDionisio de Halicarnasoteseo_4Pas encore d'évaluation

- Arquitectura ConceptualDocument2 pagesArquitectura ConceptualPamela RosarioPas encore d'évaluation

- Repaso HIS-011.Document21 pagesRepaso HIS-011.Cristina Pineda67% (3)

- Innovación EmpresarialDocument2 pagesInnovación EmpresarialLuisaPas encore d'évaluation

- La Novela Puneña - José Luis Velasquez GarambelDocument24 pagesLa Novela Puneña - José Luis Velasquez GarambelMack Mcclain0% (1)

- Naín Nómez AntologíaDocument185 pagesNaín Nómez AntologíaEscritura y Edición ICPas encore d'évaluation

- Plan Lector ESCARDocument6 pagesPlan Lector ESCARCrysRodPas encore d'évaluation

- JURISPRUDENCIA LABORAL - El Salvador PDFDocument99 pagesJURISPRUDENCIA LABORAL - El Salvador PDFHéctor Tulio BairesPas encore d'évaluation

- PHy POHDocument35 pagesPHy POHJEINY VIRGINIA KANTUTA FLORESPas encore d'évaluation

- Diseño de Estrategias Didácticas para La Formación de CompetenciasDocument3 pagesDiseño de Estrategias Didácticas para La Formación de CompetenciasJessica RodriguezPas encore d'évaluation

- 3 Diapositiva La Jurisdicción y La CompetenciaDocument12 pages3 Diapositiva La Jurisdicción y La Competenciavalentina vargasPas encore d'évaluation

- Forma y Tamaño de Dientes en Acrilicos para Protesis ParcialesDocument4 pagesForma y Tamaño de Dientes en Acrilicos para Protesis ParcialesOscar A ChalenPas encore d'évaluation

- TDAH, Atención y El Sacádico - OdtDocument5 pagesTDAH, Atención y El Sacádico - OdtMaria GarciaPas encore d'évaluation

- Grandes Poetas VenezolanosDocument6 pagesGrandes Poetas VenezolanosOmar RodriguezPas encore d'évaluation

- Mine To Mills ESPAÑOLDocument7 pagesMine To Mills ESPAÑOLJuanPas encore d'évaluation

- Apuntes Sobre La ComunicaciónDocument2 pagesApuntes Sobre La ComunicaciónIngridAmayaCarrascoPas encore d'évaluation

- SF 36v2 CastDocument7 pagesSF 36v2 CastmartynbbPas encore d'évaluation

- Fraude SocietarioDocument38 pagesFraude SocietarioKevin Cáceres Cerdán100% (2)

- Nacio Como Adivinar Con El ObiDocument2 pagesNacio Como Adivinar Con El Obieleggua85Pas encore d'évaluation

- S0 - PerfilPUC-Dape - 1Document4 pagesS0 - PerfilPUC-Dape - 1Jean Pieer Anthony Quispe GasparPas encore d'évaluation

- Desarrollo LinguisticoDocument5 pagesDesarrollo Linguisticolakld ksdjjlkPas encore d'évaluation

- Traduccion Preguntas Ingles 2 y 3Document13 pagesTraduccion Preguntas Ingles 2 y 3Maria Guadalupe DiazPas encore d'évaluation

- Teoría ConjuntistaDocument4 pagesTeoría Conjuntistaleandro100% (2)

- Leyendas Mexicanas La LloronaDocument3 pagesLeyendas Mexicanas La LloronaDanielPas encore d'évaluation

- Epidemiología Básica.3Document41 pagesEpidemiología Básica.3VICTOR ROJASPas encore d'évaluation

- 4 - Tus Emociones y SentimientosDocument4 pages4 - Tus Emociones y SentimientosJulio Cesar CamachoPas encore d'évaluation

- Analisis Gramatical WordDocument6 pagesAnalisis Gramatical WordAndrea Ochoa100% (1)

- Para Que Quieres Vivir 15 AñosDocument5 pagesPara Que Quieres Vivir 15 AñosCris GonzalesPas encore d'évaluation