Académique Documents

Professionnel Documents

Culture Documents

EE309 MP Mod1 Ktunotes - in

Transféré par

Divya KrishnanDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

EE309 MP Mod1 Ktunotes - in

Transféré par

Divya KrishnanDroits d'auteur :

Formats disponibles

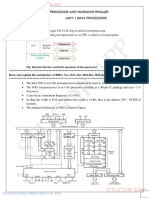

EE309 Microprocessors and Embedded Systems

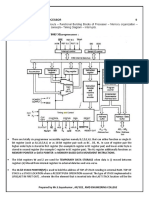

Internal Architecture of 8085

8085 is pronounced as "eighty-eighty-five" microprocessor. It is an 8-bit microprocessor designed by

Intel in 1977 using NMOS technology.

It has the following configuration −

8-bit data bus

16-bit address bus, which can address up to 64KB

A 16-bit program counter

A 16-bit stack pointer

Six 8-bit registers arranged in pairs: BC, DE, HL

Requires +5V supply to operate at 3 MHZ single phase clock

It is used in washing machines, microwave ovens, mobile phones, etc.

8085 Microprocessor – Functional Units

S . I N

U N OTE

8085 consists of the following functional units −

T

Accumulator

K

It is an 8-bit register that is part of the ALU. The register is used to store 8 bit data and to perform

arithmetic and logical operations. The result of an operation is stored in the accumulator. The

accumulator is also identified a register A

Arithmetic and logic unit (ALU)

As the name suggests, it performs arithmetic and logical operations like Addition, Subtraction, AND,

OR, etc. on 8-bit data. It includes the accumulator, the temporary register, the ALU circuits & five flags.

The temp register is used to hold data during an arithmetic and logical operation. The result is stored in

the accumulator and the flags are set or reset according to the result of the operation.

General purpose register

There are 6 general purpose registers in 8085 processor, i.e. B, C, D, E, H & L. Each register can hold

8-bit data. These registers can work in pair to hold 16-bit data and their pairing combination is like B-C,

D-E & H-L. The programmer can use these registers to copy or store data into the register by using data

copy instructions.

Program counter

1 Module 1 Notes prepared by srikanth

Downloaded from Ktunotes.in

EE309 Microprocessors and Embedded Systems

It is a 16-bit register used to store the memory address location of the next instruction to be fetched.

Microprocessor increments the program whenever an instruction is being executed, so that the program

counter points to the memory address of the next instruction that is going to be fetched and executed.

Stack pointer

It is also a 16-bit register works like stack, which is always incremented/decremented by 2 during push

& pop operations. It points to the top of the stack. The beginning of the stack is defined by loading a 16

bit address in the stack pointer.

Temporary register

2 additional registers, W and Z are included in the register array. These registers are used to hold 8 bit

data during the execution of some instructions. They are not available to the programmer.

Flag register

It is an 8 bit register. It consists of 5 flip flops which changes its status according to the result stored in

an accumulator. 3 bits are not used. It is also known as status register. It is connected to the ALU.

The five flag bits are: Sign(S), zero (z), Auxiliary carry (AC), Parity (P), Carry(C)

The bit position of the flip flop in flag register is:

S . I N

OTE

D7 D6 D5 D4 D3 D2 D1 D0

S Z

K T U N x AC x P x CY

Sign flag (S) - This flag is used with signed numbers. If D7 of the result in accumulator is 1 then sign

flag is set otherwise reset. As we know that a number on the D7 always decides the sign of the number.

If D7 is 1: the number is negative and if D7 is 0: the number is positive. It is irrelevant for operations of

unsigned numbers.

Zero flag (Z) - If the result stored in an accumulator is zero then this flip flop is set otherwise it is reset.

Auxiliary Carry (AC) - If any carry goes from D3 to D4 in the output then it is set otherwise it is

reset. Significant in BCD addition and subtraction

Parity flag (P) - If the no of 1's is even in the output stored in the accumulator then it is set otherwise it

is reset for the odd.

Carry flag (C) - If the result stored in an accumulator generates a carry from D7 in its final output then

it is set otherwise it is reset.

Instruction register and decoder

It is an 8-bit register. When an instruction is fetched from memory, it is loaded in the Instruction

register. Instruction decoder decodes the information present in the Instruction register. The instruction

register not programmable and cannot be accessed through any instruction.

Timing and control unit

It provides timing and control signal to the microprocessor to perform operations. Following are the

timing and control signals, which control external and internal circuits −

2 Module 1 Notes prepared by srikanth

Downloaded from Ktunotes.in

EE309 Microprocessors and Embedded Systems

Control Signals: READY, RD’, WR’, ALE

Status Signals: S0, S1, IO/M’

DMA Signals: HOLD, HLDA

RESET Signals: RESET IN, RESET OUT

Interrupt control

As the name suggests it controls the interrupts during a process. When a microprocessor is executing a

main program and whenever an interrupt occurs, the microprocessor shifts the control from the main

program to process the incoming request. After the request is completed, the control goes back to the

main program.

There are 5 interrupt signals in 8085 microprocessor: INTR, RST 7.5, RST 6.5, RST 5.5, and TRAP.

Serial Input/output control

It controls the serial data communication by using these two instructions: SID (Serial input data) and

SOD (Serial output data).

S . I N

OTE

Address buffer and address-data buffer

T U N

The content stored in the stack pointer and program counter is loaded into the address buffer and

K

address-data buffer to communicate with the CPU. The memory and I/O chips are connected to these

buses; the CPU can exchange the desired data with the memory and I/O chips.

Address bus and data bus

Data bus carries the data to be stored. It is bidirectional, whereas address bus carries the location to

where it should be stored and it is unidirectional.

3 Module 1 Notes prepared by srikanth

Downloaded from Ktunotes.in

EE309 Microprocessors and Embedded Systems

S . I N

T U N OTE

K

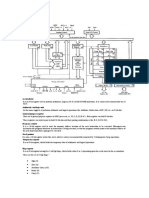

8085 PINS and their Functions - 40 pin DIP chip

4 Module 1 Notes prepared by srikanth

Downloaded from Ktunotes.in

EE309 Microprocessors and Embedded Systems

The device has 40 pins

S . I N

Requires a +5V single power supply, and can operate with a 3 MHz single phase clock.

T U N OTE

The above figure shows the logic pinout of the 8085 microprocessor. All the signals can be

K

classified into 6 groups. (1)Address bus (2) Data bus (3) Control and status signals (4) power supply

and frequency signals (5) Externally initiated signals and (6) Serial I/O ports

Address & Data Bus

8085 has 16 signal lines that are used as the address bus. These lines are split into 2 segments

A15-A8 and AD7-AD0 (multiplexed address/data bus). A15-A8 – unidirectional and used for the most

significant bits called the high order address of 16 bit address. AD7-AD0 – bidirectional and they are

used as the low order address bus as well as the data bus.

Control & Status Signals

These signals are used to identify the nature of operation. There are 3 control signals and 3 status

signals.

Control Signals

1. ALE (output) - Address Latch Enable. Indicate a valid address on the bus. It is a positive going

pulse used to latch the address on the bus.

´

RD

2. (Active low) - Read memory or IO device. This indicates that the selected memory

location or I/O device is to be read and that the data bus is ready for accepting data from the

memory or I/O device

´

3. WR (Active low) - Write memory or IO device. This indicates that the data on the data bus is

to be written into the selected memory location or I/O device.

5 Module 1 Notes prepared by srikanth

Downloaded from Ktunotes.in

EE309 Microprocessors and Embedded Systems

Status Signals

1. IO/ Ḿ - Select memory or an IO device. This signal indicates that the read / write

operation relates to whether the memory or I/O device. It goes high to indicate an I/O

operation and goes low for memory operations.

2. S1, S0 -It is used to know the type of current operation of the microprocessor.

IO/ S1 S0 OPERATION

Ḿ

0 1 1 Opcode fetch

0 1 0 Memory read

0 0 1 Memory write

1 1 0 I/O read

1 0 1 I/O write

1 1 1 Interrupt acknowledge

Z 0 1 Halt

Z x x Hold

Z x x Reset

Power Supply & Frequency Signals

Vcc: + 5 volt power supply and Vss:Ground

. I N

X1, X2: Crystal or R/C network or LC network connections to set the frequency of internal

S

U OTE

clock generator. The frequency is internally divided by two. Since the basic operating timing

N

frequency is 3 MHz, a 6 MHz crystal is connected externally.

T

K

CLK (output)-Clock Output is used as the system clock for peripherals and devices interfaced

with the microprocessor.

Externally Initiated Signals, Including Interrupts

Direct Memory Access (DMA) signals: Direct Memory Access operation is

used for large volume data transfer between memory and an I/O device

directly.

1. HOLD signal is generated by the DMA controller circuit which request the control of system

bus.

2. HLDA (Hold Acknowledge): On receipt of the HOLD signal, the microprocessor

acknowledges the request by sending out HLDA signal and leaves out the control of the buses.

After getting the HLDA signal the DMA controller starts the direct transfer of data.

READY (input): Memory and I/O devices will have slower response compared to

microprocessors. Ready input indicates that whether the memory or IO device is ready for a data

transfer. 1 indicates memory or IO device is ready for a data transfer and 0 indicate that they are

not ready. The microprocessor enters into WAIT state while the READY pin is 0.

6 Module 1 Notes prepared by srikanth

Downloaded from Ktunotes.in

EE309 Microprocessors and Embedded Systems

Rest∈¿

´¿ : This signal is used to reset the microprocessor. The program counter (PC) inside the

microprocessor is set to zero.

Reset Out : It indicates CPU is being reset. It is used to reset all the connected devices when

the microprocessor is reset.

Serial Input Output Control signals- There are two pins in this unit. Used for serial data

communication.

1. SID (input) - Serial input data line

2. SOD (output) - Serial output data line

Interrupt control Signals

Interrupts are the signals generated by external devices to request the microprocessor to perform a task.

There are 5 interrupt signals (hardware interrupts), i.e. TRAP, RST 7.5, RST 6.5, RST 5.5, and INTR.

1. TRAP (Non Maskable, vectored interrupt)

2. RST 7.5 (Maskable, vectored interrupt)

3. RST 6.5 (Maskable, vectored interrupt)

4. RST 5.5 (Maskable, vectored interrupt)

5. INTR (Maskable, Non vectored interrupt)

INTA − It is an interrupt acknowledgment signal.

S . I N

Instruction Set 8085

T U N OTE

K

Data Transfer Instructions

Opcode Operand Explanation of Description

Instruction

MOV Rd, Rs Copy data from 2 operands

MOV M, Rs the source (2nd Can be register or memory. The contents of the source are

MOV Rd, M operand) to not altered. If one of the operands is M (memory

destination (1st location), then the location is specified by the HL register

operand). pair.

Eg: MOV B, C ; B←C

MOV B, M; B←(HL)

(HL) = data in the memory location pointed by HL pair

MVI Rd, data Move The source is always an 8-bit data. Destination can be a

MVI M, data immediate 8-bit register or memory. If the operand is a memory location,

data to the its location is specified by the contents of the HL registers.

destination Example: MVI B, 57H ; B←57

specified MVI M, 57H ; (HL)←57

(HL) = memory location pointed by HL register pair

LDA 16-bit address Load Load – from memory to register

accumulator The contents of a memory location, specified by a 16-bit

with data given direct address in the operand, are copied to the

7 Module 1 Notes prepared by srikanth

Downloaded from Ktunotes.in

EE309 Microprocessors and Embedded Systems

inside the 16 bit accumulator. The contents of the source are not altered.

address location Example: LDA 2034H ; A← (2034)

LDAX Reg. pair Load The contents of the memory location pointed by

LDAX B accumulator designated register pair is copied into the accumulator.

LDAX D with data from The contents of either the register pair or the memory

the memory location are not altered.

location pointed Eg: LDAX B ; A←(BC)

by register pair.

LXI Reg. pair, 16-bit data Load register The instruction loads 16-bit data in the register pair

pair with designated in the operand.

immediate data Example: LXI H, 2034H ; H=20h L=34h

LHLD 16-bit address Load H and L The instruction copies the contents of the memory

registers with location pointed out by the 16-bit address into register L

content of the and copies the contents of the next memory location into

memory register H.

location Example: LHLD 2040H

L= content of the memory location 2040h

H= content of the memory location 2041h

STA 16-bit address Store the

S . I N

The contents of the accumulator are copied into the

T U N memory OTE

content of A in memory location specified by the operand. This is a 3-

byte instruction, the second byte specifies the low-order

K location given

by 16-bit

address

address and the third byte specifies the high-order address.

Eg: STA 4350H

STAX Reg. pair Store The contents of the accumulator are copied into the

accumulator in memory location specified by the contents of the operand

the memory (register pair). The contents of the accumulator are not

location pointed altered.

by reg pair Example: STAX B

(indirect)

SHLD 16-bit address Store H and L The contents of register L are stored into the memory

registers to the location specified by the 16-bit address in the operand and

memory the contents of H register are stored into the next memory

location whose location by incrementing the operand. The contents of

address is registers HL are not altered. Example: SHLD 2470H

specified

directly

XCHG - Exchange the The contents of register H are exchanged with the contents

(no operand) content of H of register D, and the contents of register L are exchanged

and L with D with the contents of register E.

and E Example: XCHG

8 Module 1 Notes prepared by srikanth

Downloaded from Ktunotes.in

EE309 Microprocessors and Embedded Systems

SPHL - Copy H and L The instruction loads the contents of the H and L registers

(no operand) registers to the into the stack pointer register, the contents of the H

stack pointer register provide the high-order address and the contents of

the L register provide the low-order address. The contents

of the Hand L registers are not altered. Example: SPHL

XTHL - Exchange H and The contents of the L register are exchanged with the

(no operand) L with top of stack location pointed out by the contents of the stack

stack pointer register. The contents of the H register are

exchanged with the next stack location (SP+1); however,

the contents of the stack pointer register are not altered.

Example: XTHL

PUSH Reg. pair Push register The contents of the register pair designated in the operand

pair onto stack are copied onto the stack in the following sequence. The

stack pointer register is decremented and the contents of

the higher order register (B, D, H, A) are copied into that

location. The stack pointer register is decremented again

and the contents of the low-order register (C, E, L, flag

reg) are copied to that location.

Example: PUSH B or PUSH A

POP Reg. pair Pop off stack to

S . N

The contents of the memory location pointed by the stack

I

OTE

register pair pointer register are copied to the low-order register (C, E,

L, flag reg) of the operand. The stack pointer is

K T U N incremented by 1 and the contents of that memory

location are copied to the high-order register (B, D, H, A)

of the operand. The stack pointer register is again

incremented by 1.Example: POP H or POP A

OUT 8-bit port address Output data The contents of the accumulator are write to the output

from port designated in the operand (8 bit address port)

accumulator to Example: OUT 80H

a port with 8-bit

address

IN 8-bit port address Input data to The contents of the input port designated in the operand

accumulator are read and loaded into the accumulator.

from a port with Example: IN 8CH

8-bit address

Arithmetic Instructions

Opcod Operand Explanation of Description

e Instruction

ADD R Add register or The contents of the operand (register or memory) are added

ADD M memory, to to the contents of the accumulator and the result is stored in

accumulator the accumulator. If the operand is a memory location, its

9 Module 1 Notes prepared by srikanth

Downloaded from Ktunotes.in

EE309 Microprocessors and Embedded Systems

location is specified by the contents of the HL registers. All

flags are modified to reflect the result of the addition.

Example: ADD B ; A←A+B

ADD M ; A← A+ (HL)

(HL) = data in the memory location pointed by HL pair

ADC R Add register to The contents of the operand (register or memory) and the

ADC M accumulator with Carry flag are added to the contents of the accumulator and

carry the result is stored in the accumulator. If the operand is a

memory location, its location is specified by the contents of

the HL registers. All flags are modified to reflect the result

of the addition. Eg: ADC B or ADC M

ADI 8-bit data Add immediate to The 8-bit data (operand) is added to the contents of the

accumulator accumulator and the result is stored in the accumulator. All

flags are modified to reflect the result of the addition.

Example: ADI 45H

ACI 8-bit data Add immediate to The 8-bit data (operand) and the Carry flag are added to the

accumulator with contents of the accumulator and the result is stored in the

carry accumulator. All flags are modified to reflect the result of

S . I N

the addition. Eg: ACI 45H

DAD Reg. pair

N

Add register pair

T U OTE

The 16-bit contents of the specified register pair are added

K

to H and L

registers

to the contents of the HL register and the sum is stored in

the HL register. The contents of the source register pair are

not altered. If the result is larger than 16 bits, the CY flag is

set. No other flags are affected. Eg: DAD H

SUB R Subtract register The contents of the operand (register or memory) are

M or memory from subtracted from the contents of the accumulator, and the

accumulator result is stored in the accumulator. If the operand is a

memory location, its location is specified by the contents of

the HL registers. All flags are modified to reflect the result

of the subtraction. Eg: SUB B or SUB M

SBB R Subtract source The contents of the operand (register or memory) and the

M and borrow from Borrow flag are subtracted from the contents of the

accumulator accumulator and the result is placed in the accumulator. If

the operand is a memory location, its location is specified

by the contents of the HL registers. Flags are modified to

reflect the result of the subtraction. Eg: SBB B or SBB M

SUI 8-bit data Subtract The 8-bit data (operand) is subtracted from the contents of

immediate from the accumulator and the result is stored in the accumulator.

accumulator All flags are modified to reflect the result of the subtraction.

Example: SUI 45H

10 Module 1 Notes prepared by srikanth

Downloaded from Ktunotes.in

EE309 Microprocessors and Embedded Systems

SBI 8-bit data Subtract The 8-bit data (operand) and the borrow flag are subtracted

immediate from from the contents of the accumulator and the result is stored

accumulator with in the accumulator. All flags are modified to reflect the

borrow result of the addition. Eg: SBI 45H

INR R Increment The contents of the designated register or memory are

M register or incremented by 1 and the result is stored in the same place.

memory by 1 If the operand is a memory location, its location is specified

by the contents of the HL registers.

Example: INR B or INR M

INX R Increment The contents of the designated register pair are incremented

register pair by 1 by 1 and the result is stored in the same place.

Example: INX H

DCR R Decrement The contents of the designated register or memory are M

M register or decremented by 1 and the result is stored in the same place.

memory by 1 If the operand is a memory location, its location is specified

by the contents of the HL registers.

Example: DCR B or DCR M

DCX R Decrement

. I N

The contents of the designated register pair are decremented

S

OTE

register pair by 1 by 1 and the result is stored in the same place.

DAA none K T U N

Decimal adjust

Example: DCX H

If the value of the low-order 4-bits in the accumulator is

accumulator. greater than 9 or if AC flag is set, the instruction adds 6 to

Used after an the low-order four bits.

addition If the value of the high-order 4-bits in the accumulator is

operation to greater than 9 or if the Carry flag is set, the instruction adds

convert the result 6 to the high-order four bits.

to BCD

Logical instructions

Opcod Operand Explanation of Description

e Instruction

CMP R Compare register The contents of the operand (register or memory) are

M or memory with subtracted from the contents of the accumulator. But both

accumulator contents are preserved. The result of the comparison is

shown by setting the flags of the PSW as follows:

if (A) < (reg/mem): carry flag is set

if (A) = (reg/mem): zero flag is set

if (A) > (reg/mem): carry and zero flags are reset

Example: CMP B or CMP M

11 Module 1 Notes prepared by srikanth

Downloaded from Ktunotes.in

EE309 Microprocessors and Embedded Systems

CPI 8-bit data Compare The second byte (8-bit data) is compared with the contents

immediate with of the accumulator. The values being compared remain

accumulator unchanged. The result of the comparison is shown by setting

the flags of the PSW as follows:

if (A) < data: carry flag is set

if (A) = data: zero flag is set

if (A) > data: carry and zero flags are reset

Example: CPI 89H

ANA R Logical AND The contents of the accumulator are logically ANDed with

M register or M the contents of the operand (register or memory), and the

memory with result is placed in the accumulator. If the operand is a

accumulator memory location, its address is specified by the contents of

HL registers. S, Z, P are modified to reflect the result of the

operation. CY is reset. AC is set.

Example: ANA B or ANA M

ANI 8-bit Logical AND The contents of the accumulator are logically ANDed with

data immediate with the

accumulator 8-bit data (operand) and the result is placed in the

S . I N

accumulator. S, Z, P are modified to reflect the result of the

OTE

operation. CY is reset. AC is set.

Example: ANI 86H

XRA R

K T U N

Exclusive OR The contents of the accumulator are Exclusive ORed with M

M register or the contents of the operand (register or memory), and the

memory with result is placed in the accumulator. If the operand is a

accumulator memory location, its address is specified by the contents of

HL registers. S, Z, P are modified to reflect the result of the

operation. CY and AC are reset.

Example: XRA B or XRA M

XRI 8-bit Exclusive OR The contents of the accumulator are Exclusive ORed with

data immediate with the 8-bit data (operand) and the result is placed in the

accumulator accumulator. S, Z, P are modified to reflect the result of the

operation. CY and AC are reset.

Example: XRI 86H

ORA R Logical OR The contents of the accumulator are logically ORed with M

M register or the contents of the operand (register or memory), and the

memory with result is placed in the accumulator. If the operand is a

accumulator memory location, its address is specified by the contents of

HL registers. S, Z, P are modified to reflect the result of the

operation. CY and AC are reset.

Example: ORA B or ORA M

12 Module 1 Notes prepared by srikanth

Downloaded from Ktunotes.in

EE309 Microprocessors and Embedded Systems

ORI 8-bit Logical OR The contents of the accumulator are logically ORed with the

data immediate with 8-bit data (operand) and the result is placed in the

accumulator accumulator. S, Z, P are modified to reflect the result of the

operation. CY and AC are reset. Example: ORI 86H

RLC - Rotate Each binary bit of the accumulator is rotated left by one

(no accumulator left position. Bit D7 is placed in the position of D0 as well as in

operand) the Carry flag. CY is modified according to bit D7 but CY is

not rotated. S, Z, P, AC are not affected.

RRC - Rotate Each binary bit of the accumulator is rotated right by one

(no accumulator right position. Bit D0 is placed in the position of D7 as well as in

operand) the Carry flag. CY is modified according to bit D0 but CY is

not rotated. S, Z, P, AC are not affected.

RAL - Rotate Each binary bit of the accumulator is rotated left by one

(no accumulator left position through the Carry flag. Bit D7 is placed in the

operand) through carry Carry flag, and the Carry flag is placed in the least

significant position D0. CY is modified according to bit D7.

S, Z, P, AC are not affected.

RAR - Rotate

. I N

Each binary bit of the accumulator is rotated right by one

S

OTE

(no accumulator right position through the Carry flag. Bit D0 is placed in the

operand)

K T U N

through carry Carry flag, and the Carry flag is placed in the most

significant position D7. CY is modified according to bit D0.

S, Z, P, AC are not affected.

CMA - Complement The contents of the accumulator are complemented. No

(no accumulator flags are affected.

operand)

CMC - Complement carry The Carry flag is complemented. No other flags are affected.

(no

operand)

STC - Set Carry Set Carry

(no

operand)

Branching instructions

Opcode Operand Explanation of Description

Instruction

JMP 16-bit Jump The program sequence is transferred to the memory

address unconditionally location specified by the 16-bit address given in the

operand.Example: JMP 2034H

13 Module 1 Notes prepared by srikanth

Downloaded from Ktunotes.in

EE309 Microprocessors and Embedded Systems

Conditional jumps

JC Jump on Carry (CF=1) The program sequence is transferred to the memory

JNC Jump on no Carry location specified by the 16-bit address given in the

JP (CF=0)

operand based on the specified flag of the PSW as

JM Jump on positive (SF=0)

16-bit described below.

JZ Jump on minus (SF=1)

address Jump on zero (ZF=1) Example: JZ 2034H

JNZ

JPE Jump on no zero (ZF=0)

Jump on parity even

(PF=1)

JPO

Jump on parity odd

(PF=0)

CALL 16-bit Unconditional The program sequence is transferred to the memory

address subroutine call location specified by the 16-bit address given in the

operand. Before the transfer, the address of the next

instruction after CALL (the contents of the program

counter) is pushed onto the stack. Example: CALL 2034H

RET none Return from The program sequence is transferred from the subroutine to

subroutine

S I N

the calling program. The two bytes from the top of the stack

.

OTE

unconditionally are copied into the program counter, and program execution

K T

Conditional subroutine call U N begins at the new address. Example: RET

CC Call on Carry The program sequence is transferred to the memory

CNC Call on no Carry location specified by the 16-bit address given in the

CP Call on positive operand based on the specified flag of the PSW (flag

CM Call on minus register)

CZ Call on zero

CNZ 16-bit Call on no zero

CPE address Call on parity even

CPO Call on parity odd

Return from subroutine conditionally

RC Return on Carry The program sequence is transferred from the subroutine to

RNC Return on no Carry the calling program based on the specified flag of the PSW

RP Return on positive as described below. The two bytes from the top of the stack

RM Return on minus are copied into the program counter, and program execution

RZ none Return on zero begins at the new address.

RNZ Return on no zero Example: RZ

RPE Return on parityeven

RPO Return on parity odd

14 Module 1 Notes prepared by srikanth

Downloaded from Ktunotes.in

EE309 Microprocessors and Embedded Systems

PCHL none Load program The contents of registers H and L are copied into the

counter with HL program counter. The contents of H are placed as the high-

contents order byte and the contents of L as the low-order byte.

Example: PCHL

Restart Instructions (RST0 to RST7) – no operands

The RST instruction is equivalent to a 1-byte call instruction to one of eight memory locations depending upon

the number. The instructions are generally used in conjunction with interrupts and inserted using external

hardware. However these can be used as software instructions in a program to transfer program execution to

one of the eight locations.

Instructions Restart address

RST 0 0000H

RST1 0008H

RST 2 0010H

RST 3 0018H

RST 4 0020H

RST 5 0028H

RST 6 0030H

RST 7 0038H

Machine Control Instructions

S . I N

Opcode Operan

d

Explanation of

T U N

Instruction OTE Description

NOP none

K No operation No operation is performed. The instruction is fetched and

decoded. However no operation is executed. Example: NOP

HLT none Halt and enter wait The CPU finishes executing the current instruction and halts

state any further execution. An interrupt or reset is necessary to

exit from the halt state. Example: HLT

DI none Disable interrupts The interrupt enable flip-flop is reset and all the interrupts

except the TRAP are disabled. No flags are affected. Eg: DI

EI none Enable interrupts The interrupt enable flip-flop is set and all interrupts are

enabled. No flags are affected. After a system reset or the

acknowledgement of an interrupt, the interrupt enable flip

flop is reset, thus disabling the interrupts. This instruction is

necessary to re enable the interrupts (except

TRAP).Example: EI

RIM none Read interrupt mask This is a multipurpose instruction used to read the status of

interrupts 7.5, 6.5, 5.5 and to input serial data through the

SID line. Example: RIM

15 Module 1 Notes prepared by srikanth

Downloaded from Ktunotes.in

EE309 Microprocessors and Embedded Systems

SIM none Set interrupt mask This is a multipurpose instruction and used to implement the

8085 interrupts 7.5, 6.5, 5.5, and to output data serially from

the SOD line. Example: SIM

S . I N

T U N OTE

K

16 Module 1 Notes prepared by srikanth

Downloaded from Ktunotes.in

Vous aimerez peut-être aussi

- Microprocessor NotesDocument60 pagesMicroprocessor NotesVijay KumarPas encore d'évaluation

- Micrprocessor Notes 2023Document18 pagesMicrprocessor Notes 2023GautamPas encore d'évaluation

- Introduction To Microprocessor 8085Document23 pagesIntroduction To Microprocessor 8085GousAttarPas encore d'évaluation

- UNIT-4: 8085 MicroprocessorDocument28 pagesUNIT-4: 8085 MicroprocessorMuthuvel MPas encore d'évaluation

- M4 Yash AllabadiDocument6 pagesM4 Yash Allabadidegijon661Pas encore d'évaluation

- 8085 Microprocessor: Pin Configuration, ArchitectureDocument26 pages8085 Microprocessor: Pin Configuration, ArchitectureAnitha Kumari SivathanuPas encore d'évaluation

- Intel 8085 ArchitectureDocument8 pagesIntel 8085 ArchitectureAravind VJPas encore d'évaluation

- Prepared by NITHIN JOHN: Module-1Document15 pagesPrepared by NITHIN JOHN: Module-1Nithin JohnPas encore d'évaluation

- 8085 Microprocessor Architecture and Programming-1Document92 pages8085 Microprocessor Architecture and Programming-1ShubhamPas encore d'évaluation

- MPA UNIT 1 and 2Document48 pagesMPA UNIT 1 and 2Shiva Krishna KamjulaPas encore d'évaluation

- Unit 2Document15 pagesUnit 2Rajasekaran RPas encore d'évaluation

- Pin Configuration, ArchitectureDocument26 pagesPin Configuration, ArchitectureAnitha Kumari SivathanuPas encore d'évaluation

- 8085 Microprocessor - Functional Units: AccumulatorDocument5 pages8085 Microprocessor - Functional Units: AccumulatorDeep KamblePas encore d'évaluation

- 8085 Microprocessor - Block DiagramDocument5 pages8085 Microprocessor - Block DiagramShreyash ShindePas encore d'évaluation

- 8085 Microprocessor - Functional Units: AccumulatorDocument3 pages8085 Microprocessor - Functional Units: AccumulatorANKIT SHARMAPas encore d'évaluation

- Unit - VI DEDocument60 pagesUnit - VI DErahulbixt23Pas encore d'évaluation

- 8085 Architecture & Pin DescriptionFileDocument19 pages8085 Architecture & Pin DescriptionFileKaseya TakahashiPas encore d'évaluation

- Architecture 8085Document46 pagesArchitecture 8085milf hunterPas encore d'évaluation

- Hardware Architecture of 8085 MicroprocessorDocument16 pagesHardware Architecture of 8085 MicroprocessorCsPas encore d'évaluation

- Architechture of 8085Document4 pagesArchitechture of 8085udit_mca_blyPas encore d'évaluation

- Microprocessor - 8085 ArchitectureDocument4 pagesMicroprocessor - 8085 ArchitectureLithika RameshPas encore d'évaluation

- Ee 309 M1Document7 pagesEe 309 M1Basheer V.PPas encore d'évaluation

- COA LAb File-ShubhiDocument28 pagesCOA LAb File-ShubhiKrishan Kant ShuklaPas encore d'évaluation

- 8085 MaterialDocument12 pages8085 MaterialsameerPas encore d'évaluation

- Unit I PDFDocument25 pagesUnit I PDFSomnath2014Pas encore d'évaluation

- An Introduction To Microprocessor Architecture Using 8085 As A Classic ProcessorDocument24 pagesAn Introduction To Microprocessor Architecture Using 8085 As A Classic ProcessorArnold JohnPas encore d'évaluation

- MY BOOK For MicroprocessorDocument53 pagesMY BOOK For Microprocessorbharat patelPas encore d'évaluation

- Unit 1 Lect 3Document16 pagesUnit 1 Lect 3tankdhruvik800000Pas encore d'évaluation

- 8085 ArchitectureDocument31 pages8085 Architecturevellore gatewayPas encore d'évaluation

- 8085 MicroprocessorDocument25 pages8085 Microprocessorprofessor2062Pas encore d'évaluation

- Intel 8085 Architecture: AccumulatorDocument6 pagesIntel 8085 Architecture: AccumulatorDipesh YadavPas encore d'évaluation

- Cs2 Practical PDFDocument62 pagesCs2 Practical PDFMaitri ShahPas encore d'évaluation

- Poriyaan 1cmfA62QmpEUSssZeK 4a3Lq-KUrzO1jADocument171 pagesPoriyaan 1cmfA62QmpEUSssZeK 4a3Lq-KUrzO1jAS. GobikaPas encore d'évaluation

- Intro To 8085Document23 pagesIntro To 8085Vivek KumarPas encore d'évaluation

- 8085 MicroprocessorDocument38 pages8085 MicroprocessorPrateek PandeyPas encore d'évaluation

- 8085 Features, Signal DescriptionDocument13 pages8085 Features, Signal DescriptionRakesh Kumar DPas encore d'évaluation

- Notes Unit 1Document25 pagesNotes Unit 1Ashish YadavPas encore d'évaluation

- Notes For StudentsDocument29 pagesNotes For StudentsAnif Ilham IsmailPas encore d'évaluation

- 1 8085 Microprocessor ArchitectureDocument7 pages1 8085 Microprocessor Architecturejosrichman75Pas encore d'évaluation

- 8085 ArchitectureDocument30 pages8085 ArchitecturegokulchandruPas encore d'évaluation

- An Over View of 8085Document12 pagesAn Over View of 8085nskprasad89Pas encore d'évaluation

- MPDocument34 pagesMPAbhinandan JainPas encore d'évaluation

- Microprocessor - 8085 Architecture - TutorialspointDocument3 pagesMicroprocessor - 8085 Architecture - TutorialspointRajat RajPas encore d'évaluation

- MicroprocessorsDocument11 pagesMicroprocessors158 AshleshaPas encore d'évaluation

- 8085 MicroprocessorDocument13 pages8085 MicroprocessorSajid Akram100% (1)

- An Introduction To Microprocessor Architecture Using 8085 As A Classic ProcessorDocument15 pagesAn Introduction To Microprocessor Architecture Using 8085 As A Classic ProcessorMishtuDeepPas encore d'évaluation

- Microprocessor - 8085 ArchitectureDocument3 pagesMicroprocessor - 8085 ArchitectureN.D.SurendharPas encore d'évaluation

- UNIT 3 MechatronicsDocument38 pagesUNIT 3 MechatronicsMuthuvel M67% (6)

- An Introduction To Microprocessor Architecture Using 8085 As A Classic ProcessorDocument23 pagesAn Introduction To Microprocessor Architecture Using 8085 As A Classic ProcessorRohit GangwaniPas encore d'évaluation

- The 8085 Microprocessor ArchitectureDocument12 pagesThe 8085 Microprocessor ArchitectureBernard MunyithyaPas encore d'évaluation

- Microprocessor - 8085 ArchitectureDocument3 pagesMicroprocessor - 8085 ArchitectureAlok AnkitPas encore d'évaluation

- T 8085 MPU & E 8085 L 7: HE Xample OF AN Based Computer EctureDocument16 pagesT 8085 MPU & E 8085 L 7: HE Xample OF AN Based Computer EctureGagandeep SinghPas encore d'évaluation

- MPMC Eee Unit - I 8085 ProcessorDocument35 pagesMPMC Eee Unit - I 8085 ProcessorAnonymous zaMNkL100% (1)

- Unit-1 (1) Draw and Explain The Internal Architecture of 8085Document11 pagesUnit-1 (1) Draw and Explain The Internal Architecture of 8085Mann MehtaPas encore d'évaluation

- Eec Practical 8085 MicroprocessorDocument8 pagesEec Practical 8085 MicroprocessorinxludezPas encore d'évaluation

- UntitledDocument37 pagesUntitledDineesh babu LPas encore d'évaluation

- Ii Microprocessor - 8085 ArchitectureDocument6 pagesIi Microprocessor - 8085 ArchitectureYohannis DanielPas encore d'évaluation

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960D'EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Pas encore d'évaluation

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationD'EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationPas encore d'évaluation

- Umera Anjum - M.TechDocument61 pagesUmera Anjum - M.TechDivya KrishnanPas encore d'évaluation

- HDTV T: EchnologyDocument26 pagesHDTV T: EchnologyDivya KrishnanPas encore d'évaluation

- FM Transmitters CrosbyDocument4 pagesFM Transmitters CrosbyDivya KrishnanPas encore d'évaluation

- Satellite Communication: by Ravikiran S. Anande Assistant ProfessorDocument35 pagesSatellite Communication: by Ravikiran S. Anande Assistant ProfessorDivya Krishnan100% (1)

- Introduction To TelevisionDocument27 pagesIntroduction To TelevisionDivya KrishnanPas encore d'évaluation

- Chapter: CABLE TV: Constructional Details, Working and Radiation Pattern of Dish AntennaDocument19 pagesChapter: CABLE TV: Constructional Details, Working and Radiation Pattern of Dish AntennaDivya KrishnanPas encore d'évaluation

- Colouttvfundamentals 160425132024Document105 pagesColouttvfundamentals 160425132024Divya KrishnanPas encore d'évaluation

- An Application of 8085 Register Interfacing With LedDocument13 pagesAn Application of 8085 Register Interfacing With LedDivya KrishnanPas encore d'évaluation

- Presented by HrudyaDocument10 pagesPresented by HrudyaDivya KrishnanPas encore d'évaluation

- CCTV System.: C.Sagevan. JF/BST/F/17/1/0019Document28 pagesCCTV System.: C.Sagevan. JF/BST/F/17/1/0019Divya KrishnanPas encore d'évaluation

- Electronic CommunicationDocument117 pagesElectronic CommunicationDivya KrishnanPas encore d'évaluation

- EE401 Electronic CommunicationDocument2 pagesEE401 Electronic CommunicationDivya KrishnanPas encore d'évaluation

- Delay RoutineDocument11 pagesDelay RoutineDivya KrishnanPas encore d'évaluation

- Timing DiagramDocument12 pagesTiming DiagramDivya KrishnanPas encore d'évaluation

- Programming of 8085 PPT 1Document17 pagesProgramming of 8085 PPT 1Divya KrishnanPas encore d'évaluation

- Scan Insertion Lab Observation (K.S.K.S.sarma)Document33 pagesScan Insertion Lab Observation (K.S.K.S.sarma)Kittu Krishna100% (2)

- Item: 1 (Ref:Cert-70-290.1.2.1)Document69 pagesItem: 1 (Ref:Cert-70-290.1.2.1)wololoPas encore d'évaluation

- U MG MG Myat PIC BasicDocument58 pagesU MG MG Myat PIC BasicJenny Sdd100% (1)

- Analog IO Basic Knowledge PDFDocument20 pagesAnalog IO Basic Knowledge PDFSanthosh V RaajendiranPas encore d'évaluation

- IP Control Center N 152Document4 pagesIP Control Center N 152cc_bauPas encore d'évaluation

- SSR - IsgDocument2 pagesSSR - IsgMark Alyson NginaPas encore d'évaluation

- Bsspar 150623050238 Lva1 App6892 PDFDocument221 pagesBsspar 150623050238 Lva1 App6892 PDFSridhar SonthaPas encore d'évaluation

- Shubham Pratap Singh CVDocument5 pagesShubham Pratap Singh CVShubham Pratap SinghPas encore d'évaluation

- Suprema Biostation GuideDocument15 pagesSuprema Biostation GuideNatalia Benitez GutierrezPas encore d'évaluation

- Controladora para Pixels: The Lededit Software InstructionsDocument13 pagesControladora para Pixels: The Lededit Software InstructionsGiovanni Mora MoraPas encore d'évaluation

- Information Technology VocabularyDocument2 pagesInformation Technology VocabularyCasa NaluPas encore d'évaluation

- IPSecDocument25 pagesIPSecDinesh ParasharPas encore d'évaluation

- Module 8 - NSN Product Solution For GSMDocument86 pagesModule 8 - NSN Product Solution For GSMkarthiveeraPas encore d'évaluation

- Access Switchboard TutorialDocument6 pagesAccess Switchboard TutorialPhiiphy EkwamPas encore d'évaluation

- SiemensDocument3 pagesSiemensHesham SharakyPas encore d'évaluation

- Fast, Precision Comparator AD790: 15 V Supply Operation V Max Input Offset Voltage V Max Input Hysteresis VoltageDocument11 pagesFast, Precision Comparator AD790: 15 V Supply Operation V Max Input Offset Voltage V Max Input Hysteresis VoltageytnatePas encore d'évaluation

- SJ-20141230091957-001-ZTE UniPOS NetMAX GSM (V14.40) User Manual - 615375Document185 pagesSJ-20141230091957-001-ZTE UniPOS NetMAX GSM (V14.40) User Manual - 615375Camilo Bazan Heredia100% (1)

- WLL TutorialDocument39 pagesWLL Tutorialrapsterx50% (2)

- Setting Up Internet Access Server On Basis of Mikrotik Routeros and Isp Billing System Netup Utm5Document9 pagesSetting Up Internet Access Server On Basis of Mikrotik Routeros and Isp Billing System Netup Utm5Vijay Kumar TitarmarePas encore d'évaluation

- Au Aixveritas PDFDocument22 pagesAu Aixveritas PDFsankalp1988Pas encore d'évaluation

- Tehnici Web Cors File, Filereader: Ioana Leustean Sem.I, 2016-2017Document7 pagesTehnici Web Cors File, Filereader: Ioana Leustean Sem.I, 2016-2017Vlad FrunzaPas encore d'évaluation

- Introduction To Information Technology Turban, Rainer and Potter John Wiley & Sons, IncDocument33 pagesIntroduction To Information Technology Turban, Rainer and Potter John Wiley & Sons, Incnhicole naguitPas encore d'évaluation

- Annualreport 074 75 PDFDocument100 pagesAnnualreport 074 75 PDFSuraj JoshiPas encore d'évaluation

- Isd4004 + Pic16f877aDocument38 pagesIsd4004 + Pic16f877aSteven Howard100% (1)

- NetlogDocument9 pagesNetlogAlberto JuárezPas encore d'évaluation

- Raspberry PiDocument16 pagesRaspberry PiHema Anilkumar100% (1)

- Cyberdog Fact SheetDocument2 pagesCyberdog Fact SheetscriPas encore d'évaluation

- CV AhmedDocument4 pagesCV Ahmedahmedsabeeh100% (2)

- SAM Broadcaster 4.9.2 Full PatchDocument2 pagesSAM Broadcaster 4.9.2 Full PatchPangeran Caspian0% (1)

- Awk Script Test 101 PDFDocument3 pagesAwk Script Test 101 PDFJitenPas encore d'évaluation