Académique Documents

Professionnel Documents

Culture Documents

Experimental Analysis of The Variants of PDF

Transféré par

Karlos VergaraTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Experimental Analysis of The Variants of PDF

Transféré par

Karlos VergaraDroits d'auteur :

Formats disponibles

International Journal of Engineering and Techniques - Volume 4 Issue 2 , Mar -Apr 2018

RESEARCH ARTICLE OPEN ACCESS

Experimental Analysis of the Variants of UBCT Amplifier

Circuit

Amitabh Kumar

P. G. Department of Electronics, A. N. College, Patna (India)

Abstract:

The Unipolar-Bipolar Composite Transistor (UBCT) circuit is designed to combine the advantages of high input resistance of

unipolar transistor and transfer curve linearity of bipolar transistor. The Composite Circuit has been designed with n-channel

JFET, npn BJT and a pair of resistors, therefore this type of JFET-BJT composite transistor is classified as UBCT. This

UBCT circuit exhibits enhanced static and dynamic performances as compared to that of JFET. In the present correspondence,

the performances of the variants of the UBCT amplifier circuit have been experimentally analysed on the basis of power

dissipation level and the corresponding voltage gain of the amplifier. According to the experimental results, the UBCT

amplifier circuit can be used as a power efficient small signal amplifier for analog applications.

Keywords— Composite Transistor, CT, Unipolar-Bipolar Composite Transistor, UBCT, JFET-BJT Composite Transistor,M-

FET, UBCT Amplifier.

along with three resistors. It offers high input

I. INTRODUCTION resistance and widespread linear transfer

The Unipolar-Bipolar Composite Transistor (UBCT) characteristics [4]. Later, this composite transistor

consists of circuit combination of Unipolar (JFET) is further thermally improved by comprising of an

and Bipolar (BJT) active components in association n-channel JFET, four npn BJTs, a pnp BJT and

with resistive passive components. The resultant three resistors [5]. Due to its improved FET like

circuit design can be considered for fabrication as a characteristics, it is designated as “Modified Field

single equivalent transistor, hence it is categorised Effect Transistor (M-FET)”. The M-FET has

as Composite Transistor (CT). The primary motive marked improvement in the transfer curve linearity

behind designing the circuit for UBCT is to utilize associated with good thermal stability [6]. Since it

the advantages of high input resistance of JFET exhibits superior performances to that of JFET,

along with linear transfer characteristics of BJT. hence this JFET-BJT composite transistor finds

Thus, these JFET and BJT devices are designed in better applications in designing amplifiers and

combination to achieve better performance that can oscillators [7].

be obtained with either active device alone [1]. The

JFET-BJT composite transistor circuit was

introduced by Mylroie in 1979 [2]. Later in 1985, II. CIRCUIT DESIGN OF UBCT

the BJTs were started to be fabricated along with The circuit of UBCT has been designed with n-

thin implanted JFETs on the same chip to create channel JFET (BFW10), npn BJT (CL100) and a

BIFET structure in Monolithic Integrated Circuit pair of source and emitter resistors (RS-RE). The

(MIC) technology [3]. drain of JFET and collector of BJT are connected

together to form final drain, base is connected to the

The JFET-BJT combination having FET like source, and emitter and source are connected in

characteristic has been reported in early literature, series with the emitter resistor and source resistor

which comprises an n-channel JFET and a pnp BJT respectively to form the final source for the UBCT.

ISSN: 2395-1303 http://www.ijetjournal.org Page 1053

International Journal of Engineering and Techniques - Volume 4 Issue 2 , Mar -Apr 2018

The gate of JFET works as well as the final gate for output of the amplifier is obtained at the drain end

UBCT. According to this UBCT circuit topology, it of the UBCT. The source self-biasing or self-

can also be fabricated by BIFET MIC technology biasing is basically a current series feedback circuit

and designated as a three terminal composite in which the source feedback resistor RS1 is used to

transistor device as depicted in fig.1. provide Q-point stabilization against change in

transistor parameters and variation in temperature.

Drain +VDD

RL Co

VD1=VD=VC

D C

VO

VD=VC

BFW10

Gate

G CI

S CL100 VG1=VG BFW10

B

E VI VS=VB CL100

RS RE

VE

RS RE

RG

Source

VS1

RS1 CS1

Fig.1 Circuit design of UBCT

(JFET-BJT Composite Transistor)

JFET BFW10, BJT CL100, (RS-RE) Resistor pair

This type of UBCT is specifically considered as a Fig.2 Circuit design of UBCT Amplifier

simplified circuit design of earlier reported JFET-

BJT composite transistors [8]. The circuit The feedback voltage is developed across source

components of UBCT (JFET-BJT composite resistor RS1 and the negative feedback can also be

transistor) have been optimized for parametric invalidated by using the source bypass capacitor

enhancement [9]. According to the static CS1, which keeps the source of the UBCT

performance, it also offers wide range linearity in effectively at ac ground [13]. The gate resistor RG

transfer curve and very high input resistance [10]. can be large, usually of 1MΩ, which serves to

The drain resistance and trans conductance curves maintain the average gate voltage at ac ground [14].

also exhibit linearity over the wide range of drain- Also the large value of RG prevents loading of the

to-source voltage and gate-to-source voltage ac signal source. The passive circuit components

respectively up to the pinch-off value of UBCT [11]. used in UBCT amplifier e.g. the resistors and

The dynamic performance of UBCT circuit capacitors along with the operating supply voltage

promotes its application as an efficient small signal have been optimized by a sequence of different sets

amplifier [12]. of experimental observations for procurement of

possible parametric boosts. The experimental

III. UBCT AMPLIFIER CIRCUIT

results confirm that passive components have been

This UBCT is used as an active component in a optimized at their standard values e.g. the load

common source amplifier circuit as depicted in resistor RL=1kΩ, gate resistor RG=1MΩ, source

fig.2. The circuit is biased under the source self- resistor RS1=100Ω, input & output coupling

biasing topology of JFET amplifier with an applied capacitors CI=CO=10µF, source bypass capacitor

ac source capacitively coupled to the gate input.The

ISSN: 2395-1303 http://www.ijetjournal.org Page 1054

International Journal of Engineering and Techniques - Volume 4 Issue 2 , Mar -Apr 2018

CS1=N/C for providing voltage gain with negative 10Ω) as well as (100Ω-100Ω) should be better

feedback and the supply voltage VDD=18V within choices as the voltage gain AVF of about 8dB has

the operating temperature range of 32°C to 35°C. been achieved even at lower supply voltage

VDD=15V. At VDD=21V & 24V, the variant having

IV. EXPERIMENTAL ANALYSIS resistor pair (RS-RE) (1kΩ-100Ω) also shows better

For experimental analysis of the variants of UBCT voltage gain. The UBCT variants having resistor

amplifier circuit, ac experiments have been pair (RS-RE) (10kΩ-1kΩ) and (1kΩ-1kΩ) do not

performed in which the effects of supply voltage show considerable voltage gains for the entire

and the corresponding power dissipation level on experimental range of supply voltage from 9V to

the voltage gain of the UBCT amplifier are 24V. The supply voltage VDD=21V and above, the

precisely studied. voltage gains for all the resistor pair (RS-RE) are

almost about to be saturated. In these observations,

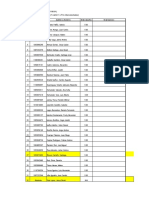

(A) Supply Voltage Analysis for UBCT the variant of UBCT amplifier circuit having

Amplifier Circuit resistor pair (RS-RE) (100Ω-10Ω) exhibits the best

The experimental observations have been taken for performance as the voltage gain AVF of 13.39dB is

five variants of UBCT amplifier circuit having achieved at the supply voltage VDD=18V.

different resistor pairs (RS-RE) (10kΩ-1kΩ), (1kΩ-

1kΩ), (1kΩ-100Ω), (100Ω-100Ω) and (100Ω-10Ω) (B) Power Dissipation Analysis for UBCT

with the supply voltage ranging from 9V to 24V Amplifier Circuit

DC and input ac voltage of 100mV (peak-to-peak) The objective of power dissipation analysis is to

having constant frequency of 1kHz (sine wave). design a power efficient UBCT amplifier circuit

These observations are plotted in the graph shown which offers the best possible voltage gain at the

in fig. 3. optimal power dissipation level. The experimental

observations for the analysis of power dissipation of

UBCT amplifier are plotted in the column graph as

A dB

VF,

shown in fig. 4. The graph depicts the Voltage gain

20.00

with negative feedback, Total power dissipation of

15.00 100Ω-10Ω

the circuit, power dissipation across Load resistor,

10.00

1kΩ-100Ω UBCT, JFET and BJT respectively for five variants

100Ω-100Ω

of UBCT circuits consisting of different pairs of

5.00 source and emitter resistors (RS-RE) having values

1kΩ-1kΩ

0.00 10kΩ-1kΩ

(10kΩ-1kΩ), (1kΩ-1kΩ), (1kΩ-100Ω), (100Ω-

6 9 12 15 18 21 24 27 100Ω) and (100Ω-10Ω) at constant supply voltage

-5.00

V V

DD,

VDD of 18V. The supply voltage of VDD = 18V is

-10.00

optimized because the voltage gains of four out of

five variants of UBCT have been almost saturated.

The power dissipation observations display that the

Fig.3 Voltage gain with negative feedback AVF

obtained voltage gains for different resistor pairs

versus the supply voltage VDD for the variants of

(RS-RE) (10kΩ-1kΩ), (1kΩ-1kΩ), (1kΩ-100Ω),

UBCT Amplifier circuits having five different

(100Ω-100Ω) and (100Ω-10Ω) are - 0.63dB,

resistor pairs (RS-RE).

1.87dB, 5.44dB, 9.54dB and 13.39dB respectively.

Specifications: UBCT (JFET BFW10, BJT CL100,

In view of this, use of the variants of UBCT having

resistor pair RS-RE), RL=1kΩ, RG=1MΩ, RS1=100Ω,

resistor pairs (RS-RE) (10kΩ-1kΩ) and (1kΩ-1kΩ)

CI=CO=10µF, CS1= N/C in case of negative

are avoided and not to be considered because of

feedback, T=32-35°C, input ac voltage VI=100 mV

their lower voltage gains. The variant of UBCT

(p-p) of 1 kHz.

having resistor pair (RS-RE) (1kΩ-100Ω) also gives

Based on the experimental observations, it appears

a lower voltage gain of 5.44dB with a large total

that the variants having resistor pair (RS-RE) (100Ω-

power dissipation level of 242.28mW.The

ISSN: 2395-1303 http://www.ijetjournal.org Page 1055

International Journal of Engineering and Techniques - Volume 4 Issue 2 , Mar -Apr 2018

satisfactory results have been obtained by the use of capacitors CI=CO=10µF, source bypass capacitor

the variants of UBCT having resistor pairs (RS-RE) CS1=N/C for providing voltage gain with negative

(100Ω-100Ω) and (100Ω-10Ω) with better voltage feedback and the range of operating temperature is

gains of 9.54dB and 13.39dB at comparable lower between 32°C to35°C. According to the

power dissipation levels of about 158.58mW and experimental observations, the UBCT amplifier

203.58mW respectively. Overall, the best result is circuit having resistor pair (RS-RE) (100Ω-10Ω) has

offered by the variant of UBCT having resistor pair performed the best among all other variants as it

(RS-RE) (100Ω-10Ω) as compared to that of (100Ω- could be able to deliver the voltage gain of 13.39dB

100Ω) is due to the optimal power dissipation levels at total power dissipation level of 203.58mW. At

of load resistor, UBCT, JFET and BJT. this condition, the power dissipation levels of the

UBCT, JFET and BJT are 62.77mW, 31.85 mW

and 26.50mW respectively, whereas the power

dissipation levels of the load resistor is 127.92mW.

Since, all these power dissipation levels are in safe

region as per the data sheets of the components

242.28

used in the circuit, hence the designed UBCT

181.17

203.58

amplifier circuit can be used as a power efficient

158.58 small signal amplifier for analogue applications.

127.92

83.16

77.62

73.21

63.00 59.69 56.02 62.77

49.53

34.04

21.34

27.22

21.39

42.80

23.53

31.85

26.50

ACKNOWLEDGMENT

12.25 9.54 11.51 13.39

3.95 1.87 5.44 2.48

-0.63

The author would like to thank The Head, P G

10kΩ-1kΩ 1kΩ-1kΩ 1kΩ-100Ω 100Ω-100Ω 100Ω-10Ω Department of Electronics, A. N. College, Patna

AVF, dB Power_Total, mW Power_RL, mW Power_UBCT, mW Power_JFET, mW Power_BJT, mW (India) for providing Research Laboratory to

perform the experimental work.

Fig.4 Power Dissipation of the variants of UBCT

REFERENCES

Amplifier circuits having five different resistor

pairs (RS-RE).

1. G J Deboo and C N Burrous, “Integrated Circuits

Specifications: UBCT (JFET BFW10, BJT CL100, and Semiconductor Devices: Theory and

resistor pair RS-RE), RL=1kΩ, RG=1MΩ, RS1=100Ω, Application”,McGaw-Hill Kogakusha Ltd., Tokyo,

CI=CO=10µF, CS1= N/C in case of negative International Student Edition, 2/e, Sec 1.5.4, p-33

feedback, T=32-35°C, input ac voltageVI=100 mV 1977.

(p-p) of 1 kHz at a constant supply voltage

2. S W Mylroie, “Composite JFET-Bipolar Structure”,

VDD=18V. US patent 4,143,392, Filed 1977, Pub. 1979.

V. CONCLUSION 3. W N Khadder, J T Wang and B E Hollins,

The present paper represents the experimental “Simplified BIFET Process”, US patent 4,512,815,

analysis regarding the performance of the variants Filed 1983, Pub. 1985.

of UBCT amplifier circuit. Observations for these 4. AA Khan, L Singh and Y A Das; “A New Composite

variants have been studied precisely by keeping Unit Device using J-FET and Bipolar

some parameters constant during the experiment e.g. Transistor”,the Journal of IETE; Vol. 28, No. 3, pp.

the supply voltage VDD is kept constant at 18V, the 117-119, 1982.

input ac voltage VI=100mV (p-p) of 1kHz, load

5. AA Khan and L Singh; “Dynamic Performance of

resistor RL=1kΩ, source resistor RS1=100Ω, gate Modified Field Effect Transistor”; Indian Journal of

resistor RG=1MΩ, input & output coupling

ISSN: 2395-1303 http://www.ijetjournal.org Page 1056

International Journal of Engineering and Techniques - Volume 4 Issue 2 , Mar -Apr 2018

Pure and Applied Physics”, Vol. 22, pp. 565-566, ISCA Patna Chapter and UGC sponsored Seminar at

Sept. 1984. TMBU, Bhagalpur, 30 Mar 2017, P 2, p-04.

6. AA Khan and L Singh; “A New Integrable 11. Amitabh Kumar, “Characteristics of Unipolar-

Composite Circuit with Improved FET-like Bipolar Composite Transistor Circuit”, Souvenir of

Characteristics”, IEEE Journal of Solid-State National Seminar by ISCA Patna Chapter at MU,

Circuits, Vol. SC-20, No. 2, pp. 648-649, 1985. Bodh-Gaya, 18-19 Nov 2017, pp. 92-93.

7. AA Khan and L Singh; “A JFET-BJT Combination 12. Amitabh Kumar, Arun Kumar, L Singh and N K

for Instrumentation Applications”, Int. J. Electronics, Goswami, “Dynamic Performance of the Variants of

Vol. 58, pp. 839-845, 1985. Unipolar-Bipolar Composite Transistor Circuits”,

Proc. of 105th Indian Science Congress (section of

8. Amitabh Kumar, Arun Kumar, L Singh and N K Physical Sciences), MU, Imphal, 16-20 Mar 2018,

Goswami, “Optimized Circuit Design for Gain Ph 105, pp. 124-125.

Improvement in Composite Transistor (M-FET)

Amplifier”, Proc. of 104th Indian Science Congress 13. T L Floyd, “Electronic Devices”, Merrill, Macmillan

(section of Physical Sciences), SVU, Tirupati, 03-07 Pub. Co., New York, 2/e, Sec 9.1, p-308, 1988.

Jan 2017, Ph 046, p-65.

14. JD Ryder,“ElectronicFundamentals andApplications:

9. Amitabh Kumar, “Circuit Optimization of Composite Integrated &Discrete Systems”, Prentice Hall of

Transistor M-FET Amplifier”, Souvenir of 6th& 7th India Pvt. Ltd., New Delhi, 5/e, Sec 6.6, p-143, 1990.

Bihar Vigyan Congress (section of Engineering

Sciences), BCST, IGSC Planetarium, Patna, 17-19

Feb 2017, ES 7, p-32.

10. Amitabh Kumar, “Static Performance of a Typical

Unipolar-Bipolar Composite Transistor (UBCT) ”,

ISSN: 2395-1303 http://www.ijetjournal.org Page 1057

Vous aimerez peut-être aussi

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Booklet - Frantic Assembly Beautiful BurnoutDocument10 pagesBooklet - Frantic Assembly Beautiful BurnoutMinnie'xoPas encore d'évaluation

- Toward A Design Theory of Problem SolvingDocument24 pagesToward A Design Theory of Problem SolvingThiago GonzagaPas encore d'évaluation

- Concrete Design Using PROKONDocument114 pagesConcrete Design Using PROKONHesham Mohamed100% (2)

- SPQRDocument8 pagesSPQRCamilo PeraltaPas encore d'évaluation

- Notas Taller Packet Tracer - TLCM-Redes LAN - 2sem2020Document6 pagesNotas Taller Packet Tracer - TLCM-Redes LAN - 2sem2020Karlos VergaraPas encore d'évaluation

- Prueba Analytics TEST (CSat)Document32 pagesPrueba Analytics TEST (CSat)Karlos VergaraPas encore d'évaluation

- Presents: YEAR 2040Document1 pagePresents: YEAR 2040Karlos VergaraPas encore d'évaluation

- Relation Between Taylor and Fourier SeriesDocument2 pagesRelation Between Taylor and Fourier SeriesKarlos VergaraPas encore d'évaluation

- Measuring Trend and TrendinessDocument3 pagesMeasuring Trend and TrendinessLUCKYPas encore d'évaluation

- Syllabus For B.A. (Philosophy) Semester-Wise Titles of The Papers in BA (Philosophy)Document26 pagesSyllabus For B.A. (Philosophy) Semester-Wise Titles of The Papers in BA (Philosophy)Ayan AhmadPas encore d'évaluation

- Configuration Steps - Settlement Management in S - 4 HANA - SAP BlogsDocument30 pagesConfiguration Steps - Settlement Management in S - 4 HANA - SAP Blogsenza100% (4)

- India: SupplyDocument6 pagesIndia: SupplyHarish NathanPas encore d'évaluation

- Conversational Maxims and Some Philosophical ProblemsDocument15 pagesConversational Maxims and Some Philosophical ProblemsPedro Alberto SanchezPas encore d'évaluation

- Grade 3Document4 pagesGrade 3Shai HusseinPas encore d'évaluation

- The John Molson School of Business MBA 607 Final Exam June 2013 (100 MARKS)Document10 pagesThe John Molson School of Business MBA 607 Final Exam June 2013 (100 MARKS)aicellPas encore d'évaluation

- Effect of Intensive Health Education On Adherence To Treatment in Sputum Positive Pulmonary Tuberculosis PatientsDocument6 pagesEffect of Intensive Health Education On Adherence To Treatment in Sputum Positive Pulmonary Tuberculosis PatientspocutindahPas encore d'évaluation

- DBA Daily StatusDocument9 pagesDBA Daily StatuspankajPas encore d'évaluation

- Eet 223 (1) Analog Electronics JagjeetDocument79 pagesEet 223 (1) Analog Electronics JagjeetMahima ArrawatiaPas encore d'évaluation

- What Is Thesis Plural FormDocument8 pagesWhat Is Thesis Plural Formtracyjimenezstamford100% (2)

- CopacabanaDocument2 pagesCopacabanaNereus Sanaani CAñeda Jr.Pas encore d'évaluation

- Thesis Statement VampiresDocument6 pagesThesis Statement Vampireslaurasmithdesmoines100% (2)

- Pediatric Autonomic DisorderDocument15 pagesPediatric Autonomic DisorderaimanPas encore d'évaluation

- Operational Effectiveness + StrategyDocument7 pagesOperational Effectiveness + StrategyPaulo GarcezPas encore d'évaluation

- The Idea of Multiple IntelligencesDocument2 pagesThe Idea of Multiple IntelligencesSiti AisyahPas encore d'évaluation

- Zimbabwe Mag Court Rules Commentary Si 11 of 2019Document6 pagesZimbabwe Mag Court Rules Commentary Si 11 of 2019Vusi BhebhePas encore d'évaluation

- Multiple Linear RegressionDocument26 pagesMultiple Linear RegressionMarlene G Padigos100% (2)

- The Cognitive Enterprise For HCM in Retail Powered by Ibm and Oracle - 46027146USENDocument29 pagesThe Cognitive Enterprise For HCM in Retail Powered by Ibm and Oracle - 46027146USENByte MePas encore d'évaluation

- Chapter 12 NotesDocument4 pagesChapter 12 NotesIvanTh3Great100% (6)

- Traps - 2008 12 30Document15 pagesTraps - 2008 12 30smoothkat5Pas encore d'évaluation

- Chapter 9 - PPT (New)Document43 pagesChapter 9 - PPT (New)Syarifah NourazlinPas encore d'évaluation

- Indus Valley Sites in IndiaDocument52 pagesIndus Valley Sites in IndiaDurai IlasunPas encore d'évaluation

- 4 Major Advantages of Japanese Education SystemDocument3 pages4 Major Advantages of Japanese Education SystemIsa HafizaPas encore d'évaluation

- 800 Pharsal Verb Thong DungDocument34 pages800 Pharsal Verb Thong DungNguyễn Thu Huyền100% (2)

- Mathematics Grade 5 Quarter 2: Answer KeyDocument4 pagesMathematics Grade 5 Quarter 2: Answer KeyApril Jean Cahoy100% (2)