Académique Documents

Professionnel Documents

Culture Documents

Pia6821 PDF

Transféré par

Mounaim MatiniTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Pia6821 PDF

Transféré par

Mounaim MatiniDroits d'auteur :

Formats disponibles

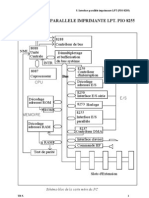

INTERFACE PARALLELE : PIA 6821

L’interface parallèle de type PIA 6821 (Peripherical Interface Adapter) fournit un moyen d’interface des

appareils périphériques avec un microprocesseur 680X. Ce circuit interface le MPU avec les

périphériques par deux bus de données 8 bits bidirectionnels et quatre lignes de contrôle.

La configuration fonctionnelle du PIA est programmée habituellement par le MPU pendant

l’initialisation du système. Chacune des lignes de données vers la périphérie (Port A et B) peut être

programmée pour être utilisée soit en entrée, soit en sortie à partir des registres internes et du bus de

données.

• bus de données (D0 à D7)

bidirectionnel vers le MPU

• 2 bus de données (ou port

A-B) bidirectionnels vers la

périphérie

• 2 registres de contrôle

programmables

• 4 lignes d’entrée

d’interruption contrôlables

individuellement

• possibilités de contrôler

des circuits CMOS à partir

des ports,

• possibilité de commander

2 charges TTL en sortie

• compatible TTL

Bus de données (D0 à D7) : 8 lignes bidirectionnelles directement reliées au bus du 6809. Elles

assurent l’échange des données entre le microprocesseur et le PIA. Si elles ne sont pas utilisées, ces

lignes sont à l’état haute impédance.

Bus d’adresses :

- CS0, CS1, /CS2 (Chip Select) : Sélectionnent le boîtier PIA (CS0xCS1x/CS2 = 1x1x0)

- RS0, RS1 (Register Select) : Sélectionnent les registres internes (4 octets mémoire).

Bus de contrôle :

- E : Signal d’activation des échanges

- /RESET : Initialisation du PIA. Les registres internes sont mis à zéro.

- R/W : Lecture - Ecriture

- IRQA, IRQB : Lignes d’interruptions

Lignes de transfert : PA0 à PA7, PB0 à PB7 : Ces 16 broches (2 x 8) permettent de transmettre ou

recevoir un mot de 8 bits. Suivant la programmation du DDRA/DDRB, elles seront utilisées en entrée

ou en sortie.

FONCTIONNEMENT :

De la périphérie vers le processeur :

La donnée disponible sur le port A en réception (port A configuré en entrée) est directement transmise

à l’amplificateur de bus de données par l’intermédiaire du bus de sortie. Elle ne transite pas par l’ORA,

il n’y a donc pas mémorisation des données en entrée.

PIA6821 Cours Page 1 sur 4

Fichier téléchargé sur : http://www.lelectronique.com - webmaster@lelectronique.com

Source : Stéphane – Tronic – http://www.tronic.fr.st – tronic@fr.st

Du processeur vers la périphérie :

La donnée disponible sur le bus du MPU est chargée dans le registre de sortie B par l’intermédiaire du

bus d’entrée, elle est donc mémorisée. Le port B est en sortie, la donnée est disponible tant qu’une

nouvelle écriture n’est pas intervenue.

Sélection des registres :

Pour sélectionner un registre, il

convient en premier lieu de

sélectionner le boîtier PIA

(CSX) puis d’agir sur l’état

logique des lignes RS1 et RS0.

Exemple d’adressage :

ADR = $E000 (adresse de base)

ADR+1 = $E001

ADR+2 = $E002

ADR+3 = $E003

Registre de contrôle CRA - CRB :

Ce registre permet la commande et le contrôle

des ports de sortie A et B. Pour y accéder, il

suffit de fixer les états logiques sur RS1 et RS0.

Ce registre va permettre d’accéder aux autres

registres : DDRA-DDRB et ORA-ORB à partir du

bit 2 du registre de contrôle :

Registres de sortie ORA – ORB :

Ce sont les registres dans lesquels vont transiter les données. Pour lire une donnée reçue par un port,

il suffira de lire le contenu de ce registre.

Registres de direction DDRA – DDRB :

Ils permettent de définir le sens de transfert de chacune des lignes des ports A et B. Un état logique

« 1 » définit la ligne en sortie, un état « 0 » , en entrée. Ex : pour mettre la ligne PB4 en entrée et

toutes les autres en sortie, il faut écrire la valeur $10 dans le registre DDRB.

PROGRAMMATION D’INITIALISATION DU PIA :

(port A en entrée, port B en sortie).

Accéder au CRA Accéder au CRB

Accéder au DDRA Accéder au DDRB

Port A en entrée Port B en sortie

Accéder au CRA Accéder au CRB

Accéder au ORA Accéder au ORB

PIA6821 Cours Page 2 sur 4

Fichier téléchargé sur : http://www.lelectronique.com - webmaster@lelectronique.com

Source : Stéphane – Tronic – http://www.tronic.fr.st – tronic@fr.st

SCHEMA FONCTIONNEL INTERNE

PIA6821 Cours Page 3 sur 4

Fichier téléchargé sur : http://www.lelectronique.com - webmaster@lelectronique.com

Source : Stéphane – Tronic – http://www.tronic.fr.st – tronic@fr.st

PIA6821 Cours Page 4 sur 4

Fichier téléchargé sur : http://www.lelectronique.com - webmaster@lelectronique.com

Source : Stéphane – Tronic – http://www.tronic.fr.st – tronic@fr.st

Vous aimerez peut-être aussi

- TD2 Corrigée PDocument5 pagesTD2 Corrigée Pfarid regraguiPas encore d'évaluation

- Corrigé TD4 CNDocument14 pagesCorrigé TD4 CNPapeCheikh SYLLA100% (1)

- Microprocesseur 8086Document79 pagesMicroprocesseur 8086Hichem Hamdi100% (3)

- Architecture Du Microprocesseur 6809 de MotorolaDocument14 pagesArchitecture Du Microprocesseur 6809 de MotorolaPhylipe Rodrigez100% (1)

- ClimatisationDocument35 pagesClimatisationJo100% (1)

- Processeur 6809Document172 pagesProcesseur 6809Oumar Mané50% (10)

- CAT Groupes Electrogenes FDocument20 pagesCAT Groupes Electrogenes Filham28683% (6)

- Cours Architecture IOT 3Document17 pagesCours Architecture IOT 3Sourour JellaliPas encore d'évaluation

- Formation Interface Communication 1Document19 pagesFormation Interface Communication 1اشر اقPas encore d'évaluation

- 16FXXXDocument86 pages16FXXXkhmPas encore d'évaluation

- TP Informatique IndustrielleDocument7 pagesTP Informatique IndustrielleYoussef_Consty_4665100% (3)

- Rapport Steg ZarzisDocument18 pagesRapport Steg ZarzisŠärâh Ğhērŕî100% (1)

- TP N°1 M1 Embarqué MicrocontrôleurDocument2 pagesTP N°1 M1 Embarqué Microcontrôleurعمر الفاروقPas encore d'évaluation

- Cour de CPI 2016-2017Document46 pagesCour de CPI 2016-2017patrijuvet100% (11)

- 2 ProcessusDocument114 pages2 ProcessusBtissamBettyPas encore d'évaluation

- Interruption 16F877Document29 pagesInterruption 16F877Tran Cuong Hung100% (1)

- Corrige TD3Document3 pagesCorrige TD3Es.sabery IsmailPas encore d'évaluation

- TD Exam PDFDocument12 pagesTD Exam PDFpapPas encore d'évaluation

- PIA6821Document4 pagesPIA6821Badel TchangomPas encore d'évaluation

- Pia 6809Document5 pagesPia 6809Abdelwahab EL Filali100% (2)

- TD 06 CorrigeDocument12 pagesTD 06 CorrigeOmar KhayyamPas encore d'évaluation

- Port Parallèle Pia 8255Document11 pagesPort Parallèle Pia 8255alex bbapPas encore d'évaluation

- Structure 68000Document9 pagesStructure 68000Otman Mchachti100% (2)

- TP Moto 6809Document7 pagesTP Moto 6809gamerzxs681Pas encore d'évaluation

- TDDocument10 pagesTDredPas encore d'évaluation

- Exercice 0:: Tp1: Architecture Des MicrocontroleursDocument3 pagesExercice 0:: Tp1: Architecture Des MicrocontroleursأمينPas encore d'évaluation

- Microprocesseur 6809: Présentation GénéraleDocument11 pagesMicroprocesseur 6809: Présentation GénéraleMOHAMED TAMZAITIPas encore d'évaluation

- Interface Serie Programmable - ACIA 6850Document10 pagesInterface Serie Programmable - ACIA 6850Lynda Tli67% (3)

- Microprocesseur 6809 - ExpoDocument44 pagesMicroprocesseur 6809 - ExpoZAAIRA HAMZAPas encore d'évaluation

- Compte RenduDocument10 pagesCompte RenduEgillPas encore d'évaluation

- Compteur SYN A2-2 2020Document8 pagesCompteur SYN A2-2 2020basmaPas encore d'évaluation

- Mise en Route Du Compilateur MPLAB XC8Document11 pagesMise en Route Du Compilateur MPLAB XC8nawzatPas encore d'évaluation

- Xor PDFDocument5 pagesXor PDFYoussef RagraguiPas encore d'évaluation

- Cmpte Rendu TP1Document15 pagesCmpte Rendu TP1groupe88100% (5)

- Exercice Corrigée Les Modes D'adresse (Assembleur Motorola 6809)Document3 pagesExercice Corrigée Les Modes D'adresse (Assembleur Motorola 6809)YoussefPas encore d'évaluation

- Travaux Dirigés-Microprocesseur MicrocontroleurDocument18 pagesTravaux Dirigés-Microprocesseur MicrocontroleurFatima BettayebPas encore d'évaluation

- TD - N°2 - EN - Systèmes À Microprocesseur PDFDocument7 pagesTD - N°2 - EN - Systèmes À Microprocesseur PDFTimble Puteur100% (1)

- TDu CDocument49 pagesTDu CnawzatPas encore d'évaluation

- Programmation de L'interface ParallèleDocument10 pagesProgrammation de L'interface ParallèleAbdeltif BelquorchiPas encore d'évaluation

- TD 1 Info Indus 2019-2020Document3 pagesTD 1 Info Indus 2019-2020Romaric Tankoano100% (4)

- Compte Rendu Assembleur 1Document3 pagesCompte Rendu Assembleur 1El Oufir El MehdiPas encore d'évaluation

- Guide Moto6809Document23 pagesGuide Moto6809fatima zahra benmeriemePas encore d'évaluation

- Cours3 Uc Ports Finale Étudiants PDFDocument10 pagesCours3 Uc Ports Finale Étudiants PDFYoussef HaidaPas encore d'évaluation

- Ch6 Pal FplaDocument6 pagesCh6 Pal Fplanoubis100% (2)

- Simulation 6809Document5 pagesSimulation 6809Mr S.KamaliPas encore d'évaluation

- PIC LeçonN°2EDocument31 pagesPIC LeçonN°2ESmart Classe50% (2)

- TD3-En-Elements de Reponse, Seance 8 (Ex1+Ex2), Amari AzizDocument6 pagesTD3-En-Elements de Reponse, Seance 8 (Ex1+Ex2), Amari AzizMahdi LahdiliPas encore d'évaluation

- Rapport Fox g20Document18 pagesRapport Fox g20Omar ZemraniPas encore d'évaluation

- tp3 Ing 2015 PDFDocument7 pagestp3 Ing 2015 PDFDorian GreyPas encore d'évaluation

- TP2 MicroprocesseurDocument14 pagesTP2 MicroprocesseurAdem AounPas encore d'évaluation

- Mikroc - Programmation Des PIC - GLT - GSIDocument31 pagesMikroc - Programmation Des PIC - GLT - GSIImane LamdainePas encore d'évaluation

- Upload - Série D'exercices N°4-3tech-Bascules-2013-2014-CorrectionDocument5 pagesUpload - Série D'exercices N°4-3tech-Bascules-2013-2014-CorrectionchediPas encore d'évaluation

- IjDocument7 pagesIjAbderrahmane WardiPas encore d'évaluation

- Logique Combinatoire (TP Automatisme ... Adder 4 Bits Soustracter 4bits Multiplieur 4 Bits .....Document37 pagesLogique Combinatoire (TP Automatisme ... Adder 4 Bits Soustracter 4bits Multiplieur 4 Bits .....Soufiane El AoufiPas encore d'évaluation

- TD 2Document5 pagesTD 2adda chariPas encore d'évaluation

- Série 5Document3 pagesSérie 5Blidi AymenPas encore d'évaluation

- Epreuve 1Document2 pagesEpreuve 1ChristianPas encore d'évaluation

- Mise A Niveau 1Document4 pagesMise A Niveau 1koyabePas encore d'évaluation

- IntroductionDocument9 pagesIntroductionabderezakpcPas encore d'évaluation

- Architectures Des Ordinateurs 2: Dr. Fouzi MekhaldiDocument26 pagesArchitectures Des Ordinateurs 2: Dr. Fouzi MekhaldiRanPas encore d'évaluation

- Port SerieDocument9 pagesPort Serieahocine2011Pas encore d'évaluation

- Chapitre 4 2020-2021Document64 pagesChapitre 4 2020-2021M'hamed Saadi BachirPas encore d'évaluation

- Cours Microcontrôleur MCS-51Document19 pagesCours Microcontrôleur MCS-51Maha BadriPas encore d'évaluation

- PlanDocument1 pagePlanMounaim MatiniPas encore d'évaluation

- ENR Hydraulique Episode 3Document4 pagesENR Hydraulique Episode 3Mounaim MatiniPas encore d'évaluation

- Stockage Energie ÉlectriqueDocument7 pagesStockage Energie ÉlectriqueMounaim MatiniPas encore d'évaluation

- Stockage Energie ÉlectriqueDocument7 pagesStockage Energie ÉlectriqueMounaim MatiniPas encore d'évaluation

- Poly TD Ident 2019Document21 pagesPoly TD Ident 2019Mounaim MatiniPas encore d'évaluation

- Etude Economique Et FinancièreDocument5 pagesEtude Economique Et FinancièreMounaim MatiniPas encore d'évaluation

- ModélisationDocument3 pagesModélisationMounaim MatiniPas encore d'évaluation

- Compte Rendu: Commande MLIDocument2 pagesCompte Rendu: Commande MLIMounaim MatiniPas encore d'évaluation

- Le Statut JuridiqueDocument4 pagesLe Statut JuridiqueMounaim MatiniPas encore d'évaluation

- I. Prototype de STEP:: 1. Composants Important Pour Le PrototypeDocument7 pagesI. Prototype de STEP:: 1. Composants Important Pour Le PrototypeMounaim MatiniPas encore d'évaluation

- DroitDocument4 pagesDroitMounaim MatiniPas encore d'évaluation

- Objet:: Au Service de Coopération Et D'action Culturelle Pole Enseignement Supérieur Recherche Et Mobilité ÉtudianteDocument1 pageObjet:: Au Service de Coopération Et D'action Culturelle Pole Enseignement Supérieur Recherche Et Mobilité ÉtudianteMounaim MatiniPas encore d'évaluation

- Le Statut Juridique de Notre EntrepriseDocument2 pagesLe Statut Juridique de Notre EntrepriseMounaim MatiniPas encore d'évaluation

- GRILLEDocument1 pageGRILLEMounaim MatiniPas encore d'évaluation

- Question 3Document1 pageQuestion 3Mounaim MatiniPas encore d'évaluation

- Résumé DroitDocument9 pagesRésumé DroitMounaim MatiniPas encore d'évaluation

- RDM CoursDocument18 pagesRDM CoursMounaim MatiniPas encore d'évaluation

- RSE2DDocument7 pagesRSE2DMounaim MatiniPas encore d'évaluation

- Travail Demandé: Recherche Sur INTERNETDocument1 pageTravail Demandé: Recherche Sur INTERNETMounaim MatiniPas encore d'évaluation

- Une Lettre de CommandeDocument5 pagesUne Lettre de CommandeMounaim MatiniPas encore d'évaluation

- ArticleDocument2 pagesArticleMounaim MatiniPas encore d'évaluation

- Nce You Upload An Approved Document, You Will Be Able To Download TheDocument24 pagesNce You Upload An Approved Document, You Will Be Able To Download Theth3 technologiePas encore d'évaluation

- ResumeDocument2 pagesResumeMounaim Matini100% (1)

- Société Vigo CarDocument5 pagesSociété Vigo CarMounaim MatiniPas encore d'évaluation

- RapportDocument5 pagesRapportMounaim MatiniPas encore d'évaluation

- TD2 ElectrotechniqueDocument2 pagesTD2 ElectrotechniqueMounaim MatiniPas encore d'évaluation

- TD 2 OnduleursDocument2 pagesTD 2 OnduleursAhmed Jellouli0% (1)

- TD 1 - 2021Document3 pagesTD 1 - 2021Mounaim MatiniPas encore d'évaluation

- CfinS1AnanuGLSID-BDCC 2020-21Document2 pagesCfinS1AnanuGLSID-BDCC 2020-21Mounaim MatiniPas encore d'évaluation

- TD 2 - 2021Document2 pagesTD 2 - 2021Mounaim MatiniPas encore d'évaluation

- Cours S5 Chap1Document88 pagesCours S5 Chap1Boutouil HassanPas encore d'évaluation

- ATHEBA - 3f - Les Murs Dans Le Bâti AncienDocument4 pagesATHEBA - 3f - Les Murs Dans Le Bâti AncienMichel WalkowiakPas encore d'évaluation

- Processus D'extraction D'huile de GrignonsDocument3 pagesProcessus D'extraction D'huile de Grignonsouzeouze123Pas encore d'évaluation

- compte rendu - نسخةDocument4 pagescompte rendu - نسخةyoucefPas encore d'évaluation

- TP MbakidiDocument10 pagesTP Mbakidifrancis luminguPas encore d'évaluation

- Beep Error Code - LENOVO - Toutes Les Idea Pad LaptopsDocument3 pagesBeep Error Code - LENOVO - Toutes Les Idea Pad LaptopsRazafimamonjy Elie J HerminotPas encore d'évaluation

- TABE Minco Maquinarias ChileDocument13 pagesTABE Minco Maquinarias ChileNelson Andrade VelasquezPas encore d'évaluation

- PFE LoubnaDocument22 pagesPFE LoubnaJeliel AzuritePas encore d'évaluation

- Support de Cours Et T.D. Reseaux DaccesDocument45 pagesSupport de Cours Et T.D. Reseaux DaccesDAP creatPas encore d'évaluation

- UntitledDocument69 pagesUntitledRégis ESCOBARPas encore d'évaluation

- Devoir WordDocument10 pagesDevoir WordJonathan FrédéricPas encore d'évaluation

- Projet Grad Tri Part 1Document8 pagesProjet Grad Tri Part 1Lamyae AMMARIPas encore d'évaluation

- Res TP PHP IHMDocument5 pagesRes TP PHP IHMfradj hediPas encore d'évaluation

- Contrat On AirDocument7 pagesContrat On AirFERRITOPas encore d'évaluation

- TD Maison IntelligenteDocument11 pagesTD Maison IntelligenteSéléna BUEBPas encore d'évaluation

- Best Practices VOIP VGDocument17 pagesBest Practices VOIP VGStéphane GuézouPas encore d'évaluation

- Le Serveur D'impression Avec Windows Server 2019Document16 pagesLe Serveur D'impression Avec Windows Server 2019Mohamed MessbahPas encore d'évaluation

- HS72 HS74 HS76Document28 pagesHS72 HS74 HS76François EstradePas encore d'évaluation

- Programmation PlanDocument10 pagesProgrammation PlanVazgen MarkaryanPas encore d'évaluation

- CV Auto EvaluationDocument11 pagesCV Auto EvaluationAlexandra Sascha Badila SterckPas encore d'évaluation

- C. Difficile Clostridium Difficile: Glossaire - Technique Radiologique AcronymesDocument3 pagesC. Difficile Clostridium Difficile: Glossaire - Technique Radiologique AcronymesSlim MâamerPas encore d'évaluation

- Série 3Document4 pagesSérie 3Zain GaradiPas encore d'évaluation

- Devoir Deux VersionsDocument8 pagesDevoir Deux VersionsTou MatwiPas encore d'évaluation

- Application Informatique Pour Le Calcul Du Temps Et Coût D'usinage Des Pièces en Fraisage Et en TournageDocument82 pagesApplication Informatique Pour Le Calcul Du Temps Et Coût D'usinage Des Pièces en Fraisage Et en TournageppePas encore d'évaluation

- CV Gestionnaire PaieDocument1 pageCV Gestionnaire PaiesandycpassyPas encore d'évaluation

- Qualité 4.0Document146 pagesQualité 4.0trabelsiPas encore d'évaluation