Académique Documents

Professionnel Documents

Culture Documents

Partie 2 A. CMOS 3-Les Amplificateurs PDF

Transféré par

Moussaoui Bassma0 évaluation0% ont trouvé ce document utile (0 vote)

10 vues22 pagesTitre original

Partie 2 A. CMOS 3-Les amplificateurs.pdf

Copyright

© © All Rights Reserved

Formats disponibles

PDF ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

10 vues22 pagesPartie 2 A. CMOS 3-Les Amplificateurs PDF

Transféré par

Moussaoui BassmaDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 22

Conception des circuits intégrés anal MR-E&ING-E

3. Les amplificateurs :

3.1. Amplificateur inverseur

Vee

—_ Vo

Charge Teta bloqué | \giem restin

! ee

Ves! Voo Vor

. mal

va] Bat conducts

Vou

Wi

~Vss

Figure34 : Différents circuits possibles : inverseur contrélé par Sinkcourant et a charge active

Vop 3

-

i typ le F

“Hyon fe Vour , shew

2 ”

1 1 1 1,

ey M [a

se a abs vee

a b c

Vss 4 a

Figure. 35 : Inverseur contrélé par sinkde courant

a- A charge active pMOS enrichissement,

b- A charge source de courant,

c- A charge active nMOS enrichissement,

d- A charge active nMOS déplétion

Les transistors Mz fonctionnement en régime active (transistors) saturés

- Analyse de l'inverseur de la figure 35-4

Transistor M2 - Vg = Vp = Vp = Veg => Vem > Vos ~|Va0]

‘Transistor tue

Og Wie)? # eZ lan Voor- Wen?

Transistor Ml on #intéresse ala zone amplification : transistor My saturé.

Condition de saturation

Vpsi > Ves: — Viw > Vour~Vss > Vin Vss ~ Vaw > Vour > Vin ~ Vi

On peut écrire (on néglige I’ effet de modulation de canal)

In #Kp

Ky Wy > KpWy >

ae War Ves Van? = SE Von — Voor” Mra)

= Voo-Vour-Vio_ [Ru WiL

Vyy-Vas Vow VE Waly

99

N. HASSEN

Conception des circuits intégrés analo giques MR-EGING-E

On peut en déduire le gain en tension petits signaux

Wous| _ Your. _ [Ew Wis __ Sm 65)

Bae by Vax Vp Wala Sn

Oum, W2=Sum, Ly=10um

T5V, Vip = -0,75V, Ky = 240ANV?

15.10

i ae 1 Mest bloqué

IN eee Si Vegi = Vaw Va < Vis +V inv

[ Vpy <-5+0.75 => Vpy <—4.25V

Figure 36 : Simulation SPICE

Modéle petits signaux en basse fréquence

. Gain en tension

aay + Em give + EE

SaV2 Tas fsa Fast

v2 Aves: Vp

—

Sat Vv Iran | Voxe

Figure 37: Modéle petits signaux en basse fréquence

Th

© Résistance d’entrée -®,

100

N. HASSEN

Conception des circuits intégrés analo giques

MR-E&ING-E

Vox (4) uo Wy, | ae

© Etude en haute fréquence

Con Ce == an Q Tea Cod

Ca

y,

bs r

Cs 1

Va

. >

Vout

Fast ['/8m2 reed Vet

Figure 38 : Schema équivalent en haute fréquence

Avec

C= Cet Cg

Cy = Cy +Cyr + Cran + Coat

C3= Coa

ByaiVin + 8n2Veut + Vout Baer + Saez +IC2@) — Vig ~ Vert )C30= 0

© VeulBno+ Baa + 842 + (C2+C3)0]=—Vin Ga iC39)

101

N. HASSEN

Conception des circuits intégrés analo giques MR-EGING-E

A, = Note = Gai ~ 1030)

Va Baa + Bai + Baa +) (C2 +C3) 0

q-12

= Sm2*8ert8a2 Sm

WG +G a

Sm2 + 8a + 8052

- = Sm = — Sat

0 Sm? + Basi + Bacr m2

gy = m2 * Basi + Basa _ Sma + Basi + Bac2

7 C,+C Copa + Cga + Com + Coan + Cg

La pulsation de coupure a-3dB est 4g = Og)

4

|arla

20log|A.9| :

Odb °

Arg As(w))

180)

135°

90

45

0 o

ot 62

Figure 39 : Simulation de module et de phase

Exemple:

Ww, 15m W, Spm ve =sv

Trio’ Tet dom 7 Won Ms =

Surface et périmétre drain-source de My est 150um? et 50 um et pour le Mz: 50 um’ et 30

um,A 20

Point de fonctionnement en statique lorsque Vout

WW, 86)

1-% - Ve.) (5—0,75)° = 36uA,

3L, pp, za) 2010 ° y H

102

N. HASSEN

Conception des circuits intégrés analo giques MR-EGING-E

My est saturé >

- Gain en tension

Simi = 50,91 Us, Eger = 0,36 US, m2 = 16,97 US, Eden = 0,72 us

A = 50,91 ae

= 7697 +036+072

- Résistance de sortie - Royy = ———___1-____= 554K

(16,97 + 0,36+0,7 4S

- Pulsation angulaire de coupure a -3dB,

Cyan = 30,93F , Cog = 24,430, Cyqy = 16,04F , Coy = 4,73, Com

18,0510

a = 234Mirtls

(0,93 + 25,43+16,04+ 4,73) x10

Ora

fag = 37M

Pour l’inverseur de la figure 35-c:: il est presque identique au circuit précédent (fig 35-a). Il ala

méme caractéristique du transfert. Il a en plus une transconductance gas qui est dea I’effet

substrat

On trouve Ay =-1,56, Ry =30,7KQ. f.ggy = 42,8MHz

Etude Uinverseur de la figure

Mp: est saturé si Vey > Vag -|Vre|=> Von - Vour > Von ~ Var ~|Vze|= Vour < Var + [Vee]

My est saturé si Vpgy > Vegi — Vinx = Vour > Vay - Vaw

Voir caractéristique de transfert (figure 40)

Calcul du gain en tension

KW,

Le courant dans un transistor est: 1p = KW,

2

‘Wes ~ Vix)" + AV ps)

Soit Ip) = Ip) >

Ky

ay

ov ~ Vss~ Vane) [+ AayVour - Vs > ~ Va ~ Wap)"[l+ Aeon - Vour)]

En dérivant cette égalité

Ky

24

= Vig — Van) hy Moe

= Og Vis = Vd ar

103

N. HASSEN

Conception des circuits intégrés analo giques MR-EGING-E

Wy

2Ly

Ve

_ Voge)? Ayte MoUt

(om Van ~ Va Aat- aE)

Mou K KW,

BAL (Vi, — Vs — Vin)" Aas +2 Va —

= Noa.

WV, Ly Ly

fan ~ |Vrp)? Ap)

Ky

2h, (Vin ~ Vs ~ Vawll + Aas (Yoru ~ V55)]

Qt Ap) Bast + Bar

Figure 40 » Résultat de simulation

Schema équivalent petits signaux (basse fréquence)

A=?

Tas2 gat Vay = — OUT

falas

= Emi gal

gm Vax rast | Vow Taal Basi + Basa

= Basi + Bas2

104

N. HASSEN

Conception des circuits intégrés analo giques MR-EGING-E

Schema équivalent petits signaux (haute fréquence)

C3

rar OP? Vat TJ

, = C: Ban Val]

Va® tt

C

a a1 Va

Coa

Cen

Avec

Cy= Cn + Cyn Cy = Coa + Sgn + Cuan » Cs = Cyn

Bint yp + ——* 5 —~ Vine - Vou)

sale! —

Cy

Vourl€ gg1 + G42 + PC + PC3 = -Vns(Gar- PCs)

Ay = Vouz = Gi= PCs) = @mi~ j0Cs) G6)

Vax Bast + Bao + P(C2 + C3) Ban * Ban + 10(C, + C3)

aeol - ees) A, (

Bert Baa Bm °

> 7+ Gn)

ja(C, +C,

14 10C2 + Cs) je

Bai + Bar pp

La pulsation de coupure a -3dB est

= Sai +8e0 Baa 8a (3)

a CytCy Gg $C gy + Cyn + Cg

Exemple AN :

W,_15um Wy Sym

L, 10um’ L, 10um

Yap =2V_ Vp =—Vs

Surface et périmetre de My - 150um” (50 um) et Mp -90 um? (30 um)

KyW, 2

T= SE (po ~ Var ~ Was)? [1+ Aa (Vo0 ~ Vou] G9)

2Ly

= 6- (0,75)? (1+ 0,1) =11,14pA,

105

N. HASSEN

Conception des circuits intégrés analo giques MR-EGING-E

0.5

2IpLa [2ai14 x10

Von = V3 0,75 + [>t O10 Ay say

cr oo 75+ Garay .

KyW,

A4pS, Bay = 0,228

Gar = 28,325, Bar = 0.115, gino

Ay

28,32

011+ 0,22

1

(O.11+0,22)10°¢

@. 3a) = 6,13Mrdl/s, £345 = 0,976MHz, Cyai = 30,934F, Ceiz = 2, 18F, Cyao= 16,048F, Cyan = 4,73 F

-84,74

2,99M,

Etude inverseur Push-pull

Wy = Sum, Ly = 10um, Wy = 15pm, Ly = 10m, Vp

Condition de saturation de My

Vour > Vin Vin

Condition de saturation de Mz

Vor xu@n ] Pan |

Ay bob J tL ke 40)

Daly + dplp

106

N. HASSEN

Conception des circuits intégrés analo giques MR-EGING-E

m1 +82

Bai +842

+2) Ip

Schéma équivalent petits signaux

Sm Var ra

—

& ete = 1035

ut + Cg + Conn

fa Vin ran | Vou

Figure 42 : Schéma équivalent en petits signaux

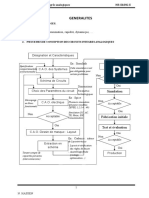

‘Comparison of the small signal performance of MOS inverters

aC ac

Veltae utp

Figere jain oa

pannel Stet !

Kavetoes 358

chums! 35h

‘tive lat Sta

= Be eee mie

source load a

sinking iene

ohana asa as

‘pet od

sing iver

Push-pull al w=

107

N. HASSEN

Conception des circuits intégrés analo giques MR-EGING-E

3.2. Amplificateur inverseur cascode :

ast

—- Vo

‘Vee saw Ves

—i" ©

|__Vour o Cet psD2

Vex { t o>) Tt

Hw ©

De, [Ju] eer resi woe “

In av e, +=

Rs

| Vss S1-92-02-6

Figure 43 : Amplificateur inverseur cascode

C= Cont Con

Cy = Cay + Cg + Ca

En basse fréquence

Feat

Va (Bast + Gn 3 + Ganea + Bass )= ~ Ba V1 + Vou Bass w

Voxe fsa = (Gin + Gas V2 — (Vena ~ V2 )eaes

Vout (Baa + Bass )= (Gn3* Gaus + Bass V2 ®

=v,

(a2 + 453) dans (1) >

Bina + Buna * Baa

NoalBan * 23) (4, + 05+ fans * Bas) = ~Ei¥i + Vous

Sm3 + Bmp3 + Bass

Ay = ew = 8mi(Bm3 +8mns + Bas) ee Smt

Vi See2 Gai +8m3+8an3t8as)+8ei8e3s Bar

Exemple AN

Guy = 28,3218

Sa2 = 0,11uS

SA, =-2575

108

N. HASSEN

Conception des circuits intégrés anal

jiques MR-E&ING-E

Augmentation du gain

Voo

Vep fm

—L™ b

Vor

Vex

| Vss

™

ve lal

x [" Mi

4

Vss

Figure 44: Augmentation de gain

Diminution du gain

Vi

Vap ”

eu

| _Vowr

Ven

= Vss

M3

‘Var Ibi

—_ Ip

My

Vss

Figure 45 : Diminution de gain

N. HASSEN

2K Wil

Sw

Lilpytp2

Baa

Ip =!p2 +o

ew

| 4] («

Lidpa

Le gain est augmenté du facteur (+

=A,

@1)

Le gain est diminué de

109

Conception des circuits intégrés analo giques

MR-EGING-E

Montage cascode symetrique

Vop

Ver. ~BmiBm38 mnt @)

ot Bal SmiSas + Sa2maBaed

V: L

“Evo fet = a eo)

° > Gaifaa . BanBan

93 Voor Baa + Gna + Bans + Bas Baa + Bas + Bune + Bae

Ia

oe vss ee

7 Tout Cea + Caps + Cara + Cou)

1

“—f M

Vss

Figure 46 - Montage cascode symétrique

Exemple: A,

10716, fay = 601MQ, @ gy = 30.93¢dls, Egy = 4 9°KH2

3.3. Amplificateur différentiel CMOS

3.3.1. Configuration générale : Caractéristique de transfert

TA

Charge active

wpe Vo e—| tp:

ey uw

Veo

Voie. MI we a

VSS

M, = M.=Vna= Vie Ka= Ke

On néglige I’ effet de la modulation du canal.

Vp = Var ~ Vez

Vos ~ Vom

KW

L

En posant : B=

110

N. HASSEN

Conception des circuits intégrés analo giques MR-EGING-E

Vp- [8 i= 4)

Ty Pry

Quand B=

Iss =I. +Ip2 45)

(44) et (45) donnent

isVp| 8 _8'Vp 46

2 lz Alyy 9)

aya

Vp] 8 PVD ca

Ine oy [E gg? a

s relations du circuit sont valables seulement si

Me 2

[=] et si My et Mp sont saturés. Vp) > Ve, — Ving Vo2 2 Ven — View

Les équations (46) et (47) sont représentées sur la figure 47,

La pente de ces courbes définit la transconductance différentielle de I’ amplificateur.

f iss

Vp=0 48)

Transconductance de sortie: Baa

Top Ip - Ipo

a9)

M1

N. HASSEN

Conception des circuits intégrés analo giques MR-EGING-E

© Caractéristique de transfert de tension (Figure 48)

On pose Ry la résistance équivalente de la charge active

Voatt= Voi = Von -B x Ips et Vouta

En mode différentiel

¥,

Vai SB, Ve =

Done la condition de saturation de My et Mz est

Vy

Voi 2 Ver ~ Vow Vo = POV

VopRiles i

3.3.2. Exemples : configuration pratique :

Vop Yeo ’ Von

if ~

M3 J iM Ms “HT [t™ 7}

L, 3

Vor Yoo [ ven_| loa Vp, Ys

reo com ye

uM [%o, Yox / Ibu Ibn

ie Ie de be te 8

Xx “7 IN , 7

Ves Sex Vos Sess veo

Iss

Ves

Iss Iss

Veo a MS Yoo e—| Ms Veo a Ms

Vss _| vss Vs

@ G

Charge active Charge: sowce de courant Charge : mir

NMOS ensichissement

de cowent

Figure 48 : Exemples de configurations pratiques

N. HASSEN

Conception des circuits intégrés analo giques MR-EGING-E

a. Etude en mode différentiel :

a1 Btude du montage * figure48-a

© Etude en grand signal

Voi = Vop ~ Voss

Voss = Vosiat + Vi

Voi = Vp ~ Vosssa ~ Vine = Vop — Ving (60)

Vo = Vop - Venu ~ | 222 (61)

/>2 = Vop ~ Vinw

VB

KW

Avec =

L

Gain en tension entrée différentielle une seule sortie

ee Sa1-(220}(22)

Ny \ Api Mp.

62)

L’équation (5)

4

1) (63)

2 B3

Ce gain est identique a celui de l'inverseur de la figure 35-c

“

Goit V,- “2 et a, =- fe pour l'inverseur)

2 2

© Etude en petits signanx (Schema équivalent Fig 48-2)

> Mode d’excitateur : Mode différentiel

Ya Via

yey

+

+) val? 1 eave K

- ° PY | rast Vos}| jas | Var

+ Tass

D\ -val? Deve [yar ve fh Va

~ ei gs ie

.

113

N. HASSEN

Conception des circuits intégrés analo giques MR-EGING-E

+

+\val2 Vv

# val?

= «= Tast us | Van

+ Ves

vial? Vea oe as? 7 Var

Vegas fa

+

Routt

eval fytas tu

¥) ew Vel

= Bt

"2

2Gns+ Gin + Bas) 2ems 2] (Wy

Kya| 2

= Su

-ve

==

Va (Gat * Barr + Bau)

Gain en entrée différentielle et sortie en différentielle

Aca, = Ned _ Ya Veo _—8m1_ Gt _ > Bm

vad ==

Va Va Bas

Ms et My sont identiques donc gus“

Résistance de sortie

1

Row =————_——_

NY Bua + Ban +2a3

N. HASSEN

Conception des circuits intégrés analo giques MR-EGING-E

1 1

Bms+Ba2tBqc4 Smt

Résistance de sortie différentielle

1,1 2

+e

83 Sm4 Sm3

Roa = Routt tRout2

@.2,_Btude en petite signaux: Figure 48-b

Le schéma équivalent petits signaux est identique ala figure 48-a, seulement on a Vesi=Vesi=0

ce qui implique que VgssGas=Vepefin=0

Var 7 Sm

Ava = = Sm

Oe" Va 2am + as)

Vo

Aya = 22 Smt

Via 2@ast + Sas3)

Avaa = Vol Sm1__ Smt

Va Sait8a3 a2 +Sa4

Rot=———! Baa =——

Baa tBu Baa +Bas

Roa =

Sai +8as3

© Etude figure 48-c

G,Ds.G4

+

eval? a

: et Tras Ve|[ as | var

* Tass Baie

+ s I.

val? Veo Qe" rasa we

+ Bat gt

De "

115

N. HASSEN

Conception des circuits intégrés anal MR-E&ING-E

+

2 Meas

)\val2 Vy wad

+ Tass I

fo oe + >

val? Ver oe" fe Dewva py... | V2

a

Vai Smt

Aaa Ay

ia 2@m3+ Sant + Sas)

no + BiVa + Car +8e4)Vea =

bots + (610 + Basin =0

~ Sno + 8m ——) + Bar + Sas) =

2 (Guna + Sari + Baca)

Smifms _1

Su3*SaitSa3 Sa2 Sas

_—__~ 8a Gaug + Bint 1

2@ma+Bei+8as) 2 Bust Be1tBa3 Car +8as)

78m 1 m1 Bn 1

S Bat _ 2 (gy + SetBmty_"_)

gma 2 8m3 842 + Baa

avec Gna" Bin et Gent Bma

78m &,

Avg = - l_=

m3 Sa2 t+ Sars

1

Wiz

2yelss 4)?

Ly

(y+ Ass

1 2 1

© Gaz t8an) Oates Mss

116

N. HASSEN

Conception des circuits intégrés anal

MR-E&ING-E

b. Etude en mode commun

VerVer=Ve= (VortVen)/2

5.1. Détermination des valeurs minimale et maximale de Vet Vexe (exemple48-c)

© Valeurs minimale et maximale de Voi

‘M; saturé implique que Vper=-Vnn

. Vpe1 = Vpp— Vsp3— Vai = Vop— Vse3 — Ven

(a

Vsas = Vane + Vepal= | >? +1 Viral

V Bs

(2,

D3

Vpei = Vop ~ 3 | Vaesl -Ver

V Bs

Vor est maximale si Voei=-Van

fis.

Veanee= Vop ~ |S 1Vepal+¥;

cine Yop ‘real +Ven

VBs

Vv Vv

J Zi “ y. {I Z J.

pes Vew = Von eVert Han Vi

7

Autrement : Voi = Vee + Voss +Ves1

Votmm = Vis + Voss +Vosise + Vin

© Valeurs minimales et maximales de Vow

Veos = Von ~ Vsp3 ~ Vout = Von ~ Vse3 ~ Vout

Mg saturé = => Veps=-[Vrpd

iE

oo fS

VBS

v

Vor ee)= WVrp31+1Vzpel

Voecain) = Verma ~ Vara, Voaeany = Vss + Vossen +Vosine

Ps, fle

+ [ss

VB,

Voagasy” Ves +

oatany™ Vos

= VB

M17

N. HASSEN

Conception des circuits intégrés analo giques MR-EGING-E

b.2.Etude en petits signaux : Exemple Fig43-b

.

Pp) Ve

+ Vs

=) Ve ? BeaV en [tar

.

Var

Smi a3 Ve

Vo Tag = Sautese

1+ 28501 Tacs

D’oitle gain en mode commun

a - Me _ Va 2 = Smiles

Ve Ve 14+ 28milas

- Taux de rejection en mode commun

mt

apuc < curr — Ava! 2@ai +848)

[Ayel_ Smifag

1+ 28 ntfass

Bas3 1 + 28mttas5)

TRMc = 8430+ “Smits? =

2@a2 + Bas) |S St

Si Gao © Bass © Basg => TRMC = Bata

118

N. HASSEN

Conception des circuits intégrés anal

MR-E&ING-E

3.4. Etage de sortie classe AB:

Yop

Vous fT" Ms

vee x , {fe 0 Vs

Vote

Vox rim

Vsost Vos=Veut Vier

VsestVes=cte si le courant de polarisation de Ms est constant. Dans cette condition,

Vaugmentation de Vgs fait diminuer Vgso et vice-versa

© Quand Vsos+Ves

implique que Vig

2

- Pour Mi conducteur: le courant drain #0 et Vgi?Vinv

- Pour Mp conducteur : le courant drain #0 et Vg2 My et Mp ne peuvent pas étre conducteur simultanément : classe B de fonctionnement.

Quand Veu>0 implique : Mj fonctionne en source suiveuse et Mp est bloqué.

Quand Veu<0 implique : Mp fonctionne en source suiveuse et My est bloqué.

© VsestVesi>0 ; M et Mz sont les deux conducteurs quand Vow =0: l'étage de sortie

fonctionne dans la zone classe AB.

Si Vna= Vins et Virz= Vaws avec [IpsF| Ins] donc

|_2Ips {ta

\EROMDs \KnODe [KO

Si Vou=0, alors ler=llarl

2s

119

N. HASSEN

Conception des circuits intégrés analo giques MR-EGING-E

1»

Kp 5

t

Kp Oe

Ce point clef permet un bon choix de courant de polarisation

© Vow maximale

Vou?0, Ve? Vnii Mi source suiveuse

Vest = Vop-Veia-Vest

‘Vees minimale donc | Veasea/=[Ves3-Val

Voramy= Voo-lVeasset |-Vast sa-Vnen

© Vow minimale

Vou, Vig? [Va

Vea= Vss+Vass*Vign avec Vs5=- Veo

=-Vont Vast Vier

Veins) =~ Voot Vass sat Voge

120

N. HASSEN

Vous aimerez peut-être aussi

- Partie 2 A. CMOS 3-Les Amplificateurs PDFDocument22 pagesPartie 2 A. CMOS 3-Les Amplificateurs PDFMoussaoui BassmaPas encore d'évaluation

- Partie 2 A. CMOS 3-Les Amplificateurs PDFDocument22 pagesPartie 2 A. CMOS 3-Les Amplificateurs PDFMoussaoui BassmaPas encore d'évaluation

- Partie 2 A. CMOS 3-Les Amplificateurs PDFDocument22 pagesPartie 2 A. CMOS 3-Les Amplificateurs PDFMoussaoui BassmaPas encore d'évaluation

- RéférencesDocument1 pageRéférencesMoussaoui BassmaPas encore d'évaluation

- Partie 2 A. CMOS 1-Modéle Simplifie Du Transistor MOSDocument10 pagesPartie 2 A. CMOS 1-Modéle Simplifie Du Transistor MOSMoussaoui BassmaPas encore d'évaluation

- Rappels GénérauxDocument2 pagesRappels GénérauxMoussaoui BassmaPas encore d'évaluation

- Som MaireDocument3 pagesSom MaireMoussaoui BassmaPas encore d'évaluation

- Partie 1 A Bipolaire 2. Elements de Base Des Circuits Intégrés PDFDocument20 pagesPartie 1 A Bipolaire 2. Elements de Base Des Circuits Intégrés PDFMoussaoui BassmaPas encore d'évaluation

- Cours INGDocument31 pagesCours INGMoussaoui BassmaPas encore d'évaluation

- Partie 1 A Bipolaire 1. Composants Intégrable-Modélisation PDFDocument17 pagesPartie 1 A Bipolaire 1. Composants Intégrable-Modélisation PDFMoussaoui BassmaPas encore d'évaluation

- Partie 2 A. CMOS 2-Elements de Base Des Circuits Intégrés CMOSDocument17 pagesPartie 2 A. CMOS 2-Elements de Base Des Circuits Intégrés CMOSMoussaoui BassmaPas encore d'évaluation

- Cours Proba 2019-20Document23 pagesCours Proba 2019-20Moussaoui BassmaPas encore d'évaluation

- Série V ADocument2 pagesSérie V AMoussaoui BassmaPas encore d'évaluation

- Partie 1 A Bipolaire 2. Elements de Base Des Circuits Intégrés PDFDocument20 pagesPartie 1 A Bipolaire 2. Elements de Base Des Circuits Intégrés PDFMoussaoui BassmaPas encore d'évaluation

- Fic 00015Document18 pagesFic 00015Anonymous 73gEYyEtLPas encore d'évaluation

- Annexe3 PDFDocument2 pagesAnnexe3 PDFMoussaoui BassmaPas encore d'évaluation

- Devoir 1Document2 pagesDevoir 1Moussaoui BassmaPas encore d'évaluation

- TP Math IngDocument27 pagesTP Math IngHichem HamdiPas encore d'évaluation

- Annexe3 PDFDocument2 pagesAnnexe3 PDFMoussaoui BassmaPas encore d'évaluation

- TD2 PDFDocument2 pagesTD2 PDFMoussaoui BassmaPas encore d'évaluation

- Chapitre2 PDFDocument6 pagesChapitre2 PDFMoussaoui BassmaPas encore d'évaluation

- 3-Traitement Numerique Du SonDocument14 pages3-Traitement Numerique Du SonJad G. Ghosn100% (1)

- Chapitre2 PDFDocument6 pagesChapitre2 PDFMoussaoui BassmaPas encore d'évaluation

- Activité1 PDFDocument3 pagesActivité1 PDFMoussaoui BassmaPas encore d'évaluation

- TP Math IngDocument27 pagesTP Math IngHichem HamdiPas encore d'évaluation

- TD2 PDFDocument2 pagesTD2 PDFMoussaoui BassmaPas encore d'évaluation

- Activité1 PDFDocument3 pagesActivité1 PDFMoussaoui BassmaPas encore d'évaluation

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (587)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (73)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (265)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (119)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)