Académique Documents

Professionnel Documents

Culture Documents

CHAP2 Complet PDF

Transféré par

Zidi NesimTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

CHAP2 Complet PDF

Transféré par

Zidi NesimDroits d'auteur :

Formats disponibles

Cours PSoC 2019/2020

Chapitre 1 Architecture d'un PSOC

1.1 Définition

PSoC : Programmable System on Chip, est une famille de circuits intégrés

introduits au début des années 2000 par Cypress

C'est un circuit intégré qui comprend un microcontrôleur et des fonctions

logiques et analogiques configurables et interconnectables entre eux.

L'idée est de remplacer le microcontrôleur et les circuits d'interfaces analogiques

(convertisseurs AN et NA, filtres, amplificateurs opérationnels, etc..) ou

numériques (compteurs, timers, uart, interfaces pour bus divers, etc..) associés

par un circuit unique. On intègre ainsi un système électronique embarqué

complet dans un circuit intégré unique, ou tout au moins, on réduit très

considérablement le nombre de composants

Le PSoC est un circuit reconfigurable en fonctionnement : on peut par exemple

imaginer un système embarqué qui s'arrête de fonctionner 1 à 2 minutes par jour

pour se reconfigurer en modem et envoyer toutes les données qu'il a acquises

dans la journée. Les fonctions utilisées pour la mesure sont reconfigurées en

modem.

Hmaied Sarhene Page 1

Cours PSoC 2019/2020

1.2. Applications

Elles sont très variées ainsi que le montre ce document Cypress.

Hmaied Sarhene Page 2

Cours PSoC 2019/2020

1.3. Architecture d'un PSoC

Un PSoC est formé de :

-Un cœur Microcontrôleur8-bits, avec

• Mémoire Flash

• Oscillateurs internes (pas de quartz externe)

• Multiplieur/accumulateur

• Contrôleur d'interruptions, Sleep Timer, Watchdog Timer

• Contrôleur I2C

-Des blocs logiques et analogiques banalisés configurables

• Blocs logiques configurables en compteurs, timers, UARTs, PWMs, SPI,

générateurs CRC, séquences pseudo aléatoires, etc.

• Blocs analogiques configurables en amplis-op simples, comparateurs,

filtres, CNAs, CANs, modem, etc.

1.3.1. Mémoire Flash

-4K-32K octets

-architecture extensible à64K octets

-espace spécifique (ROM) en mode superviseur

Hmaied Sarhene Page 3

Cours PSoC 2019/2020

Mapping mémoire Flash

Protection mémoire Flash

•Protection par blocs de 64 octets

•4 niveaux de protection pour chaque bloc

–programmation, lecture externe, écriture interne autorisées

–programmation et écriture autorisées, lecture externe interdite

–écriture autorisée, programmation et lecture externe interdites

–programmation, écriture, lecture externe interdites

•Suppression de la protection par effacement complet du composant

1.3.2. Mémoire RAM

-Mémoire paginée, 1 page = 256 octets

-Jusqu'à 8 pages

-1-8 pages selon la famille

Mapping mémoire RAM

Hmaied Sarhene Page 4

Cours PSoC 2019/2020

1.3.3. Registres

-pour l'accès aux fonctions internes, aux blocs logiques/analogiques et aux

E/S

-deux bancs de 256registres

1.3.4. Oscillateurs et Horloges

Oscillateur interne principal

-Fréquence 48MHz

-Précision +/-2,5% sans composant externe

Hmaied Sarhene Page 5

Cours PSoC 2019/2020

-Peut être calé sur quartz externe 32KHz si haute précision nécessaire

Oscillateur interne basse fréquence

-Fréquence 32KHz

-Précision +/-20% sans composant externe (50% en mode veille)

-Peut être calé sur quartz externe 32KHz si haute précision nécessaire

Système d’horlogerie

•Fréquence principale = SYSCLK

*24 MHz si mode interne

*1 à 24 MHz si horloge externe

•Horloge CPU = division de SYSCLK

*8 divisions possibles, de 24/12MHz à 96KHz (mode int.)

•VC1 = division de SYSCLK (1 à16)

•VC2 = division de VC1 (1 à16)

•VC3 = division de VC1/VC2/SYSCLK/SYSCLK2 (1 à 256)

•SYSCLK, SYSCLK2, 32KHz, VC1, VC2, VC3 :

Horloges globales utilisables par les PSoC blocs

•Horloge Sleep Timer = division de 32KHz

*4 divisions possibles, de 512Hz à1Hz

Hmaied Sarhene Page 6

Cours PSoC 2019/2020

1.3.5. Entrées/Sorties

•Jusqu'à 5 ports 8 bits + 1 port 4 bits

•La fonction des broches E/S est paramétrable :

-Entrée et/ou Sortie standard (accessible en lecture et/ou en écriture dans

l'espace registre)

-Entrée et/ou Sortie globale (connexion aux PSoC Blocks numériques)

-Entrée et/ou Sortie analogique

•Mode de sortie paramétrable

-Strong (CMOS), Pull-up, Pull-down, High-Z, Open Drain

•Mode interruption configurable pour chaque broche

-Front montant, descendant, ou changement d'état

1.3.6. PSoC Blocks (exemple CY8C27xxx)

Les PSoC Blocks sont des blocs banalisés (8 blocs logiques et 12 blocs

analogiques) configurables par l'utilisateur

Hmaied Sarhene Page 7

Cours PSoC 2019/2020

Une fois configuré un PSoC Block devient capable de remplir une fonction

particulière, choisie dans une bibliothèque de Modules

Les Modules sont paramétrables par l'utilisateur, à l'initialisation aussi bien

qu'en fonctionnement

Les Modules sont fournis prêts à l'emploi, avec routines logicielles de

paramétrage et de contrôle (API)

La sélection, le paramétrage et l'interconnexion des Modules s'effectuent

graphiquement via le logiciel de développement

a- PSoC Blocks logiques

8 PSoC Blocks logiques, chacun constituant une 'tranche' de 8 bits

Chaque bloc est constitué de 3 registres Data et 4 registres de

configuration

2 types de blocs logiques

standard : pour toute fonction de type comptage, PWM, etc.

comm : idem + fonctions de transmission de type UART, SPI, etc.

Cascadables et interconnectables

Hmaied Sarhene Page 8

Cours PSoC 2019/2020

*Configuration des blocs logiques

*User Modules

•User Module = fonction constituée de un ou plusieurs PSoC Blocks

•Regroupés en bibliothèque, et fournis prêts à l'emploi (hardware/firmware)

•Modules logiques disponibles :

Timer 8, 16, 24, 32 bits

Counter 8, 16, 24, 32 bits

Pseudo random sequence generator8, 16, 24, 32 bits

PWM 8, 16 bit

PWMDB 8, 16 bit (PWM with dead band)

CRC16

UART (Receive, Transmit, Full Duplex)

SPI (Master, Slave)

Hmaied Sarhene Page 9

Cours PSoC 2019/2020

I2C software (I2C hardware disponible en ressource standard)

IrDA (Receive, Transmit)

E2PROM (software)

LCD (software)

Exemple : Module 'Timer'

•Mesure de temps, capture d'événements, génération de baud rate, etc.

•Registre DR1 : Période

•Registre DR0 : Décompteur

•Registre DR2 : Capture

•Routines associées: Timer_write_period, Timer_enable_int, Timer_start,

Timer_write_captureval, Timer_read_period, Timer_stop, etc.

b-PSoC Blocks analogiques

•12 PSoC Blocks analogiques (4 colonnes)

•2 types :

- CT : Continuous Time

Fonctions simples : ampli op, PGA, comparateur

- SC : Switched Capacitors

Fonctions complexes : filtrage, conversion, etc.

Hmaied Sarhene Page 10

Cours PSoC 2019/2020

•Cascadables et interconnectables

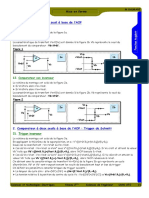

b-1-PSoC Blocks 'Continuous Time'

•Ampli-op configurables et paramétrables

•Réseau de résistances échelonnées (précision 2%)

•Référence paramétrable

Exemple : Comparateur

Hmaied Sarhene Page 11

Cours PSoC 2019/2020

b-2- Blocs 'Switched Cap'

Les résistances sont remplacées par des capacités et des switches

i = q/t = fs.q = fs.C.V

Or i=V/R donc R=1/fs.C

Hmaied Sarhene Page 12

Cours PSoC 2019/2020

Avantages des capacités commutées :

-Simplicité de réalisation sur process CMOS

-Contrôle du courant par la fréquence de commutation des switches

Exemple : Ampli non inverseur

Remarques: Il existe deux types de bloc 'Switched Cap'

•2 types: SCA et SCB

•Ampli-op programmables

•CAN incrémental et Δ−Σ

•CNA

•Filtres simples et biquad

– SCA : entrée biquad

– SCB : sortie biquad

Hmaied Sarhene Page 13

Cours PSoC 2019/2020

1.3.7. Convertisseur A/N

•Convertisseur Delta Sigma 8 bits

•1bloc analogique type SC

•1bloclogique (timer)

•Décimateur Hardware (diminue la charge du firmware)

•8 bit = 32 Kech/s

•11 bit = 7.8 Kech/s

Hmaied Sarhene Page 14

Cours PSoC 2019/2020

Exemple : Filtre passe-bas

•2 blocs SC (ordre 2)

•Paramètres programmables

–fréquence centrale (fc)

–Q

–gain

•300 Hz à 250 kHz

Hmaied Sarhene Page 15

Cours PSoC 2019/2020

1.3.8. User Modules analogiques (et mixtes)

•Modules analogiques et mixtes :

•Ampli simple, ampli différentiel, ampli inverseur, ampli à gain programmable

•Comparateur

•Convert. A/N : SAR, delta-sigma, incrémental, double/triple incrémental

•Convert. N/A : 6/9 bits, DAC multiplieur

•Filtres : passe-bas, passe-bande

•Multiplexeur analogique

•Générateur DTMF

•CapSense (détection capacitive)

Hmaied Sarhene Page 16

Cours PSoC 2019/2020

1.3.9. Fonctions combinées

1.4. Modèle de programmation

1.5. Jeu d'instructions

•1, 2 ou 3 octets, 4 à10 cycles/instruction (moyenne 6)

• Contrôle déroulement programme :

–CALL, LCALL, SSC, RET, RETI

–JMP, LJMP, JACC, JC, JNC, JZ, JNZ

–HALT, NOP

Hmaied Sarhene Page 17

Vous aimerez peut-être aussi

- CH 2 RESET Et Système Dhorloge RCCDocument52 pagesCH 2 RESET Et Système Dhorloge RCCCode CodeurPas encore d'évaluation

- Cours HTMLDocument84 pagesCours HTMLZidi NesimPas encore d'évaluation

- CH 1 Architecture Des Processeurs ARM Cortex M4Document55 pagesCH 1 Architecture Des Processeurs ARM Cortex M4Zidi Nesim100% (2)

- Exercice 1Document7 pagesExercice 1Zidi NesimPas encore d'évaluation

- 031-Cours Fonctionnement Chariot Elevateur PDFDocument20 pages031-Cours Fonctionnement Chariot Elevateur PDFIlyass Hani100% (1)

- 0068 Cours Balises HTMLDocument41 pages0068 Cours Balises HTMLSoltani AkRêmPas encore d'évaluation

- 2015 10 03 PHPDocument33 pages2015 10 03 PHPZidi NesimPas encore d'évaluation

- Orca Share Media1666035584999 6987859718307621107Document77 pagesOrca Share Media1666035584999 6987859718307621107Zidi NesimPas encore d'évaluation

- Epreuve N°01Document2 pagesEpreuve N°01Imprimerie AmnaPas encore d'évaluation

- Correction TDn°1Document6 pagesCorrection TDn°1Zidi NesimPas encore d'évaluation

- 2015 10 03 IntroductionDocument8 pages2015 10 03 IntroductionZidi NesimPas encore d'évaluation

- Guide Rapport PFE 2017-18Document10 pagesGuide Rapport PFE 2017-18Iñ SafPas encore d'évaluation

- 2015 10 03 IntroductionDocument8 pages2015 10 03 IntroductionZidi NesimPas encore d'évaluation

- Introduction Au HTMLDocument20 pagesIntroduction Au HTMLZidi NesimPas encore d'évaluation

- Guide Rapport PFE 2017-18Document10 pagesGuide Rapport PFE 2017-18Iñ SafPas encore d'évaluation

- Guide Rapport PFE 2017 18 (1) محولDocument10 pagesGuide Rapport PFE 2017 18 (1) محولZidi NesimPas encore d'évaluation

- Chap 2 GemmaDocument48 pagesChap 2 GemmaZidi NesimPas encore d'évaluation

- Rapport Perfectionnement - 2020Document15 pagesRapport Perfectionnement - 2020Zidi NesimPas encore d'évaluation

- Capteurs Position DeplacementDocument79 pagesCapteurs Position DeplacementzataraPas encore d'évaluation

- Chap 1 Grafcet AvancéeDocument36 pagesChap 1 Grafcet AvancéeZidi NesimPas encore d'évaluation

- Chap 1 Grafcet AvancéeDocument36 pagesChap 1 Grafcet AvancéeZidi NesimPas encore d'évaluation

- Charge DéchargeDocument1 pageCharge DéchargeZidi NesimPas encore d'évaluation

- Chap2psoc PDFDocument25 pagesChap2psoc PDFZidi NesimPas encore d'évaluation

- TravauxpratiquesdeFonctionsdElectroniquedeBase Benahmed FehamDocument27 pagesTravauxpratiquesdeFonctionsdElectroniquedeBase Benahmed Fehammêđ ŁïmãmêPas encore d'évaluation

- P642 PSL PDFDocument4 pagesP642 PSL PDFSofiane ChouPas encore d'évaluation

- Corrigé Partiel VHDL FPGA M1 ELN SE 2020Document6 pagesCorrigé Partiel VHDL FPGA M1 ELN SE 2020yasmine hmnPas encore d'évaluation

- Recepteur Radio CorrigeDocument8 pagesRecepteur Radio CorrigeKoukou Mita100% (1)

- Chapiter 4-1Document40 pagesChapiter 4-1ANAS ETTANANIAPas encore d'évaluation

- h3 - TC - Automatique - Qca 2003 2004 - Hei 33 34 - Qca Hei 33 34 - 1489Document2 pagesh3 - TC - Automatique - Qca 2003 2004 - Hei 33 34 - Qca Hei 33 34 - 1489Nabil LivePas encore d'évaluation

- Cours de Registres Num Riques 2015-2016Document28 pagesCours de Registres Num Riques 2015-2016leila settiPas encore d'évaluation

- Questions: La Boucle À Verrouillage de PhaseDocument5 pagesQuestions: La Boucle À Verrouillage de PhaseRadouan RemidiPas encore d'évaluation

- Cours E Logique Sequentielle Fonction MemorisationDocument14 pagesCours E Logique Sequentielle Fonction MemorisationMhammed ElhoussiniPas encore d'évaluation

- TP 02Document10 pagesTP 02ikram mbrPas encore d'évaluation

- Cours FpgaDocument24 pagesCours FpgaMouafek MARWANPas encore d'évaluation

- Upload - Série D'exercices N°4-3tech-Bascules-2013-2014-CorrectionDocument5 pagesUpload - Série D'exercices N°4-3tech-Bascules-2013-2014-CorrectionchediPas encore d'évaluation

- C4 SequentielleDocument82 pagesC4 SequentielleOumar MandodjoPas encore d'évaluation

- TD RevisionDocument2 pagesTD RevisionMãrÿ ŌûmåPas encore d'évaluation

- Neffati TAS Cours S A I OcrDocument23 pagesNeffati TAS Cours S A I OcrAntonio Saba0% (1)

- Résumé - Français - ASIC FPGA CPLD Course (Important)Document21 pagesRésumé - Français - ASIC FPGA CPLD Course (Important)hichemPas encore d'évaluation

- Rapport TP Conception Des Circuits Analogiques1Document33 pagesRapport TP Conception Des Circuits Analogiques1Hiba TANTAOUIPas encore d'évaluation

- Elex N°17 - Décembre 1989Document57 pagesElex N°17 - Décembre 1989didierpietquinPas encore d'évaluation

- MiseEnForme PDFDocument4 pagesMiseEnForme PDFŤå Ř Ïq100% (1)

- Multi Vibrate UrDocument8 pagesMulti Vibrate UrYounesHamoudiPas encore d'évaluation

- Additionneur Complet 1 BitDocument1 pageAdditionneur Complet 1 BitLi Jarmouni IIPas encore d'évaluation

- OscillateursDocument11 pagesOscillateursmaliPas encore d'évaluation

- E C Bascules D 3 Merged FAITDocument9 pagesE C Bascules D 3 Merged FAITMohamed MathématicienPas encore d'évaluation

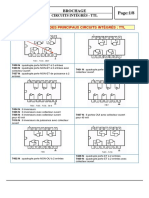

- Brochage Des Principaux CI-TTL PDFDocument8 pagesBrochage Des Principaux CI-TTL PDFFerjani Mohamed100% (1)

- TP CmosDocument32 pagesTP CmosInformatique Pour TousPas encore d'évaluation

- Série TD N°3 ELECT 21-22Document4 pagesSérie TD N°3 ELECT 21-22MAROUA BENALIPas encore d'évaluation

- Modulation AMDocument63 pagesModulation AMPape mbaye DiawPas encore d'évaluation

- TP3 Circuit LogiqueDocument17 pagesTP3 Circuit LogiqueoumarPas encore d'évaluation

- Logique Séquentielle Plan Système Combinatoire Système Séquentiel - PPT Video Online TéléchargerDocument15 pagesLogique Séquentielle Plan Système Combinatoire Système Séquentiel - PPT Video Online Téléchargerchaima chihiPas encore d'évaluation

- Amplificateur de MesureDocument9 pagesAmplificateur de MesureMohamed Amine TahiriPas encore d'évaluation