Académique Documents

Professionnel Documents

Culture Documents

NR 310503 Data Communication m04

Transféré par

MukeshTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

NR 310503 Data Communication m04

Transféré par

MukeshDroits d'auteur :

Formats disponibles

Set No: Code No: NR-310503 III-B.Tech.

I-Semester Supplementary Examinations, May-2004 DATA COMMUNICATION (Common to Computer Science and Engineering, Computer Science and Information Technology and Computer Science and Systems Engineering) Time: 3 Hours Max. Marks: 80 Answer any FIVE questions All questions carry equal marks ---

1.

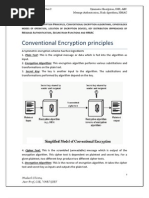

For the QPSK modulator shown in figure change the +900 phase shift network to 900 and construct the truth table, phasor diagram and constellation diagram. Explain its functioning.

I channel

fb /2

fb

logic 1=+1v

Input Buffer Bit Clock

1 0

+2 fb /2

I-Balanced +,- sinwct logic 0=-1v Modulator Reference sinwct Carier Oscillator 900 phase Linear QPSK sinwct shift Summer BPF output

logic 1=+1v

logic 0=-1v Q-Balanced Q channel fb /2 Modulator Fig. 2. 3.a) b) 4.a) b) c) 5. 6.

+,-coswct

Explain the standard used for the DTE-DCE interface in communication world. What is the relationship between the size of the CRC remainder and the divisor? Discuss the limitations of RS-232? Why must modems be used in pairs? How does a modem combine many concepts of communications? What are the functions of a transmitting modem and receiving modem? Explain the different phases of the operation of bisync protocol. Contrast the Band Width consideration, clock recovery capabilities, error detection and decoding capabilities of RZ and NRZ transmission. Draw the block diagram of DUV network and explain. Explain how lost data can be recovered if a message is corrupted by noise? Explain the mechanism of polling a remote terminal? ^^^

7. 8.

Code No: NR-310503 III-B.Tech. I-Semester Supplementary Examinations, May-2004

Set No:

DATA COMMUNICATION (Common to Computer Science and Engineering, Computer Science and Information Technology and Computer Science and Systems Engineering) Time: 3 Hours Max. Marks: 80 Answer any FIVE questions All questions carry equal marks ---

1. For the QPSK modulator shown in figure change the reference Oscillator to coswct and construct the truth table, phasor diagram and constellation diagram. Explain its functioning.

I channel

fb /2

fb

logic 1=+1v

Input Buffer Bit Clock

1 0

+2 fb /2

I-Balanced +,- sinwct logic 0=-1v Modulator Reference sinwct Carier Oscillator 900 phase Linear QPSK sinwct shift Summer BPF output

logic 1=+1v

logic 0=-1v Q-Balanced Q channel fb /2 Modulator Fig. 2. 3.a) b) 4.a) b) c) 5. 6.

+,-coswct

Explain the operation of different codes used in data communication. Write short notes on portable terminals. What are the steps required for synchronization? How does a current loop of interface differ fundamentally from a voltage interface? What is a key advantage and disadvantage of a current loop interface compared to a voltage interface? Is multi drop the same as multiplexer? Explain the similarities and differences. Give comparison between BISYNC, SDLC, and HDLC protocols. Describe FDM and explain with block diagram one application for FDM. (Contd..2)

Code No: NR-310503 7. 8.

-2-

Set No:2

Explain how data transmission will take place in PO systems. Explain a) Message waiting and b) polite selection for handling unsolicited messages in a half duplex multi point scenario?

^^^

Code No: NR-310503 III-B.Tech. I-Semester Supplementary Examinations, May-2004

Set No:

DATA COMMUNICATION (Common to Computer Science and Engineering, Computer Science and Information Technology and Computer Science and Systems Engineering) Time: 3 Hours Max. Marks: 80 Answer any FIVE questions All questions carry equal marks --1.a) b)

Explain (i) quadbit (ii) QAM Write the simplified block diagram of a differential binary PSK (DBPSK) modulator. Define topology in data communication. Explain the importance of asynchronous transmission in communication. Write the comparison between asynchronous and synchronous data transmission. What is the purpose of a null modem? The Lucky Ducky corporation has a fully connected ring network consisting of eight devices. Calculate the total number of cable links needed. What is the maximum number of information frames that can be sent before acknowledgement is required with SDLC. Explain with a block diagram the AT&Ts FDM hierarchy. Differentiate between DUV, DAV, DAVID and DIV clearly. What are the drawbacks of a half duplex block by block transmission system? How are they solved using full duplex circuits and without waiting for acknowledgements?

2. 3.a) b) 4.a) b)

5.

6. 7. 8.

^^^

Code No: NR-310503 III-B.Tech. I-Semester Supplementary Examinations, May-2004

Set No:

DATA COMMUNICATION (Common to Computer Science and Engineering, Computer Science and Information Technology and Computer Science and Systems Engineering) Time: 3 Hours Max. Marks: 80 Answer any FIVE questions All questions carry equal marks --1.

Write the block diagram, bit alignment diagrams and constellation diagram for the offset keyed QPSK (OQPSK). Explain its working. What are the disadvantages of ring topology? Describe how error correction takes place using Hamming code. What are the features of USART? Explain the function of RS 232 in detail. Explain the link access procedures in HDLC. Explain in detail the various types of T carrrier systems. Explain about Data Under Voice. What are Line protocols? Explain half duplex and full duplex point to point message transmission and compare them?

2. 3.a) b) 4. 5. 6. 7. 8.

^^^

Vous aimerez peut-être aussi

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5794)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- Servlets NotesDocument18 pagesServlets NotesMukesh100% (8)

- Cisco Introduction To Cyber Security Chap-1Document9 pagesCisco Introduction To Cyber Security Chap-1Mukesh80% (5)

- Assymetric Cryptography, Kerberos, X.509 CertificatesDocument34 pagesAssymetric Cryptography, Kerberos, X.509 CertificatesMukesh80% (5)

- Operating Systems: Files Concept & Implementing File SystemsDocument27 pagesOperating Systems: Files Concept & Implementing File SystemsMukesh88% (48)

- European Foundation Design For Seasonally Frozen GroundDocument127 pagesEuropean Foundation Design For Seasonally Frozen GroundLevente SikoPas encore d'évaluation

- Multicasting and Multicast ProtocolsDocument50 pagesMulticasting and Multicast ProtocolsMukeshPas encore d'évaluation

- MC (Unit-7) MANET'sDocument23 pagesMC (Unit-7) MANET'sMukesh93% (42)

- Advanced Numerical Modelling of Geogrids and Steel Wire Meshes - Daniele TubertiniDocument94 pagesAdvanced Numerical Modelling of Geogrids and Steel Wire Meshes - Daniele TubertiniSze Mian KuehPas encore d'évaluation

- Cisco Introduction To Cyber Security Chap-4Document9 pagesCisco Introduction To Cyber Security Chap-4MukeshPas encore d'évaluation

- Bridge Erection MachinesDocument73 pagesBridge Erection Machinesstavros_sterg80% (5)

- Cisco Introduction To Cyber Security Chap-2Document9 pagesCisco Introduction To Cyber Security Chap-2MukeshPas encore d'évaluation

- Simulation & Role PlayDocument10 pagesSimulation & Role Playpreeti sharma100% (2)

- Unicast Routing Protocols - RIP, OSPF and BGPDocument48 pagesUnicast Routing Protocols - RIP, OSPF and BGPMukesh100% (1)

- JSP NotesDocument35 pagesJSP NotesMukesh71% (14)

- Transport Layer - MukeshDocument54 pagesTransport Layer - MukeshMukeshPas encore d'évaluation

- Symmetric Encryption, DES, AES, MAC, Hash Algorithms, HMACDocument76 pagesSymmetric Encryption, DES, AES, MAC, Hash Algorithms, HMACMukesh86% (7)

- Lesson PlanDocument11 pagesLesson PlanKim Gabrielle Del PuertoPas encore d'évaluation

- C79 Service Kits and Parts List: CAP179 - C79 Aug 2017 - Rev ADocument32 pagesC79 Service Kits and Parts List: CAP179 - C79 Aug 2017 - Rev Arobert100% (2)

- OS Process Synchronization, DeadlocksDocument30 pagesOS Process Synchronization, DeadlocksMukesh100% (4)

- Protocols and Reference Models - CCNAv7-1Document41 pagesProtocols and Reference Models - CCNAv7-1MukeshPas encore d'évaluation

- Basic Router and Switch Configuration - CCNAv7 Module 2Document36 pagesBasic Router and Switch Configuration - CCNAv7 Module 2MukeshPas encore d'évaluation

- Introduction To Networks - CCNAv7 Module-1Document42 pagesIntroduction To Networks - CCNAv7 Module-1Mukesh0% (1)

- Multimedia Data and ProtocolsDocument59 pagesMultimedia Data and ProtocolsMukesh100% (1)

- Deadlocks in Operating SystemsDocument37 pagesDeadlocks in Operating SystemsMukeshPas encore d'évaluation

- Next Generation IP - IPv6Document46 pagesNext Generation IP - IPv6Mukesh100% (1)

- Quality of ServiceDocument40 pagesQuality of ServiceMukeshPas encore d'évaluation

- Unicast Routing - MukeshDocument29 pagesUnicast Routing - MukeshMukeshPas encore d'évaluation

- Bluetooth, IEEE 802.11, WIMAXDocument30 pagesBluetooth, IEEE 802.11, WIMAXMukesh71% (7)

- Classsical Encryption Techniques MukeshDocument13 pagesClasssical Encryption Techniques MukeshMukeshPas encore d'évaluation

- Network Layer - IP - MukeshDocument19 pagesNetwork Layer - IP - MukeshMukesh100% (2)

- Introduction To SecurityDocument37 pagesIntroduction To SecurityMukeshPas encore d'évaluation

- Introduction To Networks, Reference ModelsDocument38 pagesIntroduction To Networks, Reference ModelsMukesh100% (2)

- Trusted Systems, Firewalls, Intrusion Detection SystemsDocument18 pagesTrusted Systems, Firewalls, Intrusion Detection SystemsMukesh100% (34)

- MVC & Struts NotesDocument6 pagesMVC & Struts NotesMukesh100% (1)

- Database Issues in Mobile ComputingDocument20 pagesDatabase Issues in Mobile ComputingMukesh90% (51)

- Operating Systems - DeadlocksDocument14 pagesOperating Systems - DeadlocksMukesh100% (3)

- UT Dallas Syllabus For Math3303.501.10f Taught by Phillip Kisunzu (pxk091000)Document7 pagesUT Dallas Syllabus For Math3303.501.10f Taught by Phillip Kisunzu (pxk091000)UT Dallas Provost's Technology GroupPas encore d'évaluation

- Activity On The Layers of The Earth 1Document1 pageActivity On The Layers of The Earth 1Ian MarianoPas encore d'évaluation

- Rack Interface Module 3500 20SDocument71 pagesRack Interface Module 3500 20SmaheshPas encore d'évaluation

- Viaje Del SolDocument3 pagesViaje Del SolJanella UmiehPas encore d'évaluation

- Competitive Analysis: Features: Smart IrrigationDocument2 pagesCompetitive Analysis: Features: Smart IrrigationRoseanne RamonPas encore d'évaluation

- Metaphor-Spatiality-Discourse - 10-11 July 2020 - Programme - FINALDocument6 pagesMetaphor-Spatiality-Discourse - 10-11 July 2020 - Programme - FINALkostyelPas encore d'évaluation

- Software Testing and Quality AssuranceDocument26 pagesSoftware Testing and Quality Assurancemanoj hPas encore d'évaluation

- Dr./Ar. Jocelyn A. Rivera-Lutap, Fuap, FriaDocument1 pageDr./Ar. Jocelyn A. Rivera-Lutap, Fuap, FriaShanaia BualPas encore d'évaluation

- 4naa7 4eeDocument2 pages4naa7 4eeDorottya HózsaPas encore d'évaluation

- Marc ChagallDocument3 pagesMarc ChagallAnaPas encore d'évaluation

- Liter Ature - 4A: Start ThinkingDocument2 pagesLiter Ature - 4A: Start ThinkingNour AlkaloutiPas encore d'évaluation

- ABB - Composite Station Post InsulatorsDocument6 pagesABB - Composite Station Post InsulatorsDominic SantiagoPas encore d'évaluation

- PMP Itto GuideDocument11 pagesPMP Itto GuideSocrates XavierPas encore d'évaluation

- Samsung 932GW PDFDocument72 pagesSamsung 932GW PDFSaidfa FaPas encore d'évaluation

- Academic Stress ScaleDocument3 pagesAcademic Stress Scaleteena jobPas encore d'évaluation

- AYLS Annual Report 2019 LampDocument136 pagesAYLS Annual Report 2019 LampHigh FourPas encore d'évaluation

- Antennas and Wave Propagation - Nov - 2015Document8 pagesAntennas and Wave Propagation - Nov - 2015Jyothi SamanthulaPas encore d'évaluation

- Pepperdine Resume Ico William Kong Updated BDocument1 pagePepperdine Resume Ico William Kong Updated Bapi-278946246Pas encore d'évaluation

- JRX118SP SpecsheetDocument2 pagesJRX118SP SpecsheetLuisPas encore d'évaluation

- Grade 4 SYLLABUS Check Point 1Document2 pagesGrade 4 SYLLABUS Check Point 1Muhammad HassaanPas encore d'évaluation

- Porphyry Tin Deposits in BoliviaDocument15 pagesPorphyry Tin Deposits in Boliviasebastian tiriraPas encore d'évaluation

- 13 y 14. Schletter-SingleFix-V-Data-SheetDocument3 pages13 y 14. Schletter-SingleFix-V-Data-SheetDiego Arana PuelloPas encore d'évaluation

- Chapter 1 Philosophical Perspective of The SelfDocument64 pagesChapter 1 Philosophical Perspective of The SelfSUSHI CASPEPas encore d'évaluation

- FLIGHT Punta Arenas - SantiagoDocument3 pagesFLIGHT Punta Arenas - SantiagoАртем ПичугинPas encore d'évaluation