Académique Documents

Professionnel Documents

Culture Documents

T2 Ejercicios

Transféré par

Hernan Ali LopezTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

T2 Ejercicios

Transféré par

Hernan Ali LopezDroits d'auteur :

Formats disponibles

Ejerciciostema2:CircuitosCombinacionales

TecnologadeComputadores,Ing.Informtica

Tema 2: Circuitos Combinacionales

1. Analizar el siguiente circuito indicando la expresin algebraica que implementa, la tabla de verdad correspondiente y la funcin lgica en sus dos formas cannicas

2. Expresar en forma de minterms las siguientes funciones: a)- F(c,b,a)= b)- F(d,c,b,a)=

cb cbacb

dbcba

3. Convertir la siguiente funcin a su primera forma normal F(a,b,c)= abcacabc

4. Simplificar por el mtodo de Karnaugh las siguientes funciones: a)- F(d,c,b,a) = b)- F(d,c,b,a) = c)- F(d,c,b,a) = d)- F(d,c,b,a) =

0,1,4 ,5,6,8,9,13 ,14 0,1,2,4 ,5,8,10 0,1,3,4,5,7,8,9,14 ,15 1,2,3,5,6,7,8,9,10,11,14

5. Simplificar la siguiente funcin por los mtodos conocidos: F(d,c,b,a)= 0,2,5,7,8,10,13,15

6. Disear un circuito compuesto por puertas lgicas AND y OR de cuatro entradas y dos salidas definido por las funciones siguientes:

DepartamentodeAutomtica.UniversidaddeAlcal Pgina1de6

Ejerciciostema2:CircuitosCombinacionales

TecnologadeComputadores,Ing.Informtica

a)- F1(d,c,b,a)= b)- F2(d,c,b,a)=

0,1,4,5,6,8,9,13 ,14 0,1,2 ,4,5,8,10,13,14

(misma que 4.a)

c)- Redisearlos con puertas NAND exclusivamente 7. Dado el siguiente diagrama de tiempos para las seales de entrada a,b y c, y la de salida F, Obtener la expresin lgica ms simple de F utilizando los diferentes mtodos de simplificacin conocidos.

a

b c

8. Disear un decodificador de tres entradas que permita representar en un display de 7 segmentos el valor en binario puro de dichas entradas. (Hacer la tabla de verdad, obtener la expresin en minterms/maxterms para cada segmento Fa, Fb..Fg-, simplificarlas y hacer los circuitos). 9. Disear un circuito que discrimine si una entrada de 4 bits representa o no un dgito BCD vlido 10. Disear un circuito que sume dos nmeros BCD natural y nos d el resultado en cdigo binario de 5 bits. Se pueden usar sumadores BCD, sumadores binarios de 4 bits y las puertas necesarias. 11. Dados dos nmeros naturales de dos bits cada uno A (a2 a1) y B (b2 b1) disear un sistema combinacional que obtenga el valor absoluto de la diferencia entre ellos |A-B|. 12. Disear un circuito que sume dos nmeros naturales de dos bits A (a2 a1) y B (b2 b1) proporcionando la salida en tres bits. 13. Disear un circuito que compare dos nmeros naturales de dos bits A (a2 a1) y B (b2 b1) y proporcione las siguientes salidas: a)- En funcin de las entradas A y B:

DepartamentodeAutomtica.UniversidaddeAlcal Pgina2de6

Ejerciciostema2:CircuitosCombinacionales

TecnologadeComputadores,Ing.Informtica

S1 = 1 si A > B y 0 en cualquier otro caso S2 = 1 si A = B y 0 en cualquier otro caso S3 = 1 si A < B y 0 en cualquier otro caso b)- Como una variante al diseo anterior, obtener S2 a partir de S1 y S3 14. Utilizando multiplexores y las puertas lgicas necesarias integrar los circuitos diseados anteriormente en un nico circuito combinacional: este ha de tener igualmente dos entradas A (a2 a1) y B (b2 b1), y 3 salidas (S3, S2 y S1) de datos pero adems tendr dos entradas de control C2 C1 que debern seleccionar el tipo de funcionamiento del circuito: si C2 =0 y C1 = 0 --> las salidas S = 111 si C2 =1 y C1 = 0 --> las salidas mostrarn la suma de A y B (circuito ya diseado en un problema anterior) si C2 =0 y C1 = 1 --> las salidas mostrarn la comparacin de A y B (circuito ya diseado en un problema anterior) si C2 =1 y C1 = 1 --> las salidas S = 000 15. Disear mediante puertas lgicas un circuito que tenga por entrada un nmero binario de 4 bits X (d,c,b,a) que realice las siguientes operaciones de salida: si X>9, se activa una lnea de salida S1 que enciende una luz roja si X<9, se activa una lnea de salida S2 que enciende una luz verde si X=9, se activa una lnea de salida S3 que enciende una luz mbar 16. Realizar un circuito que ante una entrada de 8 bits indique si esta informacin tiene paridad par o impar. 17. Un embalse de una presa que se est llenando de agua dispone de 4 sensores de nivel n0 a n3. La salida de cada sensor vale 1 o 0 segn est o no cubierto por agua. Las salidas de los sensores estn conectadas a un circuito combinacional que codifica el nivel del agua como un nmero de 2 bits X (x1, x0). Otra salida denominada V solo vale 1 cuando todos los sensores indican que la presa est vaca, en cuyo caso el valor de X no importa. Se pide a)- Escribir la tabla de la verdad de las funciones x1, x0 y V b)- Obtener expresiones simplificadas para estas salidas c)- Implementar la funcin V con puertas NAND 18. Identificar las puertas P1 y P2 sabiendo que el circuito propuesto es un sumador completo. Las entradas E1 y E2 representan los bits a sumar y

DepartamentodeAutomtica.UniversidaddeAlcal Pgina3de6

Ejerciciostema2:CircuitosCombinacionales

TecnologadeComputadores,Ing.Informtica

CENT es el acarreo procedente de la etapa anterior. Las salidas son S que corresponde al bit de suma y C SAL al acarreo de la etapa actual. Razonar la respuesta

19. A partir de comparadores 7485 de nmeros de 4 bits, realizar un comprador de magnitudes de 32 bits. 20. Dados dos decodificadores 3 a 8 como el de la figura, constryase un decodificador de 4 a 16.

21. Realizar un convertidor de cdigo BCD natural a un cdigo BCD con exceso a tres. a)- con puertas lgicas b)- con circuitos multiplexores 22. Construir un decodificador para visualizar nmeros binarios de 3 bits con un display 7 segmentos. 23. El bloque codificador de la figura es un circuito combinacional que realiza una codificacin de las seales de entrada (a,b,c) segn las ecuaciones siguientes:

c b a

x = b xor a

Codificador x = b xor a y = c xor b z=c

z y x

Decodificador

c b a

DepartamentodeAutomtica.UniversidaddeAlcal

Pgina4de6

Ejerciciostema2:CircuitosCombinacionales

TecnologadeComputadores,Ing.Informtica

y = c xor b z = c siendo c y z los bits ms significativos Se pide: a)- Obtener la salida del codificador b)- Disear el circuito decodificador de modo que permita obtener de nuevo el cdigo original 24. Un embalse de una presa que se est llenando de agua dispone de 4 sensores de nivel n0 a n3. La salida de cada sensor vale 1 o 0 segn est o no cubierto por agua. Las salidas de los sensores estn conectadas a un circuito combinacional que codifica el nivel del agua como un nmero de 2 bits X (x1, x0). Otra salida denominada V solo vale 1 cuando todos los sensores indican que la presa est vaca, en cuyo caso el valor de X no importa. Se pide a)- Escribir la tabla de la verdad de las funciones x1, x0 y V b)- Obtener expresiones simplificadas para estas salidas c)- Implementar la funcin V con puertas NAND 25. Un banco desea instalar un sistema de alarma dotado de sensores de proximidad por rayos infrarrojos. Existen dos zonas de seguridad X e Y y la alarma de seguridad debe dispararse cuando se active cualquiera de ellas. La zona X tiene 3 sensores. A, B y C, mientras que la zona Y tiene 4 sensores: D,E,F y G. Para evitar falsas alarmas producidas por el disparo aleatorio de algunaos sensores, el sistema activar cuando bien en la zona X o bien en la zona Y se activen al menos 2 sensores simutneamente. Disear el circuito de control con la funcin ms sencilla obtenida. redisear con puertas NOR nicamente.

DepartamentodeAutomtica.UniversidaddeAlcal

Pgina5de6

Ejerciciostema2:CircuitosCombinacionales

TecnologadeComputadores,Ing.Informtica

Ejercicios Leyes de de-Morgan.

Transformar mientras sea posible. 13579 AB C D EF

2- ABC D 4- A BC D EF 6- ABC 8 ABC D EF

ABC DFE ABC D E ABCD A BCD E

Ejercicios lgebra de Boole:

Reducir algebraicamente

Expresin Solucin

1-

AB A BC B BC A B A BC B BC A BCBD A BC CD [ AB C BD AB ] A BC A B C A B C A B C ABC AB C A B C A BC A B C AB AC A B C AB AC A B C

BAC AB BC CD BC A BC B AB C AC A B A B C A BC

2345678-

DepartamentodeAutomtica.UniversidaddeAlcal

Pgina6de6

Vous aimerez peut-être aussi

- Ejercicios DigitalesDocument7 pagesEjercicios DigitalesAlvaro SanchezPas encore d'évaluation

- Capitulo9 CircuitosLogicosDocument13 pagesCapitulo9 CircuitosLogicosRonald Requejo SamamePas encore d'évaluation

- Ejercicios de Puertas LogicasDocument2 pagesEjercicios de Puertas LogicasJhonny Choez Burgos100% (1)

- Boletin 2Document4 pagesBoletin 2Jose Teijeiro CruzPas encore d'évaluation

- Informe AluDocument8 pagesInforme AluDanielSaniPas encore d'évaluation

- 7 Dispositivos Integrados PDFDocument105 pages7 Dispositivos Integrados PDFcchristt2584Pas encore d'évaluation

- 6 Circuitos Combinacionales P ImprimirDocument36 pages6 Circuitos Combinacionales P ImprimirFabian AcostaPas encore d'évaluation

- Practica Calificada de Circuitos Digitales 01-02TDocument1 pagePractica Calificada de Circuitos Digitales 01-02TXavier PalaciosPas encore d'évaluation

- Ejercicios Primer Parcial Sistemas Digitales 2012-2Document4 pagesEjercicios Primer Parcial Sistemas Digitales 2012-2Leonard MoralesPas encore d'évaluation

- Capitulo 4 Codificadores FF MULT DEMUXDocument49 pagesCapitulo 4 Codificadores FF MULT DEMUXCarlos Fredy EcheverríaPas encore d'évaluation

- Guia IseDocument33 pagesGuia IseMiguel Lara NisttahuzPas encore d'évaluation

- ProyectosDocument8 pagesProyectosSantiago ArciniegasPas encore d'évaluation

- Actividades de CircuitosDocument1 pageActividades de CircuitosAndrea GarciaPas encore d'évaluation

- Laboratorio 006Document2 pagesLaboratorio 006JD GpPas encore d'évaluation

- Multiplex DemultiplexorDocument13 pagesMultiplex DemultiplexorSamn EddyPas encore d'évaluation

- Multiplexores y demultiplexores: introducción y aplicacionesDocument2 pagesMultiplexores y demultiplexores: introducción y aplicacionesOscarPillajoPas encore d'évaluation

- Decodificador 4:16 TTL 74154Document5 pagesDecodificador 4:16 TTL 74154Jose Jimenez OropezaPas encore d'évaluation

- Fase1 E5Document8 pagesFase1 E5Luis EdynPas encore d'évaluation

- Módulo ADC Del Pic16f877Document14 pagesMódulo ADC Del Pic16f877Roberto ArredondoPas encore d'évaluation

- Capitulo 6. Sistemas Secuenciales PDFDocument24 pagesCapitulo 6. Sistemas Secuenciales PDFEfra IbacetaPas encore d'évaluation

- Ejercicios de arreglos, matrices y registros en CDocument4 pagesEjercicios de arreglos, matrices y registros en CJose AlejandroPas encore d'évaluation

- Análisis Matemático II Campos EscalaresDocument37 pagesAnálisis Matemático II Campos EscalarespabloPas encore d'évaluation

- Lab 01 Informe FinalDocument18 pagesLab 01 Informe FinalAnonymous iGvZPKrPas encore d'évaluation

- Practica 2 PicoBlazeDocument24 pagesPractica 2 PicoBlazeAntonio David EscobarPas encore d'évaluation

- Circuitos Digitales 1 Informe 3Document39 pagesCircuitos Digitales 1 Informe 3Rasec MundoPas encore d'évaluation

- LABORATORIO 05 - 2 Contadores AsincronosDocument5 pagesLABORATORIO 05 - 2 Contadores AsincronosDarwin YoverdPas encore d'évaluation

- Suma en BCDDocument4 pagesSuma en BCDYamil Alberto Peña LoayzaPas encore d'évaluation

- PLDs CaracterizaciónDocument6 pagesPLDs CaracterizaciónMelanie Romero100% (1)

- Compuertas UniversalesDocument10 pagesCompuertas UniversalesFernandoPas encore d'évaluation

- Compuertas LógicasDocument8 pagesCompuertas LógicasEduardo RomeroPas encore d'évaluation

- Reloj DigitalDocument18 pagesReloj DigitalRuben PadillaPas encore d'évaluation

- Pract10 Lab DLDocument8 pagesPract10 Lab DLANDREA YANELLI GUTIERREZ GARCIAPas encore d'évaluation

- Practica de Laboratorio Introducción A SimulinkDocument6 pagesPractica de Laboratorio Introducción A SimulinkJordanSplitWairerPas encore d'évaluation

- Practica6 Organización y Arquitectura de ComputadorasDocument17 pagesPractica6 Organización y Arquitectura de ComputadorasEduardo RojasPas encore d'évaluation

- Exposicion de Compuertas NotDocument23 pagesExposicion de Compuertas Notanon_214264213100% (2)

- Max Plus IIDocument95 pagesMax Plus IIOmar Reyes Bacusoy100% (1)

- Diseño e Implementación de Un Multiplicador IterativoDocument9 pagesDiseño e Implementación de Un Multiplicador IterativoMarco TorresPas encore d'évaluation

- Laboratorio 8 DigitalDocument7 pagesLaboratorio 8 DigitalSebastian Miguel Cáceres HuamánPas encore d'évaluation

- Alexander Lagla Compuerta Logicas 4 ADocument9 pagesAlexander Lagla Compuerta Logicas 4 AAlexander LaglaPas encore d'évaluation

- Aplicaciones de Circuitos DigitalesDocument15 pagesAplicaciones de Circuitos DigitalesAlex Pomier AliagaPas encore d'évaluation

- Circuitos DigitalesDocument11 pagesCircuitos DigitalesShirley Beleño BarriosPas encore d'évaluation

- Análisis probabilístico proveedores chips LS-24Document4 pagesAnálisis probabilístico proveedores chips LS-24Carlos CaicedoPas encore d'évaluation

- Sesion 11Document18 pagesSesion 11Oso TedPas encore d'évaluation

- Lab 05 Circuitos Digitales UNMSMDocument7 pagesLab 05 Circuitos Digitales UNMSMBrandon RH ErickBraddPas encore d'évaluation

- Tema 6 Teclado Digital DecimalDocument4 pagesTema 6 Teclado Digital Decimal2mercedesPas encore d'évaluation

- Tema 5Document64 pagesTema 5Johanna ComettantPas encore d'évaluation

- E3Document3 pagesE3Linda Esmeralda Torres RiosPas encore d'évaluation

- Sesión de AprendizajeDocument2 pagesSesión de Aprendizajemtrc743707Pas encore d'évaluation

- Circuitos Logicos MsiDocument32 pagesCircuitos Logicos MsiAndrés ArbeláezPas encore d'évaluation

- Practica 10 Registro UniversalDocument7 pagesPractica 10 Registro UniversalJonathan DominguezPas encore d'évaluation

- Mapa de Karnaugh (Mapa K)Document6 pagesMapa de Karnaugh (Mapa K)CDSGPas encore d'évaluation

- Compuertas LógicasDocument15 pagesCompuertas LógicasAnonymous YYfNGjdPas encore d'évaluation

- Programación Lineal y No Lineal - Métodos Simplex, Lagrange y Khun-TuckerDocument75 pagesProgramación Lineal y No Lineal - Métodos Simplex, Lagrange y Khun-Tuckerengengeng1Pas encore d'évaluation

- Ej T3FtosDocument6 pagesEj T3Ftospete sajotPas encore d'évaluation

- En Word REPASO EX FINALDocument3 pagesEn Word REPASO EX FINALCriss-tian Eduardo Estupiñan VasquezPas encore d'évaluation

- Problemas Circuitos Combinacionales 0506Document6 pagesProblemas Circuitos Combinacionales 0506Abner Isaac RomeroPas encore d'évaluation

- Algebra BooleanaDocument9 pagesAlgebra Booleanavargasc7Pas encore d'évaluation

- ProblemasCircuitosCombinacionales 072012Document5 pagesProblemasCircuitosCombinacionales 072012Santiago GuallichicoPas encore d'évaluation

- Prácticas de redes de datos e industrialesD'EverandPrácticas de redes de datos e industrialesÉvaluation : 4 sur 5 étoiles4/5 (5)

- Métodos Matriciales para ingenieros con MATLABD'EverandMétodos Matriciales para ingenieros con MATLABÉvaluation : 5 sur 5 étoiles5/5 (1)

- Evolucion de La Productividad en MexicoDocument11 pagesEvolucion de La Productividad en MexicoObed PGPas encore d'évaluation

- Akron Green Road GasolinaDocument3 pagesAkron Green Road GasolinaSalvador BarraganPas encore d'évaluation

- Informe de Monitoreo de RiesgosDocument2 pagesInforme de Monitoreo de RiesgosClau CamposPas encore d'évaluation

- Formulario Declaración JuradaDocument1 pageFormulario Declaración JuradaPablo Pérez GarcíaPas encore d'évaluation

- Obligación de DarDocument32 pagesObligación de DarJimmy Joel Guevara CoralPas encore d'évaluation

- InformeServicioCasaVentaAlquiler40Document7 pagesInformeServicioCasaVentaAlquiler40GianfrancoVelazcoParaguayPas encore d'évaluation

- Control de Calidad FruverDocument3 pagesControl de Calidad FruverIng Oscar GómezPas encore d'évaluation

- El Agua en Las Obras de ConstrucciónDocument2 pagesEl Agua en Las Obras de ConstrucciónVale RojasPas encore d'évaluation

- Construcción de pista y vereda en ParamongaDocument20 pagesConstrucción de pista y vereda en ParamongaAnonymous mgbUMZOWMoPas encore d'évaluation

- Ley 10-91 del Colegio Dominicano de PeriodistasDocument8 pagesLey 10-91 del Colegio Dominicano de Periodistaspersonal2Pas encore d'évaluation

- Catalogo Tecnoweld PDFDocument124 pagesCatalogo Tecnoweld PDFCarlos AguacíaPas encore d'évaluation

- Factura electrónica servicio granalladoDocument1 pageFactura electrónica servicio granalladoJubert Angelo Ramos ParedesPas encore d'évaluation

- Ja 09037001Document25 pagesJa 09037001Cainán AlmagorPas encore d'évaluation

- Informe Cuadro de Mando OperativoDocument3 pagesInforme Cuadro de Mando OperativoJǝsu RodriguǝzPas encore d'évaluation

- Aji El Picante de Los Dioses-Jorge AstudilloDocument73 pagesAji El Picante de Los Dioses-Jorge AstudilloFreddy IturraldePas encore d'évaluation

- Estrategia Metodológica de Intervención en PandemiaDocument2 pagesEstrategia Metodológica de Intervención en PandemiaPAHOLA CALLE BLANCOPas encore d'évaluation

- SOLUCION DE PROBLEMAS Semana 6 Anaisis OrganizacionalDocument3 pagesSOLUCION DE PROBLEMAS Semana 6 Anaisis OrganizacionalJairo RiveraPas encore d'évaluation

- Tabla de Contenido Pensamiento Matemático 2 EncuadreDocument2 pagesTabla de Contenido Pensamiento Matemático 2 Encuadremeowoe2lPas encore d'évaluation

- Requisitos de RecursosDocument3 pagesRequisitos de RecursosJamin mite0% (2)

- Genesys 10SDocument8 pagesGenesys 10SDATA240% (1)

- Blockchain-Disrupción, Valor y SeguridadDocument48 pagesBlockchain-Disrupción, Valor y SeguridadJuan Carlos Gallardo SaavedraPas encore d'évaluation

- 2 Tarjeta MadreDocument4 pages2 Tarjeta MadreIcela BarralesPas encore d'évaluation

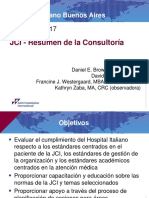

- Presentación Hospital Italiano Buenos Aires - JCI - 2017Document50 pagesPresentación Hospital Italiano Buenos Aires - JCI - 2017jorgebiolattoPas encore d'évaluation

- PDF 20230202 093443 0000Document4 pagesPDF 20230202 093443 0000Wilvana GutierrezPas encore d'évaluation

- Actividad Adicional m6Document4 pagesActividad Adicional m6Catalina Altamar CuervoPas encore d'évaluation

- Ejercicios Prácticos de Impuesto A La RentaDocument1 pageEjercicios Prácticos de Impuesto A La RentaJenny ARPas encore d'évaluation

- CP Hola AméricaDocument2 pagesCP Hola Américafzes2xpgPas encore d'évaluation

- Tarea Administración Financiera 3er C BTI 23-06-2023Document2 pagesTarea Administración Financiera 3er C BTI 23-06-2023Thiago FigueredoPas encore d'évaluation

- CUESTIONARIOSDocument5 pagesCUESTIONARIOSjavier erazoPas encore d'évaluation

- LEY 52 de Herencias VacantesDocument12 pagesLEY 52 de Herencias VacantesJocce RamiroPas encore d'évaluation