Académique Documents

Professionnel Documents

Culture Documents

Performance of Different Cmos Logic Styles For Low Power and High Speed

Transféré par

Anonymous e4UpOQEPTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Performance of Different Cmos Logic Styles For Low Power and High Speed

Transféré par

Anonymous e4UpOQEPDroits d'auteur :

Formats disponibles

International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.

2, June 2011

PERFORMANCE OF DIFFERENT CMOS LOGIC STYLES FOR LOW POWER AND HIGH SPEED

Sreenivasa Rao.Ijjada1, Ayyanna.G 2, G.Sekhar Reddy3, Dr.V.Malleswara Rao4

1 2 3 4

Department of ECE, GIT, GITAM University, Visakhapatnam, India

isnaidu2003@gmail.com

Department of ECE, GIT, GITAM University, Visakhapatnam, India

ayyanna.garaga@gmail.com

Department of ECE, GIT, GITAM University, Visakhapatnam, India

sekharreddy4187@gmail.com

Department of ECE, GIT, GITAM University, Visakhapatnam, India

mraoveera@yahoo.com

ABSTRACT

Designing high-speed low-power circuits with CMOS technology has been a major research problem for many years. Several logic families have been proposed and used to improve circuit performance beyond that of conventional static CMOS family. Fast circuit families are becoming attractive in deep submicron technologies since the performance benefits obtained from process scaling are decreasing as feature size decreases. This paper presents CMOS differential circuit families such as Dual rail domino logic and pseudo Nmos logic their delay and power variations in terms of adder design and logical design. Domino CMOS has become the prevailing logic family for high performance CMOS applications and it is extensively used in most state-of-the-art processors due to its high speed capabilities. The drawback of domino CMOS is that it provides only non-inverting functions because of its monotonic nature. Dual-Rail Domino logic, (also known as clocked Cascade voltage switch logic where both polarities of the output are generated, provides a robust solution to this problem.

KEYWORDS

Static CMOS Logic, Dual rail domino logic, pseudo nmos, Low power.

1. INTRODUCTION

VLSI designers have different options to reduce the power dissipation in the various design stages. For example, the supply voltage may be reduced through fabrication technology, circuit design or dynamically through the system level. Switched load capacitance may be reduced through technology scaling [10], efficient layout, circuit design, gate level optimization, and/or System level. This paper gives emphasis on low power design [2] aspect using some CMOS differential circuit families. In CMOS (Complementary Metal-Oxide Semiconductor) technology, both N-type and P-type transistors are used to realize logic functions. The static CMOS style [1] is really an extension of the static CMOS inverter to multiple inputs .Today, CMOS technology is the dominant semiconductor technology for microprocessors, memories and application specific integrated circuits (ASICs). The main advantage of CMOS over NMOS and bipolar technology is the much smaller power dissipation. Unlike NMOS or bipolar circuits, a CMOS circuit has almost no static power dissipation. Power is only dissipated in case the circuit actually switches. This allows to integrate many more CMOS gates on an IC The main principle behind CMOS circuits that allows them to implement logic gates is the use of p-type and n-type metaloxide semiconductor field-effect transistors to create paths to the output from either the voltage source

DOI : 10.5121/vlsic.2011.2206 66

International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.2, June 2011

or ground. When a path to output is created from the voltage source, the circuit is said to be pulled up. The other circuit state occurs when a path to output is created from ground and the output pulled down to the ground potential. Much of the research efforts of the past years in the area of digital electronics have been directed towards increasing the speed of digital systems. Recently, the requirement of portability and the moderate improvement in battery performance indicate that the power dissipation is one of the most critical design parameters [1]. The three most widely accepted metrics to measure the quality of a circuit or to compare various circuit styles are area, delay and power still demands high computational speeds. Hence, in recent VLSI systems the power-delay product becomes the most essential metric of performance.

2. STATIC CMOS LOGIC

The most widely used logic style is static complementary CMOS which consists of pull down

and pull up networks as shown in Fig 1.

Figure 1. Static cmos logic The static CMOS style is really an extension of the static CMOS inverter to multiple inputs.[1] In this static CMOS logic for an N-input logic gate, 2N-transistors are required which results in significantly large implementation area. Conventional static CMOS has been a technique of choice in most processor design. Alternatively, static pass transistor circuits have also been suggested for low-power applications [3] ,[12]. Dynamic circuits, when clocked carefully, can also be used in low-power high speed systems [4].

2.1. Static Adder

The Static CMOS logic adder design as shown in Fig 2 which consists of three input bits A, B, CIN, and has two outputs SUM and CARRY. Sum = a xor b xor cin Carry=ab + acin+ bcin A1 .A2

67

International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.2, June 2011

Figure 2. Static cmos adder

2.2. Static Logic

A static logic could be defined as a combinational circuit that performs the logical operations such has AND, NAND, XOR, XNOR. It consists of two inputs A and B and two outputs Fig 3 shows the logic level diagram of a static logic.

Figure 3. Static logic circuit

68

International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.2, June 2011

3. DUAL RAIL DOMINO ADDER

Domino CMOS has become the prevailing logic family for high performance CMOS applications and it is extensively used in most state-of-the-art processors due to its high speed capabilities [11].

3.1. Dual Rail Adder

Dual-Rail Domino Logic [5], [6], [8] is a pre-charged circuit technique which is used to improve the speed of CMOS circuits. A domino gate consists of a dynamic CMOS circuit followed by a static CMOS buffer. The dynamic circuit consists of a PMOSFET pre-charge transistor and an NMOSFET evaluation transistor with the clock signal (CLK) applied to their gate nodes, and an NMOSFET logic block which implements the required logic function. During the pre-charge phase (CLK = 0) the output node of the dynamic circuit is charged through the pre-charged PMOSFET transistor to the supply voltage level. The output of the static buffer is discharged to ground. During the evaluation phase (CLK = 1) the evaluation NMOSFET transistor is ON, and depending on the logic performed by the NMOSFET logic block, the output of the dynamic circuit is either discharged or it will stay pre-charged. Since in dynamic logic every output node must be pre-charged every clock cycle, some nodes are pre-charged only to be immediately discharged again as the node is evaluated, leading to higher switching power dissipation [1] ,[13]. One major advantage of the dynamic, pre-charged design styles over the static styles is that they eliminate the spurious transitions and the corresponding power dissipation. Also, dynamic logic does not suffers from short-circuit currents which in static circuits when a direct path from power supply to ground is caused. However, in dynamic circuits, additional power is dissipated by the distribution network and the drivers of the clock signal.

Figure 4. Dual rail adder The Dual rail adder design as shown in Fig 4 which consists of three input bits A, B, CIN, and has two outputs SUM and CARRY.

69

International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.2, June 2011

3.2. Dual Rail Logic

Dual rail domino logic [6] could be defined as a combinational circuit that performs the logical operations such has AND, NAND, XOR, XNOR. It consists of two inputs A and B and two outputs Fig 5 shows the logic level diagram of dual rail logic.

Figure 5. Dual rail logic

4. PSEUDO NMOS

4.1. Pseudo NMOS Adder

The design of a high-speed low-power I-bit full adder cell [7]. The main design objectives for this adder circuit are low power consumption and higher speed at low supply voltage. Using pseudoNMOS [7], [8] together with two inverters this adder cell has been designed in CMOS process. As shown in fig (6). Considering transistor chaining, grouping, and signal sequencing in our proposed adder layout which all have noticeable impacts on the circuit performance, shows substantial power saving and high speed improvement [9] at no area penalty. Inverters act as drivers. Therefore, each stage will not suffer degradation in its deriving capabilities. This saves power, area, and time.

Figure 6. Pseudo NMOS Adder

70

International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.2, June 2011

4.1. Pseudo NMOS Logic

Pseudo nmos logic [7], [8] could be defined as a combinational circuit that performs the logical operations such has AND, NAND, XOR, XNOR. It consists of two inputs A and B and two outputs Fig 7 shows the logic level diagram of pseudo NMOS logic.

Figure 7. Pseudo NMOS Logic

5. OBSERVATIONS

The following are the observations of delay and power of static CMOS logic in 45 nm process. Static cmos logic Delay(Ps) Sum Carry AND NAND XOR XNOR 442.18 540.12 202.23 198.23 239.34 276.54 Power(watts) 0.49 0.69 0.14 0.91 0.81 0.83

Table 1. Static CMOS Logic Observations The following are the observations of delay and power of Dual rail domino logic in 45 nm CMOS process

71

International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.2, June 2011

DUAL RAIL DOMINO LOGIC Delay(Ps) Sum Carry AND NAND XOR XNOR 543.45 298.3 192.3 209.5 275.6 299.8 Power(watts) 0.56 0.65 0.24 0.99 0.89 0.95

Table 2. Dual Rail Logic Observations The following are the observations of delay and power of Pseudo NMOS logic in 45 nm CMOS process PSEUDO NMOS LOGIC Delay(Ps) Sum Carry AND NAND XOR XNOR 343.14 272.32 182.15 175.53 225.6 262.8 Power(watts) 0.59 0.68 0.27 1.01 0.92 0.97

Table 3. Pseudo NMOS Logic Observations

5. SIMULATION RESULTS

5.1 The figure 6 shows static full adder sum and carry out puts.

Figure 6. Static sum and carry

72

International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.2, June 2011

5.2 The figure 7 shows static CMOS basic gates like AND, NAND, XOR and XNOR Out puts.

Figure 7. Static AND, NAND, XOR, XNOR 5.3 The figure 8 shows Full adder outputs by using Dual rail Domino Logic.

Figure 8. Dual Rail sum and carry 5.4 The figure 9 shows Dual rail Domino Logic basic gates like AND, NAND, XOR and XNOR Out puts

Figure 9. Dual Rail AND, NAND, XOR, XNOR

73

International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.2, June 2011

5.5 The figure 10 shows Full adder outputs by using Pseudo NMOS Logic

14tfa

45 v(C o ut ) 40 35

V o l ta g e ( m V )

30

25

20

15

10

-5 0 10 20 30 40 50 60 70 80 90 100

Ti m e (n s)

14tfa

v(s u m) 45

40

35

V o l ta g e ( m V )

30

25

20

15

10

-5 0 10 20 30 40 50 60 70 80 90 100

Ti m e (n s)

14tfa

9 00

v(C n ) i

8 00

7 00

V o l ta g e ( m V )

6 00

5 00

4 00

3 00

2 00

1 00

0 0 10 20 30 40 50 60 70 80 90 100

Ti m e (n s)

14tfa

9 00

v(B )

8 00

7 00

V o l ta g e ( m V )

6 00

5 00

4 00

3 00

2 00

1 00

0 0 10 20 30 40 50 60 70 80 90 100

Ti m e (n s)

14tfa

9 00

v(A )

8 00

7 00

V o l ta g e ( m V )

6 00

5 00

4 00

3 00

2 00

1 00

0 0 10 20 30 40 50 60 70 80 90 100

Ti m e (n s)

Figure 10. Pseudo NMOS sum and carry 5.6 The figure 11 shows Pseudo NMOS Logic basic gates like AND, NAND, XOR and XNOR Out puts

l ogi c

4 5 v( xn o r ) 4 0

V o lt a g e ( m V )

3 5

3 0

2 5

2 0

1 5

1 0

50

1 00

1 50

Ti m e (n s)

l ogi c

v( xo r ) 90 0

V o lt a g e ( m V )

85 0

80 0

75 0

70 0

65 0

60 0

50

1 00

1 50

Ti m e (n s)

l ogi c

90 0

v( na n d)

85 0

V o lt a g e ( m V )

80 0

75 0

70 0

65 0

60 0

50

1 00

1 50

Ti m e (n s)

l ogi c

v( an d )

4 0

V o lt a g e ( m V )

3 5

3 0

2 5

2 0

1 5

1 0

50

1 00

1 50

Ti m e (n s)

l ogi c

90 0

v ( B)

80 0

V o lt a g e ( m V )

70 0

60 0

50 0

40 0

30 0

20 0

10 0

50

1 00

1 50

Ti m e (n s)

l ogi c

90 0

v ( A)

80 0

V o lt a g e ( m V )

70 0

60 0

50 0

40 0

30 0

20 0

10 0

50

1 00

1 50

Ti m e (n s)

Figure 11. Pseudo NMOS AND, NAND, XOR, XNOR

6. CONCLUSION

In this paper we have implemented CMOS differential circuit families such as static CMOS logic, dual rail logic and pseudo NMOS logic which performs different arithmetic and logical operations. A comparison has been carried out between Static CMOS, Dual Rail Domino Logic and pseudo Nmos. In this thesis we have observed full adder sum and carry and also observed basic logic gates like AND, NAND, XOR & XNOR and also a 32-bit Arithmetic Logic Unit (ALU) has been designed & depending upon the Multiplexer selection the operations like ADDER, AND, NAND, XOR & XNOR has been performed along with this stimulation results were observed. In this paper among three logic the pseudo NMOS is low transistor count and high speed compared to static and dual rail logics.

74

International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.2, June 2011

REFERENCES

[1]

A. Chandrakasan, R.Brodersen, Low Power Digital CMOS circuits, Kiuwer Academic publishers, 1995. J.Rabaey, Digital Integrated Circuits, A Design Perspective, Prentice Hall, Upper Saddle River, NJ, 1996. K.Yano, Y.Sasaki, K.Rikino, K.Seki,TOP-DOWN PASS-TRANSISTER LOGIC DESIGN IEEE Journal of Solid-state Circuits, Vol.31, pp.792-803.1996. MIPS Technologies, R4200 TECHNOLOGIES Inc., 1994. MICROPROCESSOR Product Information, MIPS

[2]

[3]

[4]

[5]

R.Krambeck, C Lee, H Law, High-Speed Compact Circuit with CMOS, IEEE Journal of Solidstate Circuits, Vol 17, pp.614-619, 1982. V.Oklobdzija, R.Montoya, Design-performance Trade off in CMOS-Domino Logic, IEEE journal of Solid-state Circuit, vol21, pp.304-309, 1986. Amir Ali Khatibzadeh, Kaamran Raahemifar A 14-TRANSISTOR LOW POWER HIGH-SPEED FULL ADDER CELL. CCECE 2003 - CCGEI 2003, Montrhl, Maylmai 20030-7803-77818/03/$17.000 2003 lEEE. A Textbook Neil H.EWESTE and David HarrisCMOS VLSI DESIGN. A circuits and systems Perspective. I.Yuan, C.Svensson, High speed CMOS Circuit Technique, IEEE JSSC, vol. 24, No. 1, Feb 1989. S. Dutta, S. Nag, K. Roy, ASAP: A Transistor Sizing tool for speed, area, and power optimization of static CMOS circuits, IEEE International Symposium on Circuits and Systems, pp. 61-64, June, 1994. R. H. Crambeck High-speed Compact Circuit with CMOS, IEEE JSSC, vol. 17, lune 1982. A text book European low power initiative for electronic system design designing CMOS circuit for low power by Dimitrios soudries, Christian piguet, costas Goutis. Low-Power CMOS Digital DesignAnantha P. Chandrakasan, Samuel Sheng, and Robert W. Brodersen, Fellow, IEEE 0018-9200/92$03.00 0 1992 IEEE

[6]

[7]

[8]

[9] [10]

[11] [12]

[13]

75

International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.2, June 2011

AUTHORS 1)Sreeenivasa Rao.Ijjada received his AMIE degree from The Institution of Engineers (INDIA) in the year 2001 and received M.Tech degree in the year 2006 from J.N.T.U. Kakinada. He is a Ph.D Scholar and working in GITAM Institute of Technology, GITAM University, and Vishakhapatnam as an Assistant Professor. He is a life member of AMIE. His Research activities are related to Low Power VLSI Design. 2) Ayyanna Garaga received his B.Tech degree from JNTU Hyderabad in the Year 2007 and presently pursuing M.Tech in GITAM University. His research activities are related to Low power VLSI Design.

3) Sekhar Reddy Gaddam received his B.Tech degree from JNTU Hyderabad in the year2009 and presently pursuing M.Tech in GITAM University. His research activities are related to Low power VLSI Design.

4) Dr.V.Malleswara Rao received his B.E. degree from Andhra University In the year 1985 and received M.E. degree in the year 1985 from Andhra University and completed his Ph.D from J.N.T.U Hyderabad and working in GITAM Institute of Technology, GITAM University, Visakhapatnam as Professor and H.O.D. He is a life member of AMIE. His research activities are related to Low Power VLSI Design, Microwave, Bio-Signal processing.

76

Vous aimerez peut-être aussi

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryD'EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryÉvaluation : 3.5 sur 5 étoiles3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)D'EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Évaluation : 4.5 sur 5 étoiles4.5/5 (121)

- Grit: The Power of Passion and PerseveranceD'EverandGrit: The Power of Passion and PerseveranceÉvaluation : 4 sur 5 étoiles4/5 (588)

- Never Split the Difference: Negotiating As If Your Life Depended On ItD'EverandNever Split the Difference: Negotiating As If Your Life Depended On ItÉvaluation : 4.5 sur 5 étoiles4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingD'EverandThe Little Book of Hygge: Danish Secrets to Happy LivingÉvaluation : 3.5 sur 5 étoiles3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaD'EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaÉvaluation : 4.5 sur 5 étoiles4.5/5 (266)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeD'EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeÉvaluation : 4 sur 5 étoiles4/5 (5795)

- Her Body and Other Parties: StoriesD'EverandHer Body and Other Parties: StoriesÉvaluation : 4 sur 5 étoiles4/5 (821)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreD'EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreÉvaluation : 4 sur 5 étoiles4/5 (1091)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyD'EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyÉvaluation : 3.5 sur 5 étoiles3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersD'EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeD'EverandShoe Dog: A Memoir by the Creator of NikeÉvaluation : 4.5 sur 5 étoiles4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerD'EverandThe Emperor of All Maladies: A Biography of CancerÉvaluation : 4.5 sur 5 étoiles4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnD'EverandTeam of Rivals: The Political Genius of Abraham LincolnÉvaluation : 4.5 sur 5 étoiles4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceD'EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceÉvaluation : 4 sur 5 étoiles4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureD'EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureÉvaluation : 4.5 sur 5 étoiles4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealD'EverandOn Fire: The (Burning) Case for a Green New DealÉvaluation : 4 sur 5 étoiles4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)D'EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Évaluation : 4 sur 5 étoiles4/5 (98)

- The Unwinding: An Inner History of the New AmericaD'EverandThe Unwinding: An Inner History of the New AmericaÉvaluation : 4 sur 5 étoiles4/5 (45)

- AutotelephoneDocument220 pagesAutotelephonetamiresPas encore d'évaluation

- Effectron II Manual PDFDocument32 pagesEffectron II Manual PDFtelengard_t100% (2)

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- Mighty Macros and Powerful Parameters: Maximizing Efficiency and Flexibility in HDL ProgrammingDocument18 pagesMighty Macros and Powerful Parameters: Maximizing Efficiency and Flexibility in HDL ProgrammingAnonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI Design & Communication Systems (VLSICS)Document1 pageInternational Journal of VLSI Design & Communication Systems (VLSICS)Anonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSIdesign & Communication Systems (VLSICS)Document1 pageInternational Journal of VLSIdesign & Communication Systems (VLSICS)Anonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- Approximate Arithmetic Circuit Design For Error Resilient ApplicationsDocument16 pagesApproximate Arithmetic Circuit Design For Error Resilient ApplicationsAnonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- International Journal of VLSI DesignDocument1 pageInternational Journal of VLSI DesignAnonymous e4UpOQEPPas encore d'évaluation

- VSFC IdDocument58 pagesVSFC IdDhananjay NandanpawarPas encore d'évaluation

- PSP300 IntertekDocument6 pagesPSP300 IntertekJames Wayne BarkerPas encore d'évaluation

- Biographical Recount TextDocument1 pageBiographical Recount TextRafi DaffaPas encore d'évaluation

- Practice 1 PDFDocument8 pagesPractice 1 PDFadahrenellePas encore d'évaluation

- ART VPM FAQ Handbook Iss HDocument38 pagesART VPM FAQ Handbook Iss HAzwan ShahmeePas encore d'évaluation

- 08-13 1M801 - ENG72dpi PDFDocument6 pages08-13 1M801 - ENG72dpi PDFRuben Dario SolartePas encore d'évaluation

- CH 11 Section 1 Reading EssentialsDocument5 pagesCH 11 Section 1 Reading EssentialsCAMERON MIZEPas encore d'évaluation

- EnerSys Power Safe SBSDocument2 pagesEnerSys Power Safe SBSronychavesPas encore d'évaluation

- Coontrol Vit SalicruDocument16 pagesCoontrol Vit SalicruHugoPas encore d'évaluation

- Specifications: 5 SecondsDocument2 pagesSpecifications: 5 SecondsMohammed RPas encore d'évaluation

- Energy Efficiency and Enviromental CapabilitiesDocument136 pagesEnergy Efficiency and Enviromental CapabilitiesRadu GanciuPas encore d'évaluation

- Electrical Safety ONS 09 0 PR 4016 - R1Document21 pagesElectrical Safety ONS 09 0 PR 4016 - R1Ehsan YarmohammadiPas encore d'évaluation

- Type SG @su Auxiliary Relay: A Irii! P/IbuiDocument7 pagesType SG @su Auxiliary Relay: A Irii! P/IbuiImperial TranslationsPas encore d'évaluation

- VXR-7000 Om Eng Eu E13671108Document0 pageVXR-7000 Om Eng Eu E13671108Edinaldo GuimaraesPas encore d'évaluation

- Diagrama de Genius SP Hf1800aDocument16 pagesDiagrama de Genius SP Hf1800aИегҵ Гемассне100% (4)

- TASCAM MM-1 Keyboard MixerDocument33 pagesTASCAM MM-1 Keyboard MixerDanderman12375% (4)

- AMP2 S8 MDA - DDocument4 pagesAMP2 S8 MDA - DaboediartoPas encore d'évaluation

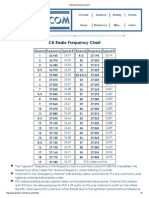

- CB Band Frequency Chart PDFDocument2 pagesCB Band Frequency Chart PDFdeyede2003Pas encore d'évaluation

- Filtros Murata LEADEDDocument16 pagesFiltros Murata LEADEDcbernal73Pas encore d'évaluation

- Panasonic SA-AK750GCPDocument106 pagesPanasonic SA-AK750GCPvasilemil100% (1)

- CBMA Curve Rev 2000Document3 pagesCBMA Curve Rev 2000dvaccarielloPas encore d'évaluation

- HSHV385K GTPDocument4 pagesHSHV385K GTPAkshita JainPas encore d'évaluation

- MC34262, MC33262 Power Factor ControllersDocument21 pagesMC34262, MC33262 Power Factor ControllersMaria VaccarielloPas encore d'évaluation

- VHF-Transceiver AR6201 - (XXX) : Installation and OperationDocument63 pagesVHF-Transceiver AR6201 - (XXX) : Installation and OperationJacquesSuirePas encore d'évaluation

- Ac70 SeriesDocument147 pagesAc70 SeriesNguyễn Đức SơnPas encore d'évaluation

- Announcements: - HW#10 Will Be Posted TonightDocument18 pagesAnnouncements: - HW#10 Will Be Posted TonightHarsha BalamPas encore d'évaluation

- Buck Converter Control For Lead Acid Battery ChargDocument9 pagesBuck Converter Control For Lead Acid Battery ChargS KhatibPas encore d'évaluation

- FINAL Lic MANUAL Studentcopy 1455085288190Document89 pagesFINAL Lic MANUAL Studentcopy 1455085288190Biswanath PatroPas encore d'évaluation