Académique Documents

Professionnel Documents

Culture Documents

N

N

Transféré par

Said Regani0 évaluation0% ont trouvé ce document utile (0 vote)

11 vues6 pagesTitre original

27540638_1715914831798624_8028986388649460606_n

Copyright

© © All Rights Reserved

Formats disponibles

PDF ou lisez en ligne sur Scribd

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF ou lisez en ligne sur Scribd

0 évaluation0% ont trouvé ce document utile (0 vote)

11 vues6 pagesN

N

Transféré par

Said ReganiDroits d'auteur :

© All Rights Reserved

Formats disponibles

Téléchargez comme PDF ou lisez en ligne sur Scribd

Vous êtes sur la page 1sur 6

Djilali Bowrwiainin Kh

ulté des sciences et de fa tech

Durée: OF henee

Epreuve dun]

Exereice 1:(6 points)

On veut modéliser un eireuit permettant de comparer 2 bus de données de 8 bits, A et By

et de générer 3 signauy de surtic :

EQUA si les données sur tes deux bus sont égales,

sup

ta doanée du bus A est supérieure & la donnée du bus By

INFE sila donnée du bus A est infériewre a la doanée du bus B,

A cCB sont des entrées du type std logic vecteur;

EQUA, SUPE, INFE sont des sorties de type std_logic ;

Ecrire Ventité de ee comparateur de § bits et coder Parchiteeture de ce motile,

Exercice 2:(7 points)

it lu description VHDL suivante:

entity exereive? Pi: process (4, f, sel)

port ( v1, x2, x3, sol: in std_ topic; begin

‘out std_ogie); ifset=10" then

end exercice2; yo d

architecture description of exerciee? is

signal a, by c,d, ¢, f: std_logies

begin

a <=Nxi or x2;

b<=x1 and x2;

ox x3 and iy

d<=bo

NE

te

rtir d°ééments de base le schéma eorrespon

1, Traces

il combinatuire ou séquentiel? Justificz.

2. Le processus PI est

”

3. Quel est selon vous ta fonction de ce ci

(7 points) (Interrogation)

re

On soubaite modiiser un additionncur complet 41 bit \ partir d'un composent demi

additionseur pour cel:

1. Donner le code vhdl d'un demi additionneur,

2, Utiliser ce composent pour donner le code vhdl d'un additionneur complet.

Bon courage

Exercies 1: Comparsteur

On veut modeliser un ciroul pemetian de compare: 2 bus G2 données de.6 bite, Alet

B, et de genérer 3 signaux de some:

EQUA si lee données sur les deux bus sont gales,

‘SUPE sila donnée du bus A esteupérieure a la donnée du bus 5,

INFE si ta donnée.du bus A est inferaure a la données du bus B,

Ae? B sontdes entrées du type sid_logic_vecteur,

EQUA, SUPE, INFE sont des sorties ce type std_logie ;

Eonre fentiée gece comparsteur de 8 pfs, et coder architecture de ce modéle.

forgcnen

Librasy ieee;

Ube )eee.ste_logie. 1 164.2

entity comparateurBolts 's port

(A, Bc in std_togie vector (7 downto o);

EQUA, SUPE, IMFE: oul sic_logich:

eid COmparateursbits,

architecture ARCH _comparateurébits of comparateursbits 's

Bagin

EQUAs='1' when A=B else "D5

SUPE<='1' when A> efse D,

INFE<="1" when A<6 aise 1

end ARCH_comparateuraalts;

Exerciced2 Correction

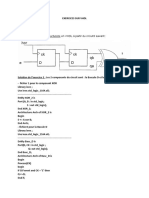

1- Le schéma correspondant

xl ———_»—

x2

a | atta

J p>—

2- C'est une description comportementale, puisqu'il n'y a aucune Composante.

sel

C'est un pracessus combinatoire car il inclut toutes les entrées (signaux lus) dans la

liste. de sensitivité. De plus. toutes les valeurs possibles de sel sont traitées.

3- C'est un plein additionneur avec multiplexage des sorties somme et retenue_

| |

pAb | | . | |

et anche

Vous aimerez peut-être aussi

- Liste Des Retenus ElectroniqueDocument18 pagesListe Des Retenus ElectroniqueSaid ReganiPas encore d'évaluation

- TD2 19Document3 pagesTD2 19Said ReganiPas encore d'évaluation

- Novelle STRDocument10 pagesNovelle STRSaid ReganiPas encore d'évaluation

- TD1 19corrDocument5 pagesTD1 19corrSaid ReganiPas encore d'évaluation

- CH 1Document4 pagesCH 1Said ReganiPas encore d'évaluation

- Exercice3 Sur VHDLDocument2 pagesExercice3 Sur VHDLSaid ReganiPas encore d'évaluation

- Rattrapage FabricationDocument2 pagesRattrapage FabricationSaid ReganiPas encore d'évaluation

- TD Octobre 2021Document21 pagesTD Octobre 2021Said ReganiPas encore d'évaluation

- Corrige TD1 - EXO5 - PLDsDocument1 pageCorrige TD1 - EXO5 - PLDsSaid ReganiPas encore d'évaluation

- Rapport Bibliographique Sur Les Particules Ultrafines (PUF) - 1Document29 pagesRapport Bibliographique Sur Les Particules Ultrafines (PUF) - 1Said ReganiPas encore d'évaluation

- Modèle Mémoire Master M2 2021Document21 pagesModèle Mémoire Master M2 2021Said ReganiPas encore d'évaluation

- Chapitre 3 DiodeDocument4 pagesChapitre 3 DiodeSaid ReganiPas encore d'évaluation

- Sources de RayonnementDocument7 pagesSources de RayonnementSaid ReganiPas encore d'évaluation

- Partie I: Vrai Ou Faux ? (Répondez Sur Cette Feuille) : TD2 en Vision ArtificielleDocument2 pagesPartie I: Vrai Ou Faux ? (Répondez Sur Cette Feuille) : TD2 en Vision ArtificielleSaid ReganiPas encore d'évaluation

- TP #03 Diode I 2018 2019Document6 pagesTP #03 Diode I 2018 2019Said ReganiPas encore d'évaluation

- Test TDDocument2 pagesTest TDSaid ReganiPas encore d'évaluation