Académique Documents

Professionnel Documents

Culture Documents

Eletrônica Digital 7

Transféré par

DeyviddasilvaCopyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Eletrônica Digital 7

Transféré par

DeyviddasilvaDroits d'auteur :

Formats disponibles

Memrias estticas - Introduo

Na pgina Eletrnica digital XI-10 pode ser visto que o valor da sada de um flip-flop (bloco bsico da lgica sequencial) pode ser mantido fixo ou ter alterao permitida pela entrada de clock. Isso sugere o uso de flip-flops em memrias, que so denominadas memrias estticas. Memrias estticas so de acesso aleatrio, mas no so em geral as conhecidas "RAM" encaixveis nas placas-me dos computadores. So mais usadas como cache (armazenamento temporrio) interno dos microprocessadores. So provavelmente as de menor tempo de acesso, mas a implementao exige um nmero relativamente elevado de componentes por bit armazenado. Nesta pgina, algumas informaes bsicas.

Porta E como elemento de habilitao

Este arranjo j existe em vrios circuitos de pginas anteriores, mas aqui dado um destaque por fazer parte importante dos circuitos das memrias estticas. Seja um circuito conforme (a) da Figura 01: uma entrada E, uma sada S e uma entrada de "liberao" ou "habilitao" H.

Fig 01 Pela tabela de verdade do bloco E, pode-se facilmente concluir que, se a entrada H 1, S=0 se E=0 e S=1 se E=1. Ou seja S = E. Em termos lgicos, como se a entrada estivesse diretamente conectada sada, como em (b) da figura. Se H=0, S sempre 0, independente do valor da entrada E. Em termos lgicos, como se a entrada E estivesse aberta e a sada S ligada a um potencial de nvel lgico zero. Ver (c) da referida figura. Resumindo, o circuito funciona como uma chave liga-desliga, com a particularidade de manter a sada nula na condio desligada.

Memria esttica elementar

A Figura 01 d o arranjo de um circuito de memria esttica do mais elementar possvel: memoriza apenas um bit de informao em um flip-flop tipo RS. A entrada END para endereamento. Para um bloco s, ela no faz muito sentido. Mas, num circuito real, com mais de um bloco, ela "conecta" ou "desconecta"

logicamente as entradas e sada do flip-flop com uso das portas ES, ER e EQ conforme tpico anterior.

Fig 01 D a entrada do bit de informao. O inversor faz com que as entradas S e R do flipflop s possam ser inversas, evitando estado impossvel do flip-flop RS (S=1 e R=1. Ver pgina Eletrnica digital XI-10 para mais informaes). L/E a entrada que define a operao da memria (leitura ou escrita). Usa a entrada de clock do flip-flop. A tabela a seguir d um resumo da operao do circuito. basicamente a operao de um flip-flop, que mantm ou muda o seu valor de acordo com o nvel da entrada de clock. END Status 1 L/E Operao Descrio Se a entrada de clock do flip-flop zero, o valor da Habilitado 0 Leitura sada no muda, quaisquer sejam os valores das entradas. Portanto, a sada O tem o valor memorizado. Se a entrada de clock um, o flip-flop pode mudar de Habilitado 1 Escrita estado. Portanto, a sada Q ser o valor que for aplicado em D. As portas E "isolam" o flip-flop e a sada O ser Desabilitado No h sempre 0 para quaisquer valores das entradas.

1 0

Para simplificar os diagramas, simboliza-se o circuito da Figura 01 como um nico bloco, de forma similar a outros blocos lgicos.

Fig 02 A Figura 02 exibe a disposio do bloco, isto , uma "clula" bsica de memria esttica, que armazena um nico bit de informao.

Memria de vrios bits

Uma memria de apenas um bit teria pouca utilidade prtica. A natural evoluo a associao de vrios blocos elementares do tpico anterior para formar dispositivos de maior capacidade. O nmero de bits que podem ser armazenados igual ao nmero de

blocos elementares. Por exemplo: para armazenar 4 bits, pode-se imaginar um circuito com 4 blocos elementares, uma sada para leitura, uma entrada de dado, uma entrada de controle leitura/escrita. Precisa-se ainda de um meio para selecionar (ou enderear) o bloco elementar (ou posio de memria) que se deseja operar (ler ou escrever). Essa seleo pode ser executada por um circuito gerador de produtos cannicos, do tipo usado em multiplex e demultiplex (ver pgina Eletrnica Digital XXXI-10 e seguintes para mais detalhes).

Fig 01 A Figura 01 d o diagrama bsico da memria esttica de 4 bits. Para cada combinao das entradas de endereo A e B, h somente uma nica sada de valor 1 no gerador de produtos cannicos. Isso ativa a respectiva clula ou posio de memria e mantm as demais inativas. Entrada A 0 0 1 1 Entrada B 0 1 0 1 Clula ativa 0 1 2 3

Assim, as entradas de endereo selecionam a posio de memria desejada e, para cada posio, as operaes de leitura e escrita ocorrem conforme tpico anterior. A porta OU na sada o elemento de unio das sadas de cada posio de memria. Desde que apenas a posio selecionada pode ser 0 ou 1 e as demais so sempre 0 (inativas), a sada da porta OU acompanha o valor da sada da posio selecionada (ou endereada).

Exemplo de memria de 16 bits

O circuito do tpico anterior permite construir memrias com quaisquer nmeros de bits, mas um arranjo em linha, que, no aspecto construtivo e eltrico, pode no ser o melhor.

O circuito da Figura 01 usa um gerador de produtos cannicos em forma de matriz, j visto na pgina Eletrnica Digital IV. Por razes de simplicidade, ele apresentado em duas partes e as linhas de interligao no so indicadas: (a) a matriz de produtos cannicos mencionada, de 16 sadas. (b) a correspondente matriz de 16 blocos elementares de memria.

Fig 01 Subentende-se que cada sada (1, 2, 3,..., 15) da matriz (a) est ligada a cada entrada (1, 2, 3, ..., 15) de endereo END da matriz (b). As sadas O de cada bloco elementar so ligadas entrada da porta OU para formar a sada nica, de modo idntico ao do circuito do tpico anterior. Tambm de forma similar, as entradas de leitura/escrita e de dados so unidas conforme indicado. Portanto, ele opera da mesma forma do circuito anterior, com 16 e no 4 bits. Apenas o arranjo fsico diferente. Exemplo: se A=1, B=1, C=1, D=0, o bloco 14 ativado, permitindo, nesse bloco, operaes de leitura ou escrita.

Vous aimerez peut-être aussi

- Simbologia DIN ISO 1219Document5 pagesSimbologia DIN ISO 1219Bruno LimaPas encore d'évaluation

- Memória RomDocument5 pagesMemória RomFranciscoPas encore d'évaluation

- Símbolos PneumáticosDocument4 pagesSímbolos PneumáticosAline Das SantasPas encore d'évaluation

- Procedimento de ComunicaçãoDocument24 pagesProcedimento de ComunicaçãoJorge Luiz Bastos FonsecaPas encore d'évaluation

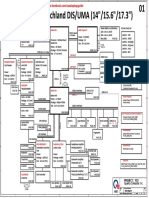

- HP Pavilion 15-p Quanta Y23 Y23a Vine Amd Richland Dis Uma (14'' 15.6'' 17.3'') Rev 1aDocument41 pagesHP Pavilion 15-p Quanta Y23 Y23a Vine Amd Richland Dis Uma (14'' 15.6'' 17.3'') Rev 1auzenhoPas encore d'évaluation

- Simbolos ISADocument15 pagesSimbolos ISAanon-484829100% (5)

- Eletrônica Digital 1Document3 pagesEletrônica Digital 1Deyviddasilva100% (1)

- Automação IndustrialDocument25 pagesAutomação IndustrialLeonardo MartinsPas encore d'évaluation

- Automação - Simbologia PneumaticaDocument18 pagesAutomação - Simbologia Pneumaticajuliano_automacaoPas encore d'évaluation

- Roteito para Trabalho EscolaresDocument2 pagesRoteito para Trabalho EscolaresDeyviddasilvaPas encore d'évaluation

- Eletrônica Digital 3Document5 pagesEletrônica Digital 3DeyviddasilvaPas encore d'évaluation

- Eletrônica Digital 12Document3 pagesEletrônica Digital 12DeyviddasilvaPas encore d'évaluation

- Eletrônica Digital 5Document4 pagesEletrônica Digital 5DeyviddasilvaPas encore d'évaluation

- Eletrônica Digital 2Document5 pagesEletrônica Digital 2DeyviddasilvaPas encore d'évaluation

- Eletrônica Digital 10Document4 pagesEletrônica Digital 10DeyviddasilvaPas encore d'évaluation

- Eletrônica Digital 6Document2 pagesEletrônica Digital 6DeyviddasilvaPas encore d'évaluation

- Eletrônica Digital 4Document5 pagesEletrônica Digital 4DeyviddasilvaPas encore d'évaluation

- Eletrônica Digital 8Document4 pagesEletrônica Digital 8DeyviddasilvaPas encore d'évaluation

- Eletrônica Digital 16Document3 pagesEletrônica Digital 16DeyviddasilvaPas encore d'évaluation

- Eletrônica Digital 9Document4 pagesEletrônica Digital 9DeyviddasilvaPas encore d'évaluation

- Eletrônica Digital 12Document3 pagesEletrônica Digital 12DeyviddasilvaPas encore d'évaluation

- Aula - 01 - Introduçao Metrologia - Grandezas Físicas (Modo de Compatibilidade)Document10 pagesAula - 01 - Introduçao Metrologia - Grandezas Físicas (Modo de Compatibilidade)DeyviddasilvaPas encore d'évaluation

- Eletrônica Digital 13Document3 pagesEletrônica Digital 13DeyviddasilvaPas encore d'évaluation

- Eletrônica Digital 14Document5 pagesEletrônica Digital 14DeyviddasilvaPas encore d'évaluation

- Aula - 01 - Introduçao Metrologia - Grandezas Físicas (Modo de Compatibilidade)Document10 pagesAula - 01 - Introduçao Metrologia - Grandezas Físicas (Modo de Compatibilidade)DeyviddasilvaPas encore d'évaluation

- Grade Integrada Revisada em 2009-09-25Document1 pageGrade Integrada Revisada em 2009-09-25DeyviddasilvaPas encore d'évaluation

- Eletrônica Digital 15Document3 pagesEletrônica Digital 15DeyviddasilvaPas encore d'évaluation

- Eletrônica Digital 17Document4 pagesEletrônica Digital 17DeyviddasilvaPas encore d'évaluation

- Eletrônica Digital 18Document6 pagesEletrônica Digital 18DeyviddasilvaPas encore d'évaluation

- Aula - 01 - Introduçao Metrologia - Grandezas Físicas (Modo de Compatibilidade)Document10 pagesAula - 01 - Introduçao Metrologia - Grandezas Físicas (Modo de Compatibilidade)DeyviddasilvaPas encore d'évaluation

- Aula - 01 - Introduçao Metrologia - Grandezas Físicas (Modo de Compatibilidade)Document10 pagesAula - 01 - Introduçao Metrologia - Grandezas Físicas (Modo de Compatibilidade)DeyviddasilvaPas encore d'évaluation

- Memórias SecundáriasDocument13 pagesMemórias SecundáriasTiago LeitePas encore d'évaluation

- Vocabulário Japonês - Computadores e Informatica - Suki DesuDocument21 pagesVocabulário Japonês - Computadores e Informatica - Suki DesuIsrael Gomes de LimaPas encore d'évaluation

- Plano de Curso Montagem e Manutenção de Micro e NotebooksDocument4 pagesPlano de Curso Montagem e Manutenção de Micro e NotebooksIgor FernandoPas encore d'évaluation

- UntitledDocument57 pagesUntitledSthefany RamalhoPas encore d'évaluation

- Painel digital para Buggy com Basic StampDocument7 pagesPainel digital para Buggy com Basic StampanglosaxaoPas encore d'évaluation

- Atps RedesDocument13 pagesAtps RedesAriel PereiraPas encore d'évaluation

- Gestão da manutenção com o SIGMADocument26 pagesGestão da manutenção com o SIGMAsmarts777Pas encore d'évaluation

- Artigo 01 Tecnologia CAD CAM Aplicada A Protese Dentaria e Sobre Implantes o Que e Como Funciona Vantagens e Limitacoes Revisao Critica Da LiteraturaDocument6 pagesArtigo 01 Tecnologia CAD CAM Aplicada A Protese Dentaria e Sobre Implantes o Que e Como Funciona Vantagens e Limitacoes Revisao Critica Da LiteraturaCamila Araújo100% (1)

- RecuperaDocument60 pagesRecuperaConseiller AbstraitePas encore d'évaluation

- Leila o 18189Document20 pagesLeila o 18189Jaime JustinianoPas encore d'évaluation

- Tutorial Emulador ZsnesDocument62 pagesTutorial Emulador ZsnesromeroeqPas encore d'évaluation

- Manual Rebonr PrimeiraDocument30 pagesManual Rebonr PrimeiraBruno DalfiorPas encore d'évaluation

- Tabela 19 03 12 UnicompDocument64 pagesTabela 19 03 12 UnicompGuilherme AntunesPas encore d'évaluation

- Printer history log entriesDocument63 pagesPrinter history log entriesAnonymous tAeYP07Pas encore d'évaluation

- Instalar Windows 7 via pen driveDocument76 pagesInstalar Windows 7 via pen driveDan RibeiroPas encore d'évaluation

- Optiplex-780 - Service Manual - PT-PT PDFDocument65 pagesOptiplex-780 - Service Manual - PT-PT PDFVanderlei Alves de OliveiraPas encore d'évaluation

- Asus M5a99x Evo Am3Document13 pagesAsus M5a99x Evo Am3Luiz OtavioPas encore d'évaluation

- Inventario Abril 2018 (3) VerificadoDocument46 pagesInventario Abril 2018 (3) VerificadoMaikon GarciaPas encore d'évaluation

- Controlador FE50RP: manual de operação otimizado paraDocument8 pagesControlador FE50RP: manual de operação otimizado paraFernando CarvalhoPas encore d'évaluation

- Exercícios Arquitetura2Document7 pagesExercícios Arquitetura2Luis Vitor MattosPas encore d'évaluation

- Inspiron 11 3168 2 in 1 Laptop - Setup Guide - PT BRDocument24 pagesInspiron 11 3168 2 in 1 Laptop - Setup Guide - PT BREstevam Gomes de AzevedoPas encore d'évaluation

- Porta ParalelaDocument32 pagesPorta ParalelaGilson Mendes SilvaPas encore d'évaluation

- 08gerencia de MemoriaDocument23 pages08gerencia de Memoriajoseamorim26Pas encore d'évaluation

- Configuração Da Bios - TudoDocument32 pagesConfiguração Da Bios - TudoEdgar ArturPas encore d'évaluation

- 05.2 - Arquitetura e Organização de Sistemas Computadorizados - Memória 1Document49 pages05.2 - Arquitetura e Organização de Sistemas Computadorizados - Memória 1Gabaritando - PreparatórioPas encore d'évaluation

- Manual A55 MobDocument47 pagesManual A55 Mob9tjj6275d6Pas encore d'évaluation

- Teclas BIOS NotebooksDocument3 pagesTeclas BIOS NotebooksJúniorPereiraPas encore d'évaluation