Académique Documents

Professionnel Documents

Culture Documents

Or, Xor and Not by Beginning With A Truth Table Organized As A K-Map and Assigning (S1, S0) Codes To AND, OR, Etc. S A B + S A B + S A B + S S A

Transféré par

Lini IckappanDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Or, Xor and Not by Beginning With A Truth Table Organized As A K-Map and Assigning (S1, S0) Codes To AND, OR, Etc. S A B + S A B + S A B + S S A

Transféré par

Lini IckappanDroits d'auteur :

Formats disponibles

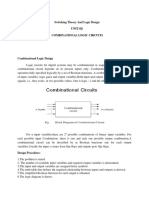

Arithmetic Logic Unit (ALU) In this and the next section, we deal with detailed design of typical ALUs

and shifters Decompose the ALU into: An arithmetic circuit A logic circuit A selector to pick between the two circuits

Arithmetic circuit design Decompose the arithmetic circuit into: An n-bit parallel adder A block of logic that selects four choices for the B input to the adder See next slide for diagram

Arithmetic Circuit Design (continued) There are only four functions of B to select as Y in G = A + Y: 0 B B 1

What functions are implemented with carry-in to the adder = 0? =1? Arithmetic Circuit Design (continued) Adding selection codes to the functions of B: The useful arithmetic functions are labeled in the table Note that all four functions of B produce at least one useful function Logic Circuit The text gives a circuit implemented using a multiplexer plus gates implementing: AND, OR, XOR and NOT Here we custom design a circuit for bit Gi by beginning with a truth table organized as a Kmap and assigning (S1, S0) codes to AND, OR, etc. Gi = S0 Ai Bi + S1 Ai Bi + S0 Ai Bi + S1 S0 Ai

Gate input count for MUX solution > 29 Gate input count for above circuit < 20 Custom design better Arithmetic Logic Unit (ALU) The custom circuit has interchanged the (S1,S0) codes for XOR and NOT compared to the MUX circuit. To preserve compatibility with the text, we use the MUX solution. Next, use the arithmetic circuit, the logic circuit, and a 2-way multiplexer to form the ALU. See the next slide for the bit slice diagram. The input connections to the arithmetic circuit and logic circuit have been been assigned to prepare for seamless addition of the shifter, keeping the selection codes for the combined ALU and the shifter at 4 bits: Carry-in Ci and Carry-out Ci+1 go between bits Ai and Bi are connected to both units A new signal S2 performs the arithmetic/logic selection The select signal entering the LSB of the arithmetic circuit, Cin, is connected to the least significant selection input for the logic circuit, S0. Arithmetic Logic Unit (ALU) (continued)

The next most significant select signals, S0 for the arithmetic circuit and S1 for the logic circuit, are wired together, completing the two select signals for the logic circuit. The remaining S1 completes the three select signals for the arithmetic circuit.

Vous aimerez peut-être aussi

- Lcdf3 Chap 10 p1Document29 pagesLcdf3 Chap 10 p1Ali AhmadPas encore d'évaluation

- 11 AluDocument23 pages11 AluPrasanth PrasePas encore d'évaluation

- Fun of DEDocument35 pagesFun of DETonmoy ChowdhuryPas encore d'évaluation

- Fundamentals of Electronics 2: Continuous-time Signals and SystemsD'EverandFundamentals of Electronics 2: Continuous-time Signals and SystemsPas encore d'évaluation

- Unit 3Document58 pagesUnit 3Anji ReddyPas encore d'évaluation

- STLD Unit IIIDocument29 pagesSTLD Unit IIIsnow54685Pas encore d'évaluation

- LOGCIRA113 Midterm Lecture 3 4 Combinational Logic Circuits Part 1 Arithmetic and Code Conversion CircuitsDocument44 pagesLOGCIRA113 Midterm Lecture 3 4 Combinational Logic Circuits Part 1 Arithmetic and Code Conversion CircuitsSento IsuzuPas encore d'évaluation

- Arithmetic OperationsDocument5 pagesArithmetic Operationspurvivaghela2003Pas encore d'évaluation

- DLD Unit 2 Combinational Circuits (2022)Document35 pagesDLD Unit 2 Combinational Circuits (2022)Hritik KaulPas encore d'évaluation

- Computer Architecture 7Document15 pagesComputer Architecture 7ARAFAT GaamanPas encore d'évaluation

- CO Unit - IIDocument45 pagesCO Unit - IISubathra Devi MourouganePas encore d'évaluation

- DLCA - Practical No 5Document8 pagesDLCA - Practical No 504 Tushar BhadrikePas encore d'évaluation

- Courses in Electrical Engineering: Digital Electronics Chapter Six: Combinatory LogicDocument29 pagesCourses in Electrical Engineering: Digital Electronics Chapter Six: Combinatory LogicNGOUNEPas encore d'évaluation

- DE Unit-4Document31 pagesDE Unit-4Dheeraj GoswamiPas encore d'évaluation

- Nusrath ImranaDocument13 pagesNusrath Imranafreefireboss633Pas encore d'évaluation

- Lab - ALUDocument3 pagesLab - ALUERICK BERNARDO TEQUIZ MERCHANPas encore d'évaluation

- ALUDocument7 pagesALUmonsour888Pas encore d'évaluation

- Combinational Logic Circuits: Computer ComponentsDocument7 pagesCombinational Logic Circuits: Computer ComponentsKumar Amit VermaPas encore d'évaluation

- Module 2 - DDCO 5Document58 pagesModule 2 - DDCO 5Sai SumanPas encore d'évaluation

- COEN 3103 Lesson 6 - 7 - Arithnetic and Logic Function CircuitsDocument68 pagesCOEN 3103 Lesson 6 - 7 - Arithnetic and Logic Function CircuitsAkosi LenaPas encore d'évaluation

- COE301 Lab 11 Datapath Component DesignDocument7 pagesCOE301 Lab 11 Datapath Component DesignItz Sami UddinPas encore d'évaluation

- Binary AddersDocument11 pagesBinary Addershassam qureshiPas encore d'évaluation

- Course Project: Topic: 8 Bit ALUDocument6 pagesCourse Project: Topic: 8 Bit ALUPruthvi PrakashaPas encore d'évaluation

- DDCO Module 2Document73 pagesDDCO Module 2begaxab741Pas encore d'évaluation

- Digital Electronics: C.H. Roth and L. L. Kinney, Fundamentals ofDocument31 pagesDigital Electronics: C.H. Roth and L. L. Kinney, Fundamentals ofSaumyaPas encore d'évaluation

- 34 Alu AssgDocument8 pages34 Alu AssgU are EdiTorPas encore d'évaluation

- Digital Design LAB Lab 5 Adder SubtractorDocument7 pagesDigital Design LAB Lab 5 Adder SubtractorWalied FarghalyPas encore d'évaluation

- 6 - Combinational CurcuitDocument38 pages6 - Combinational CurcuitPlay StorePas encore d'évaluation

- Adder and Subtractor Aim:: Block DiagramDocument10 pagesAdder and Subtractor Aim:: Block DiagramJaiom JoshiPas encore d'évaluation

- Unit 3Document34 pagesUnit 3Brooke DPas encore d'évaluation

- EE200 Experiment 07Document5 pagesEE200 Experiment 07xanxus2012Pas encore d'évaluation

- DPSD 20-21 Notes Unit-2Document84 pagesDPSD 20-21 Notes Unit-2Karthick Sivakumar ChellamuthuPas encore d'évaluation

- 2 Bit Full AdderDocument21 pages2 Bit Full AdderSilvestre VásquezPas encore d'évaluation

- 4CS015PortfolioTask1 90180Document4 pages4CS015PortfolioTask1 90180rahulshah23100Pas encore d'évaluation

- S.No Assignment Date Remarks 1. 2.: IndexDocument31 pagesS.No Assignment Date Remarks 1. 2.: IndexInstantPas encore d'évaluation

- STLD Unit - Iii (Original Notes)Document70 pagesSTLD Unit - Iii (Original Notes)Saipriya KadiyalaPas encore d'évaluation

- Adder-Subtracter: Digital Circuits Adding Subtracting BinaryDocument8 pagesAdder-Subtracter: Digital Circuits Adding Subtracting BinaryPathan SaifPas encore d'évaluation

- Coa Unit3Document116 pagesCoa Unit3tanay282004guptaPas encore d'évaluation

- Switching Theory Unit 2: By:Surbhi SarohaDocument58 pagesSwitching Theory Unit 2: By:Surbhi SarohaSonu Chauhan RajputPas encore d'évaluation

- Digital Design LaboratoryDocument10 pagesDigital Design Laboratorykarths22Pas encore d'évaluation

- Coa Question BankDocument97 pagesCoa Question BankSaiteja KandakatlaPas encore d'évaluation

- DPCO Unit 1Document45 pagesDPCO Unit 1Laks SadeeshPas encore d'évaluation

- Biteranta CsoworkDocument13 pagesBiteranta Csoworkapi-619829083Pas encore d'évaluation

- Digital PracticalDocument32 pagesDigital PracticalSaif Ali KhanPas encore d'évaluation

- Chapter 5 - Combinational Logic (EEEg4302)Document41 pagesChapter 5 - Combinational Logic (EEEg4302)Toli fiqeePas encore d'évaluation

- 3 Combinational CircuitDocument21 pages3 Combinational CircuitAKASH PALPas encore d'évaluation

- Rangkaian Logika: Materi Kuliah Ke-4Document7 pagesRangkaian Logika: Materi Kuliah Ke-4Jimran LeoPas encore d'évaluation

- Chapter 4 Combinational LogicDocument54 pagesChapter 4 Combinational LogicKaran RegmiPas encore d'évaluation

- Fig.2 Functional Representation of Arithmetic Logic UnitDocument7 pagesFig.2 Functional Representation of Arithmetic Logic Unitsamfear60Pas encore d'évaluation

- Analysis and Design ProcedureDocument31 pagesAnalysis and Design ProcedureMani Bharathi VPas encore d'évaluation

- Adder SubtractorDocument15 pagesAdder Subtractormellonera219Pas encore d'évaluation

- Unit 2Document88 pagesUnit 2Navjot Kaur MahiPas encore d'évaluation

- Combinational Logic CircuitsDocument17 pagesCombinational Logic CircuitsAdarsha Bhattarai100% (1)

- DD and COmodule 2Document97 pagesDD and COmodule 2Madhura N KPas encore d'évaluation

- DigitalDocument85 pagesDigitalRaghavan23100% (2)

- Arithmetic and Logic UnitDocument14 pagesArithmetic and Logic UnitVincent GaldoPas encore d'évaluation

- 10CS33 Logic Design NotesDocument14 pages10CS33 Logic Design Notesjgssb85Pas encore d'évaluation

- Final Exam Study GuideDocument2 pagesFinal Exam Study GuideLini IckappanPas encore d'évaluation

- 4Document42 pages4Lini IckappanPas encore d'évaluation

- Puter ScienceDocument12 pagesPuter ScienceGulzar IslamPas encore d'évaluation

- NreDocument22 pagesNreLini IckappanPas encore d'évaluation

- Splay Trees Are Binary Search Trees (BSTS) ThatDocument15 pagesSplay Trees Are Binary Search Trees (BSTS) ThatLini IckappanPas encore d'évaluation

- Introduction To Fuzzy Set TheoryDocument67 pagesIntroduction To Fuzzy Set TheoryLini IckappanPas encore d'évaluation

- 04 - A Fuzzy SystemDocument55 pages04 - A Fuzzy SystemLini IckappanPas encore d'évaluation

- Evaluation CriteriaDocument16 pagesEvaluation CriteriaLini IckappanPas encore d'évaluation

- Subprogram (Robert Text)Document109 pagesSubprogram (Robert Text)Lini IckappanPas encore d'évaluation

- The Design of Unix Operating System by Maurice J BachDocument486 pagesThe Design of Unix Operating System by Maurice J Bachrakeshpm100% (5)

- BindingDocument3 pagesBindingLini IckappanPas encore d'évaluation

- The Spaghetti DiagramDocument21 pagesThe Spaghetti DiagramBoamina Balondona AurelienPas encore d'évaluation

- Guarded CommandsDocument9 pagesGuarded CommandsLini IckappanPas encore d'évaluation

- PPL Module3Document8 pagesPPL Module3Lini IckappanPas encore d'évaluation

- PPL Module2Document9 pagesPPL Module2Lini IckappanPas encore d'évaluation

- Solving Problems by SearchingDocument47 pagesSolving Problems by SearchingLini IckappanPas encore d'évaluation

- PPL Module4Document11 pagesPPL Module4Lini IckappanPas encore d'évaluation

- Module 1Document45 pagesModule 1Lini IckappanPas encore d'évaluation

- PPL Module5Document9 pagesPPL Module5Lini IckappanPas encore d'évaluation

- PPL Module1Document8 pagesPPL Module1Lini IckappanPas encore d'évaluation

- PPL Module3Document8 pagesPPL Module3Lini IckappanPas encore d'évaluation

- Uniform Cost SearchDocument3 pagesUniform Cost SearchLini IckappanPas encore d'évaluation

- Constraint Satisfaction ProblemDocument5 pagesConstraint Satisfaction ProblemLini IckappanPas encore d'évaluation

- Module 3 - Wireless TechnologyDocument46 pagesModule 3 - Wireless TechnologyLini IckappanPas encore d'évaluation

- Introduction To AIDocument26 pagesIntroduction To AILini IckappanPas encore d'évaluation

- Algorithm: Depth First SearchDocument1 pageAlgorithm: Depth First SearchLini IckappanPas encore d'évaluation

- AI NotesDocument7 pagesAI NotesLini IckappanPas encore d'évaluation

- AI Problem CharacteristicsDocument1 pageAI Problem CharacteristicsLini IckappanPas encore d'évaluation

- AI ProblemsDocument46 pagesAI ProblemsLini IckappanPas encore d'évaluation

- Unit IiiDocument10 pagesUnit IiiLini IckappanPas encore d'évaluation

- CompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)D'EverandCompTIA Security+ All-in-One Exam Guide, Sixth Edition (Exam SY0-601)Évaluation : 5 sur 5 étoiles5/5 (1)

- Unlock Any Roku Device: Watch Shows, TV, & Download AppsD'EverandUnlock Any Roku Device: Watch Shows, TV, & Download AppsPas encore d'évaluation

- Computer Science: A Concise IntroductionD'EverandComputer Science: A Concise IntroductionÉvaluation : 4.5 sur 5 étoiles4.5/5 (14)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyD'EverandChip War: The Quest to Dominate the World's Most Critical TechnologyÉvaluation : 4.5 sur 5 étoiles4.5/5 (227)

- Chip War: The Fight for the World's Most Critical TechnologyD'EverandChip War: The Fight for the World's Most Critical TechnologyÉvaluation : 4.5 sur 5 étoiles4.5/5 (82)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102D'EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Évaluation : 5 sur 5 étoiles5/5 (2)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XD'EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XÉvaluation : 3 sur 5 étoiles3/5 (2)

- Hacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxD'EverandHacking With Linux 2020:A Complete Beginners Guide to the World of Hacking Using Linux - Explore the Methods and Tools of Ethical Hacking with LinuxPas encore d'évaluation

- Amazon Web Services (AWS) Interview Questions and AnswersD'EverandAmazon Web Services (AWS) Interview Questions and AnswersÉvaluation : 4.5 sur 5 étoiles4.5/5 (3)

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsD'EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsÉvaluation : 5 sur 5 étoiles5/5 (1)

- How to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideD'EverandHow to Jailbreak Roku: Unlock Roku, Roku Stick, Roku Ultra, Roku Express, Roku TV with Kodi Step by Step GuideÉvaluation : 1 sur 5 étoiles1/5 (1)

- Programming with STM32: Getting Started with the Nucleo Board and C/C++D'EverandProgramming with STM32: Getting Started with the Nucleo Board and C/C++Évaluation : 3.5 sur 5 étoiles3.5/5 (3)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]D'EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Évaluation : 5 sur 5 étoiles5/5 (1)

- CompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102D'EverandCompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Pas encore d'évaluation

- Patterns in the Machine: A Software Engineering Guide to Embedded DevelopmentD'EverandPatterns in the Machine: A Software Engineering Guide to Embedded DevelopmentÉvaluation : 5 sur 5 étoiles5/5 (1)

- Windows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertD'EverandWindows 10 Mastery: The Complete User Guide to Learn Windows 10 from Beginner to ExpertÉvaluation : 3.5 sur 5 étoiles3.5/5 (6)

- Amazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesD'EverandAmazon Echo Manual Guide : Top 30 Hacks And Secrets To Master Amazon Echo & Alexa For Beginners: The Blokehead Success SeriesPas encore d'évaluation

- CompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)D'EverandCompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Évaluation : 5 sur 5 étoiles5/5 (2)

- How To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsD'EverandHow To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsPas encore d'évaluation

- Raspberry Pi | 101: The Beginner’s Guide with Basics on Hardware, Software, Programming & ProjecD'EverandRaspberry Pi | 101: The Beginner’s Guide with Basics on Hardware, Software, Programming & ProjecPas encore d'évaluation

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-1-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1714737415?v=1)