Académique Documents

Professionnel Documents

Culture Documents

Buses

Transféré par

Paras GambhavaDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Buses

Transféré par

Paras GambhavaDroits d'auteur :

Formats disponibles

_.. __ _..... ----.

_-

INTERFACING PERIPHERALS (llb'S) AND 568

BUS INTERFACE STANDARDS

The microcomputer is a bus-oriented system whereby subsystems or peripherals are

interconnected through the bus architecture. The design approach should be such that

systems are modular, expandable, and multipurpose. For example, a microcomputer with

32K memory should be expandable to 64K memory without any design changes as the

user's needs change. The user should be able to select a peripheral from any manufacturer

and plug it into the system. Similarly, the user should be able to print out programs as well

as collect data from various instruments. To design microcomputers with such features,

a common understanding of equipment specifications among manufacturers is needed; this

is known as defining standards. In the field of electronics, these standards are generally

defillvu such as IEEE (Institute for Electrical and Electronics

Engineers); EIA (Electronic Industries Association), or the standards are forced upon the

industry either by a dominant manufacturer or by common practice. The need for expand

ability and modularity gave rise to various bus standards, as listed in Table 18.2. The bus

S-IOO, the Standard Bus, the Multibus, and the GPIB are described here, others were

described in Chapter 16.

".

TABLE 18.2

Bus Standards

Buses 110 Mode Applications/Descript.ion

I. S-100 Parallel To interconnect various components within the micro

(lEEE-696) computer. It has 100 signals.

2. STD Bus Parallel This is a bus competing with 5-100. It has 56 signals.

3. Multibus Parallel Interface between modules with the master/slave type com

(IEEE-796) munication. It has 86 signals.

4. OPIB Parallel Interface between the microcomputer and measurement

(IEEE-488) equipment such as a voltmeter. It has 24 signals.

5. RS-232 C Serial Interface between the microcomputer and serial peripherals

such as a terminal and a printer (see Chapter 16).

6. RS-422 and Serial High speed serial communication for distances longer than

RS-423 20 meters.

7. Current Loop Serial Interface with current operated peripherals such as Teletype

(see Chapter 16).

18.51 S-100 (IEEE 696') and Standard Bus

The primary force behind the development of these buses is their expandability. This type

of bus allows the user to plug in additional peripherals (including memory) without any

design changes and also facilitates troubleshooting. The bus design is based on the concept

of the "mother board," a printed circuit board with parallel foil strips. Several edge

connectors, connected to the foil strips, are included in a system, and some edge con

nectors are left empty for the user.

!LItATICNS

pherals are

e such that

nputer with

nges as the

anufacturer

ams as well

ch features,

needed; this

re generally

Electronics

ed upon the

for expand

U. The bus

others were

micro

signaL,.

ve type com

surement

lnals.

Oplo-Input

TRIAC

Relay

Drivers

Industrial 110 Peripheral

Interface

UART

Control Panel

CRT

Other

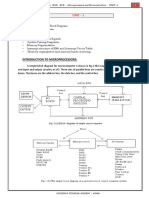

FIGURE 18.13

Bus Interface

II peripherals I

:r 16).

; longer than

:h as Teletype

r

lity. This type

I) without any

on the concept

Several edge

.me edge con-

TRENDS IN MICROPROCESSOR TECHNOLOGY AND BUS STANDARDS

BUS INTERFACE

The bus signals are divided into four groups, as shown in Figure 18.13: power, data,

address, and control. The S-I00 bus has 100 signals, and$he STD bus has 56 signals.

The 5-100 bus was originally developed by MITS and I ~ A S A I in 1975, even before

the existence of a 16-bit microprocessor. TI:te bus quickly becatne popular with hobbyists

and it became the de-facto industry standard. Initially, several lines were undefined,

causing contradictory uses by manufacturers. Eventually, IEEE adopted the S-loo, with

some modifications, as the IEEE-696 standard. This bus has 24 address lines, 16 data

lines, 11 interrupts, and provision for multiprocessing.

The STD bus was recently (l981),aeveloped by Pro-Log Corporation and MOSTEK,

as a simple bus structure for 8-bit microprocessors. It is a 56-pin bus with 8 data lines,

16 address lines, 22 control lines, and 10 power lines. It is a better-defined bus, an

improvement over the original 5-100 bus. However, the S-lCl() is so widely used that the

STD bus may have difficulty demonstrating its superiority to industry.

User's Interface

... ... u

.;:

<.J

.5! . ~

> >

...

0 ~ ~

]

~ ~

'00

OIl

Ci Ci

""

Ci

Processors Memory Digital 110

8085 RAM Input Ports

Z80 ROM Output Ports

8080A

Other

SOQRCE: courtesy of Pro-Log COlpoflltion, Monterey, Calif.

/

"

I

~

u ~ .

u

~

is

>

en

c

0Cl OIl

'0

.9

'"

c;;

c c

Analog 110

DACs

ADCs

570 INTERFACING PERIPHERALS (I/O'S) ANO APPLICATIONS

18,52 Multibus (IEEE 796)

The multibus is an 86-line (optionaI60-line) bus developed by Intel Corporation to connect

independent modules (or microcomputers) of various microprocessors to share. resources.

Each board can operate independently using its: own memory and 1I0s for dedicated

functions. They can access a system's resources such as a hard disk or printer through

the multibus.

The bus includes twenty address lines, sixteen bidirectional data lines, numerous

control lines, an(l multiple power and ground lines; the bus control can be managed by IC

dev,ces such as the Intel 8:?,18 or 8288. A multibus system can have many masters;

therefore, control logic is required for arbitration and data flow when multiple requests are

made to access the bus. Simultaneous requests to access the bus are handled through either

serial or parallel techniques by control signals.

18.53 GPIB Interface Bus (IEEE 488)

This bus was developed to facilitate interfacing of programmable instruments (such as

printers, digital voltmeters, and digital tape rec;orders) with computers. Initially, the bus

was developed by Hewlett-Packard; later, \it was accepted as the IEEE 488 Interface

Standard. The bus standard is also known as the General Purpose Interface Bus (GPIB)

or the Hewlett-Packard Interface Bus ( H P ~ I B ) . '

Some of the features of this bus are the following:

1. Data transfer among the interconnected devices is digital.

2. Fifteen devices may be connected to one continuous bus.

3. Total transmission path is limited to twenty meters or two meters per device.

4. Data rate on any signai line is limited to 1M-byte/sec.

BUS SIGNALS

The bus has 24 signals: eight bidirectional data lines, five general bus management lines,

three handshake lines, and eight grounds. Figure 18.14 shows four types of devices that

.'

,

,

can be connected to the bus. These devices are classified as follows:

1. Listener is a device capable of receiving data when addressed; fourteen devices can

listen at a time. Examples include printers and display devices.

2. Talker is a device capable of transmitting data when addressed; only one device can be

active at a time. Examples inciude tape readers and voltmeters.

3. Listener/Talker is a device that can receive as well as transmit data over the interface.

A programmable digital voltmeter (DVM) is a listener/talker device.

4. Controller is a device that controls signals and specifies which device can talk and

which device can listen. A microcomputer with an appropriate 110 card can serve as

a controller.

_. . .__ ... :ii_

T

D connect

I

esources.

dedicated

I

r through

numerous

ged by IC

. masters;

quests are

ugh either

I

5 (such as

y, the bus

. Interface

us (GPlB)

ment lines,

:evices that

,

"\

kvices can

vice can be

e interface.

an talk and

:an serve as

TRENDS IN MICROPROCEssoR TECHNOLOGY AND BUS STANDARDS 571

Hewlett-Packard Interface Bus S>

Device A Device B Device C Device 0

Able 10 Talk, .\ble 10 Talk Able 10 Lislen Able 10 Talk

Lislen and Conlrol and Listen Only Only

(e.g., calculator) (e.g., digital voltmeter) (e.g., signal generator) (e.g., tapc recorder)

I EO

REN

SRQ

III

II

/ ........ III

T

II

1

fi

I

f+

f-

f+

ATN

IFC '

./

f-

f-

NOAC

NRFD

DAY

(

\

\

)

f-

f

.. 8 010 I.

,

I

I

( )

General Bus Handshake

Management Lines

FIGURE 18.14

GPIB (IEEE 488) Bus Interface

SOURCE: Hewlett-Packard Company. TUlOrial Description oj the Hew/el/-Packard Imerface Bus (Palo Allo. Calif.: Authot,

1980), p. 8. teproduced with permission.

SU!v1MARY

In this chapter, various microprocessors - from S-bit to 32-bit - and single-chip

microcontrollers from the Intel family were discussed. compared, and contrasted in

terms of their characteri tics and appiications. Future trends in microprocessor tech

nology were suggested.

Eight-bit microprocessors contemporary to the 80S5/S080A were discllssed in

Section 18.1. These processors were classified primarily into two groups: register

oriented and memory-referenced. The Z80 and the NSCSOO appear to have combined

the best features of both the groups.

Single-chip microcomputers (also known as microcontrollers) and their applica

tions were discllssed in Section 18.2. These microcontrollers are specially designed to

be geared towards celtain applications, and their characteristics differ according to

their areas of application .

. Microprocessors with 16- and 32-bit words were discussed in Sections 18.3 and

18.4, respectively. They are designed to facilitate uses of high-level languages, and ill

expected to compete with mini- arid mainframe computers. New architectural concept.

such as memory segmentation, parallel processing, and queueing were employed in

designing some of these processors, and some are designed with a package larger

than 40 pins.

In addition, various bus standards were discussed.

(.,,:.(I!I{!" )l:!?It'

,/"

PLiCATIONS

I data

ror, go

:ounter and

Chapter II

4 x 4 key

rins; include

output ports

as complete

; difficult to

rouble spots,

o is built and

-should be

I system? An

rying to start

Jrking socket

>lved in these

tution. These

>cessor-based

imilar to the

:sources with

emulator, is

ystern of the

y, as software

em (discussed

d by using an

Iy changes the.

,re., to examine

)turing data in

I

relati0n to instructions. are requIred. Three such instruments are discussed..br-iepy in the.

next section: In-circuit Emulator, Logic State Analyzer, and Signature . '';.

17.21 In-Circuit Emulator

The in-circuit emulation technique has become an essential part of the desigiiprQces(.!or

microprocessor-based products. In-circuit emulation is the execution of:l

ware program in prototype hardware under the control of a software development

To perfonn an in-circuit emUlation, the microprocessor is removed from the

design board, and a 40-pin cable from an in-circuit emulator is plugged into th.e socket

previously occupied by the microprocessor. The in-circuit emulator perfonnsall the

functions of the replaced microprocessor; in addition, it allows the prototype hardware to

share all its resources, such as software, memory, and 1I0s. It provides a window for

looking inio th.:. ;;)",;-':-;:;.:; -" . ::r:-ratiol1 of the prototype hardware. At present, a

variety of in-circuit emulators are available, ranging from universal emulators

with complete software development systems to st:lnd-alone microprocessor units. Fig

ure 17.8(a) shows an universal in-circuit emulator (9508) manufactured by Gould Inc.; it

is designed to emulate various microprocessors with plug-in boards. Figure 17.8(b) shows

a stand-alone in-circu.t emulator (EM-18S) ciesigned by Advanced Micro Systems.

EMUI:ATION PROCESS

To test subsystems (such as i/O and memory) using an in-circuit emulator, the minimum

prototype hardware required is a 40-pin microprocessor '!:ocket, without the micro

processor, and a power supply. All other resources can be borrowed from the in-circuit

emulator. As more and more prototype hardware is built. fewer and fewer resources from

the in-circuit emulator will be required. In the final stage, total software and hardware are

integrated for testing. A hardware prototype can be viewed as a fetus growing in stages

in the womb of an in-circuit emulator; until the fetus is fully developed and functioning

independently, the in-circuit emulator provides the necessary environment and resources.

FEATURES OF IN-CIRCUIT EMULATOR

An in-circuit emulator is a softwarelhardware troubleshooting instrument. It can be a

stand-alone un.it or part of a software development system. A small program can be entered

directly into the emulator, or a program can be transferred into the emulator from a host

computer system through an RS-232 serial link. Once a program is loaded, a user can

interact with .the eplulator through its keyboard or a tenninal. The emulator has its own

commands to perform various debugging functions. The main capabilities of

3{l in-circuit emulator can be listed as follows:

o Downloading: Facilities to transfer programs between a software development system

or a host computer and the in-circuit emulator.

o .ResoUrce Sharing: The in-circuit emulator allows the system being tested to share its

memory arid 110 ports. The memory and 110 ports of the in-circuit emulator can be

assigtied any addresses, which will avoid conflict with memory and 1I0s of the proto

type; this is called memory and 110 mapping.

. . .' . .

) APPLlCA: at s

>tand-Alone

B: Photograph couI1esy

o Debugging Tools: Breakpoints

Mnemonic Display

Real-Time Trace

In-Line Assembly

Disassembly

Register Display/Modifications

DEBUGGING TOOLS

The debugging tools listed above are used in troubleshooting programs. Single-stepping

and setting breakpoints have already been discussed in Chapter 5. The others are briefly

discussed" below.

Real-Time Trace The in-circuit emu!ator hil;; R/W memory used as a buffer to store the

last several (such as 12iS) lV;;;"':v, .. 'ce displayed on the 'screen. The

display is like a snapshot of all the bus operations in real time. A typical display is shown

in Figure 17.9. The user can specify severa] requirements, such as a memory address

and certain data conditions for recognizing an event, in order to trigger and display a

trace. Similarly, a trace can be observed between two breakpoints or at a specified delay

after a certain event. The real-time trace is a valuable tool in debugging microprocessor

based products.

In-Line Assembly This allows the user to change data or instructions while the software

is ill. in-circuit emulator.

Disassembly After instructions are changed in the in-circuit emulator, this facility can

write mnemonics in software.

Register Display This displays the register contents after the execution of instructions.

17.22 Logic State Analyzer

The logic state analyzer, also known as the logic analyzer, is a multi trace digital oscil

loscope especially designed to use with microprocessor-related products. In a multitrace

scope, the timing relationships of severa! signals can be with respect to some

event or events. For example, a four-trace scope can show the timing re

latiooships of four signals. In a microprocessor-related product, the user is interested in

observing digital signals on the address bus. the data bus, the control bus and, possibly,

an external instrument relative to a specified triggering event or events. Furthermore, data

display should be in a conveniently readable format, such as Hex or binary. The logic

analyzer performs these functions.

A typical logic analyzer designed primarily to work with the microprocessor has a

40-pin probe plus an auxiliary probe to gather external information. It includes Read-Only

_" .ioL" _

Vous aimerez peut-être aussi

- IEEE-488: OriginsDocument8 pagesIEEE-488: OriginsDavid BusieneiPas encore d'évaluation

- Figure 1. IEEE-488 (HP-IB/GP-IB) Bus ConfigurationDocument3 pagesFigure 1. IEEE-488 (HP-IB/GP-IB) Bus ConfigurationabracadabraaaPas encore d'évaluation

- 006 I2C Bus ProtocolDocument16 pages006 I2C Bus Protocolcoolkunal77100% (1)

- Serial and Parallel CommunicationDocument21 pagesSerial and Parallel CommunicationHari KrishPas encore d'évaluation

- Tutorial Background: Fundamentals of Virtual Instruments Tradtional Instruments Virtual InstrumentsDocument17 pagesTutorial Background: Fundamentals of Virtual Instruments Tradtional Instruments Virtual InstrumentsMohammed JunedPas encore d'évaluation

- Assignment Set I (1) UpdateDocument15 pagesAssignment Set I (1) UpdateAshish OjhaPas encore d'évaluation

- Gpib and Ieee 488Document17 pagesGpib and Ieee 488communicationridersPas encore d'évaluation

- Serial Communication StandardsDocument5 pagesSerial Communication Standardsyagnasree_s100% (1)

- Embedded System SolveDocument15 pagesEmbedded System SolveAshish OjhaPas encore d'évaluation

- Communication InterfaceDocument36 pagesCommunication InterfaceAsante WilliamPas encore d'évaluation

- Es Notes Unit 3Document7 pagesEs Notes Unit 3Sai ReddyPas encore d'évaluation

- Challenges in The Migration To 4GDocument36 pagesChallenges in The Migration To 4GSatti PanduPas encore d'évaluation

- Programmable Logic Controllers, Industrial Field Buses and SCADADocument45 pagesProgrammable Logic Controllers, Industrial Field Buses and SCADAZeeshan MahmoodPas encore d'évaluation

- Serial Communication Protocols v0.1Document20 pagesSerial Communication Protocols v0.1abhi_vlsiPas encore d'évaluation

- I C-Bus Specification and User ManualDocument50 pagesI C-Bus Specification and User ManualAll4UyenPas encore d'évaluation

- Communication Medium - 1Document7 pagesCommunication Medium - 1adaptive4u4527Pas encore d'évaluation

- LM18Document4 pagesLM18DHANASEKAR RPas encore d'évaluation

- 8085 Chapter9Document6 pages8085 Chapter9Amir Hossein Javan AmoliPas encore d'évaluation

- Serial Communiaction ProtocolsDocument17 pagesSerial Communiaction ProtocolsRama Krishna Reddy GudooruPas encore d'évaluation

- C CCC CCC C CC C CDocument6 pagesC CCC CCC C CC C CMd Rizwan AhmadPas encore d'évaluation

- Week 4:: Computer Interconnection Structures, Bus Interconnection, PCIDocument16 pagesWeek 4:: Computer Interconnection Structures, Bus Interconnection, PCIRegji IndonPas encore d'évaluation

- Microcontrollres Notes PDFDocument66 pagesMicrocontrollres Notes PDFYash KuncolienkerPas encore d'évaluation

- Microcontrollres NotesDocument66 pagesMicrocontrollres Notesthiruct77Pas encore d'évaluation

- Microprocessor 8085 MicrocontrollerDocument223 pagesMicroprocessor 8085 MicrocontrollerJidh KumarPas encore d'évaluation

- Centronics and Ieee 488 (Parallel Interfaces)Document139 pagesCentronics and Ieee 488 (Parallel Interfaces)Govinda Prasad Acharya100% (1)

- ARM Question Bank Unit - 5Document14 pagesARM Question Bank Unit - 5sakthivelv.eecPas encore d'évaluation

- GPIBDocument39 pagesGPIBRaviraj MaiyaPas encore d'évaluation

- Secure Data CommunicationDocument11 pagesSecure Data CommunicationNeela ChennurPas encore d'évaluation

- Assignment ACNDocument7 pagesAssignment ACNMukeshPas encore d'évaluation

- Selecting A Serial Bus: Application Note 3967Document7 pagesSelecting A Serial Bus: Application Note 3967nevdullPas encore d'évaluation

- Inv U1 TICDocument11 pagesInv U1 TICLucas LopezPas encore d'évaluation

- Building IP Networks Using Advanced Telecom Computing ArchitectureDocument6 pagesBuilding IP Networks Using Advanced Telecom Computing Architectureavishek2005Pas encore d'évaluation

- PLCDocument119 pagesPLCamism24100% (1)

- I2c Bus OverviewDocument158 pagesI2c Bus OverviewSkyline Dv100% (2)

- 1 UnitDocument21 pages1 UnitrambabuPas encore d'évaluation

- Unit 3 System Interfacing and ControllersDocument48 pagesUnit 3 System Interfacing and ControllersSrinivasan V PPas encore d'évaluation

- UART/USART, SPI, I C Features and ApplicationsDocument5 pagesUART/USART, SPI, I C Features and ApplicationsVishal Kottarathil100% (2)

- Module 1a A Brief History of Computer ArchitectureDocument53 pagesModule 1a A Brief History of Computer ArchitectureMairos Kunze BongaPas encore d'évaluation

- Exploring I2cDocument6 pagesExploring I2cspyeaglePas encore d'évaluation

- Modbus ProtocolDocument9 pagesModbus ProtocolSupachai Klu100% (1)

- AI 340 Standard Field BussesDocument45 pagesAI 340 Standard Field BussesAdhitya Surya PambudiPas encore d'évaluation

- Unit 3Document56 pagesUnit 3TakeItEasyDude TIEDPas encore d'évaluation

- AC500 PLC BrochureDocument52 pagesAC500 PLC Brochureekspl927Pas encore d'évaluation

- Microprocessor Interfacing TechniquesDocument351 pagesMicroprocessor Interfacing Techniquesjsa100% (3)

- Report On Digital Switching SystemDocument20 pagesReport On Digital Switching SystemKurban UbulPas encore d'évaluation

- Microprocesror and Programming Theory-KM-S4Document29 pagesMicroprocesror and Programming Theory-KM-S4Adhara MukherjeePas encore d'évaluation

- Computer Organization and Architecture-1Document5 pagesComputer Organization and Architecture-1Milan AntonyPas encore d'évaluation

- Matrix Key Board Ieee 488Document9 pagesMatrix Key Board Ieee 488mohit mishraPas encore d'évaluation

- Microprocessors and MicrocontrollersDocument86 pagesMicroprocessors and MicrocontrollersbrightmorePas encore d'évaluation

- Micro InterfacingDocument15 pagesMicro InterfacingDeepesh KhanejaPas encore d'évaluation

- GPI BusDocument11 pagesGPI BusCamilo A. InfantePas encore d'évaluation

- USB Project BookDocument60 pagesUSB Project BookVara Prasad VemulaPas encore d'évaluation

- I2c - Bus From ViitDocument19 pagesI2c - Bus From ViitSantosh KumarPas encore d'évaluation

- IOT Wired ProtocolsDocument6 pagesIOT Wired ProtocolsutpolaPas encore d'évaluation

- Handbook of Serial Communications Interfaces: A Comprehensive Compendium of Serial Digital Input/Output (I/O) StandardsD'EverandHandbook of Serial Communications Interfaces: A Comprehensive Compendium of Serial Digital Input/Output (I/O) StandardsÉvaluation : 1 sur 5 étoiles1/5 (4)

- Computer Organization and Design: The Hardware / Software InterfaceD'EverandComputer Organization and Design: The Hardware / Software InterfaceÉvaluation : 4 sur 5 étoiles4/5 (12)

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.D'EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Pas encore d'évaluation

- LinuxKI 4.1 CURSODocument78 pagesLinuxKI 4.1 CURSOXavi MilanPas encore d'évaluation

- Java Inheritance PDFDocument7 pagesJava Inheritance PDFMallikarjun AradhyaPas encore d'évaluation

- Mil Q2 Modules-7-8Document28 pagesMil Q2 Modules-7-8Nyanko Soriano100% (1)

- Real-Time Arrival Information of The Kowloon Motor Bus Company (1933) LimitedDocument38 pagesReal-Time Arrival Information of The Kowloon Motor Bus Company (1933) LimitedFung AlexPas encore d'évaluation

- Logitech G-17-02Document6 pagesLogitech G-17-02Juliana Dianira Sandoval LopezPas encore d'évaluation

- CCNA Modul 11Document8 pagesCCNA Modul 11Hery Tjah KakoiPas encore d'évaluation

- Weintek MT6050iP, MT8050iPDocument3 pagesWeintek MT6050iP, MT8050iPvijayrockz06Pas encore d'évaluation

- 2020 Ol Sinhala Literature Paper Olevelapi PDFDocument3 pages2020 Ol Sinhala Literature Paper Olevelapi PDFdehemi deekshaPas encore d'évaluation

- SR-5000 Script Reference - EDocument24 pagesSR-5000 Script Reference - EDomagoj ZagoracPas encore d'évaluation

- 8 Bit Kogge Stone Adder - Final - ReportDocument8 pages8 Bit Kogge Stone Adder - Final - ReportbigfatdashPas encore d'évaluation

- Drain Design MetricDocument31 pagesDrain Design MetricEmre MermerPas encore d'évaluation

- Unit 3 NotesDocument15 pagesUnit 3 NotesRemya A V AvinutyPas encore d'évaluation

- CHAPTER 1 Review AnswersDocument3 pagesCHAPTER 1 Review AnswersVîhãGä ÔlüKä RàñâsîñGhêPas encore d'évaluation

- Lanyliel EstanoDocument2 pagesLanyliel Estanolanyliel EstanoPas encore d'évaluation

- Practical File Computer Applications Class 10 For 2022-23Document25 pagesPractical File Computer Applications Class 10 For 2022-23Aditya Chauhan100% (2)

- Chapter 6: Questions and AnswersDocument51 pagesChapter 6: Questions and Answersnnbphuong810% (2)

- EDA - Ciclo2022 - 2 - EstadisticaByvariadaDocument9 pagesEDA - Ciclo2022 - 2 - EstadisticaByvariadaRicardo CremaPas encore d'évaluation

- Wrong Number Series Short Tricks Question Answers PDFDocument44 pagesWrong Number Series Short Tricks Question Answers PDFAbhijit DharPas encore d'évaluation

- Visual BasicDocument8 pagesVisual BasicSUNNY KUMARPas encore d'évaluation

- Section 5 QuizDocument7 pagesSection 5 QuizAnca Vochescu100% (1)

- MeDocument2 pagesMeisaacamankwaaPas encore d'évaluation

- DAX Guidebook UpdatedDocument13 pagesDAX Guidebook Updatedmaria lopezPas encore d'évaluation

- ProxySG Required PortsDocument8 pagesProxySG Required PortsbooksmagicPas encore d'évaluation

- EE313 Lab 2Document6 pagesEE313 Lab 2Alvish NaiduPas encore d'évaluation

- Nema Vs IPDocument1 pageNema Vs IPTamer Ahmed SalemPas encore d'évaluation

- 12 Channels Temp. RECORDER: ISO-9001, CE, IEC1010Document2 pages12 Channels Temp. RECORDER: ISO-9001, CE, IEC1010EdwardRamosPas encore d'évaluation

- EDU 655 Week 3 Discussion 1 Ashford University Student Education Keith C Quarles GRADE A PAPERDocument3 pagesEDU 655 Week 3 Discussion 1 Ashford University Student Education Keith C Quarles GRADE A PAPERkeith_quarlesPas encore d'évaluation

- Portainer Documentation: Release 1.22.1Document55 pagesPortainer Documentation: Release 1.22.1Gabriel UlloaPas encore d'évaluation

- Information Security and Cryptography: Series EditorsDocument12 pagesInformation Security and Cryptography: Series Editorsadam mukhrizPas encore d'évaluation