Académique Documents

Professionnel Documents

Culture Documents

Memory Module Specifications: KVR667D2D4F5/2G 2GB 256M X 72-Bit PC2-5300 Cl5 Ecc 240-Pin Fbdimm

Transféré par

HippyKillerTitre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Memory Module Specifications: KVR667D2D4F5/2G 2GB 256M X 72-Bit PC2-5300 Cl5 Ecc 240-Pin Fbdimm

Transféré par

HippyKillerDroits d'auteur :

Formats disponibles

Memory Module Specifications

KVR667D2D4F5/2G 2GB 256M x 72-Bit PC2-5300 CL5 ECC 240-Pin FBDIMM

Description:

This document describes ValueRAM's 2GB (256M x 72-bit) PC2-5300 CL5 SDRAM (Synchronous DRAM) "fully buffered" ECC "dual rank" memory module. This module is based on thirty-six 128M x 4-bit 667MHz DDR2 FBGA components. The module also includes an AMB device (Advanced Memory Buffer). The electrical and mechanical specifications are as follows:

Feature:

FBDIMM Module: 240-pin JEDEC Standard: R/C H Memory Organization: 2 rank of x4 devices DDR2 DRAM Interface: SSTL_18 DDR2 Speed Grade: 667 Mbps CAS Latency: 5-5-5 Module Bandwidth: 5.3 GB/s FBDIMM Channel Peak Throughput: 8.0 GB/s DRAM: VDD = VDDQ = 1.8V AMB: VCC = VCCFBD = 1.5V EEPROM: VDDSPD = 3.3V (typical) Heat Spreader: AMB-only heat sink PCB Height: 30.35mm, double-side RoHS Compliant

VALUERAM0483-001.A00

04/14/06

Page 1

T E C H N O L O G Y

DDR2 240-pin FBDIMM Pinout:

Pin #

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30

Front Side

VDD VDD VDD VSS VDD VDD VDD VSS VCC VCC VSS VCC VCC VSS VTT VID1 RESET VSS RFU** RFU** VSS PN0 PN0 VSS PN1 PN1 VSS PN2 PN2 VSS

Pin #

121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136

Back Side

VDD VDD VDD VSS VDD VDD VDD VSS VCC VCC VSS VCC VCC VSS VTT VID0

Pin #

31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60

Front Side

PN3 PN3 VSS PN4 PN4 VSS PN5 PN5 VSS PN13 PN13 VSS VSS RFU* RFU* VSS VSS PN12 PN12 VSS PN6 PN6 VSS PN7 PN7 VSS PN8 PN8 VSS PN9

Pin #

151 152 153 154 155 156 157 158 159 160 161 162 163 164 165 166 167 168 169 170 171 172 173 174 175 176 177 178 179 180

Back Side

SN3 SN3 VSS SN4 SN4 VSS SN5 SN5 VSS SN13 SN13 VSS VSS RFU* RFU* VSS VSS SN12 SN12 VSS SN6 SN6 VSS SN7 SN7 VSS SN8 SN8 VSS SN9

Pin #

61 62 63 64 65 66 67 68

Front Side

PN9 VSS PN10 PN10 VSS PN11 PN11 VSS

Pin #

181 182 183 184 185 186 187 188 KEY

Back Side

SN9 VSS SN10 SN10 VSS SN11 SN11 VSS

Pin #

91 92 93 94 95 96 97 98 99

Front Side

PS9 VSS PS5 PS5 VSS PS6 PS6 VSS PS7 PS7 VSS PS8 PS8 VSS RFU** RFU** VSS VDD VDD VSS VDD VDD VDD VSS VDD VDD VTT SA2 SDA SCL

Pin #

211 212 213 214 215 216 217 218 219 220 221 222 223 224 225 226 227 228 229 230 231 232 233 234 235 236 237 238 239 240

Back Side

SS9 VSS SS5 SS5 VSS SS6 SS6 VSS SS7 SS7 VSS SS8 SS8 VSS RFU** RFU** VSS SCK SCK VSS VDD VDD VDD VSS VDD VDD VTT VDDSPD SA0 SA1

69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90

VSS PS0 PS0 VSS PS1 PS1 VSS PS2 PS2 VSS PS3 PS3 VSS PS4 PS4 VSS VSS RFU* RFU* VSS VSS PS9

189 190 191 192 193 194 195 196 197 198 199 200 201 202 203 204 205 206 207 208 209 210

VSS SS0 SS0 VSS SS1 SS1 VSS SS2 SS2 VSS SS3 SS3 VSS SS4 SS4 VSS VSS RFU* RFU* VSS VSS SS9

100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120

137 DNU/M_Test 138 139 140 141 142 143 144 145 146 147 148 149 150 VSS RFU** RFU** VSS SN0 SN0 VSS SN1 SN1 VSS SN2 SN2 VSS

RFU = Reserved Future Use. * These pin positions are reserved for forwarded clocks to be used in future module implementations ** These pin positions are reserved for future architecture flexibility 1) The following signals are CRC bits and thus appear out of the normal sequence: PN12/PN12, SN12/SN12, PN13/PN13, SN13/SN13, PS9/PS9, SS9/SS9

VALUERAM0483-001.A00

Page 2

T E C H N O L O G Y

DIMM Connector Pin Description:

Pin Name SCK SCK PN[13:0] PN[13:0] PS[9:0] PS[9:0] SN[13:0] SN[13:0] SS[9:0] SS[9:0] SCL SDA SA[2:0] VID[1:0] RESET RFU VCC VDD VTT VDDSPD VSS Pin Description System Clock Input, positive line1 System Clock Input, negative line1 Primary Northbound Data, positive lines Primary Northbound Data, negative lines Primary Southbound Data, positive lines Primary Southbound Data, negative lines Secondary Northbound Data, positive lines Secondary Northbound Data, negative lines Secondary Southbound Data, positive lines Secondary Southbound Data, negative lines Serial Presence Detect (SPD) Clock Input SPD Data Input / Output SPD Address Inputs, also used to select the DIMM number in the AMB Voltage ID: These pins must be unconnected for DDR2-based Fully Buffered DIMMs VID[0] is VDD value: OPEN = 1.8 V, GND = 1.5 V; VID[1] is V CC value: OPEN = 1.5 V, GND = 1.2 V AMB reset signal Reserved for Future Use

2

Count 1 1 14 14 10 10 14 14 10 10 1 1 3 2 1 16 8 24 4 1 80

AMB Core Power and AMB Channel Interface Power (1.5 Volt) DRAM Power and AMB DRAM I/O Power (1.8 Volt) DRAM Address/Command/Clock Termination Power (V DD/2) SPD Power Ground The DNU/M_Test pin provides an exter nal connection on R/Cs A-D for testing the margin of Vref which is produced by a voltage divider on the module. It is not intended to be used in normal system operation and must not be connected (DNU) in a system. This test pin may have other features on future card designs and if it does, will be included in this specification at that time. 1 Total

DNU/M_Test

240

1. System Clock Signals SCK and SCK switch at one half the DRAM CK/CK frequency 2. Eight pins reserved for forwarded clocks, eight pins reserved for future architecture flexibility

VALUERAM0483-001.A00

Page 3

T E C H N O L O G Y

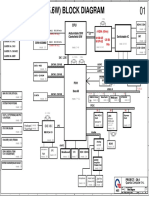

Functional Block Diagram:

VSS S1 S0

DQS0 DQS0 DQ0 DQ1 DQ2 DQ3 DQS1

DQS1

DM

CS DQS DQS

DM

DQS9 DQS9

CS DQS DQS DM

I/O 0 I/O 1 I/O 2 I/O 3

D0

I/O 0 I/O 1 I/O 2 I/O 3

D18

DQ4 DQ5 DQ6 DQ7 DQS10 DQS10

CS DQS DQS

DM

CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3

D9

I/O 0 I/O 1 I/O 2 I/O 3

D27

DM

DQ8 DQ9 DQ10 DQ11 DQS2 DQS2 DQ16 DQ17 DQ18 DQ19 DQS3 DQS3 DQ24 DQ25 DQ26 DQ27 DQS4 DQS4 DQ32 DQ33 DQ34 DQ35 DQS5 DQS5 DQ40 DQ41 DQ42 DQ43 DQS6 DQS6 DQ48 DQ49 DQ50 DQ51 DQS7 DQS7 DQ56 DQ57 DQ58 DQ59 DQS8 DQS8 CB0 CB1 CB2 CB3

PN0-PN13 PN0-PN13 PS0-PS9 PS0-PS9 DQ0-DQ63 CB0-CB7 DQS0-DQS17 DQS0-DQS17 SCL SDA SA1-SA2 SA0 RESET SCK/SCK

CS DQS DQS

DM

CS DQS DQS

DM

I/O 0 I/O 1 I/O 2 I/O 3

DM

D1

I/O 0 I/O 1 I/O 2 I/O 3

DM

D19

DQ12 DQ13 DQ14 DQ15 DQS11 DQS11

CS DQS DQS

DM

CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3

DM

D10

I/O 0 I/O 1 I/O 2 I/O 3

DM

D28

CS DQS DQS

CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3

DM

D2

I/O 0 I/O 1 I/O 2 I/O 3

DM

D20

DQ20 DQ21 DQ22 DQ23 DQS12 DQS12 DQ28 DQ29 DQ30 DQ31 DQS13 DQS13

CS DQS DQS

CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3

DM

D11

I/O 0 I/O 1 I/O 2 I/O 3

DM

D29

CS DQS DQS

CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3

DM

D3

I/O 0 I/O 1 I/O 2 I/O 3

DM

CS DQS DQS

CS DQS DQS

D21

I/O 0 I/O 1 I/O 2 I/O 3

DM

D12

I/O 0 I/O 1 I/O 2 I/O 3

DM

D30

CS DQS DQS

CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3

DM

D4

I/O 0 I/O 1 I/O 2 I/O 3

DM

D22

DQ36 DQ37 DQ38 DQ39 DQS14 DQS14 DQ44 DQ45 DQ46 DQ47 DQS15 DQS15 DQ52 DQ53 DQ54 DQ55 DQS16 DQS16 DQ60 DQ61 DQ62 DQ63 DQS17 DQS17 CB4 CB5 CB6 CB7

CS DQS DQS

CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3

DM

D13

I/O 0 I/O 1 I/O 2 I/O 3

DM

D31

CS DQS DQS

CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3

DM

D5

I/O 0 I/O 1 I/O 2 I/O 3

DM

CS DQS DQS

CS DQS DQS

D23

I/O 0 I/O 1 I/O 2 I/O 3

DM

D14

I/O 0 I/O 1 I/O 2 I/O 3

DM

D32

CS DQS DQS

CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3

DM

D6

I/O 0 I/O 1 I/O 2 I/O 3

DM

CS DQS DQS

CS DQS DQS

D24

I/O 0 I/O 1 I/O 2 I/O 3

DM

D15

I/O 0 I/O 1 I/O 2 I/O 3

DM

D33

CS DQS DQS

CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3

DM

D7

I/O 0 I/O 1 I/O 2 I/O 3

DM

CS DQS DQS

CS DQS DQS

D25

I/O 0 I/O 1 I/O 2 I/O 3

DM

D16

I/O 0 I/O 1 I/O 2 I/O 3

DM

D34

CS DQS DQS

CS DQS DQS

I/O 0 I/O 1 I/O 2 I/O 3

D8

I/O 0 I/O 1 I/O 2 I/O 3

CS DQS DQS

CS DQS DQS

D26

I/O 0 I/O 1 I/O 2 I/O 3

D17

VTT VCC VDDSPD

I/O 0 I/O 1 I/O 2 I/O 3

D35

Terminators AMB SPD, AMB D0-D35, AMB D0-D35 D0-D35, SPD, AMB

SN0-SN13 SN0-SN13 SS0-SS9 SS0-SS9

All address/command/control/clock

Serial PD SCL WP A0 A1 A2 SA0 SA1 SA2

VTT

SDA

A M B

S0 -> CS (D0-D17) CKE0 -> CKE (D0-D17) S1 -> CS (D18-D35) CKE1 -> CKE (D18-D35) ODT -> ODT0 (all SDRAMs) BA0-BA2 (all SDRAMs) A0-A15 (all SDRAMs) RAS (all SDRAMs) CAS (all SDRAMs) WE (all SDRAMs) CK/CK (all SDRAMs)

VDD VREF

3. There are four physical copies of each clock

VSS Notes: 1. DQ-to-I/O wiring may be changed within a nibble 2. There are two physical copies of each address/command/control

VALUERAM0483-001.A00

Page 4

T E C H N O L O G Y

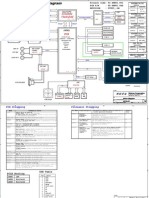

Architecture:

Advanced Memory Buffer Pin Description:

Pin Name Pin Description Count

FB-DIMM Channel Signals

SCK SCK PN[13:0] PN[13:0] PS[9:0] PS[9:0] SN[13:0] SN[13:0] SS[9:0] SS[9:0] FBDRES System Clock Input, positive line System Clock Input, negative line Primary Northbound Data, positive lines Primary Northbound Data, negative lines Primary Southbound Data, positive lines Primary Southbound Data, negative lines Secondary Northbound Data, positive lines Secondary Northbound Data, negative lines Secondary Southbound Data, positive lines Secondary Southbound Data, negative lines To an external precision calibration resistor connected to Vcc

99

1 1 14 14 10 10 14 14 10 10 1

DDR2 Interface Signals

DQS[8:0] DQS[8:0] DQS[17:9]/DM[8:0] DQS[17:9] DQ[63:0] CB[7:0] A[15:0]A, A[15:0]B BA[2:0]A, BA[2:0]B RASA, RASB CASA, CASB WEA, WEB ODTA, ODTB CS[1:0]A, CS[1:0]B CLK[3:0] CLK[3:0] DDRC_C14 DDRC_B18 DDRC_C18 DDRC_B12 DDRC_C12 Data Strobes, positive lines Data Strobes, negative lines Data Strobes (x4 DRAM only), positive lines. These signals are driven low to x8 DRAM on writes. Data Strobes (x4 DRAM only), negative lines Data Checkbits Addresses. A10 is part of the pre-charge command Bank Addresses Part of command, with CAS, WE, and CS[1:0]. Part of command, with RAS, WE, and CS[1:0]. Part of command, with RAS, CAS, and CS[1:0]. On-die Termination Enable Chip Select (one per rank)

175

9 9 9 9 64 8 32 6 2 2 2 2 4 4

CKE[1:0]A, CKE[1:0]B Clock Enable (one per rank)

CLK[1:0] used on 9 and 18 device DIMMs, CLK[3:0] used on 36 device DIMMs. CLK[3:2] should be out4 put disabled when not in use. Negative lines for CLK[3:0] DDR Compensation: Common return pin for DDRC_B18 and DDRC_C18. DDR Compensation: Resistor connected to common return pin DDRC_C14 DDR Compensation: Resistor connected to common return pin DDRC_C14 DDR Compensation: Resistor connected to VSS DDR Compensation: Resistor connected to VDD 4 1 1 1 1 1

VALUERAM0483-001.A00

Page 5

T E C H N O L O G Y

Advanced Memory Buffer Pin Description: SPD Bus Interface Signals

SCL SDA SA[2:0] Serial Presence Detect (SPD) Clock Input SPD Data Input / Output SPD Address Inputs, also used to select the DIMM number in the AMB

5

1 1 3

Miscellaneous Signals

PLLTSTO VCCAPLL VSSAPLL TEST_pin# TESTLO_pin# BFUNC RESET NC RFU PLL Clock Observability Output Analog VCC for the PLL. Tied with low pass filter to VCC. Analog VSS for the PLL. Tied to ground on the AMB die. Do not tie to ground on the DIMM. Leave floating on the DIMM Tie to ground on the DIMM AMB reset signal No connect. Many NC are connected to VDD on the DIMM, to lower the impedance of the VDD power islands. Reserved for Future Use

2

163

1 1 1 6 5 1 1 129 18

Tie to ground to set functionality as buffer on DIMM.

Power/Ground Signals

VCC VCCFBD VDD VDDSPD VSS AMB Core Power (1.5 Volt) AMB Channel I/O Power (1.5 Volt) AMB DRAM I/O Power (1.8 Volt) SPD Power (3.3 Volt) Ground

213

24 8 24 1 156

Total

655

1. System Clock Signals SCK and SCK switch at one half the DRAM CK/CK frequency. 2. TESTLO_AB20 and TESTLO_AC20 should be configured for debug purposes on prototype DIMMs: each pin should have a zero ohm resistor pulldown to ground, and an unpopulated resistor pullup to VCC. These resistors can be replaced on production DIMMs with a direct connection to ground.

VALUERAM0483-001.A00

Page 6

FBGA DDR2 SDRAM FBGA DDR2 SDRAM FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

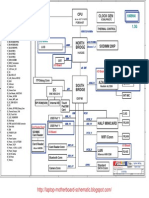

Package Dimensions:

VALUERAM0483-001.A00

0.346 (8.8) MAX with heat sink

FBGA DDR2 SDRAM FBGA DDR2 SDRAM

0.054 (1.37) 0.046 (1.17)

FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

(Units = millimeters)

FBGA DDR2 SDRAM FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

45x 0.0071(0.18)

0.047 (1.19)

Units: inches (millimeters)

FBGA DDR2 SDRAM FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

Detail A

FBGA DDR2 SDRAM FBGA DDR2 SDRAM FBGA DDR2 SDRAM FBGA DDR2 SDRAM

T E C H N O L O G Y

0.042 (1.06)

0.042 (1.06)

FBGA DDR2 SDRAM

AMB

Advance Memory Buffer

FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

Page 7

FBGA DDR2 SDRAM

FBGA DDR2 SDRAM

T E C H N O L O G Y

Vous aimerez peut-être aussi

- Features: 200pin Unbuffered Ddr2 Sdram So-Dimms Based On 1Gb Version CDocument23 pagesFeatures: 200pin Unbuffered Ddr2 Sdram So-Dimms Based On 1Gb Version CAthal-wardPas encore d'évaluation

- DDR1 SODIMM 512Mb Die BDocument18 pagesDDR1 SODIMM 512Mb Die BNeraw KozeyPas encore d'évaluation

- Ddr3 Sdram Unbuffered Sodimms Based On 1Gb B-Die: Hmt164S6Bfr6C Hmt112S6Bfr6C Hmt125S6Bfr8CDocument51 pagesDdr3 Sdram Unbuffered Sodimms Based On 1Gb B-Die: Hmt164S6Bfr6C Hmt112S6Bfr6C Hmt125S6Bfr8COrlando SedamanoPas encore d'évaluation

- Hws 13642Document3 pagesHws 13642dhieward100% (2)

- Pc100 Sdram Module KMM366S1723T Preliminary: Revision HistoryDocument11 pagesPc100 Sdram Module KMM366S1723T Preliminary: Revision Historyfalco2010Pas encore d'évaluation

- PSR-S700 S900 Lsi CDocument13 pagesPSR-S700 S900 Lsi CAdriano CamocardiPas encore d'évaluation

- HP Envy 15 (Quanta SP7)Document42 pagesHP Envy 15 (Quanta SP7)efeln1Pas encore d'évaluation

- JM667QSJ-1G 2162 SDocument3 pagesJM667QSJ-1G 2162 Sgns_vcPas encore d'évaluation

- Gateway W350DI.Document44 pagesGateway W350DI.Abubakar SidikPas encore d'évaluation

- SRT 4155 and SRT4355 - ServicemanualDocument40 pagesSRT 4155 and SRT4355 - ServicemanualMohamed MakiPas encore d'évaluation

- Hy5du561622ftp d43Document31 pagesHy5du561622ftp d43yhomerPas encore d'évaluation

- Toshiba Satellite L730 (Quanta BU5D) Laptop SchematicsDocument41 pagesToshiba Satellite L730 (Quanta BU5D) Laptop SchematicsIsa Firmanto100% (1)

- NT1GD64S8HA0FM / NT1GD64S8HB0FM 1GB: 128M X 64 PC2700 / PC2100 Unbuffered DDR SO-DIMM 200 Pin Unbuffered DDR SO-DIMM FeaturesDocument14 pagesNT1GD64S8HA0FM / NT1GD64S8HB0FM 1GB: 128M X 64 PC2700 / PC2100 Unbuffered DDR SO-DIMM 200 Pin Unbuffered DDR SO-DIMM FeaturesLuis Carlos Cardenas MancoPas encore d'évaluation

- Intel CPU: Ddriii 800/1066/1333 Ddriii 800/1066/1333 Ics9Lrs3197AklftDocument50 pagesIntel CPU: Ddriii 800/1066/1333 Ddriii 800/1066/1333 Ics9Lrs3197Aklftdrop9721Pas encore d'évaluation

- Autoestereo Pioneer DEH-4090MP DEH-6010MPDocument39 pagesAutoestereo Pioneer DEH-4090MP DEH-6010MPGustavo De la OPas encore d'évaluation

- Atmel 11209 32 Bit Cortex M4 Microcontroller SAM G51 DatasheetDocument866 pagesAtmel 11209 32 Bit Cortex M4 Microcontroller SAM G51 Datasheetmsmith6477Pas encore d'évaluation

- System Setting DetailsDocument50 pagesSystem Setting DetailsFelipePas encore d'évaluation

- 7-1 Overall Block DiagramDocument4 pages7-1 Overall Block DiagramCraig KalinowskiPas encore d'évaluation

- cdp1802 CosmacDocument27 pagescdp1802 Cosmacrebirth90Pas encore d'évaluation

- A SemiconductoresDocument19 pagesA Semiconductoresajcl_1987Pas encore d'évaluation

- 1632 CV 100Document22 pages1632 CV 100Bruno FascendiniPas encore d'évaluation

- MC-4564EC727: Mos Integrated CircuitDocument16 pagesMC-4564EC727: Mos Integrated CircuitTania TorresPas encore d'évaluation

- P+5V P+5V: Power On MuteDocument8 pagesP+5V P+5V: Power On MuteuyrikPas encore d'évaluation

- 196 124334 HT16C21Document34 pages196 124334 HT16C21jeeep32Pas encore d'évaluation

- 4GB Registered DDR2 SDRAM DIMM: EBE41AE4ACFA (512M Words 72 Bits, 2 Ranks)Document27 pages4GB Registered DDR2 SDRAM DIMM: EBE41AE4ACFA (512M Words 72 Bits, 2 Ranks)ramgopalreddykPas encore d'évaluation

- Product Sheet Ddr3 So DimmDocument3 pagesProduct Sheet Ddr3 So Dimmmartin sembinelliPas encore d'évaluation

- K4D261638FDocument18 pagesK4D261638F9183290782Pas encore d'évaluation

- Quanta QL4Document44 pagesQuanta QL4Robson ZimmermannPas encore d'évaluation

- Double Data Rate (DDR) SdramDocument8 pagesDouble Data Rate (DDR) Sdramcatsoithahuong84Pas encore d'évaluation

- Power Sequence Timing ChartDocument40 pagesPower Sequence Timing Chartgabiun0% (1)

- Data Sheet: MN2PS00003RFDocument43 pagesData Sheet: MN2PS00003RFSoni BhattaPas encore d'évaluation

- Service Manual: CD/DVD PlayerDocument30 pagesService Manual: CD/DVD PlayerkeopsnattPas encore d'évaluation

- Acer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHDocument67 pagesAcer Aspire 7741 7741z 7741g 7741zg Emachines G730g Wistron JE70-CP Rev - 1M SCHWilgen GarciaPas encore d'évaluation

- PE4H VER24 SchematicDocument2 pagesPE4H VER24 SchematicB Huerta MuñozPas encore d'évaluation

- Asus Eeepc 1008ha - Rev 1.3gDocument50 pagesAsus Eeepc 1008ha - Rev 1.3gS_sergPas encore d'évaluation

- Frdm-kl25z Pinouts (Rev 1.0)Document5 pagesFrdm-kl25z Pinouts (Rev 1.0)huiuhiuhuiPas encore d'évaluation

- DS26LS32C/DS26LS32M/DS26LS32AC/DS26LS33C/ DS26LS33M/DS26LS33AC Quad Differential Line ReceiversDocument8 pagesDS26LS32C/DS26LS32M/DS26LS32AC/DS26LS33C/ DS26LS33M/DS26LS33AC Quad Differential Line Receiversjnax101Pas encore d'évaluation

- Graphics LCD Controller Details PCF8833Document113 pagesGraphics LCD Controller Details PCF8833Ramazan BattalPas encore d'évaluation

- HP Pavilion Dv7 - Quanta Up6 7 Jones Cujo 2.0 Dis - Rev 1.0 26out2009Document42 pagesHP Pavilion Dv7 - Quanta Up6 7 Jones Cujo 2.0 Dis - Rev 1.0 26out2009Hans PeterPas encore d'évaluation

- VL393T2863M E6sDocument10 pagesVL393T2863M E6sNguyễn Công CườngPas encore d'évaluation

- CECL08D Datasheet Mp3-PlayerDocument1 pageCECL08D Datasheet Mp3-PlayerGlauber CostaPas encore d'évaluation

- Rev: 3.0A: W /S3 W/O S3Document25 pagesRev: 3.0A: W /S3 W/O S3drako123456789Pas encore d'évaluation

- At91m55800 PDFDocument250 pagesAt91m55800 PDFLeland ChristensenPas encore d'évaluation

- Ts 7500 SchematicDocument4 pagesTs 7500 Schematicimransiddiquiatvxt100% (1)

- Pin Mt1389eeDocument11 pagesPin Mt1389eeDavid MartinPas encore d'évaluation

- LCD Controller s6b0108Document24 pagesLCD Controller s6b0108Sunny HuxiPas encore d'évaluation

- WH1602W Tmi JTDocument29 pagesWH1602W Tmi JTscribe72Pas encore d'évaluation

- SPCA718+CXA2647N+SONY BOOMBOXDocument8 pagesSPCA718+CXA2647N+SONY BOOMBOXpablo190381Pas encore d'évaluation

- Circuit Diagram: ModelDocument26 pagesCircuit Diagram: ModelOmar LugoPas encore d'évaluation

- 1008ha UnlockedDocument53 pages1008ha UnlockednoevidalPas encore d'évaluation

- CCTV Surveillance: Video Practices and TechnologyD'EverandCCTV Surveillance: Video Practices and TechnologyÉvaluation : 4 sur 5 étoiles4/5 (1)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsD'EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsPas encore d'évaluation

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsD'EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsÉvaluation : 1 sur 5 étoiles1/5 (1)

- Radio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142D'EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142Pas encore d'évaluation

- Oracle Database 11g - Develop PL/SQL Program Units Vol 3Document80 pagesOracle Database 11g - Develop PL/SQL Program Units Vol 3Eslam Kamel MorsiPas encore d'évaluation

- Troubleshooting Guide For Licensing Problems in FLOW-3DDocument6 pagesTroubleshooting Guide For Licensing Problems in FLOW-3DBasemPas encore d'évaluation

- Embedded Uart Eth Wifi ModuleDocument37 pagesEmbedded Uart Eth Wifi ModulebuildmetPas encore d'évaluation

- XC2785X PDFDocument136 pagesXC2785X PDFRazaan2326Pas encore d'évaluation

- Week 4 - Computer NetworksDocument17 pagesWeek 4 - Computer Networksbright letsahPas encore d'évaluation

- Terraform Variables, Conditionals, Loops, Data Sources, Import and WorkspacesDocument11 pagesTerraform Variables, Conditionals, Loops, Data Sources, Import and WorkspacesKumar PPas encore d'évaluation

- Infotm IUW ReleaseNotes 2.0.15b 20121211Document13 pagesInfotm IUW ReleaseNotes 2.0.15b 20121211nandinesmgPas encore d'évaluation

- Informatica PowerCenter and Data Quality Deliver Up to 5X Faster Performance on Oracle ExadataDocument8 pagesInformatica PowerCenter and Data Quality Deliver Up to 5X Faster Performance on Oracle Exadatajakeer hussainPas encore d'évaluation

- LogDocument13 pagesLogMis DeptPas encore d'évaluation

- MT6755 Android Scatter EmmcDocument11 pagesMT6755 Android Scatter EmmcJoel MoorePas encore d'évaluation

- Tut 6 QuestionsDocument4 pagesTut 6 QuestionsSơn Lê VănPas encore d'évaluation

- Technical Summative Assessment 2: Group 8Document10 pagesTechnical Summative Assessment 2: Group 8Kimberly Anne DimalPas encore d'évaluation

- MT41J128M16JT 125KDocument211 pagesMT41J128M16JT 125Khash definePas encore d'évaluation

- Unit Ii: Machine Instructions & ProgrammesDocument7 pagesUnit Ii: Machine Instructions & ProgrammesdvadonePas encore d'évaluation

- PHP Runner Manual 9.6Document795 pagesPHP Runner Manual 9.6DiegoKodner75% (4)

- Getting Started With Infinispan PDFDocument32 pagesGetting Started With Infinispan PDFdasgoyalPas encore d'évaluation

- TIB BC 6.3 InstallationDocument50 pagesTIB BC 6.3 InstallationsddfsPas encore d'évaluation

- Oracle EBS Adding Node Using Rapid CloneDocument5 pagesOracle EBS Adding Node Using Rapid Cloneearslan1982Pas encore d'évaluation

- HPE Alletra 9000-PSN1013540069USENDocument4 pagesHPE Alletra 9000-PSN1013540069USENBaris NesimiogluPas encore d'évaluation

- Bahria University,: Karachi CampusDocument10 pagesBahria University,: Karachi CampusMuhammad Umer FarooqPas encore d'évaluation

- Conjur Fundamentals: Troubleshooting & ReportingDocument23 pagesConjur Fundamentals: Troubleshooting & Reportingkarthik chithariPas encore d'évaluation

- HDBMSDocument3 pagesHDBMSAfeefaPas encore d'évaluation

- 3com SuperStack 4 Switch 5500G-EI - Command Reference Guide v3.1.xDocument530 pages3com SuperStack 4 Switch 5500G-EI - Command Reference Guide v3.1.xAndresito de PereiraPas encore d'évaluation

- Developing A Database Appucation For Pine ValleyDocument8 pagesDeveloping A Database Appucation For Pine ValleyDEv Kaushal0% (1)

- Technical Reference Options and Adapters Volume 2 4of5Document124 pagesTechnical Reference Options and Adapters Volume 2 4of5kgrhoadsPas encore d'évaluation

- Rdbms Interview QuesDocument5 pagesRdbms Interview QuesGohan KawaPas encore d'évaluation

- Memory Management Part1 1Document5 pagesMemory Management Part1 1Mehulkumar DubeyPas encore d'évaluation

- Von Neumann vs Harvard architecturesDocument4 pagesVon Neumann vs Harvard architecturesAmeenPas encore d'évaluation

- 8.c PointersDocument11 pages8.c PointerssubashPas encore d'évaluation

- Fundamentals of Oracle Database and SQLDocument4 pagesFundamentals of Oracle Database and SQLAmit SharmaPas encore d'évaluation