Académique Documents

Professionnel Documents

Culture Documents

Edma Controller: Level 1 Programme Memory

Transféré par

Achmad ZuchalDescription originale:

Titre original

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Signaler ce documentDroits d'auteur :

Formats disponibles

Edma Controller: Level 1 Programme Memory

Transféré par

Achmad ZuchalDroits d'auteur :

Formats disponibles

Video Capture using the TMS320C6211 DSP N.Dahnoun A.Lillie University of Bristol, UK Naim.Dahnoun@Bristol.ac.uk 1.

Introduction This paper is concerned with developing a system that will capture a video signal from an analogue video camera and provide a platform for video coding, using the TMS320C6211 DSP [1, 3] from Texas Instrument. Black and White transmission of television pictures began as early as 1926 in Britain and the United States. The Second World War greatly slowed the development of the television broadcast industry, but military research during these years allowed colour television transmissions to begin in the US by 1949. This development lead to a massive growth post-war. Recently Digital technology has revolutionised the broadcast industry with the advent of digital television. It has also allowed the development of Personal Computer (PC) motion video [2]. Rather than just being a novelty, the ability to display moving images on a PC has many applications. Video conferencing is an application, which, at present is receiving a lot of interest. This interest is driven by the development of voice over packet technology. In order that video images can be transmitted efficiently in real time, video-coding techniques must be employed to reduce the amount of image data that must be communicated. This is achieved by exploiting the spatial and temporal redundancy present in natural image sequences. Many standards for the compression of video and still images exist, one example for the coding of still images is the JPEG (Joint Photographic Experts Group) standard. For video images the MPEG (Moving Pictures Experts Group), standards exist. These standards are based upon the DCT (Discrete Cosine Transform). Since its introduction in 1974, the DCT has become a very popular transform in image coding [4]. 2. C6211 CPU Architecture The 32-bit C6211 fixed point DSP belongs to the C6000 family of processors, with performance of up to 1600 million instructions per second (1600 MIPS at 200MHz) [3]. It is up to 10 times faster than a standard DSP processor. This family is the first to use the VelociTITM advanced very long instruction

word (VLIW) set to achieve high performance by enabling parallel processing, within the 8 functional units of the CPU during one clock cycle. Combined with a high clock rate this makes a very powerful processor. This family of processors has applications in many fields including, communications, consumer electronics and automotive engineering because of its high performance and good development tools that support it.

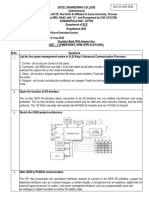

EMIF

Level 1 Programme Memory

Serial Port 1

EDMA Controller

CPU Level 2 Memory Control Data Path1 Data Path 2

Serial Port 2

HPI

Level 1 Data Memory

Timers

Figure 1, C6211 Digital Signal Processor The C6211 contains an Enhanced Direct Memory Access (EDMA) Controller [5], a replacement for the DMA controller found in other devices in the family. The C6211 can perform data transfers using either the CPU or the EDMA controller. The EDMA is normally used for block data or peripheral initiated transfers, freeing the CPU to deal with computationally intensive operations. The EDMA has 16 channels, which are each associated with a particular event such as an external interrupt or a timer. Each channel is separately programmable and has a user defined priority assignment; channels can also be linked to allow more complex data movements. Transitions from L2 Cache memory, peripherals and between external memory spaces are all supported. Parameters for EDMA transfers are stored in RAM so they are easily accessible by address generation hardware and relevant peripheral units such as the External Memory Interface (EMIF) [5]. 3. Video Interface Daughter Board In order to perform video coding on an image, the frames or sections to be coded must be stored in digital format within memory. A Daughter Board interface between the analogue video camera and the C6211 DSP must be developed. The function of the board is two-fold:

Sample, quantise and format the analogue data stream into a useable format Buffer the digital data so that it can be read by the DSP

I2C Interface [7] interfaces the DSP and the video decoder. Control Logic decodes the chip enable address signals so the FIFO and the I2C can be addressed independently. Write Logic controls the writing of data from the video decoder to the FIFO [8].

Host PC

3.1 Enhanced Input Video Processor (EVIP)

Capture System Daughter Board

Camera

C6211 DSP

Figure 2, Top Level System Overview Figure 2 shows the daughter boards interaction with the other elements of the system. Figure 3 shows a more detailed representation of the daughter board and its interaction with the DSP. The five elements that make up the daughter board are:

The video decoder SAA7111A by Philips Semiconductors [6], takes an analogue input in either CVBS or Y/C format, samples it and outputs the data in a number of common formats. The output format used is YUV [4:1:1] because it has 8-bit luminance and 4 bit chrominance components. This is particularly useful for a monochrome system as it provides a resolution of 0-255 for the luminance component. The chrominance saving is possible because the human visual system can tolerate a greater degradation in the chrominance than in the luminance component. The luminance component of the image data is output on the bus lines, VPO [15:8], the most significant byte. For a monochrome format, only the luminance component of the signal is required, therefore the U and V components can be discarded. These could be included to produce a full colour system if required. Each byte of data on the VPO bus represents a single pixel. The pixels are grouped together to form a frame as shown in Figure 3.

Video Decoder [6] (EVIP SAA7111A) converts an analogue camera input to digital format. First in First Out buffer (FIFO) 4K by 9-bit. Data is written by the video decoder and read by the DSK allowing some flexibility between the two processes.

Daughter Board Write Logic

Write Reset DB_CNTL1 D[7:0]

FIFO

Reference VPO[15:8] Analogue Video Input D[7:0] Read

Q[7:0]

C6211 DSP

Control Logic Video Processor

SDA SCL Vertical Sync Horizontal Sync

CE[3,2]

I2C Interface

D[1,0]

External Interrupt 4 External Interrupt 5

Figure 3, Daughter Board and DSK Board Block Diagram

720 Pixels

8*8 Blocks

Strip = 5760 Bytes

Frame = 450 KBytes

The daughter board supports a full frame rate (50 frames per second) monochrome video signal with a resolution of 720*625 pixels per frame without data loss. Ten lines of 720 pixels can be stored in the FIFO before overflow occurs. Most image coding standards work on blocks of 8*8 pixels therefore this capacity is large enough to cope with a single strip (Figure 4). The capture system could be up-graded to colour with relative ease. The monochrome video camera would have to be replaced with a colour alternative. The FIFO buffer width would also have to be increased from 8-bits to 12-bits so that the chrominance components of the signal could be captured. This would require no extra hardware, just replacement of the existing devices 4. Data Acquisition using the EDMA Controller The External Memory Interface (EMIF) can be configured to form a glue-less logic interface with external memory devices. By configuring the EMIF to match the timing characteristics of the FIFO, the EDMA can be used to acquire image data. Data transfers can be synchronised using the vertical and horizontal synchronisation signals from the Video Processor, shown in Figure 3, which indicate the start of a frame or line respectively. With the EDMA operating in 2-Dimensional Transfer mode with frame synchronisation, image data can be transferred line by line with frame synchronisation initiating the transfer. With silicon version 1 of the C6211 DSP the external interrupts 4-7 have not been mapped to the EDMA event register (ER) correctly. To overcome this problem interrupts must be manually mapped to the Event Set Register (ESR) via the CPU interrupt system. The aim when using the EDMA is to make memory transfers transparent to the CPU; image coding can be performed as a parallel activity. This fault means that the CPU is directly involved in each transfer and will therefore reduce its capacity to perform an image-coding algorithm.

625 Pixels

Figure 4, Frame Format 3.2 I2C Interface The Video Processor is controlled using a serial data interface developed by Philips Semiconductors called the Inter IC (I2C) Bus [7]. All I2C compatible devices incorporate an on chip interface which allows them to communicate with each other via the I2C bus. The main features of the bus are: The bus consists of two lines. A serial data line (SDA) and a clock line (SCL) All devices are software accessible by a unique address Serial 8-bit data can be communicated at up to 100Kbits/s (normal mode)

In order for non-compatible devices to communicate on the bus they must use a gluelogic interface. Figure 5 shows a simple implementation of such an interface, which allows the DSP to communicate with the Video Processor. The write/read inputs are active low controls with data being written/read from the D0 and D1 ports. This implementation facilitates complete control of the Video Processor by the DSP through the I2C interface.

D

Write

ENB

SET

SCL

CLR

Q

A ENB

R1

Read D0

5V B

SET

Q

ENB

SDA

CLR

Q

A ENB

R2

D1

5V B

Figure 5, Simple I2C Hardware Interface

EDMA Channel x Initial Transfer Parameters

EDMA Channel N Reload Parameters Exit

EDMA Channel O Reload Parameters

transfer. To achieve this transfer to L2 memory the throughput of the system would have to be greatly improved. At present a whole frame is stored to memory, requiring 450KBytes of memory. The L2 memory is only 64KBytes in size. This increase in throughput is possible by coding each frame, strip by strip and then transferring the coded data out of the DSP, only requiring 6KBytes of memory per strip.

Start A

Initialise Peripherals

Figure 6, Linked EDMA Transfers In order to transfer more than one frame of image data, EDMA channels can be linked. By combining three channels together as shown in Figure 6. It is possible to form a circular loop [1] to continuously transfer frames to memory. In order to stop this process the CPU can manually brake the loop by disabling the external interrupts. 5. Process Flow Figure 7 is a schematic detailing the flow of the DSP program. Once the system has been initialised [B] the first frame of data is transferred on the frame synchronisation signal [C]. The EDMA will transfer a whole frame line by line. The FIFO is reset at the beginning of each line [D] so that synchronisation is maintained and overflow prevented. Once complete [E], an image-coding algorithm can be performed in parallel by the CPU as the EDMA transfers the next frame [F,G]. The EDMA controller has been successfully configured so that it will transfer data from the FIFO to SDRAM memory. The EDMA controller transfers alternate frames to different memory regions so that image coding may be performed upon the non-active memory region. The DSP can retrieve from the daughter board video frames at a rate of 50 frames per second with a resolution of 256*256 pixels per frame. The resolution of the frames is limited by the ability of the EDMA to transfer data from the FIFO into SDRAM memory. Full size frames could be retrieved from the FIFO if the destination of the data was L2 RAM. The L2 RAM has a much faster access time than the SDRAM memory. The SDRAM is limiting the

Frame Synchronisation

D Line Synchronisation

Reset FIFO

Data Written to FIFO

EDMA Transfer

FrameTransfer Complete

E F

G Reload Parameters Image Coding

Data Ready

Finish

Figure 7, Overall System Process Flow 6. Host PC Application To display real time video images on screen a custom host application is developed using Visual C++. The application controls the DSP and receives image data through the parallel port interface, as shown in Figure 8. The application communicates with the DSP Host Port Interface (HPI) through the parallel port interface using a set of commands contained in a Dynamic Link Library (DLL) which have been defined specifically for the task.

Parallel Port DSP Memory Map HPI

Host PC Application Interface

stored in a FIFO so that it can be read by the DSP. The Enhanced Direct Memory Access (EDMA) controller and the External Memory Interface (EMIF) on the DSP have been configured so that they form an image data acquisition system. In order that complete image frames can be stored into DSP memory, the EDMA transfers data from the daughter board into SDRAM memory. The result is a bottleneck limiting the frame resolution to 256*256 pixels. The frame rate however is still full at 50 frames per second. The DSP peripherals have been set-up in such a way as to provide the ideal platform from which an image-coding algorithm could be launched using the CPU. Future work will demonstrate the implementation of a colour capture system. 8. References [1] N.Dahnoun, Digital Signal Processing Implementation using the TMS320C6000 DSP Platform, Prentice Hall, ISBN 0201-61916-4, 2000 [2] P.E. Matterson, Practical Digital Video with Programming Examples in C, John Wiley, ISBN 0-471-31015-8, 1994

Custom Application

Figure 8, Host Interface The user interface is fully functional, allowing the user full control over the DSP including the loading of COFF files. The interface will display synchronised captured still images on screen as shown in figure 9.

Figure 9, Captured Image, Real time video images with a frame rate of 1 frame per second are also supported. The very low frame rate is caused by the limited bandwidth of the parallel port interface. It can only support this rate, because no compression of image data using a video-coding scheme has been implemented. If this were the case then the frame rate would be dramatically improved 7. Conclusion The emphasis of this project has been on developing and implementing a real time video capture system using the C6211 DSP. This aim has been fully achieved. The daughter board interface between a monochrome analogue video camera and the C6211 DSP manufactured on double-sided PCB is fully functional. A video processor decodes the analogue video signal at a rate of 50 frames per second with a resolution of 720*525 pixels. The video processor is fully DSP controllable through an Inter IC (I2C) interface. The data is

[3] TMS320C6211 Fixed Point Digital Signal Processor, SPRS073A, March 1999 [4] Discrete Cosine Transform, N.Ahmed, T.Natarajan, K.Rao, IEEE transactions Computers Vol C23, Jan 1974 [5] TMS320C6000 Peripherals Reference Guide, Literature No. SPRU190C, April 1999 [6] SAA7111A Enhanced Video Input Processor, Philips Semiconductors, 1998 [7] The I2C Bus and How to Use It (Update), Philips Semiconductors, 1995 [8] TMS320C6000 EMIF to External FIFO Interface, Application Note SPRA543, May 1999

Vous aimerez peut-être aussi

- VW Polo 1 Diagnosis On Can BusDocument10 pagesVW Polo 1 Diagnosis On Can BusLucio OliveiraPas encore d'évaluation

- Pic Microcontroller Projects List (800 Projects)Document14 pagesPic Microcontroller Projects List (800 Projects)duino4projects83% (6)

- ADXL345 Digital Accelerometer: Created by Bill EarlDocument17 pagesADXL345 Digital Accelerometer: Created by Bill EarlherbertmgPas encore d'évaluation

- A Master-Slave DSP Board For Digital ControlDocument5 pagesA Master-Slave DSP Board For Digital Controlfurious143Pas encore d'évaluation

- Set - Top Box (STB)Document20 pagesSet - Top Box (STB)AbinayaPas encore d'évaluation

- Interfacing Nokia ScreenDocument4 pagesInterfacing Nokia ScreenDavid Sanderson100% (2)

- Document Version: 1.6.4 Image Version: V1.6.3: Lsn50 Lora Sensor Node User ManualDocument59 pagesDocument Version: 1.6.4 Image Version: V1.6.3: Lsn50 Lora Sensor Node User ManualOswaldo Andrés Vanegas GuillénPas encore d'évaluation

- Schematic Diagram of Ip Camera With EthernetDocument18 pagesSchematic Diagram of Ip Camera With EthernetnguyenminhtuanenginePas encore d'évaluation

- Implementation of A Streaming Camera Using An FPGA and CMOS Image SensorDocument8 pagesImplementation of A Streaming Camera Using An FPGA and CMOS Image SensorPravin WilfredPas encore d'évaluation

- Implementation of An Audio FX Processor Using The TMS320C6713 DSPDocument10 pagesImplementation of An Audio FX Processor Using The TMS320C6713 DSPjonesy5000Pas encore d'évaluation

- Color Detection Using FPGA Based Smart CameraDocument19 pagesColor Detection Using FPGA Based Smart Cameratry199Pas encore d'évaluation

- IA Series® Remote Terminal Unit (RTU)Document8 pagesIA Series® Remote Terminal Unit (RTU)Wisnu Hartono100% (1)

- Remote Terminal Unit (RTU)Document8 pagesRemote Terminal Unit (RTU)Wisnu HartonoPas encore d'évaluation

- 6713 User ManualDocument92 pages6713 User Manualsningle100% (1)

- Sistema de Compresión Embebida de Audio & VideoDocument4 pagesSistema de Compresión Embebida de Audio & Videoricardoag_newPas encore d'évaluation

- Embedded Real Time Video Monitoring System Using Arm: Kavitha Mamindla, Dr.V.Padmaja, CH - NagadeepaDocument5 pagesEmbedded Real Time Video Monitoring System Using Arm: Kavitha Mamindla, Dr.V.Padmaja, CH - Nagadeepabrao89Pas encore d'évaluation

- Tec5 3206 PI CMOS Electronics e 201803Document6 pagesTec5 3206 PI CMOS Electronics e 201803Mihail AvramovPas encore d'évaluation

- Mpeg 1 Part2 VideoDocument107 pagesMpeg 1 Part2 Videomtim360Pas encore d'évaluation

- Multimedia AssignmentDocument5 pagesMultimedia AssignmentKartik MandlaPas encore d'évaluation

- DSP LabmanualDocument82 pagesDSP LabmanualHemanth SharmaPas encore d'évaluation

- Ccs Manual 1Document53 pagesCcs Manual 1VicathorPas encore d'évaluation

- Decode Mpeg-2 Video With Virtex FpgasDocument3 pagesDecode Mpeg-2 Video With Virtex FpgasBlesson GeorgePas encore d'évaluation

- An Implementation of Rate-Adaptive IPTV System On DSP: Yen-Jen Chen, Chih-Chung Wang, and Jr-Jen HuangDocument7 pagesAn Implementation of Rate-Adaptive IPTV System On DSP: Yen-Jen Chen, Chih-Chung Wang, and Jr-Jen HuangKagitha TirumalaPas encore d'évaluation

- Gpls Vme Module: A Diagnostic and Display Tool For Nsls Micro SystemsDocument3 pagesGpls Vme Module: A Diagnostic and Display Tool For Nsls Micro SystemsSai KrishnaPas encore d'évaluation

- DSP Lab Manual - UpdatedDocument70 pagesDSP Lab Manual - UpdatedSatya kavyaPas encore d'évaluation

- Design of Architecture and FPGA Implementation of A Video EncoderDocument9 pagesDesign of Architecture and FPGA Implementation of A Video EncoderBijoy Kumar UpadhyayaPas encore d'évaluation

- A System On Chip For Digital TVDocument6 pagesA System On Chip For Digital TV席銘杰Pas encore d'évaluation

- Ee 549 Undergraduate Project Ii: "Voip To PSTN Converter"Document30 pagesEe 549 Undergraduate Project Ii: "Voip To PSTN Converter"Obaweya SeyiPas encore d'évaluation

- FPGA Based Implementation of Baseline JPEG DecoderDocument7 pagesFPGA Based Implementation of Baseline JPEG DecoderUmar AnjumPas encore d'évaluation

- Hardware Co-Simulation For Video Processing Using Xilinx System GeneratorDocument5 pagesHardware Co-Simulation For Video Processing Using Xilinx System Generatordwivedi89Pas encore d'évaluation

- IJCER (WWW - Ijceronline.com) International Journal of Computational Engineering ResearchDocument4 pagesIJCER (WWW - Ijceronline.com) International Journal of Computational Engineering ResearchInternational Journal of computational Engineering research (IJCER)Pas encore d'évaluation

- LS01 ServiceDocument53 pagesLS01 ServicehutandreiPas encore d'évaluation

- Section 16781 CCTV System: King Faisal University Al-Ahsa 16781-1 CCTV System Library BuildingDocument10 pagesSection 16781 CCTV System: King Faisal University Al-Ahsa 16781-1 CCTV System Library Buildingnadeem UddinPas encore d'évaluation

- STB Hardware ComponentsDocument10 pagesSTB Hardware ComponentsshajeenahamedPas encore d'évaluation

- Data SheetDocument17 pagesData Sheetvijay963Pas encore d'évaluation

- DSP Lab 21-09-2021Document78 pagesDSP Lab 21-09-2021POORNIMA PPas encore d'évaluation

- Tms320c6713 User ManualDocument60 pagesTms320c6713 User ManualJagannath Vishnuteja Desai100% (1)

- DSP Lab ManualDocument26 pagesDSP Lab ManualMadhan ReddyPas encore d'évaluation

- Raphics Ideo Ubsystem: Subsystem OverviewDocument16 pagesRaphics Ideo Ubsystem: Subsystem OverviewThomas A. EDISSONPas encore d'évaluation

- Video Coding and A Mobile Augmented Reality ApproachDocument10 pagesVideo Coding and A Mobile Augmented Reality Approachvfotop1Pas encore d'évaluation

- 13.1 A Fully-Integrated Single-Chip SOC For BluetoothDocument3 pages13.1 A Fully-Integrated Single-Chip SOC For BluetoothkurabyqldPas encore d'évaluation

- Tech SeminarDocument27 pagesTech SeminarNaresh KPas encore d'évaluation

- ARM Question Bank Unit - 5Document14 pagesARM Question Bank Unit - 5sakthivelv.eecPas encore d'évaluation

- Line BufferDocument11 pagesLine BufferTuan HuynhPas encore d'évaluation

- Video Connectivity Using TMDS IO inDocument36 pagesVideo Connectivity Using TMDS IO inYatindra TrivediPas encore d'évaluation

- Vga Pin AssignmentDocument10 pagesVga Pin Assignmentafmohkjbg100% (1)

- Vestel dvd7500 Orion dvd-2705 5.1ch SMDocument25 pagesVestel dvd7500 Orion dvd-2705 5.1ch SMgondifPas encore d'évaluation

- ADPCM ImplementationDocument13 pagesADPCM ImplementationDumitru GheorghePas encore d'évaluation

- DSP CasestudyDocument23 pagesDSP CasestudyShayani BatabyalPas encore d'évaluation

- Dsa 00376113Document4 pagesDsa 00376113गणेश पराजुलीPas encore d'évaluation

- HMIDocument20 pagesHMIJakki ReddyPas encore d'évaluation

- Manual For Cycle 1Document193 pagesManual For Cycle 1Seth GreenePas encore d'évaluation

- Xapp495 S6TMDS Video InterfaceDocument16 pagesXapp495 S6TMDS Video InterfaceNông Văn DânPas encore d'évaluation

- Desmo Uliers 2012Document12 pagesDesmo Uliers 2012Anonymous UI7JawqPas encore d'évaluation

- Ex No: Introduction To DSP & DSK (Tms320C6711) DateDocument9 pagesEx No: Introduction To DSP & DSK (Tms320C6711) DateParthaSarathyPas encore d'évaluation

- SLM - Unit 13Document15 pagesSLM - Unit 13Shobhit ShahPas encore d'évaluation

- Exor 2011 CatalogDocument6 pagesExor 2011 CatalogServo2GoPas encore d'évaluation

- Cell Broadband Engine Implementations: Viterbi Decoder: Nadia Akhtar MT2009007 (Cell: 9538308949)Document12 pagesCell Broadband Engine Implementations: Viterbi Decoder: Nadia Akhtar MT2009007 (Cell: 9538308949)FRB123Pas encore d'évaluation

- Osciloscopio GameBoy PDFDocument10 pagesOsciloscopio GameBoy PDFCarmelo LlorentePas encore d'évaluation

- K L With Advanced Encryption Standard (AES) Receiver/DecoderDocument8 pagesK L With Advanced Encryption Standard (AES) Receiver/DecoderbilarodrigoPas encore d'évaluation

- Understanding Mpeg-2: Digital Video CompressionDocument7 pagesUnderstanding Mpeg-2: Digital Video CompressionARTMehr Eng. GroupPas encore d'évaluation

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.D'EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Pas encore d'évaluation

- Color Profile: Exploring Visual Perception and Analysis in Computer VisionD'EverandColor Profile: Exploring Visual Perception and Analysis in Computer VisionPas encore d'évaluation

- SCE - EN - 014-101 Hardware Configuration IOT2000EDU - R1806Document71 pagesSCE - EN - 014-101 Hardware Configuration IOT2000EDU - R1806NileshPas encore d'évaluation

- Repieter FrimwareDocument1 pageRepieter FrimwareWillian CarlosPas encore d'évaluation

- How To Interface I2C-EEPROM With LPC2148 - ARM7 SlickerDocument8 pagesHow To Interface I2C-EEPROM With LPC2148 - ARM7 SlickerabidparwezPas encore d'évaluation

- USB 2.0 Video PC Camera Controller SN9C270A Datasheet: Document No.: SA3TD-270ADocument20 pagesUSB 2.0 Video PC Camera Controller SN9C270A Datasheet: Document No.: SA3TD-270AВладимир ЧакийPas encore d'évaluation

- UNIT-4 Data Link Layer of IoTDocument20 pagesUNIT-4 Data Link Layer of IoTnimmaladinesh82Pas encore d'évaluation

- EeproDocument4 pagesEeproAnkit DhimanPas encore d'évaluation

- ZL30159 Full DatasheetDocument85 pagesZL30159 Full Datasheetrohitsingh2909Pas encore d'évaluation

- Kenwood KDC 2031 SG Service ManualDocument32 pagesKenwood KDC 2031 SG Service ManualVangelis BoulasikisPas encore d'évaluation

- Philips Chassis L9.2e-AaDocument58 pagesPhilips Chassis L9.2e-AaAnonymous XUyUvTaUidPas encore d'évaluation

- DM-TFT26-381 DatasheetDocument18 pagesDM-TFT26-381 DatasheetIceflowPas encore d'évaluation

- Dokumen - Tips - Cansat Program Stensat Group Introduction To Cansat It Is Arduino CompatibleDocument58 pagesDokumen - Tips - Cansat Program Stensat Group Introduction To Cansat It Is Arduino CompatibleJoaquim FirminoPas encore d'évaluation

- Multiwingspan Microbit RTCDocument3 pagesMultiwingspan Microbit RTCDenes MarschalkoPas encore d'évaluation

- Sohail ResumeDocument4 pagesSohail ResumeSohail NayyarPas encore d'évaluation

- MC059A - B Training ManualDocument26 pagesMC059A - B Training ManualfalchoniPas encore d'évaluation

- Rxi Box Ipc-Xr: Hardware Reference ManualDocument60 pagesRxi Box Ipc-Xr: Hardware Reference ManualTung NguyenPas encore d'évaluation

- SF45 - LiDAR Datasheet - Rev 1Document8 pagesSF45 - LiDAR Datasheet - Rev 1steedPas encore d'évaluation

- Using The TWI Module As I2C MasterDocument11 pagesUsing The TWI Module As I2C Mastermithrandair100% (1)

- MCP2016 16 Bit I-O I2C PDFDocument38 pagesMCP2016 16 Bit I-O I2C PDFwhynot05Pas encore d'évaluation

- PICAXE-18M2 Information: RevolutionDocument6 pagesPICAXE-18M2 Information: RevolutionJoão CeraPas encore d'évaluation

- Microcontrolador Main TV Samsung WT61P802 PDFDocument54 pagesMicrocontrolador Main TV Samsung WT61P802 PDFAntonio Chavez100% (1)

- FT5336Document13 pagesFT5336Sándor DósaPas encore d'évaluation

- Nvdimm Vs DimmDocument25 pagesNvdimm Vs DimmmanPas encore d'évaluation

- Seat Detection System Using Internet of ThingsDocument4 pagesSeat Detection System Using Internet of ThingsAnonymous s66avcC100% (1)

- GNSS-Implementation AppNote (UBX-13001849)Document84 pagesGNSS-Implementation AppNote (UBX-13001849)extortionchloride610Pas encore d'évaluation

- Picaxe Manual1Document112 pagesPicaxe Manual1carloslouPas encore d'évaluation

- PHILIPS LC04 LCD TV Technical Training ManualDocument44 pagesPHILIPS LC04 LCD TV Technical Training Manualcentauro2013Pas encore d'évaluation